Abstract

In this paper, a modified differential voltage current conveyor transconductance amplifier (MDVCCTA) based meminductor emulator has been proposed. The proposed meminductor is realized using one MDVCCTA, one resistor, and two grounded capacitors that leads to a very simple configuration. The emulator is working for a significant range of frequencies up to 80 MHz. The transient and non-volatility tests are found to be satisfactory. The corner and Monte Carlo analyses are done to verify the robustness of the proposed design. In addition, to assess the endurance of the recommended meminductor emulator, its workability with variations in supply voltage, temperature, and component values has been investigated. The pinched hysteresis loops that are fingerprints for the meminductor emulator are not deformed for any such variations. A comparison of suggested meminductor with those available in literature has been done based on several performance parameters. Two applications that demonstrate the viability of the suggested meminductor emulator have also been comprehended.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Mem-elements (memristor, meminductor, and memcapacitor) are now being used in a variety of applications including brain-inspired neuromorphic computing [1, 2], secure communications [3], artificial intelligence circuits [4], neural networks [5], non-volatile memories [6], in-memory computation [7], etc. Their wide range of applications is possible due to the unique features offered such as non-linear behaviour, and the inherent memory properties that open a window for in-memory computation. These two unique characteristics of mem-elements make them superior to the conventional circuit elements i.e., resistors, capacitors, and inductors. The properties offered by mem-elements cannot be replicated by combining the properties of the conventional circuit elements. Due to this fact, mem-elements are now treated as specific elements that are dominating many areas of science and engineering including electronics and communication, electrical, computer science, biological sciences, etc. All credit goes to Prof. Leon Chua who envisaged the memristor long back in 1971 in his seminal paper [8]. Later, Prof. Chua and Prof. S. M. Kang generalized the idea of memristive systems in 1976 [9]. In current scenarios, memristive systems are viewed as the future of electronics [10]. The constraints of CMOS technology have become a bottleneck to advancing the performance of systems in terms of speed, area, and power dissipation. These limitations are due to the adverse effects of CMOS technology which became dominating when the size of CMOS is reduced beyond the limit and no further improvement is possible. Memristor (memory-resistor) has paved the way as an alternative of CMOS technology due to its inherent ability of tininess and very low power consumption. Due to above-mentioned facts, the coming era of electronics and computer engineering belong to memristors and the two other members of the mem-elements namely memcapacitors and meminductors. A lot has already been done on memristor and it is presently available as an off-the-shelf component in the market. However, the same cannot be said for memcapacitor and meminductor. Consequently, the goal of this paper is to realize a simple meminductor emulator configuration. Mem-elements possess almost similar characteristics when a periodic signal is applied across their terminals. Pinched hysteresis loops (PHLs) are observed that indicate the existence of memory inside them. These PHLs have been observed between charge (q) and flux (ɸ) for memristor (MR), whereas it is observed between charge (q) and voltage (v), and flux (ɸ) and current (i), for memcapacitor (MC) and meminductor (ML) respectively. The inter-relations among these mem-elements are given in Fig. 1 [11]. The following equations serve as a definition of meminductive systems.

where ML represents the meminductance of the emulator. From Eqs. (1), (2), and (3), the relation between flux (ɸ) and current (i) is deduced as:

where i(t) and ɸ(t) are the meminductive current and induced flux respectively. The flux ɸ(t) of meminductor is defined as:

where Vin(t) is the periodic signal applied across the meminductor.

Interrelations among mem-elements [11]

In the literature, a number of meminductor emulators have been reported. The significant meminductors available in open literature have been summarized in Table 1. The objective of the work in this paper is to develop a single active building block (ABB) based floating meminductor emulator. The focus has been on realizing an electronically tunable meminductor with a simple structure, sparse use of passive components, and broad frequency operation.

The structure of the proposed meminductor is very simple and requires only one modified differential voltage current conveyor transconductance amplifier (MDVCCTA), one resistor, and two capacitors. The incremental and decremental modes of operation can be obtained by adding one switch at the input side. The proposed meminductor has the following characteristics: (i) the circuit is very simple and does not require any multipliers (ii) both incremental and decremental modes can be obtained (iii) flexible to use in both grounded and floating modes (iv) large frequency range (v) does not use any memristor. Various features such as, the number of analog building blocks, operating frequency, multiplier/multiplier-less, electronic tunability, number of passive components, floating/grounded mode, inductor/inductor-less, flux/charge controlled, incremental/decremental configurations, matching conditions, control parameters, and power supply are used to compare the proposed meminductor to previously reported circuits in the literature.

The following conclusions are drawn in view of the comparison shown in Table 1:

-

1.

The proposed circuit uses only one MDVCCTA, whereas previously reported circuits in reference no. [13,14,15,16,17,18,19,20,21,22,23,24,25,26,27,28,29,30,31,32,33,34,35, 38, 39, 41, 42, 44,45,46,47,48, 50, 51, 53, 55,56,57,58, 61,62,63] use more than one building block.

-

2.

The proposed emulator design does not require any memristor, whereas the circuits reported in reference no. [12, 14,15,16, 21, 25, 26, 37, 40, 43, 52, 53, 57] require a memristor for their implementation.

-

3.

The recommended circuit is electronically tunable, but the meminductors reported in reference numbers [12,13,14,15,16,17,18,19,20,21,22,23,24,25,26,27,28,29,30, 36, 43, 49, 53, 56,57,58,59, 62] are not electronically tunable.

-

4.

The suggested emulator can be operated in both grounded and floating modes, but the emulators reported in reference no. [12,13,14,15, 18, 22, 23, 27, 32,33,34, 36, 43, 46,47,48,49, 52, 53, 56,57,58, 60, 62] can only be operated in grounded mode.

-

5.

The meminductor emulator of reference numbers [13, 18,19,20, 22,23,24, 27, 28, 31,32,33, 48, 49, 61] use multiplier but in the proposed circuit no multiplier is needed.

-

6.

The meminductor emulators reported in reference numbers [12, 13, 16,17,18,19,20,21,22,23,24, 26,27,28,29, 31, 32, 35,36,37, 40, 43, 48, 48,49,50,51,52,53, 57,58,59] work satisfactorily in the operating frequency between Hz to kHz range but the proposed circuit operates up to MHz range. The operating frequency of the meminductor emulator reported in reference [54] is 50 MHz and in [60] is 25 MHz, whereas the proposed meminductor works up to 80 MHz with some shifting in cross-over point.

-

7.

The limitation of the proposed meminductor emulator is the restricted range of tunability and shifted pinched point at higher frequencies.

-

8.

The meminductor emulator of reference numbers [13, 15, 21,22,23, 32,33,34, 49, 52, 53, 57, 61] use high power supply voltage but in the proposed circuit use only ± 0.9 V.

-

9.

The meminductor reported in the reference numbers [13, 21, 23, 28, 30, 36, 37, 40, 49, 55, 61, 62] are operated on charge-controlled mode whereas the proposed circuit operated on flux-controlled mode.

-

10.

The proposed meminductor is working on both incremental and decremental mode but previously reported circuits in reference no [13,14,15,16,17,18,19,20,21,22,23,24,25,26,27,28,29,30,31,32, 36, 38, 41, 47, 49, 51,52,53, 57,58,59,60,61,62] is working on one mode only.

-

11.

The meminductor reported in the reference numbers [14, 17, 19, 23, 28, 29, 38, 50, 53, 57] use matching conditions but the proposed circuit does not need any matching condition.

The work in the paper has been divided into 7 sections, including the 1st introductory section. Section 2 gives a brief description of the ABB used to design the suggested meminductor emulator. The explanation of the recommended meminductor along with its mathematical analysis has been given in Sect. 3. LTSpice results observed in 0.18 μm technology along with their appropriate discussion have been presented in Sect. 4. Section 5 focuses on the precision analysis and study of non-ideal aspects related to the proposed meminductor emulator. The section delineates variations in its fundamental characteristics concerning changes in temperature, supply voltage, and component parameters. Furthermore, it provides an in-depth exploration of the influence of non-idealities and parasitic components within the MDVCCTA block. Application of the suggested meminductor in implementing chaotic oscillator and adaptive learning circuit has been explained in Sect. 6. Finally, the conclusion summary of the work is given in Sect. 7.

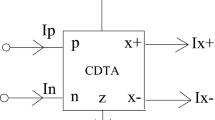

2 Description of MDVCCTA

The differential voltage current conveyor transconductance amplifier (DVCCTA) is a comparatively new ABB proposed by Pandey and Paul in 2011 [64]. It integrates the traits of a transconductance amplifier (TA) and a differential difference current conveyor (DDCC) [65]. The DVCCTA incorporates the adaptable and distinctive characteristics of DDCC, such as the simplicity with which differential and floating input circuits can be implemented, with the flexibility of in-built parameter tuning. The modified differential voltage current conveyor transconductance amplifier (MDVCCTA) is a modified version of a DVCCTA, which possess two transconductance amplifiers. The block diagram representing the input and output terminals of MDVCCTA is shown in Fig. 2. Y1 and Y2 are the differential input voltage terminals. X and Z are intermediate terminals responsible for generating voltage and current proportional to input voltage based on components attached to these terminals. O+ and O- are output current terminals of the transconductance amplifier unit and generate current proportional to the voltage developed at the Z terminal. The two transconductance gains of this unit can be controlled by biasing voltage VB2 and VB3.

Block diagram of MDVCCTA [64]

The matrix equation depicting the port relations of MDVCCTA is given by Eq. (6).

In Eq. (6), Gm1 and Gm2 represent the transconductance gains of MDVCCTA. Assuming symmetric differential pairs, transconductance for the proposed circuit can be written as:

here, β represents the transconductance parameter of the corresponding MOSFET, VSS is the negative supply voltage and Vth is the threshold voltage of a MOSFET. In addition, VB2 and VB3 are the biasing voltages responsible for controlling the biasing current of first and second transconductance amplifiers respectively. Here, K1 and K2 are the transconductance parameters defined as:

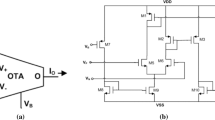

The MOSFET-based complete circuit of MDVCCTA is illustrated in Fig. 3.

3 Proposed MDVCCTA-based electronically tunable floating meminductor

Figure 4 depicts the complete design of meminductor emulator proposed in the paper. In this circuit, the differential input signal is directed between Y1 and Y2 terminals of MDVCCTA. This differential signal is transferred to the “X” terminal, where the resistor R1 generates a current proportional to an input voltage signal. Further, this current is copied at the “Z” terminal of the MDVCCTA block. This current charge the capacitor C1 connected at this node, leading to the generation of a voltage VZ at the “Z” terminal. A current directly proportional to VZ appears at the output terminal (O±), which leads to a similar current to be drawn from the input voltage source. The output terminals are shorted to input Y terminals. These arrangements lead to the inductive behaviour of the circuit depicted in Fig. 4. A capacitor C2 is connected to VB3 and as shown in the circuit, the current flowing through O1- terminal charges this capacitor. This current being proportional to the input voltage (Vin), makes a feedback connection that ensures the meminductive input current to be dependent on the input flux (ϕ). This leads to the meminductive behaviour of the circuit.

3.1 Derivation of meminductance of proposed meminductor

The proposed meminductor can be used in incremental configuration (“x” connected to “a” and “y” connected to “b”) as well as decremental configuration (“x” connected to “b” and “y” connected to “a”). Using the terminal equations of MDVCCTA depicted in Eq. 6 and performing basic analysis of the meminductor circuit given in Fig. 4 for incremental configuration, the terminal voltages VX (Voltage at X terminal), VZ (Voltage at Z terminal) and VB3 (Voltage at VB3 terminal) can be represented as:

Applying Kirchoff’s voltage law, VB3 can be derived as:

Using the integral relations given by Eqs. (5) and (1), and performing mathematical simplification, Eqs. (9) and (10) can be expressed as:

Equations (14) and (15) have been written considering all the capacitances to be initially relaxed. Analysing circuit of MDVCCTA based meminductor shown in Fig. 4, input current (Iin) can be expressed as:

Here, Gm1 and Gm2 are the two transconductance gains of the MDVCCTA block, that are defined by Eq. (7). Combining Eqs. (14) and (16) and later substituting Gm2 and VB3 from Eqs. (7) and (15) respectively, Iin can be expressed as:

From Eq. (17) and considering relation (4), ML−1 of the proposed meminductor is given as:

From Eq. (18), it can be analysed that meminductance of the suggested meminductor comprises of a fixed component and a variable component. The fixed term is dependent on the MOSFET threshold voltage and the circuit's negative supply voltage. However, the variable term depends on input voltage and can be controlled by passive components (C1, C2 and R1) and transconductance of the amplifier.

The suggested meminductor design given in Fig. 4 can be used in decremental mode by connecting “x” node to “b” and “y” node to “a” in the switch shown in Fig. 4. The derivation of meminductance of the proposed circuit in this configuration can be carried out using the steps similar to the incremental mode derivation. In this case, the terminal voltage and current equations can be derived as:

Using Eq. (21) and Eq. (4), ML−1 of the proposed meminductor in decremental configuration is given as:

In decremental configuration, the fixed term is positive while the variable term of meminductance is negative. However, the magnitude and dependency of both the terms are same as that of the incremental configuration.

In the derivation of the incremental and decremental meminductance relations for the proposed emulator, Gm1 is supposed to be fixed. However, this gain term can be adjusted by regulating the bias voltage applied at VB2 terminal, imparting tunability feature to the proposed emulator.

4 Simulation results and discussion

The simulation results of the meminductor circuit designed in the paper have been shown in this section. These results have been generated in the LTspice tool. The MOSFETs of the CMOS-based MDVCCTA circuit have been implemented with a 0.18 μm model file. Supply voltage of ± 0.9 V, VB1 = 0.1 V and VB2 = 0.4 V have been used for the simulation of the MDVCCTA block. The feature size of the MOSFETs has been listed in Table 2. The basic characteristics of the suggested meminductor emulator have been plotted with C1 = C2 = 5pF and R1 = 1kΩ.

4.1 Simulation results of proposed floating meminductor when operated in incremental configuration

Initially, the proposed meminductor emulator's characteristics working as an incremental meminductor have been studied. To achieve incremental mode, the switch is connected as “x” to “a” and “y” to “b”. To examine the inductive behaviour of the proposed configuration, its transient response is observed with a bipolar signal of 100 mV amplitude and 10 kHz frequency. The waveforms observed for input current and flux (\(\phi\)) have been shown in Fig. 5. The flux (\(\phi =\int {V}_{in}dt\)) was measured at the input terminal. The phase lag witnessed in flux and current waveforms determine the inductive nature of the proposed circuit.

Non-volatile behaviour is one of the most important fingerprints for meminductors. When a pulse signal is provided, it anticipates that the meminductance will change correspondingly during the pulse's ON time, while it retains its value during the OFF time of the pulse. To observe the non-volatile behaviour of the circuit, a pulse signal of 25 mV amplitude, with 1 μs ON period and 10 μs OFF period has been applied. The resultant meminductance is depicted in Fig. 6. This meminductance (ML) has been obtained by dividing the flux (ɸ) by the input current.

(Iin). From this figure, it is evident that the meminductance remains constant during the OFF period of the input pulse but varies during the ON phase, validating the concept that the proposed meminductor is non-volatile.

Another essential feature of a meminductor is a pinched hysteresis loop (PHL) in flux (ɸ) vs. current (i) plane, when a bipolar signal is applied. A sinusoidal signal of 10 kHz frequency and 100 mV amplitude has been applied to the suggested meminductor and the response observed is plotted in Fig. 7.

The dumbbell shape of the PHL curve with zero-crossing, as seen in Fig. 7, further supports the proposed circuit's meminductive behaviour. The PHL curves are seen in the proposed meminductor for a wide range of input frequency signals. These loops for frequencies varying from 40 kHz to15MHz have been drawn in Fig. 8a and b. To obtain the PHL curves with zero-crossing for the specified range of frequencies, the passive components have been adjusted. The decreasing area of the PHL lobes with an increase in frequency is another essential feature of a meminductive device. The PHL curves of Fig. 8 provide a good visual representation of this characteristic.

Several applications demand capacitive tuning of a circuit. The circuit's capacitance tunability feature is determined by the property of change in PHL shape with changes in capacitance. To investigate this feature in the proposed meminductor, its response in φ vs. i plane for 10 kHz sinusoidal signal with different values of C1 and C2 has been analyzed. The curves obtained for varying C1 and C2 from 5 to 15pF have been plotted in Fig. 9. These curves shown in Fig. 9 depict the capacitance tunability feature of the proposed meminductor.

Electronic tunability is a feature that allows variations in key parameters of a circuit with changes in applied bias voltage or bias current. To illustrate the electronic tunability behaviour of the proposed meminductor, its PHL has been plotted in Fig. 10 for different values of VB2. All these cures have been drawn for an input signal of 10 kHz, 100 mV sinusoidal signal.

4.2 Simulation results of proposed floating meminductor emulator when operated in decremental configuration:

The curves plotted in Figs. 7, 8, 9, 10 are for incremental configuration of the suggested meminductor emulator. It can be operated in decremental configuration, provided the switch is positioned to get the links between “x” to “b” and “y” to “a”. The transient analysis curve and the PHL curve observed for this configuration for 10 kHz, 100 mV sinusoidal signal have been shown in Fig. 11a and b respectively. These curves for input signal frequency varying from 40 kHz to 15 MHz are shown in Fig. 12. All these curves show that the proposed meminductor operates satisfactorily in decremental configuration for frequencies range of 40 kHz–15 MHz.

At higher frequencies, shifting in the pinched point (v = 0, i = 0) is observed in PHL curves. The shifting of pinched point can be mitigated with proper selection of values of capacitors. The PHL curves observed are not deformed up to 80 MHz frequency, as can be seen in Fig. 13a–d.

5 Precision analysis of proposed meminductor

Practically, a device will be subjected to different environmental and manufacturing conditions leading to variations in its behaviour. To check the tolerance of a device in a practical environment its behaviour must be examined under different values of parameters. The effects of varying the suggested meminductor's parameters have been examined in this section.

5.1 Temperature variation analysis

The proposed meminductor's behaviour with temperature fluctuations ranging from −55 °C to + 125 °C has been investigated. PHL curves obtained for incremental and decremental configuration of the proposed meminductor for the specified range of temperature variations have been shown in Fig. 14a and b. These figures illustrate how the proposed meminductor exhibits minor variations in the PHL curves' shapes, resulting in successful operation as meminductor within the designated temperature range.

5.2 Monte-Carlo analysis

A MOSFET is subjected to variations in aspect ratio and threshold voltage while being manufactured in a real environment. Monte Carlo (MC) analysis has been carried out to assess the effects of variations in the proposed meminductor's properties caused by fabrication limitations experienced by the constituent MOSFETs. The MC analysis has been performed with 5% variations in aspect ratio and the threshold voltage of MOSFETs using the Gaussian distribution function. The MC plots of PHL curves for a sinusoidal signal of 10 kHz frequency have been drawn in Fig. 15a and b for threshold variations for incremental and decremental meminductors respectively. These curves have been plotted for 100 runs. These MC plots illustrate that the shape of PHL curves is maintained while demonstrating only minor alterations because of changes in the MOSFET specifications, supporting the meminductive behaviour of the proposed circuit over the complete mismatch range.

5.3 Corner analysis

Based on fabrication technology and design environment, a MOSFET can undergo variations in design parameters. It has been observed that there is an upper and lower limit to the variations that can appear during a particular fabrication process. In view of this, 4 design corners have been specified for CMOS-based circuits. These design corners are: fast–fast (FF), fast-slow (FS), slow-fast (SF) and slow-slow (SS). In all these corners, the first term signifies the NMOS characteristic, and the second term represents PMOS behaviour. To ensure the robust operation of the proposed circuit, its behaviour at four different corners has been studied. The PHL curves observed for these design corners along with typical curves for a sinusoidal signal of 10 kHz have been shown in Fig. 16. From Fig. 16, it can be analysed that the PHL loops are observed at all the corners, confirming the effective functioning of the suggested design in the entire design space.

5.4 Supply voltage variations

To analyse the effect of supply voltage variations on the behaviour of the proposed meminductor, the MDVCCTA block has been subjected to a variation of ± 10% in supply voltage. The proposed meminductor incorporating this MDVCCTA block is simulated with a sinusoidal signal of 10 kHz frequency and the resultant PHL curve observed in ϕ vs. i plane has been recorded in Fig. 17. These waveforms plot the PHL curves for variations in supply voltage from 0.81 to 0.99 V for VDD and −0.81 to −0.99 V for VSS. PHL curves shown in Fig. 17 confirm that the proposed meminductor operates satisfactorily with minor changes in lobe shape for ± 10% deviations in supply voltage.

5.5 Variations due to resistance tolerance

Precise values of the components can never be achieved at the time of fabrication. There is always some tolerance in the component values, which may sometimes lead to circuit failure. To examine the effect of the variations in resistance values, the proposed meminductor has been simulated for different values of resistors. The PHL curves for the incremental and decremental meminductor, observed with different values of R1 (10kΩ, 20kΩ, and 30kΩ) have been plotted in Fig. 18.

The figures from Figs. 14, 15, 16, 17, 18 show the tolerance of the proposed meminductor to changes in temperature, supply voltage, and component characteristics. All of these figures reveal that the PHL lobe's shape changes slightly while preserving the necessary shape when any of these parameters changes.

5.6 Non-ideal and parasitic analysis

The mathematical analysis and derivations presented in Sect. 3 were based on the assumption that the MDVCCTA depicted in Fig. 4 is ideal. In this analysis, the current and voltage transfers at various ports of the MDVCCTA block were treated as ideal, as indicated by Eq. (6). Additionally, the presence of parasitic elements in the active devices used to implement the block were disregarded. In this section, the meminductance of the proposed block has been derived while considering the impact of these non-ideal parameters and parasitic components. The port matrix of the MDVCCTA, accounting for non-idealities, can be expressed as:

In Eq. (23), α and β denote the non-ideal voltage and current gains at terminals 'X' and 'Z' of the MDVCCTA, while γ represents the non-ideal parameter affecting the transconductance gain at port 'O' of the MDVCCTA. These parameters assume a value of unity in the ideal case. The equivalent circuit of the proposed meminductor, accounting for parasitic capacitors and resistors at various terminals of the MDVCCTA block, is illustrated in Fig. 19 [66].

To simplify the analysis, one terminal of the input voltage source is grounded. In this circuit, each parasitic component is identified by a superscript corresponding to the terminal at which it is present, while Rs represents the source resistance. Taking into account the non-idealities expressed by Eq. (23) and the parasitic components depicted in Fig. 19, the subsequent section provides the mathematical analysis of the meminductance for the proposed emulator.

Considering the specified non-idealitites and parasitics, port equations of MDVCCTA can be expressed as:

Simple analysis of node ‘Z’ reveals:

Substituting the value of IX and VX from Eqs. (24) and (25), yields:

Applying Kirchoff’s current law at node ‘Y1’ gives:

Using Eqs. (23) and (29), Iin can be expressed as:

Considering source resistor (Rs), Eq. (31) can be expressed as:

Simplifying Eq. (32), VY1 can be obtained as:

From Eq. (28), it can be analyzed that:

Assuming, 1/RZ<<s(C1+CZ) for the operating frequency range, Eq. (34) can be simplified as:

Using Eqs. (23), (24), (25), and (33), along with Eq. (5) that represents flux of meminductor as time integral of input voltage, VZ can be defined as:

Simple analysis of Fig. 18 shows that:

Assuming, \(\left(\frac{1}{{R}_{0-}}+\frac{1}{{R}_{B}}\right)\ll\) \(s\left({C}_{0-}+{C}_{B}+{C}_{2}\right)\), and substituting I01- from Eqs. (23), (37) can be simplified as:

Substituting VZ from Eq. (36) and using flux relation given by Eqs. (1), (38) can be modified as:

Performing routine analysis at node ‘Y1’, it can be analysed that:

Carrying out simple mathematical analysis on Eqs. (30) and (40), yields:

Using Eq. (7), Iin and ML-1 of proposed meminductor while considering parasitics and non-idealities are expressed by Eq. (42) and (43) respectively.

here,

Analysis of Eqs. (42), (43), and (44) reveals that the parasitic elements, namely RX, CZ, C0, and CB, can be effectively disregarded by consolidating them with R1, C1, and C2, respectively. Additionally, assuming R0+ and RY1 to be significantly large, and CY1 and C0+ to be extremely small, enables the neglect of the minor current IZY1 in comparison to Iin. These considerations collectively contribute to the robust and practically stable behavior of the proposed meminductor.

6 Applications of proposed meminductor

In this section, to demonstrate the viability of the suggested meminductor emulator, two applications—chaotic oscillator and adaptive learning circuit—have been implemented.

6.1 Chaotic oscillator

Since the previous three decades, the chaos phenomena has been extensively explored in a variety of scientific fields, including physics, ecology, biology, optics, etc. An intriguing and straightforward tool for researching and creating chaos in electronic and communication systems is Chua's chaotic oscillator. This circuit exhibits rich dynamics, is simply built, and is tractable mathematically. These features have made Chua's oscillator a popular choice for producing chaotic signals for real-world applications, including: music, secure communications, neural networks, nonlinear waves, and visual sensing [67, 68]. This oscillator's architecture is mostly built around Chua's diode, an active three-segment nonlinear resistor. In Fig. 20, a simple fourth-order chaotic oscillator is displayed [18]. In this circuit, Chua’s diode has been replaced with the proposed meminductor emulator. The negative resistance required in the circuit has been implemented using OPAMP based negative impedance converter (NIC). The four state variables of this circuit are: voltage across capacitor C1 (VC1), voltage across capacitor C2 (VC2), current through inductor L (IL), and current through meminductor ML (IML).

The state-equations representing first-order dynamics of this circuit are given as:

here C1, C2, L, ML, R1 and R2 denote the values (capacitance, inductance, meminductance or resistance) of the corresponding element. The suitable values of these component parameters have been chosen in order to obtain chaotic response across state variables of the circuit. For the chaotic circuit depicted in Fig. 20, various projection plots generated in LTspice have been plotted in Fig. 21. These plots have been observed with the parameter’s values chosen as C1 = 65nF, C2 = 10nF, L1 = 60mH, R1 = 100Ω, and R2 = -2kΩ. The required value of R2 has been obtained with Ra = 2kΩ and Rb = 2kΩ. Here, ML has been replaced by proposed MDVCCTA based meminductor.

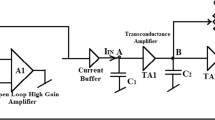

6.2 Adaptive learning circuit

The neuromorphic circuit using proposed meminductor emulator is presented in Fig. 22. The meminductors are found to be more suitable for neuromorphic applications as compared to memristors [69]. The proposed meminductor emulator circuit has been used in adaptive learning circuit to demonstrate how it adjusts its meminductance to achieve the appropriate resonance frequency of the circuit according to the applied input voltage (Vin). The response of the circuit mimics the behaviour of amoeba that is one of the simplest creatures on earth having brain-like behaviours in terms of controlling their actions based on the past events. The amoeba's locomotive speed is influenced by its surrounding temperature. Amoeba reduces its locomotive speed when temperature falls. The adaptive learning circuit shown in Fig. 22 behaves the similar way. The input pulse (Vin) represents the surrounding temperature, and the output voltage (Vout) represents the locomotive speed of amoeba. The amplitude of output voltage (amoeba’s locomotive speed) gets reduced when the input voltage (temperature) drops. The pattern of input voltage follows the three cases: drops in voltage (reduced temperature), rise in voltage (increased temperature), and the constant voltage (no change in temperature) as shown in Fig. 23. Initially, voltage is maintained constant, and it gets reduced after some time to a particular level. Thereafter, the voltage is increased to achieve the same level from where it started. The same process is repeated thrice initially and thereafter maintains the constant voltage for a specific time and again follows the same pattern for one period. This pattern is applied to provide all scenarios that amoeba faces in terms of temperature. The amoeba locomotive speed gets reduced, increased, and maintained constant for reduction, increment, and constant temperature, respectively. In the similar way, the output response (Vout) of the circuit closely follows the behaviour of input pulse due to inherent ability of remembrance of meminductor as can be seen from Fig. 23. Therefore, the adaptive learning circuit is made to anticipate the amoeba's behaviour in response to changes temperature in the environment. Three steps can be used to define the amoeba's learning process: storage of previous occurrences, future forecasting, and comprehension of the timing of recurrent events [70, 71]. An element with memory retention capabilities can be employed to simulate an adaptive learning circuit with amoeba-like behavioural responses. Therefore, the proposed meminductor emulator circuit is employed to realize an adaptive learning circuit. This circuit is implemented with the help of a resistor (R), a capacitor (C), and the suggested meminductor (ML).

Locomotive response against temperature fluctuations as seen by adaptive learning circuit of Fig. 22

7 Conclusion

The possibility of designing a single active block-based floating meminductor has been explored. The modified differential voltage current conveyor transconductance amplifier has been chosen due to its simple structure along with differential and in-built tuning features. The proposed circuit's appropriate operation has been confirmed by looking at the essential meminductor fingerprints, pinched hysteresis loops with zero-crossing and non-volatility tests. Through a simple switch connected at the input terminals, it has been demonstrated that the suggested circuit can operate in both incremental and decremental modes. The simulation results obtained in LTspice show the workability of the proposed circuit till 80 MHz while consuming 3.82mW power. The pinched hysteresis loops observed with temperature variations from −55 °C to + 125 °C, variations in resistance from 10 to 30kΩ, and ± 10% variations in supply voltage confirm the suitability of the proposed circuit in a practical environment. Additionally, Monte Carlo and corner analyses demonstrate the suggested meminductor's robustness. Furthermore, the successful design of a chaotic oscillator and an adaptive learning circuit utilizing the suggested meminductor has been illustrated.

Code availability

The code is available with corresponding author. It can be provided on reasonable request.

References

Zhang, Y., Wang, Z., Zhu, J., Yang, Y., Rao, M., Song, W., Zhuo, Y., Zhang, X., Cui, M., Shen, L., Huang, R., & Joshua Yang, J. (2020). Brain-inspired computing with memristors: Challenges in devices, circuits, and systems. Applied Physics Reviews, 10(1063/1), 5124027.

Li, Y., Wang, Z., Midya, R., Xia, Q., & Joshua Yang, J. (2018). Review of memristor devices in neuromorphic computing: Materials sciences and device challenges. Journal of Physics D: Applied Physics. https://doi.org/10.1088/1361-6463/aade3f

Sun, J., Shen, Y., Yin, Q., & Xu, C. (2013). Compound synchronization of four memristor chaotic oscillator systems and secure communication. Chaos: An Interdisciplinary Journal of Nonlinear Science. https://doi.org/10.1063/1.4794794

Liu, S., Wang, Y., Fardad, M., & Varshney, P. K. (2018). A memristor-based optimization framework for artificial intelligence applications. IEEE Circuits and Systems Magazine, 18, 29–44. https://doi.org/10.1109/MCAS.2017.2785421

Thomas, A. (2013). Memristor-based neural networks. Journal of Physics D: Applied Physics. https://doi.org/10.1088/0022-3727/46/9/093001

Ho, Y., Huang, G. M., Li, P. (2009). Nonvolatile memristor memory, pp. 485–490. https://doi.org/10.1145/1687399.1687491

Mehonic, A., Sebastian, A., Rajendran, B., Simeone, O., Vasilaki, E., & Kenyon, A. J. (2020). Memristors—from in-memory computing, deep learning acceleration, and spiking neural networks to the future of neuromorphic and bio-inspired computing. Advanced Intelligent Systems, 2, 2000085. https://doi.org/10.1002/aisy.202000085

Chua, L. (1971). Memristor-The missing circuit element. IEEE Transactions on Circuit Theory, 18, 507–519. https://doi.org/10.1109/TCT.1971.1083337

Chua, L. O., & Kang, S. M. (1976). Memristive devices and systems. Proceedings of the IEEE, 64, 209–223. https://doi.org/10.1109/PROC.1976.10092

Zidan, M. A., Strachan, J. P., & Lu, W. D. (2018). The future of electronics based on memristive systems. Nature Electronics, 1, 22–29. https://doi.org/10.1038/s41928-017-0006-8

Biolek, D., Biolek, Z., Biolkova, V. (2009). SPICE modeling of memristive, memcapacitative and meminductive systems. In ECCTD 2009 - Eur. Conf. Circuit Theory Des. Conf. Progr, pp. 249–252. https://doi.org/10.1109/ECCTD.2009.5274934

Pershin, Y. V., & Di Ventra, M. (2010). Memristive circuits simulate memcapacitors and meminductors. Electronics Letters, 46, 517–518. https://doi.org/10.1049/el.2010.2830

Sah, M. P., Budhathoki, R. K., Yang, C., & Kim, H. (2014). Charge controlled meminductor emulator. JSTS:Journal of Semiconductor Technology and Science, 14, 750–754. https://doi.org/10.5573/JSTS.2014.14.6.750

Wang, S. F. (2016). The gyrator for transforming nano memristor into meminductor. Circuit World., 42, 197–200. https://doi.org/10.1108/CW-01-2016-0002

Singh, A., & Rai, S. K. (2021). Novel meminductor emulators using operational amplifiers and their applications in chaotic oscillators. Journal of Circuits, Systems and Computers, 30, 1–20. https://doi.org/10.1142/S0218126621502194

Romero, F. J., Escudero, M., Medina-Garcia, A., Morales, D. P., & Rodriguez, N. (2020). Meminductor emulator based on a modified antoniou’s gyrator circuit. Electron., 9, 1–10. https://doi.org/10.3390/electronics9091407

Yu, D., Liang, Y., Iu, H. H. C., & Chua, L. O. (2014). A universal mutator for transformations among memristor, memcapacitor, and meminductor. IEEE Transactions on Circuits and Systems II: Express Briefs, 61, 758–762. https://doi.org/10.1109/TCSII.2014.2345305

Yuan, F., Wang, G., Jin, P., Wang, X., & Ma, G. (2016). Chaos in a meminductor-based circuit. International Journal of Bifurcation and Chaos. https://doi.org/10.1142/S0218127416501303

Yang, L., Shi, Y., Hu, B., Chen, L., & Su, J. (2018). Design and characteristic analysis of floating flux-controlled meminductor emulator. Xitong Fangzhen Xuebao Journal of System Simulation, 30, 1337–1346. https://doi.org/10.16182/j.issn1004731x.joss.201804016

Zhai, D. D., & Wang, F. Q. (2020). Simple double-scroll chaotic circuit based on meminductor. Journal of Circuits, Systems and Computers, 29, 1–21. https://doi.org/10.1142/S0218126620500486

Liang, Y., Chen, H., & Yu, D. S. (2014). A practical implementation of a floating memristor-less meminductor emulator. IEEE Transactions on Circuits and Systems II: Express Briefs, 61, 299–303. https://doi.org/10.1109/TCSII.2014.2312807

Sah, M. P., Budhathoki, R. K., Yang, C., Kim, H. (2014). A mutator-based meminductor emulator circuit. In Proceedings under IEEE International Symposium on Circuits and Systems, pp. 2249–2252. https://doi.org/10.1109/ISCAS.2014.6865618

Sah, M. P., Budhathoki, R. K., Yang, C., & Kim, H. (2014). Mutator-based meminductor emulator for circuit applications. Circuits, Systems, and Signal Processing, 33, 2363–2383. https://doi.org/10.1007/s00034-014-9758-9

Zhao, Q., Wang, C., & Zhang, X. (2019). A universal emulator for memristor, memcapacitor, and meminductor and its chaotic circuit. Chaos: An Interdisciplinary Journal of Nonlinear Science. https://doi.org/10.1063/1.5081076

Pershin, Y. V., & Di Ventra, M. (2011). Emulation of floating memcapacitors and meminductors using current conveyors. Electronics Letters, 47, 243–244. https://doi.org/10.1049/el.2010.7328

Yu, D. S., Liang, Y., Iu, H. H. C., & Hu, Y. H. (2014). Mutator for transferring a memristor emulator into meminductive and memcapacitive circuits. Chinese Physics B. https://doi.org/10.1088/1674-1056/23/7/070702

Fouda, M. E., Radwan, A. G. (2015). Memristor-less current- and voltage-controlled meminductor emulators. In 2014 21st IEEE Int. Conf. Electron. Circuits Syst. ICECS 2014, pp. 279–282. https://doi.org/10.1109/ICECS.2014.7049976

Liu, Y., & Iu, H. H. C. (2020). Novel floating and grounded memory interface circuits for constructing mem-elements and their applications. IEEE Access., 8, 114761–114772. https://doi.org/10.1109/ACCESS.2020.3004160

Yu, D., Zhao, X., Sun, T., Iu, H. H. C., & Fernando, T. (2020). A simple floating mutator for emulating memristor, memcapacitor, and meminductor. IEEE Transactions on Circuits and Systems II: Express Briefs, 67, 1334–1338. https://doi.org/10.1109/TCSII.2019.2936453

Yu, D., Zhao, X., Sun, T., Iu, H. H. C., & Fernando, T. (2020). The simple charge-controlled grounded/floating mem-element emulator. IEEE Transactions on Circuits and Systems II: Express Briefs, 67, 1334–1338. https://doi.org/10.1109/TCSII.2019.2936453

Sozen, H., & Cam, U. (2020). A novel floating/grounded meminductor emulator. Journal of Circuits Systems and Computers. https://doi.org/10.1142/S0218126620502473

Konal, M., & Kacar, F. (2020). Electronically tunable meminductor based on OTA. AEU - International Journal of Electronics and Communications, 126, 153391. https://doi.org/10.1016/j.aeue.2020.153391

Raj, A., Singh, S., & Kumar, P. (2021). Electronically tunable high frequency single output OTA and DVCC based meminductor. Analog Integrated Circuits and Signal Processing, 109, 47–55. https://doi.org/10.1007/s10470-021-01913-z

Kumar, K., & Nagar, B. C. (2021). New tunable resistorless grounded meminductor emulator. Journal of Computational Electronics, 20, 1452–1460. https://doi.org/10.1007/s10825-021-01697-5

Aggarwal, B., Rai, S. K., & Sinha, A. (2023). New memristor-less, resistor-less, two-OTA based grounded and floating meminductor emulators and their applications in chaotic oscillators. Integration., 88, 173–184. https://doi.org/10.1016/j.vlsi.2022.10.005

Babacan, Y. (2018). An operational transconductance amplifier-based memcapacitor and meminductor. Istanbul University-Journal of Electrical & Electronics Engineering, 18, 36–38. https://doi.org/10.5152/iujeee.2018.1806

ÇamTaşkıran, Z. G., Sağbaş, M., Ayten, U. E., & Sedef, H. (2020). A new universal mutator circuit for memcapacitor and meminductor elements. AEU- International Journal of Electronics and Communications, 119, 153180. https://doi.org/10.1016/j.aeue.2020.153180

Bhardwaj, K., & Srivastava, M. (2021). New electronically adjustable memelement emulator for realizing the behaviour of fully-floating meminductor and memristor. Microelectronics Journal, 114, 105126. https://doi.org/10.1016/j.mejo.2021.105126

Yadav, N., Rai, S. K., & Pandey, R. (2021). New grounded and floating memristor-less meminductor emulators using VDTA and CDBA. Journal of Circuits Systems and Computers. https://doi.org/10.1142/S0218126621502832

Singh, A., & Rai, S. K. (2021). VDCC-based memcapacitor/meminductor emulator and its application in adaptive learning circuit. Iranian Journal of Science and Technology, Transactions of Electrical Engineering, 45, 1151–1163. https://doi.org/10.1007/s40998-021-00440-x

Vista, J., & Ranjan, A. (2020). High frequency meminductor emulator employing VDTA and its application. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 39, 2020–2028. https://doi.org/10.1109/TCAD.2019.2950376

Yadav, N., Rai, S. K., & Pandey, R. (2022). New high frequency memristorless and resistorless meminductor emulators using OTA and CDBA. Sadhana-Academy Proceedings in Engineering Science. https://doi.org/10.1007/s12046-021-01785-z

Singh, A., & Rai, S. K. (2022). New meminductor emulators using single operational amplifier and their application. Circuits, Systems, and Signal Processing, 41, 2322–2337. https://doi.org/10.1007/s00034-021-01886-4

Yadav, N., Rai, S. K., & Pandey, R. (2023). Simple grounded and floating meminductor emulators based on VDGA and CDBA with application in adaptive learning circuit. Journal of Computational Electronics, 22, 531–548. https://doi.org/10.1007/s10825-022-01950-5

Aggarwal, B., Rai, S. K., Arora, A., Siddiqui, A., & Das, R. (2023). A floating decremental/incremental meminductor emulator using voltage differencing inverted buffered amplifier and current follower. Journal of Circuits Systems and Computers. https://doi.org/10.1142/s0218126623502432

Raj, A., Kumar, K., & Kumar, P. (2021). CMOS realization of OTA based tunable grounded meminductor. Analog Integrated Circuits and Signal Processing, 107(2), 475–482. https://doi.org/10.1007/s10470-021-01808-z

Singh, A., Borah, S. S., & Ghosh, M. (2021). Simple grounded meminductor emulator using transconductance amplifier. Midwest Symposium on Circuits and Systems, 2021-August, pp. 1108–1111. https://doi.org/10.1109/MWSCAS47672.2021.9531754

Orman, K., Yesil, A., & Babacan, Y. (2022). DDCC-based meminductor circuit with hard and smooth switching behaviors and its circuit implementation. Microelectronics Journal, 125, 105462. https://doi.org/10.1016/j.mejo.2022.105462

Korkmaz, M. O., Babacan, Y., & Yesil, A. (2023). A new CCII based meminductor emulator circuit and its experimental results. AEU - International Journal of Electronics and Communications. https://doi.org/10.1016/j.aeue.2022.154450

Bhardwaj, K., & Srivastava, M. (2023). VDTA and DO-CCII based incremental/decremental floating memductance/meminductance simulator: A novel realization. Integration. https://doi.org/10.1016/j.vlsi.2022.09.014

Bhardwaj, K., & Srivastava, M. (2022). New grounded passive elements-based external multiplier-less memelement emulator to realize the floating meminductor and memristor. Analog Integrated Circuits and Signal Processing, 110(3), 409–429. https://doi.org/10.1007/s10470-021-01976-y

Singroha, V., Aggarwal, B., & Rai, S. K. (2022). Voltage differencing buffered amplifier (VDBA) based grounded meminductor emulator. International Journal of Electrical and Electronics Research, 10(3), 487–491. https://doi.org/10.37391/ijeer.100314

Gupta, A., Rai, S. K., & Gupta, M. (2022). Grounded meminductor emulator using operational amplifier-based generalized impedance converter and its application in high pass filter. International Journal of Electrical and Electronics Research, 10(3), 496–500. https://doi.org/10.37391/ijeer.100316

Petrović, P. B. (2022). A new electronically controlled floating/grounded meminductor emulator based on single MO-VDTA. Analog Integrated Circuits and Signal Processing, 110(1), 185–195. https://doi.org/10.1007/s10470-021-01946-4

Singh, A., & Rai, S. K. (2022). OTA and CDTA-based new memristor-less meminductor emulators and their applications. Journal of Computational Electronics, 21(4), 1026–1037. https://doi.org/10.1007/s10825-022-01889-7

Goel, A., Rai, S. K., & Aggarwal, B. (2023). A new generalized approach for the realization of meminductor emulator and its application. Wireless Personal Communications, 131(4), 2501–2523. https://doi.org/10.1007/s11277-023-10549-3

Gupta, S., Gupta, M., Rai, S. K., & Singh, S. P. (2023). Grounded meminductor emulator using operational amplifiers and memristor. International Conference on Sustainable Computing and Smart Systems, ICSCSS 2023 - Proceedings, Icscss, pp. 1220–1225. https://doi.org/10.1109/ICSCSS57650.2023.10169173

Jain, H., Rai, S. K., & Aggarwal, B. (2023). A new electronically tunable current differencing transconductance amplifier based meminductor emulator and its application. Indian Journal of Engineering and Materials Sciences, 30(4), 550–558. https://doi.org/10.56042/ijems.v30i4.2047

Jain, H., Aggarwal, B., & Rai, S. K. (2023). New modified voltage differencing voltage transconductance amplifier (MVDVTA) based meminductor emulator and its applications. Indian Journal of Pure and Applied Physics, 61(4), 239–246. https://doi.org/10.56042/ijpap.v61i4.71313

Sharma, P. K., Tasneem, S., & Ranjan, R. K. (2023). A new electronic tunable high-frequency meminductor emulator based on a single VDTA. IEEE Canadian Journal of Electrical and Computer Engineering, 46(2), 179–184. https://doi.org/10.1109/ICJECE.2023.3261886

Ersoy, D., & Kacar, F. (2023). Electronically charge-controlled tunable meminductor emulator circuit with OTAs and its applications. IEEE Access, 11(May), 53290–53300. https://doi.org/10.1109/ACCESS.2023.3281200

Bhardwaj, K., & Srivastava, M. (2023). On the boundaries of the realization of single input single element-controlled universal memelement emulator. Circuits, Systems, and Signal Processing, 42(10), 6355–6366. https://doi.org/10.1007/s00034-023-02420-4

Yadav, N., Rai, S. K., & Pandey, R. (2023). An electronically tunable meminductor emulator and its application in chaotic oscillator and adaptive learning circuit. Journal of Circuits, Systems and Computers, 32(02), 25–27. https://doi.org/10.1142/S0218126623500317

Pandey, N., & Paul, S. K. (2011). Differential difference current conveyor transconductance amplifier: A new analog building block for signal processing. Journal of Electrical and Computer Engineering. https://doi.org/10.1155/2011/361384

Chiu, W., Liu, S. I., Tsao, H. W., & Chen, J. J. (1996). CMOS differential difference current conveyors and their applications. IEE Proceedings-Circuits, Devices and Systems, 143(2), 91–96.

Ranjan, R. K., Raj, N., Bhuwal, N., & Khateb, F. (2017). Single DVCCTA based high frequency incremental/decremental memristor emulator and its application. AEU - International Journal of Electronics and Communications, 82, 177–190. https://doi.org/10.1016/j.aeue.2017.07.039

Elwakil, A. S., & Kennedy, M. P. (2000). Improved implementation of Chua’s chaotic oscillator using current feedback op amp. IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications, 47, 76–79. https://doi.org/10.1109/81.817395

Tlelo-Cuautle, E., Gaona-Hernández, A., & García-Delgado, J. (2006). Implementation of a chaotic oscillator by designing Chua’s diode with CMOS CFOAs. Analog Integrated Circuits and Signal Processing, 48, 159–162. https://doi.org/10.1007/s10470-006-7299-2

Pershin, Y., La Fontaine, S., & Di Ventra, M. (2008). Memristive model of amoeba’s learning. Nature Precedings. https://doi.org/10.1038/npre.2008.2431.1

Pershin, Y. V., La Fontaine, S., & Di Ventra, M. (2009). Memristive model of amoeba learning. Physical review E: Statistical, Nonlinear, and Soft Matter Physics, 80, 1–6. https://doi.org/10.1103/PhysRevE.80.021926

Wang, F. Z. (2023). Beyond memristors: Neuromorphic computing using meminductors. Micromachines. https://doi.org/10.3390/mi14020486

Funding

Not applicable.

Author information

Authors and Affiliations

Contributions

Dr. SKR and Dr. RD contributed to the conception of ideas and circuit design. Material preparation and data collection were performed by Dr. RD and Dr. SKR. Simulations and analyses were performed by Dr. RD and Dr. BA. All authors have contributed to writing the manuscript and approved the final manuscript.

Corresponding author

Ethics declarations

Conflict of interest

There is no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Das, R., Rai, S.K. & Aggarwal, B. A floating meminductor emulator using modified differential voltage current conveyor transconductance amplifier and its application. Analog Integr Circ Sig Process 119, 475–496 (2024). https://doi.org/10.1007/s10470-024-02257-0

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-024-02257-0