Abstract

Meminductors are memory-based elements, which are gaining a lot of popularity as a result of their applications in widespread areas. However, due to the non-availability of their off-the-shelf ICs, designers are trying to find alternatives of meminductor emulators. This paper presents a generalized approach to designing a meminductor emulator from an active inductor circuit. An active inductor circuit having a current conveyor (CC), operational transconductance amplifier (OTA), and a grounded capacitor has been utilized. The idea is encouraged by the thought of putting memory in conventional active inductor circuits. In the proposed configuration, one additional block namely a current differencing buffered amplifier (CDBA) and an extra grounded capacitor have been used to modify the active inductor circuit into a meminductor emulator circuit. The goal is to implement a meminductor emulator employing active blocks which can be designed using commercially available ICs. Simulation results of the proposed emulator are obtained using the LTspice tool along with 0.18 µm CMOS technology parameters. The essential testimonials, pinched hysteresis loops, and non-volatility tests, confirm that the suggested circuit works as a meminductor emulator. Furthermore, the pinched hysteresis loops are observed for a large range of frequencies, verifying the wide dynamic frequency range of the suggested circuit. To assess how well the suggested meminductor emulator performs, a chaotic oscillator has been developed.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Resistors, inductors, and capacitors are the three basic components of electrical engineering. These components have been known for a long time, however, the other three, memristor, memcapacitor, and meminductor, have only recently come to light since last decade. These elements are generally known as mem-elements. Memristors, meminductors, and memcapacitors are therefore thought of as resistors, inductors, and capacitors with memories, respectively. Memristor was introduced by Prof. Leon Chua long back [1] but the device gained popularity after its physical realization in Hewlett-Packard Lab [2]. Memristor offers unique properties that can be utilized in different domains of electrical, electronics, and computer engineering. It is widely used in many areas of engineering and finds numerous fascinating applications [3,4,5,6,7,8]. Memristor has the capability to drive the various fields of engineering and is now accessible as an off-the-shelf component. But, still, there is a scope for the betterment of performance, and practicing engineers are continuously giving feedback about its pros and cons. Therefore, several circuits of emulators have also been developed to mimic the properties of memristors [9,10,11,12,13,14]. A vast amount of research has been done around memristors and the device is now seen as the element of the new era. After a successful journey of more than a decade, researchers are now exploring the extensive applications of other two mem-elements namely memcapacitor and meminductor. Memcapacitors and meminductors are not accessible as off-the-shelf components that paved the way for the designing of various emulator circuits. The realizations of meminductor emulators are quite challenging than memristors and memcapacitors.

In literature, the realizations of meminductor and memcapacitor emulators have been done by employing different prominent analog building blocks namely operational amplifiers (OP-AMPs), second-generation current conveyors (CCIIs), operational transconductance amplifiers (OTAs), current feedback operational amplifiers (CFOAs), current backward transconductance amplifier (CBTA), current differencing transconductance amplifier (CDTA), voltage differencing transconductance amplifier (VDTA), voltage differencing current conveyor (VDCC) and etc. In 2010, the first realization of the meminductor emulator employing OP-AMP, memristor, resistor, and the capacitor was claimed [15]. In the next paper, the mutator circuit that can convert the memristor into a meminductor and memcapacitor has been recommended [16]. It highlights the fact that the implementations of meminductors and memcapacitors are not easily possible as is the case of memristors. Subsequently, emulator circuits for both meminductor and memcapacitor have been suggested using CCIIs, memristor, capacitor, and inductor. To create the memcapacitor emulator from the meminductor emulator, the locations of the resistor, capacitor, and memristor are changed with the memristor, inductor, and resistor, correspondingly [17]. A meminductor emulator employing two CCIIs, one memristor, one capacitor, and one resistor was reported [18]. Four CCIIs, an adder, a multiplier, a buffer, a lossy integrator, a capacitor, and a lossy integrator have been used to design a memristor-less meminductor emulator [19]. With the help of an inductor, a multiplier, three OP-AMP, a number of MOSFETs, and two capacitors, a meminductor emulator controlled through charge was created [20]. Next, a meminductor emulator having both current-controlled and voltage-controlled features has been designed employing three CCIIs, a multiplier, an adder, three resistors, and two capacitors [21]. Subsequently, the memristor emulator circuit was coupled with a mutator circuit to realize a meminductor emulator. The mutator circuit was designed employing two CCIIs, a buffer, and two passive components whereas the memristor emulator was designed using inverting amplifiers, a buffer, a multiplier, and a few passive components [22]. Another meminductor emulator based on the mutation concept employing a mutator and a memristor emulator was published in [23]. A CCII+, a capacitor, three OP-AMPs, and resistors were used to design the mutator, and the same memristor emulator as described in [22] was also used. The performance of the meminductor circuits was proved by realizing parallel and hybrid connections of meminductor emulators [23]. Three CFOAs, a memristor emulator, a few resistors, and capacitors have been employed in designing a universal mutator [24]. Memristor-to-meminductor conversion has been described for an OP-AMP-based gyrator circuit [25]. Mutator-based meminductor emulator has been reported using four AD844s, one op-amp, a varactor diode, several resistors, and a capacitor [26]. Grounded/floating meminductor circuits having both grounded and floating characteristics were realized by employing CCIIs, analog multipliers, several resistors, and capacitors [27]. A CBTA, memristor, and capacitor have been employed in the reported mutator circuit for meminductor and memcapacitor designs. To convert the arrangement of the memcapacitor to the meminductor, the memristor, and capacitor's respective locations have been switched [28]. After altering the Riordan gyrator's circuit, a floating meminductor emulator has been described [29]. Two VDTAs and two capacitors are used in a fully floating meminductor emulator circuit that has been published [30]. The operation of another grounded emulator using VDTA, OTA, and two capacitors was described in [31]. Three OTAs and two capacitors have been used to create an OTA-based grounded meminductor emulator [32]. It has been stated that a different memcapacitor and meminductor emulator uses multi-output OTA and a few passive components [33]. Two CCIIs, one OTA, two resistors, and two capacitors have been employed to implement a flux-controlled meminductor circuit [34]. Six different meminductor circuits have been realized using two OP-AMPs, a memristor, a few resistors, and a capacitor [35]. A memristor, a capacitor, and one VDCC are used in another meminductor/memcapacitor circuit that has been published. To create meminductor and memcapacitor emulators, the memristor and capacitor positions have been switched [36]. It has been stated that a grounded capacitor, current differencing buffered amplifier (CDBA), and VDTA can be used to emulate a memristor-less meminductor [37]. A different memristor-less meminductor emulator employing OTA and CDBA was reported in [38]. The next paper describes a memristor, resistors, and capacitors-based operational amplifier-based meminductor emulator [39]. A meminductor emulator based on OTA and CDTA was reported in [40], whereas a meminductor emulator based on voltage differencing buffered amplifier (VDBA) and CDBA was implemented in [41]. Then, in order to create the meminductor emulator, a voltage differencing gain amplifier (VDGA) and a CDBA were utilized [42]. An adaptive learning circuit has also been realized to show the workability of proposed meminductor emulator. Then, using two OTAs and two grounded capacitors, the meminductor emulator was created [43]. Another meminductor emulator has been proposed in [44] and uses a current follower (CF), a voltage differencing inverted buffered amplifier (VDIBA), a parasitic resistance, and two capacitors. In [45], a meminductor emulator having a single active building block based on a modified voltage differencing voltage transconductance amplifier (MVDVTA) was described. In [46], a CCII-based meminductor emulator has been reported. A VDTA and current-conveyor (CC) based meminductor emulator was implemented in [47].

According to the literature on meminductor emulators, there are two common methods for designing meminductor emulator circuits. In the first approach, a mutator circuit is designed which converts memristor emulator circuits into meminductor and memcapacitor emulators. The second approach aims at memristor-less designs of the meminductor emulators. This paper attempts to highlight the meminductor design using a new approach. The methodology followed in this paper utilizes the concept of converting an active inductor circuit into a meminductor emulator by storing the charge flowing through the circuit in a capacitor. The idea is very similar to the thought of putting memory in an active inductor circuit [48]. While exploring the meminductor emulator circuits described in the literature, it has been witnessed that the majority of them either require the use of complex active blocks that are not readily obtainable as off-the-shelf components, or they demand the use of complex components such as memristors, multipliers, integrators, and adders. The motivation for the work done in this paper is to realize a simple meminductor employing active blocks that can be readily designed using off-the-shelf components available in the market. Additionally, no complex components must be required in its design. In the paper, following the new approach, the meminductor emulator has been designed in which an active inductor circuit formed by OTA and CCII is changed into a meminductor emulator circuit by storing its charge using a capacitor connected to one of the terminals of CDBA. This suggested emulator is free from the need of any complex components and all the employed blocks can be easily designed from the ICs commercially available in the market.

The paper is presented in eight different sections, which include the current introductory section. A basic review of the mem-elements is presented in Sect. 2. The features of the analog building blocks utilized in the suggested circuit architecture are illustrated in Sect. 3. Section 4 gives a thorough discussion of the proposed decremental/incremental grounded meminductor as well as a mathematical analysis of it. In Sect. 5, the simulation results are presented for the proposed meminductor emulator using the LTspice tool. The comparison summary of the suggested emulator circuit with the emulator circuits available in the literature is presented in Sect. 6. Section 7 shows how the suggested emulator is employed to realize a chaotic oscillator.

2 Basic Reviews of Mem-Elements

The mem-elements (memristor, memcapacitor, and mem-inductor) are viewed as conventional circuit elements (resistor, capacitor, and inductor) having memory. After incorporating memory in conventional circuit elements, very interesting results have been obtained that are utilized in several ways in circuit theory during the past decade. In this section, mem-elements are reviewed in order to give a clear understanding of the topic. The two important properties of mem-elements are the presence of memories and the capability of remembering past events. Thus, in order to confirm the behaviour of a device as a mem-element, the formation of pinched hysteresis loops is very important. Pinched hysteresis loops are obtained between voltage and current for the memristor. It is attained between charge and voltage for the memcapacitor whereas for the meminductor, it is obtained between flux and current. Another important testimonial for mem-elements is their state-retaining capability which is verified through the non-volatility test.

The various constitutive relations that correlate the mem-elements are formed with the help of current i, charge q, voltage v, and flux φ. The following relationship describes how a memristor (MR) functions:

that can be expressed as:

where V(t) is the potential across memristor MR and I(t) represents the current flowing through the memristor.

Memcapacitor (MC) relationship of charge q(t) and corresponding voltage V(t) is given by:

Meminductance (ML) is governed by the relationship of flux φ(t) and current I(t) flowing through it and is given as:

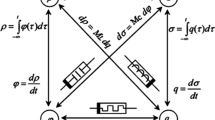

The interrelationships of these mem-elements are shown schematically in Fig. 1. The two new variables ρ and σ are time integrals of flux (φ) and charge (q) and are given by the following relations:

3 Analog Active Building Blocks (ABBs) Used in the Work

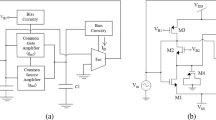

There are numerous analog active building blocks (ABBs) that are prominently employed for the development of emulator circuits. In this paper, operational transconductance amplifier (OTA), second generation current conveyor (CCII), and current differencing buffered amplifier (CDBA) have been used to present the meminductor emulator circuits. Figs. 2 and 3 show the symbolic representation of OTA and its circuit diagram respectively. An OTA acts as a current source controlled by a voltage that gives an output current (I0) when a differential voltage (VP - VN) is applied. The equation of I0 is expressed as:

where gm is the transconductance gain and is directed by a bias voltage (VB) as depicted in Eq. (8).

where k is μnCoxW/L and depends on a particular technology.

The current conveyor (CC) is a dominating block of the analog family. It can convey the input current at the different terminals of CCII. The characteristic equation of the second-generation current conveyor of negative type (CCII-) is given in Eq. (9).

The symbolic representation of CCII- and its circuit diagram are presented in Figs. 4 and 5 respectively.

4 Proposed decremental/incremental grounded meminductor emulator

The proposed meminductor emulator is shown in Fig. 8. An active inductor is formed with the help of OTA, CCII-, resistor R, and capacitor C1. The active inductor circuit is converted into a meminductor emulator circuit by storing the charge proportional to input current (Iin) in capacitor C2 that works as a memory element and the voltage developed across the capacitor (C2) has been utilized to change the transconductance (gm) gain of the OTA. The voltage (Vz) developed across the capacitor (C2) is equal to the voltage (Vw). The “W” terminal of CDBA is connected to the controlling terminal (VB) of OTA that controls the transconductance (gm). Transconductance (gm) affects the input current and thus the meminductance of the circuit is controlled by the previous charge stored across capacitor C2. The output current (Io) of OTA charges the capacitor (C1) and the voltage across the capacitor (C1) is “Vy” that is copied to the terminal “Vx” following the property of CCII-. The voltage “Vx” produces the current “Ix” in the resistor (R). The current “Iz” is equal to the current “Ix”. The current (Iz) is determined by the voltage (Vx) that is indirectly dependent on the value of the input current (Iin). The input current (Iin) gets changed according to the previous charge stored across the capacitor (C2). The circuit is having memory and from the input side, it realizes an active inductor. Thus, the proposed circuit behaves as a meminductor. The responses for both decremental and incremental meminductor emulators can be obtained by connecting the “z” terminal of CCII- to “P” and “N” terminals of CDBA, respectively.

The routine analysis of the circuit (Fig. 8) yields the following equations:

Current differencing buffered amplifier (CDBA) is another important ABB used for the realization of current-node circuits. The symbolic representation and circuit diagram of CDBA are depicted in Figs. 6 and 7 respectively. Ip and In represent the two input currents of CDBA. Their difference flows through a high impedance terminal "Z", and equal voltages are obtained at the "W" and "Z" terminals by the internal buffers of CDBA. The characteristic equation of CDBA is expressed as:

where as \(\int {\mathrm{V}}_{\mathrm{in}}\mathrm{dt}=\) \({\mathrm{\varphi }}_{\mathrm{in}}(\mathrm{t})\), Therefore, Eq. (12) can be written as

Terminal “Z-” of CCII- has to be coupled to the “P” or “N” terminal of CDBA for making the meminductor emulator decremental or incremental respectively. When the “Z-” terminal is connected to the “P” terminal, current Iz1 through capacitor C2 connected at the “Z1” terminal of CDBA is given as:

Therefore, the voltage “Vz1” across capacitor C2 is written as:

The current “Iz-” at output terminal “Z-” of CCII- is written as:

Replacing Vy in Eq. (13) with the help of Eq. (16), we get

Using current “Iz-” from Eq. (17) and substituting into Eq. (15), we get:

where \(\int {\mathrm{\varphi }}_{\mathrm{in}}\mathrm{dt}=\) \(\uprho (\mathrm{t})\) and \(\int {\mathrm{I}}_{\mathrm{in}}\mathrm{dt}=\) \(\mathrm{q}(\mathrm{t})\).

Thus, the Eq. (18) can be rewritten as:

The voltage “Vw” of CDBA is equal to voltage “Vz” and “W” terminal is connected to controlling voltage “VB”. Thus, we can writec the following equation as:

Putting “VB” from Eq. (20) to Eq. (8) results in:

Replacing the transconductance (gm) in Eq. (17) with the value of gm expressed in Eq. (21) gives:

Current I (t), meminductance (ML), and flux Φ (t) are related in the following way:

Rearranging the equation (23) results in:

After comparing Eq. (22) and Eq. (24) we get:

The Eq. (25) can be rearranged as:

If the terminal “Z-” of CCII- is interchanged from “P” terminal to “N” terminal of CDBA, Eq. (26) modifies to

Equations (26) and (27) can be merged into single equation (28) in which “+” sign correspond to inverse meminductance of incremental meminductor emulator whereas “-” sign indicates the inverse meminductance of decremental meminductor emulator.

5 Simulation Results and Discussions

The suggested meminductor circuit has been modelled with 0.18 μm CMOS parameters using the LTspice simulation tool. Table 1 lists the feature size of the MOSFETs utilized in the implementation of OTA, CCII-, and CDBA. The passive elements values utilized in the suggested meminductor emulator's design are R1 = 1 kΩ, C1 = C2 = 40 pF. The supply voltage is chosen as VDD = − VSS = 0.9V.

5.1 Meminductive Behaviour

One of the important testimonials of the meminductor is the appearance of a pinched hysteresis loop (PHL) when a bipolar signal is applied. The PHL is observed when the characteristic of the meminductor is plotted on the current (i) versus. flux (φ) plane. To investigate the proposed meminductor behaviour, a sinusoidal signal having 100mV amplitude is applied at its input terminals. The obtained curves for frequency range varying from 100 Hz – 1 MHz have been shown in Fig. 9a–f. These curves show dumb-bell-shaped PHL curves with zero-crossing, verifying the first testimonial of the meminductor. Furthermore, it can be observed from the curves of Fig. 9 that the area enclosed by the lobes reduces with an increase in frequency. This is another important testimonial of a meminductor. The curves depicted in Fig. 9 are plotted when the meminductor is operated in incremental configuration, which is obtained when the “Z-” terminal of CCII- is connected to the “N” terminal of CDBA. The PHL loops for the decremental meminductor design are drawn in Figs. 10a–f. To plot all these curves, the positive terminal of OTA is excited with a 100mV sinusoidal signal. These curves depict that the circuit operates in a decremental configuration from 100 Hz to 1 MHz, further verifying its satisfactory operation for a wide frequency range.

Similar to an inductor, the voltage signal of a meminductor has phase lead in comparison to current and flux signals. To verify this property in the suggested emulator, its transient response has been observed for a 1 kHz sinusoidal signal of 100 mV amplitude. The waveform observed for input voltage (Vin) along with flux and current waveforms are drawn in Fig. 11. The phase lag of current and flux signals compared to the input voltage signal is confirmed by the analysis of this figure. Thereby, justifying the meminductive behaviour of the proposed design.

It is expected from a mem-element to remember its current state. This memory characteristic of any mem-element is verified by observing its response to a pulse signal. The mem-element retains the current state during the OFF period of the pulse, while it changes the state during the ON period of the pulse. This is known as a non-volatility test for the mem-inductor. For the proposed incremental meminductor emulator non-volatility test is performed by applying a pulse signal of 100 mV amplitude and “ON” time of 50 ns whereas the total time period is 1000 ns. The output obtained is shown in Fig. 12, which indicates that the proposed meminductor emulator successfully verifies the non-volatility test as it remembers the previous value of meminductance and starts increasing for the next “ON” period.

5.2 Capacitive Tuning

The variations in the PHL response of the meminductor with different values of capacitance is a desired feature for the applications that offer capacitive tuning. To investigate the impact of variations in capacitor values, the proposed meminductor is simulated with a sinusoidal signal of 100 mV and 1 kHz. The PHL curves observed for C2 varying from 30pF to 50pF in equal steps of 5pF have been plotted in Fig. 13. The slight variations in the PHL curves confirm the capacitive tuning feature of the suggested meminductor emulator.

5.3 Performance and Tolerance Analysis

Practically a device will be subjected to environmental factors leading to changes in its behaviour. To testify the performance and tolerance of the proposed meminductor emulator while facing environmental variations, its response with changes in temperature and supply voltage has been investigated. For these analyses a 1kHz sinusoidal signal of 100mV amplitude is applied at the input terminal of the suggested circuit. Fig. 14 plots the variations observed in PHL curves when the temperature is varied from − 100 °C to 100 °C. These curves follow meminductive behaviour showing zero-crossing dumb bell-shaped PHL curves. However, slight variations in the shape are observed with changes in temperature. The PHL responses observed for variations in supply voltage have been shown in Fig. 15. These plots have been obtained for supply voltage varying from ±0.8V to ±1V.

The simulation results shown in Fig. 9, 10, 11, 12, 13 have been plotted considering the specified aspect ratios given in Table 1. However, any fabrication process is bound to have certain uncertainties. The impact of these uncertainties can be examined with the help of corner analysis. There are 4 corners (i) fast-fast (FF), (ii) fast-slow (FS), (iii) slow-fast (SF), and (iv) slow-slow (SS). These 4 corners act as the complete workspace for the circuit as after being fabricated the characteristics of the circuit are limited by these 4 corners. The suggested circuit's corner analysis has been performed, and the findings are displayed in Fig. 16. From this figure it is perceived that PHL loops are formed with zero-crossing for all 4 corners, confirming the workability of the proposed emulator in complete design space. Here also similar to previous cases PHL curves for different corners are obtained with slight variations in the shape.

Figures 14, 15, and 16 testify the robust nature of the suggested meminductor design with variations in environmental and fabrication factors.

6 Comparative Summary of the Proposed Meminductor Emulator with Meminductor Emulators of Literature

In Table 2, the suggested meminductor emulator's performance has been contrasted with that of meminductor emulators currently in use. The following observations have been pointed out:

-

1.

The suggested meminductor design does not employ memristor while the meminductor emulators reported in [15, 17, 18, 23, 24, 28, 29, 35, 36] use memristor in their design.

-

2.

The realized emulator circuit is very simple while the meminductor emulator reported in [20, 22, 24, 27] uses an analog multiplier and several other components that make the design very complex.

-

3.

The meminductor emulator realizations reported in [15, 23, 27,28,29] are simple but have restricted frequency range limited to a few Hz or kHz frequencies while the meminductor proposed in this work to satisfaction up to 3 MHz frequency.

-

4.

The frequency of operation of other meminductor emulators reported recently in [30, 31, 35] is also comparable to the frequency of operation of the proposed emulator.

7 Chaotic Oscillator using Proposed Meminductor Emulator

The proposed grounded meminductor design is employed in the design of a chaotic oscillator. The chaotic oscillator is a non-periodic oscillator that exhibits classic chaotic behavior. Chua’s circuit is considered to be the simplest electronic circuit that produces chaos. A 4th-order canonical Chua’s oscillator is shown in Fig. 17. In this circuit, the non-linear device (ML) has been implemented by the suggested meminductor emulator. The values of passive components chosen for SPICE simulations are capacitor C1 = C2 = 50pF and inductor L = 25 μH. A negative impedance converter (NIC) has been designed with resistance values Ra = 15 Ω and Rb = 5 Ω. The chaotic oscillator’s 2-D projection plots are shown in Fig. 18.

8 Conclusions

This paper presents a new approach to the realization of a meminductor emulator circuit. Using this approach, active inductor circuits can be easily converted into meminductor emulator circuits. This approach is the generalized one and many new circuits of meminductor emulators can be realized using it. Following this approach, an active inductor circuit consisting of an OTA, CCII, resistor, and a capacitor has been transformed into a meminductor emulator circuit using one additional block namely CDBA, and an extra grounded capacitor. The important fingerprints: pinched hysteresis loops and non-volatility tests, confirm the functioning of the proposed emulator as a meminductor emulator. PHL curves have been obtained for both decremental and incremental meminductor emulators for a wide range of frequencies. Additionally, corner analysis and study of the suggested emulator with different environmental parameters indicate its robustness. The proposed meminductor emulator has been used to realize a chaotic oscillator that verifies the workability of the emulator as well as the proposed approach of conversion.

Code availability

The code is available with corresponding author. It can be provided on reasonable request.

References

Chua, L. (1971). Memristor-the missing circuit element. IEEE Transactions on circuit theory, 18(5), 507–519. https://doi.org/10.1109/TCT.1971.1083337

Strukov, D. B., Snider, G. S., Stewart, D. R., & Williams, R. S. (2008). The missing memristor found. Nature Publishing Group, 453(7191), 80–83. https://doi.org/10.1038/nature06932

Itoh, M., & Chua, L. (2019). Memristor cellular automata and memristor discrete-time cellular neural networks. Springer, Handbook of Memristor Networks. https://doi.org/10.1007/978-3-319-76375-0_47

Kim, K. H., Gaba, S., Wheeler, D., Cruz-Albrecht, J. M., Hussain, T., Srinivasa, N., & Lu, W. (2012). A functional hybrid memristor crossbar-array/CMOS system for data storage and neuromorphic applications. Nano letters, 12(1), 389–395. https://doi.org/10.1021/nl203687n

Hu, X., Duan, S., Wang, L., & Liao, X. (2012). Memristive crossbar array with applications in image processing. Science China Information Sciences, 55(2), 461–472. https://doi.org/10.1007/s11432-011-4410-9

Yang, J. J., Pickett, M. D., Li, X., Ohlberg, D. A. A., Stewart, D. R., & Williams, R. S. (2008). Memristive switching mechanism for metal/oxide/metal nanodevices. Nature Nanotechnology, 3(7), 429–433. https://doi.org/10.1038/nnano.2008.160

Pickett, M. D., Strukov, D. B., Borghetti, J. L., Yang, J. J., Snider, G. S., Stewart, D. R., & Williams, R. S. (2009). Switching dynamics in titanium dioxide memristive devices. Journal of Applied Physics, 106(7), 074508. https://doi.org/10.1063/1.3236506

Wang, X., Chen, Y., Gu, Y., & Li, H. (2009). Spintronic memristor temperature sensor. IEEE Electron Device Letters, 31(1), 20–22. https://doi.org/10.1109/LED.2009.2035643

Yadav, N., Rai, S. K., & Pandey, R. (2020). New grounded and floating memristor emulators using OTA and CDBA. International Journal of Circuit Theory and Applications, 48(7), 1154–1179. https://doi.org/10.1002/cta.2774

Gupta, S., & Rai, S. K. (2020). New grounded and floating decremental/incremental memristor emulators based on CDTA and its application. Wireless Personal Communications, 113(2), 773–798. https://doi.org/10.1007/s11277-020-07252-y

Yadav, N., Rai, S. K., & Pandey, R. (2021). Novel memristor emulators using fully balanced VDBA and grouned capacitor. Iranian Journal of Science and Technology, Transactions of Electrical Engineering, 45, 229–245. https://doi.org/10.1007/s40998-020-00357-x

Srivastava, P., Gupta, R. K., Sharma, R. K., & Ranjan, R. K. (2020). MOS-only Memristor emulator. Circuits, Systems, and Signal Processing, 39(11), 5848–5861. https://doi.org/10.1007/s00034-020-01421-x

Sharma, V. K., Parveen, T., & Ansari, M. S. (2021). Four quadrant analog multiplier based memristor emulator using single active element. AEU-International Journal of Electronics and Communications, 130, 152575. https://doi.org/10.1016/j.aeue.2020.153575

Ranjan, R. K., Sharma, P. K., Sagar, R. N., Kumari, B., & Khateb, F. (2019). Memristor emulator circuit using multiple-output OTA and Its experimental results. Journal of Circuits, Systems and Computers, 28(10), 1950166. https://doi.org/10.1142/S0218126619501664

Pershin, Y. V., & Ventra, M. D. (2010). Memristive circuits simulate memcapacitors and meminductors. Electronics Letters, 46(7), 517–518. https://doi.org/10.1049/el.2010.2830

Biolek, D., Biolkova, V., & Kolka, Z. (2020). Mutators simulating memcapacitors and meminductors. IEEE Asia Pacific Conference on Circuits and Systems. https://doi.org/10.1109/APCCAS.2010.5774993

Pershin, Y. V., & Di, V. M. (2011). Emulation of floating memcapacitors and meminductors using current conveyors. Electronics Letters, 47(4), 243–244. https://doi.org/10.1049/el.2010.7328

D-Sheng, Y, Yan, L., HHC, Iu, & Yi-Hua, H,. (2014). Mutator for transferring a memristor emulator into meminductive and memcapacitive circuits. Chinese Physics B, 23(7), 1–11. https://doi.org/10.1088/1674-1056/23/7/070702

Liang, Y., Chen, H., & Yu, D. S. (2014). A practical implementation of a floating memristor-less meminductor emulator. IEEE Transactions on Circuits and Systems II: Express Briefs, 61(5), 299–303. https://doi.org/10.1109/TCSII.2014.2312807

Sah, M. P., Budhathoki, R. K., Yang, C., & Kim, H. (2014). Charge controlled meminductor emulator. Journal of Semiconductor Technology and Science, 14(6), 750–754. https://doi.org/10.5573/JSTS.2014.14.6.750

Fouda M.E., & Radwan, AG (2014). Memristor-less current and voltage-controlled meminductor emulators. In: 21st IEEE International Conference on Electronics, Circuits and Systems (ICECS), pp 279-282. https://doi.org/10.1109/ICECS.2014.7049976

Sah, M. P., Budhathoki, R. K., Yang, C., & Kim, H. (2014). A mutator-based meminductor emulator circuit. IEEE International Symposium on Circuits and Systems (ISCAS). https://doi.org/10.1109/ISCAS.2014.6865618

Sah, M. P., Budhathoki, Y., & RK, & Kim, C. H. (2014). Mutator-based meminductor emulator for circuit applications. Circuits, Systems, and Signal Processing, 33(8), 2363–2383. https://doi.org/10.1007/s00034-014-9758-9

Yu, D., Liang, Y., Iu, H. H. C., & Chua, L. (2014). A universal mutator for transformations among memristor, memcapacitor, and meminductor. IEEE Transactions on Circuits and Systems II: Express Briefs, 61(10), 758–762. https://doi.org/10.1109/TCSII.2014.2345305

Wang, S. F. (2016). The gyrator for transforming nano memristor into meminductor. Circuit World, 42(4), 197–200. https://doi.org/10.1108/CW-01-2016-0002

Yu, D., Zhao, X., Sun, T., Iu, T., & HHC, Fernando,. (2019). A simple floating mutator for emulating memristor, memcapacitor, and meminductor. IEEE Transactions on Circuits and Systems II: Express Briefs, 67(7), 1334–1338. https://doi.org/10.1109/TCSII.2019.2936453

Zhao, Q., Wang, C., & Zhang, X. (2019). A universal emulator for memristor, memcapacitor, and meminductor and its chaotic circuit. Chaos: An Interdisciplinary Journal of Nonlinear Science, 29(1), 1–14. https://doi.org/10.1063/1.5081076

Taskiran, Z. G. C., Sagbas, M., Ayten, U. E., & Sedef, H. (2020). A new universal mutator circuit for memcapacitor and meminductor elements. AEU-International Journal of Electronics and Communications, 119, 1–11. https://doi.org/10.1016/j.aeue.2020.153180

Francisco, R. J., & Alfredo, M.-G. (2021). Design and implementation of a floating meminductor emulator upon Riordan gyrator. AEU: International Journal of Electronics and Communications, 133, 1–7. https://doi.org/10.1016/j.aeue.2021.153671

Bhardwaj, K., & Srivastava, M. (2021). New electronically adjustable memelement emulator for realizing the behaviour of fully-floating meminductor and memristor. Microelectronics Journal, 114(105126), 1–15. https://doi.org/10.1016/j.mejo.2021.105126

Kumar, K., & Nagar, B. C. (2021). New tunable resistorless grounded meminductor emulator. Journal of Computational Electronics, 20, 1452–1460. https://doi.org/10.1007/s10825-021-01697-5

Raj, A., Kumar, K., & Kumar, P. (2021). CMOS realization of OTA based tunable grounded meminductor. Analog Integrated Circuits and Signal Processing, 107, 475–482. https://doi.org/10.1007/s10470-021-01808-z

Demir, E., Yesil, A., Babacan, Y., & Karacali, T. (2021). Operational transconductance amplifier-based electronically controllable memcapacitor and meminductor emulators. Journal of Circuits Systems and Computers (World Scientific), 30(12), 2150222. https://doi.org/10.1142/S0218126621502224

Raj, N., Ranjan, R. K., Khateb, F., & Kumngern, M. (2021). Mem-elements emulator design with experimental validation and its application. IEEE Access, 9, 69860–69875. https://doi.org/10.1109/ACCESS.2021.3078189

Singh, A., & Rai, S. K. (2021). Novel meminductor emulators using operational amplifiers and their applications in chaotic oscillators. Journal of Circuits, Systems, and Computers, 30(12), 2150219. https://doi.org/10.1142/S0218126621502194

Singh, A., & Rai, S. K. (2021). VDCC-based memcapacitor/meminductor emulator and its application in adaptive learning circuit. Iranian Journal of Science and Technology, Transactions of Electrical Engineering, 45, 1151–1163. https://doi.org/10.1007/s40998-021-00440-x

Yadav, N., Rai, S. K., & Pandey, R. (2021). New grounded and floating memristor-less meminductor emulators using VDTA and CDBA. Journal of Circuits Systems and Computers, 30(15), 2150283. https://doi.org/10.1142/S0218126621502832

Yadav, N., Rai, S. K., & Pandey, R. (2022). New high frequency memristorless and resistorless meminductor emulators using OTA and CDBA. Sadhana, 47(8), 1–18. https://doi.org/10.1007/s12046-021-01785-z

Singh, A., & Rai, S. K. (2022). New meminductor emulators using single operational amplifier and their application. Circuits, Systems, and Signal Processing, 41(4), 2322–2337. https://doi.org/10.1007/s00034-021-01886-4

Singh, A., & Rai, S. K. (2022). OTA and CDTA-based new memristor-less meminductor emulators and their applications. Journal of Computational Electronics, 21(4), 1026–1037. https://doi.org/10.1007/s10825-022-01889-7

Yadav, N., Rai, S. K., & Pandey, R. (2023). An electronically tunable meminductor emulator and its application in chaotic oscillator and adaptive learning circuit. Journal of Circuits, Systems, and Computers, 32(2), 2350031. https://doi.org/10.1142/S0218126623500317

Yadav, N., Rai, S. K., & Pandey, R. (2023). Simple grounded and floating meminductor emulators based on VDGA and CDBA with application in adaptive learning circuit. Journal of Computational Electronics, 22(1), 531–548. https://doi.org/10.1007/s10825-022-01950-5

Aggarwal, B., Rai, S. K., & Sinha, N. (2023). New memristor-less, resistor-less, two-OTA based grounded and floating meminductor emulators and their applications in chaotic oscillators. Integration, 88, 173–184. https://doi.org/10.1016/j.vlsi.2022.10.005

Aggarwal, B., Rai, S. K., Arora, A., Siddique, A., & Das, R. (2023). A floating decremental /incremental meminductor emulator using voltage differencing inverted buffered amplifier and current follower. Journal of Circuits, Systems, and Computers,. https://doi.org/10.1142/S0218126623502432

Jain, H., Aggarwal, B., & Rai, S. K. (2023). New modified voltage differencing voltage transconductance amplifier (MVDVTA) based meminductor emulator and its applications. Indian Journal of Pure & Applied Physics, 61(4), 239–246. https://doi.org/10.56042/ijpap.v61i4.71313

Korkmaz, M. O., Babacan, Y., & Yesil, A. (2023). A new CCII based meminductor emulator circuit and its experimental results. AEU-International Journal of Electronics and Communications, 158, 154450. https://doi.org/10.1016/j.aeue.2022.154450

Bhardwaj, K., & Srivastava, M. (2023). VDTA and DO-CCII based incremental/decremental floating memductance/meminductance simulator: A novel realization. Integration, 88, 139–155. https://doi.org/10.1016/j.vlsi.2022.09.014

Ventra, M. D., & Pershin, Y. V. (2009). Putting memory into circuit elements: Memristors, memcapacitors and meminductors. Proceedings of the IEEE, 97(8), 1371–1372. https://doi.org/10.1109/JPROC.2009.2022882

Funding

Not applicable.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

There is no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Goel, A., Rai, S.K. & Aggarwal, B. A New Generalized Approach for the Realization of Meminductor Emulator and Its Application. Wireless Pers Commun 131, 2501–2523 (2023). https://doi.org/10.1007/s11277-023-10549-3

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11277-023-10549-3