Abstract

In this research article, a grounded resistorless meminductor emulator is proposed. The proposed emulator uses one voltage differencing transconductance amplifier (VDTA) and one operational transconductance amplifier (OTA) with corresponding grounded capacitances. It can be operated in both decremental and incremental configurations. The comparison of the proposed emulator with available literature is also included. The proposed meminductor emulator circuit has been designed and simulated in Cadence Virtuoso Analog Design Environment using 180 nm gdpk technology parameters. Moreover, the application of the proposed emulator as a second-order bandpass filter (BPF) is also given. The simulation results agree well with the theory and confirm the meminductor functionality.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

The essential elements of circuits are resistor, capacitor, and inductor, and these essential elements describe the relationship between the voltage, current, and charge. Other than these essential elements, in 1971, L. O. Chua [1] introduced one more component of the circuit called a memristor, which is filling the gap between the relationship between the current, charge, voltage, and flux. Now this new system, which has a mathematical relationship between charge and flux, is finally a practical design discovered by Hewlett Packard (HP), which is based on a thin film of titanium dioxide [2]. It waves the researcher toward the memristor. After the concept of memristor, two new memory elements charge controlled memcapacitor and meminductor [3] introduced, which has the same storage capacity based on the capacitance and inductance, which can be used efficiently in the absence of a power source. The problem was how to make these designs fabricate and make them compatible with the trends. Most of the circuits present in the market are based on the CMOS. In recent years, a lot of scientific studies have been done for these modern memory elements with their design and their application [4,5,6,7]. A new era of research has been started for hybrid memristors, memcapacitors, and meminductors based on CMOS devices. Now in design researcher primary motivation is toward making a memory for the real-time application in low power digital computation [8], neuromorphic circuit [9], adaptive filter [10], chaotic signal generator [11], programmable analog circuits [12, 13], adaptive learning [14, 15] and non-volatile memories [16, 17].

A lot of attention has been given to design grounded and floating meminductor emulators utilizing the different high-performance active analog building blocks (ABBs) such as operational amplifier (OA) [21], second-generation current conveyor (CCII) [22], voltage differencing transconductance amplifier (VDTA) [24], and operational transconductance amplifier (OTA) [25] have been reported. Unfortunately, these reported circuits suffer from one or more of the following weaknesses:

-

Excessive use of passive components, especially external resistors [18].

-

Use of floating capacitors, which is not suitable for monolithic integration [25].

-

Use of multiplier, which has suffered lots of limitations [18, 19, 25].

-

Limited operating frequency range up to a few kHz [18,19,20,21,22, 25].

-

The reported circuits [18, 19, 21] uses OA, which has suffered the gain bandwidth and slew rate limitations.

The authors in this article proposed a new tunable grounded meminductor emulator using VDTA and OTA that overcomes all the drawbacks mentioned above. The proposed circuit provides the following advantages features:

-

The proposed circuit does not employ an external multiplier.

-

The proposed circuit employs only grounded capacitors, which are advantages from the point of IC implementation. The use of grounded capacitor circuits can compensate for the stray capacitances at their nodes.

-

The proposed emulator is completely resistorless, i.e., no external resistors are employed.

-

The proposed circuit provides electronic tunability.

-

The proposed circuit does not employ memristors.

This paper presents a resistless meminductor emulator with grounded capacitors. The paper is organized as follows. Section 2 describes the port relationship of VDTA and OTA ABBs and illustrates their symbol and CMOS implementations, followed by Sect. 3, which describes the proposed emulator with a detailed mathematical explanation of its operation. Section 4 presents the simulation results of various analyses performed. Section 5 shows the comparison of the proposed meminductor emulator with available literature. Conclusions are drawn in Sect. 6.

2 Analog building blocks with their properties

In this paper, one voltage difference transconductance amplifier (VDTA) and one operational transconductance amplifier (OTA) are used as active building blocks (ABBs). The VDTA is a simple and versatile ABB. It is composed of two cascaded transconductance amplifiers, and both transconductances (gm1 and gm2) provide electronic tunability [12]. The port relationships of VDTA are given as:

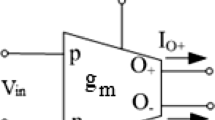

The schematic symbol and MOS realization of VDTA are shown in Fig. 1. The differential input voltage \(\left({V}_{P}-{V}_{N}\right)\) is the function of transconductance (\({g}_{m1}\)) is transferred to a current in Z port and similarly, transconductance (\({g}_{m2}\)) with voltage (\({V}_{Z}\)) acts as a current in X port. Finally, both the transconductances are defined by \({g}_{m1}=\frac{{g}_{1}+{g}_{4}}{2}\), and \({g}_{m2}=\frac{{g}_{5}+{g}_{8}}{2}\). Here, \({g}_{i}\) is the transconductance value of \({i}^{th}\) the transistor is denoted by \({g}_{i}\)=\(\sqrt{2{I}_{D}{k}_{Mi}}\). Assume the following pairs \(\left({M}_{1}{,M}_{2}\right), \left({M}_{3}{,M}_{4}\right), \left({M}_{5}{,M}_{6}\right) and \left({M}_{7}{,M}_{8}\right)\) are identical. This results in the reduction of transconductance gains (\({g}_{m1}\) and \({g}_{m2}\)) of VDTA can be expressed as:

where,\({k}_{1}=\left[\frac{\sqrt{{k}_{M\mathrm{1,2}}}+\sqrt{{k}_{M\mathrm{3,4}}}}{2\sqrt{2}}\right]\sqrt{{k}_{B}}\) and \({k}_{2}=\left[\frac{\sqrt{{k}_{M\mathrm{5,6}}}+\sqrt{{k}_{M\mathrm{7,8}}}}{2\sqrt{2}}\right]\sqrt{{k}_{B}}\).

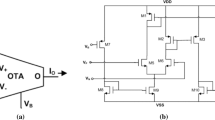

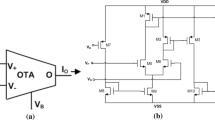

The OTA is a high gain high input and output impedance amplifier. The circuit symbol and its CMOS implementation of OTA are shown in Fig. 2. The characteristics of an OTA are expressed as:

where \({V}_{in}={V}_{+}-{V}_{-}\) is the differential input voltage and \({G}_{M}\) is the transconductance of an OTA. The transconductance of OTA (\({G}_{M}\)) is expressed as:

where \(K=\upmu {C}_{Ox}\frac{W}{L}\) and the µ, Cox, W, L, Vth are mobility, oxide capacitance, channel width, channel length, and the threshold voltage of MOS transistor, respectively.

3 Proposed circuit

The meminductor and memcapacitor are the elements of the memristor family. The input current (Iin) and flux (\({\phi}_{in}\)) relation of meminductor is defined as

where \({L}_{M}^{-1}\) is the inverse meminductance of the meminductor.

The flux control meminductor [13,14,15] having an initial value of inverse meminductance (x) and decremental or incremental product term (y) is generally expressed as

A proposed grounded resistorless meminductor is implemented using one VDTA, one OTA, and two grounded capacitors. The schematic diagram of the grounded meminductor is shown in Fig. 3. From Fig. 3,

where \(p\left(t\right)=\int \Phi (t)dt\). From Eqs. (12) and (13)

Eq. (14) shows that the proposed circuit works as a grounded meminductor. Where \({g}_{m3}\) and \({g}_{m2}\) can be controlled by the bias voltage VB and VB2, respectively. That’s why the proposed grounded meminductor circuit makes it electronically tunable. The decremental/incremental operation can be achieved by the proper switch selection between the V+ and V- terminal of OTA. Equation (14) represents decremental/incremental meminductor where \(-\) K1(gm2/C1)(VSS + Vth) is a constant value, and \(\pm \) K1(gm2/C1)(gm3gm2ρ(t)/C1C2) is the time-varying term as ρ(t) is the function of the time-varying input signal.

4 Simulation results

The proposed meminductor emulator is theoretically proved, and all simulated results are verified on Cadence Virtuoso 180 nm gpdk technology parameters. The aspect ratio of VDTA and OTA are shown in Table 1. The supply voltages for CMOS based VDTA and OTA are VDD = − VSS = 1.2 V and biasing voltage is given by VB1 = VB2 = 0.1 V. Figure 4a and b shows the transient response, and Fig. 4c shows the hysteresis loop of grounded meminductor with an input signal amplitude of 500 mV at a frequency of 3 MHz, and the capacitance values are chosen as C1 = 2 pF and C2 = 3 pF. The non-volatile is the most key feature of the meminductor. The characteristics behavior of the meminductor emulator is examined by considering the input pulse signal with an amplitude of 500 mV and pulse width 100 ns for the period of 250 ns. The changes in the meminductance input signal are plotted with respect to time is shown in Fig. 5 for incremental and decremental topology, respectively. During ON time, the ratio of current and flux varies, whereas it remains constant during the OFF state. Hence, we can conclude that the meminductor is non-volatile in nature.

Non-volatile behavior of proposed meminductor emulator for a incremental, and b decremental topology of input pulse signal with an amplitude of 500 mV and pulse width as 100 ns for a period of 250 ns shows the meminductance varies during the ON time of the input pulse signal and remains constant during the off time

4.1 Process variation

When the design methodology of monolithic integration is followed, then the process variation is an important design aspect that needs to take care of. The proposed grounded meminductor emulator is analyzed for the different process variation such as SS (Slow N and Slow P transistors), SF (Slow N and Fast P transistors), NN (Nominal N and Nominal P transistors), FS (Fast N and slow P transistors) and FF (Fast N and Fast P transistors). The process variation is done at 500 kHz for the values of C1 = 30 pF and C2 = 40 pF, as shown in Fig. 6. It’s clear from Fig. 6 that the flow of current for FF mode is larger than in SS mode, which is expected for the proposed emulator.

4.2 Capacitor variation

The proposed meminductor emulator is analyzed for a different capacitor (40 pF, 45 pF, 50 pF, 60 pF), and the effect on the pinched hysteresis loop for variation of the capacitor is shown in Fig. 7, which shows a current decrease as an increase in the value of the capacitor. It concludes that the hysteresis loop shrinks with an increase in the capacitor.

4.3 Voltage variation

In this meminductor emulator, the bias voltage of active analog block OTA is varying (50 mV, 100 mV, 200 mV, 300 mV) with fixed values of the capacitors C1 = 60 pF, C2 = 70 pF, and the results are shown in Fig. 8. The results show that when bias voltage increased, then the flow of current in the meminductor is also increased. This provides adjustability in different process corners.

4.4 Frequency variation

In this case, the emulator input bias voltage is fixed, and the frequency varying (200 kHz, 300 kHz, 400 kHz, and 500 kHz) and the results are shown in Fig. 9 that shows the area of the hysteresis loop decreased as increased the value of frequency. Figure 10 showed the hysteresis loop variation for simultaneously varying the values of capacitor and frequency. This shows that the area under the hysteresis loop shrinks at the frequency increase and capacitor decreases.

4.5 Temperature variation

The temperature variation is one of the factors that affect the threshold voltage, saturation velocity, and carrier mobility of integrated circuits (ICs) that affect the transistor drain current [23]. The proposed meminductor emulator is implemented by using CMOS-based VDTA and OTA structures. Therefore the temperature effect is necessary to analyze for the proposed meminductor’s responses. The simulation results at various temperatures (−40 °C, 20 °C, 0 °C, 20 °C, 40 °C) are shown in Fig. 11. It concludes that the temperature effect is negligible that shows the robustness of the proposed emulator.

4.6 Application of proposed meminductor emulator

In this section, the performance of the proposed grounded meminductor emulator is verified by the implementation of a second-order bandpass filter (BPF). The second-order passive RLC based BPF is compared with a meminductor emulator-based second-order BPF if we replaced passive inductance (L) with meminductor (MEM-L). The circuit diagram of RLC and RMC based second-order BPF is shown in Fig. 12. The transfer function H(s), cut-off frequency (\({\rm{f}}_{0}\) and quality factor (Q) of the filter are given as

The values chosen for simulation are R = 10 GΩ, C = 200 pF, and L = 15 nH for the center frequency of 91.88 MHz and unity quality factor, respectively. The frequency response of both the RLC and RMC based filter is shown in Fig. 13a and b respectively. It is clear from Fig. 13a and b that the theoretical center frequency is 91.88 MHz, while the simulated frequency for the values of the same components is 92.00 MHz. The error is due to the non-ideality of the components. This shows that the proposed meminductor emulator works very well.

5 Comparision

The performance of the proposed meminductor emulator circuit with previously available literature is given in Table 2 in terms of the number of passive and active components, operation mode (grounded or floating), and the operating frequency. It can conclude that the operating frequency range of the proposed emulator is higher than the previous existing meminductor emulator, and it has a fewer number of transistors used.

Table 2 concludes the specialty of the proposed meminductor model in terms of the higher frequency with a minimum number of components. The proposed model has only one VDTA, one OTA, and two grounded capacitors, which is less as compared to the previous one. The literature also reveals that the meminductor model [21, 22] requires a memristor, and hence the frequency of operation depends on the memristor operating range as well. Hence the proposed meminductor emulator implement using one VDTA as well as OTA which, uses a transconductance term to vary the time-dependent inductance makes the emulator suitable for higher frequency.

6 Conclusions

In this article, a new electronically tunable grounded meminductor emulator using one VDTA, one OTA, and two capacitors has presented. The advantages of the proposed meminductor are the following: (i) resistor less structure, (ii) higher operating frequency range, (iii) electronic tunability by a bias voltage, (iv) use of grounded capacitors which are suitable for monolithic IC fabrication, and (v) less number of transistor counts. An application of the proposed emulator as a BPF is also given. The Cadence Virtuoso simulation results agree well with the theory.

References

Chua, L.O.: Memristor-the missing circuit element. IEEE. Trans. Circuit Theory 18(5), 507–519 (1971)

Strukov, D.B., Stewart, G.S., Williams, R.S.: The missing memristor found. Nat. Lett. 453, 80–83 (2008)

Di, M., Ventra, Y., Pershin, V., Chua, L.O.: Circuit elements with memory: memristors, memcapacitors, and meminductors. Proc. IEEE 97(10), 1717–1724 (2009)

X. Wang, and Y. Chen, Spintronic memristor device and application. In: Proc. of Design, Automation, and Text in Europe Conference and Exhibition, pp. 667–674, (2010)

Valov, I., Kozicki, M.: Organic memristors come of age. Nat. Mater. 16, 1170–1172 (2017)

Chanthbouala, A., Garcia, V., Cherifi, R.O., Bouzehouane, K., Fusil, S., Moya, X., Xavier, S., Yamada, H., Deranlot, C., Mathur, N.D., Bibes, M., Barthelemy, A., Grollier, J.: A ferroelectric Memristor. Nat. Mater. 11, 86–864 (2012)

Elwakil, A.S., Fouda, M.E., Radwan, A.G.: A simple model of double loop hysteresis behavior in memristive elements. IEEE Trans. Circuits Syst. II 60(8), 487–491 (2013)

Z. H. Hu, Y. X. Li, L. Jia, and J. B. Yu, Chaotic oscillator based on current-controlled meminductor. In Proc. IEEE ICCCAS, pp. 820–823, (2010)

Sung, H., Chang, T., Ebong, I., Bhadviya, B.B., Mazumder, P., Wei, L.: Nanoscale memristor device as synapse in neuromorphic systems. Nano. Lett. 10(4), 1297–1301 (2010)

Driscoll, T., Quinn, J., Klein, S., Kim, H.T., Kim, B.J., Pershin, Y.V., Di Ventra, M., Basov, D.N.: Memristive adaptive filters. Appl. Phys. Lett. 97(9), 093502-1092502–3 (2010)

Pershin, Y.V., Di Ventra, M.: Neuromorphic, digital and quantum computation with memory circuit elements. Proc. IEEE 100(6), 2071–2080 (2012)

Yesil, A., Babacan, Y., Kacar, F.: Design and experimental evolution of memristor with only one VDTA and one capacitor. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 99, 1–9 (2018)

Shin, S., Kim, K., Kang, S.M.: Memristor applications for programmable analog ICs. IEEE Trans. Nanotechnol. 10(2), 266–274 (2010)

Wang, F.Z., et al.: Adaptive neuromorphic architecture (ANA). Neural Netw. 45, 111–116 (2013)

Feali, M.S., Ahmadi, A., Hayati, M.: Implementation of adaptive neuron based on memristor and memcapacitor emulators. Neurocomputing 309, 157–167 (2018)

Almurib, H.A.F., Kumar, T.N., Lombardi, F.: Design and evaluation of a memristor-based look-up table for non-volatile field-programmable gate arrays. IET Circuits, Devices Syst. 10(4), 292–300 (2016)

A. Bhola and G. Kanitkar. Memristors and crossbar latches. In: ICWET 2010 -International Conference and Workshop on Emerging Trends in Technology 2010, Conference Proceedings, no. Icwet, pp. 915–918, 2010.

Liang, Y., Chen, H., Yu, D.S.: A practical implementation of a floating memristor-less meminductor emulator. IEEE Trans. Circuits Syst.-II: Express Briefs 61(5), 299–303 (2014)

Sah, M.P., Budhathoki, R.K., Yang, C., Kim, H.: Charge controlled meminductor emulator. J. Semicond Technol. Sci. 14(6), 750–754 (2014)

Biolek, D., Biolek, Z., Biolkova, V.: PSPICE modeling of meminductor. Analog Integr. Circ. Sig. Process 66, 129–137 (2011)

Pershin, Y.V., Di Ventra, M.: Memristive circuits simulate memcapacitors and meminductors. Electron. Lett. 46(7), 517518 (2010)

Pershin, Y.V., Di Ventra, M.: Emulation of floating memcapacitors and meminductors using current conveyors. Electron. Lett. 47(4), 243244 (2011)

R. Kumar, and V. Kursun. Impact of temperature fluctuations on circuit characteristics in 180nm and 65nm CMOS technologies. In: IEEE International Symposium on Circuits and Systems, pp. 1–5, 2006.

Vista, J., Ranjan, A.: High-frequency meminductor emulator employing VDTA and its application. IEEE Trans. Comput. Des. Integr. Circuits Syst. 39(10), 2020–2028 (2020). https://doi.org/10.1109/TCAD.2019.2950376

Konal, M., Kacar, F.: Electrically tunable meminductor based on OTA. Int. J. Electron. Commun. (AEU) 126, 153391–153391 (2020)

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Kumar, K., Nagar, B.C. New tunable resistorless grounded meminductor emulator. J Comput Electron 20, 1452–1460 (2021). https://doi.org/10.1007/s10825-021-01697-5

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-021-01697-5