Abstract

A simple and robust design for CMOS realization of a tunable grounded meminductor using three operational transconductance amplifier (OTA) and two capacitors have been proposed. Both theoretical analyses and simulation using Cadence Virtuoso at 0.18 \(\upmu {m}\) CMOS technology parameters verify the validity of the meminductor. Its meminductance can be tuned with the help of external bias voltage and has an operating frequency of 10 MHz, which makes it suitable for high-frequency applications. The proposed meminductor can also be configured using both incremental and decremental mode by interchanging the pin of OTA. Various parameters variability analysis like process variation, capacitor variation, voltage variation, temperature variation, and frequency variation has been carried out and our proposed meminductor has shown excellent performance.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

According to the circuit theory, there are three fundamental two-terminal circuit element, defined with the relationship of current-voltage, charge-voltage, and flux-current. The relationship between current (I) and voltage (v) defines resistor, the relationship between charge (q) and voltage (v) defines capacitor, and the relationship between flux (\(\phi \)) and current (I) defines inductor. The fourth missing fundamental two-terminal circuit element is characterized by the relation between flux (\(\phi \)) and charge (q), known as the memristor.

In 1971 L. O. Chua [1] reported the fourth missing circuit element memristor, which means memory depending upon past history (memory + resistor) and the physical relationship between \(\phi \) and q is not a necessary condition. Memristor is characterized by a relation g (\(\phi \), q) = 0. It provides a missing link between flux and charge. Maxwell’s equation explain the non-linear characterization of memristor, charge \(q(t)=\int _{-\infty }^{t}i(t)dt\) and flux \(\phi {(t)}=\int _{-\infty }^{t}v(t)dt\). Memristor has peculiar properties, then resistor, inductor, or capacitor which cannot be realized using RLC networks. Somehow memristor behaves as a non-linear resistor with memory. At high frequency, the memristor behaves as a linear resistor.

The two new memory elements that are generalized by the memristor are memcapacitor and meminductor [2]. Both have the storage capacity of energy in the form of capacitance and inductance, respectively. Recently in analog memory, these circuits have many applications as adaptive filters [3], neuromorphic circuit [4], low power computation [5], and programmable analog circuits [6, 8]. Hewlett Packard designed a thin-film \(TiO_{2}\) [8] based memristor, but it had a disadvantage of complexity in design. The complexity of design in Hewlett Packard led the analog designer to use various active blocks for the modeling of the memristor [9]- [11]. But, there are no standard models of memristor that can be followed for designing memristor. Recently it has been generated with VDTA (Voltage Difference Transconductance Amplifier) and OTA (Operational Transconductance Amplifier). In this, memristance swing can be controlled by changing the current of the OTA. Later, a flux controlled memristor using Operational Transconductance become new analog emulator circuit. Meminductor is a new special class of memory element realized by connecting memristors with the mutator circuit. This phenomenon is similar to a memristor emulator that converts the mutator into a non-linear characteristic of a memristor [12, 13]. Mutator based meminductor [14] does not apply to all memristors. However, the researcher designed a meminductor using commercially available ICs [15]; but, this type of meminductor has a large number of passive components and less operating frequency. Therefore, in this paper meminductor with three active element (OTA) and only two capacitor has been proposed. This paper is organized as follows: Sect. 2 incorporates the circuit description of proposed OTA based tunable meminductor, along with the mathematical derivation for investigation. Simulation parameters and results are elaborated in Sect. 3. Parameters variability analysis has ben done in Sect. 4. Finally, Sect. 5 draws important conclusions from present investigation.

2 Circuit description

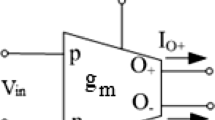

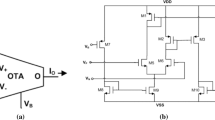

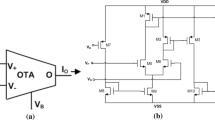

The Operational Transconductance Amplifier (OTA) has high input impedance as well as high output impedance. The circuits symbol of OTA is shown in Fig. 1a and CMOS realization of OTA is shown in Fig. 1b.

The characteristics of an OTA is expressed as

where \(V_{in} = V_{+}-V_{-}\) , called as differential input, \(G_{m}\) is the transconductance of an OTA [16]. The transconductance of an OTA is expressed as

where \(\mu \), \(C_{ox}\), W, L, and \(V_{th}\) are mobility of carrier, capacitance per unit area, channel width, channel length, and threshold voltage of MOSFET respectively. The CMOS realisation of the proposed grounded meminductor emulator is shown in Fig. 2

The mathematical analysis of the proposed meminductor emulator can be done in following ways using design shown in Fig. 2

where \(\rho (t) = \int {\phi (t)dt}\). Further, calculations are;

Thus, the relation between \(I_{in}\) and \(\phi (t)\) has been obtained in Eq. (17). Here, the positive sign indicate the incremental operation and negative sign indicate the decremental operation. Hence, the proposed tunable CMOS realization of OTA can operate in both incremental and decremental operation by interchanging the terminal of third OTA between \(V_{+}\) and \(V_{-}\).

3 Simulation parameters and results

Simulation of OTA based grounded tunable meminductor realization with CMOS using Cadence Virtuoso Tool, at gdpk 0.18 \(\upmu {m}\) technology having aspect ratio as given in Table (1) justify the above theoretical explanation. In simulation a supply voltage of \(V_{DD} = -V_{SS} = 1.2\) V with a tuned voltage of \(V_{B1} = V_{B2} = 0.1\) V. Layout of the proposed OTA based grounded meminductor is shown in Fig. 3, transient response are shown in Fig. 4a, b, whereas hysteresis plot is shown in Fig. 4c. These responses were carried out for input supply voltage having magnitude 500 mV at frequency 10 MHz. The value of capacitor \(C_{1} = 1\) pF and \(C_{2} = 2\) pF. The input voltage and flux have a \(90^\circ \) phase shift.

As non-volatile nature is an important characteristic of the memristor family, the proposed meminductor is examined for non-volatile nature in Fig. 5 by considering the input pulse amplitude of 500 mV at a pulse width of 100 ns for the period of 250 ns. The external bias voltage is 500 mV, \(C_{1} = 90\) pF, and \(C_{2} = 1\) pF. In Fig. 5a, b input voltage and meminductance is plotted with respect to time and shows that proposed grounded meminductor is non-volatile in nature as the flux and current varies during on time and it remains constant during off state.

4 Parameters variability analysis

4.1 Process variation

Process variation for different process model like SS, SF, NN, FS, and FF has been examined for the proposed grounded tunable meminductor. The current flow in FF model is larger than SS model along with area variation in hysteresis loop for 500 KHz at \(C_{1} = 30\) pF and \(C_{2} = 40\) pF as shown in Fig. 6. It also exhibits pinched hysteresis loop in all the process variation.

4.2 Capacitor variation

Effect on \(V_{\phi }-I\) hysteresis loop for \(C\in \left\{ 40, 45, 50, 60\right\} \) pF at fixed value of frequency 500 KHz, fixed bias voltage \(V_{B1} = V_{B2} = 0.1\) V, and amplitude of input signal 1 V has been shown in Fig. 7. It shows that the magnitude of current increases through the meminductor by moving to the lower value of capacitances, which validates the Eqs. (17) as this equation says that current through meminductor is inversely proportional to the capacitance.

4.3 Voltage variation

Equation (17) of the proposed meminductor shows that current of meminductor is directly proportional to transconductance \(G_{m1}\) and \(G_{m2}\). This \(G_{m1}\) and \(G_{m2}\) are directly proportional to external bias voltage \(V_{B1}\) and \(V_{B2}\) as per Eq. (2). So, according to these equation meminductance should increase with increase of external voltage and same characteristic is shown by the proposed meminductor in Fig. 8. The simulation is carried for external bias voltage \(V_{B2}\in \left\{ 25, 50, 75, 100\right\} \) mV at frequency 500 KHz, \(C_{1} = 30\) pF, and \(C_{2} = 40\) pF. It concludes that meminductance can be tuned by external bias voltage.

4.4 Temperature variation

In CMOS circuit temperature has a large impact on the carrier mobility, threshold voltage, and velocity saturation [17], which further affect the drain current and performance of the circuit.The effect of temperature on the hysteresis loop is shown in the Fig. 9. for \(T\in \left\{ -40^\circ , -20^\circ , 0^\circ , 20^\circ , 40^\circ \right\} \) C at frequency 500 KHz, \(C_{1} = 30\) pF, \(C_{2} = 40\) pF, \(V_{B1} = V_{B2} = 0.1\) V and amplitude of input signal 1 V. The proposed meminductor shows robust performance with the change of temperature.

4.5 Frequency variation

In the proposed meminductor frequency variation of \(f\in \left\{ 400, 500, 600\right\} \) KHz at \(C_{1} = 30\) pF, \(C_{2} = 40\) pF, \(V_{B1} = V_{B2} = 0.1\) V and amplitude of input signal 1 V is shown in Fig. 10. According to this meminductance decreases with increase of frequency. But, this issue has been resolved by proper selection of capacitance value of \(C_{1}\) and \(C_{2}\) as shown in Fig. 11 where at \(C_{1} = 1\) pF and \(C_{2} = 2\) pF the proposed meminductor give good performance even at \(f = 10\) MHz.

4.6 Comparison

The proposed tunable meminductor has been compared with existing meminductor in terms of number of active components like VDTA, OTA, etc., number of passive components like resistor, capacitor, inductor, etc., modes in which these are operating, and their operating frequency. The comparison are shown in Table 2. Thus, from this comparison we conclude that the proposed tunable meminductor has less number of passive components which reduces the power consumption of the circuit. The current in the pinched hysteresis loop of our proposed grounded meminductor circuit ranges from 600 to \(-600~\upmu \)A in comparison 20 to \(-20~\upmu \)A in circuit design reported by Vista and Ranjan (2020) [22]. At the same time capacitor used in our design is 1 pF and 2 pF, whereas Vista and Ranjan (2020) used 50 pF and 85 pF, therefore in the proposed circuit design delay will be less and will also require less area in layout design. The average power dissipation in proposed circuit is \(120~\upmu \)W, whereas circuit reported by Vista and Ranjan has \(200~\upmu \)W average power dissipation. Finally, the operating frequency of 10 MHz for proposed tunable meminductor is highest among all the reported work in Table 2, which makes it more suitable for high-frequency applications. Further, it can also be tuned to desired frequency by proper selection of capacitor.

5 Conclusion

Memristor emulators have gained attention nowadays because of its unique features, so it becomes essential to develop a memristor-based circuit and system design. We have proposed a simple and robust design for CMOS realization of a tunable grounded meminductor using three OTA and two capacitors. Meminductor has grounded passive elements, which make it more suitable for making it fully monolithic. The proposed meminductor exhibits excellent performance in comparison to existing emulators. Both theoretical analyses and simulation using commercially available tool Cadence Virtuoso at 0.18 \(\upmu {m}\) CMOS technology parameters verify the validity of the meminductor. Various parameters variability analysis like process variation, capacitor variation, voltage variation, temperature variation, and frequency variation has been carried out, and our proposed meminductor has shown excellent performance. For a better analysis of performance, the proposed meminductor has been compared with the existing emulators and has shown better performance than existing. Its operating frequency of 10 MHz makes it suitable for high-frequency applications.

References

Chua, L. (1971). Memristor-The missing circuit element. IEEE Transactions on Circuit Theory, 18(5), 507–519. https://doi.org/10.1109/TCT.1971.1083337.

Ventra, M. Di, Pershin, Y. V., & Chua, L. O. (2009). Circuit elements with memory: Memristors, memcapacitors and meminductors. Proceedings of the IEEE, 97(10), 1717–1724. https://doi.org/10.1109/JPROC.2009.2021077.

Driscoll, T., Quinn, J., Klein, S., Kim, H. T., Kim, B. J., Pershin, Y. V., et al. (2010). Memristive adaptive filters. Applied Physics Letters, 97(9), 093502. https://doi.org/10.1063/1.3485060.

Sung, H., Chang, T., Ebong, I., Bhavitavya, B. B., Mazumder, P., & Lu, W. (2010). Nanoscale memristor device as synapse in neuromorphic systems. Nano Letters, 10(4), 1297–1301. https://doi.org/10.1021/nl904092h.

Hu, Z. H., Li, Y. X., Jia, L., & Yu, J. B. (2010). Chaotic oscillator based on current-controlled meminductor. In Proceedings of IEEE ICCCAS, pp. 820-823. https://doi.org/10.1109/ICCCAS.2010.5581866.

Yesil, A., Babacan, Y., & Kacar, F. (2018). Design and experimental evolution of memristor with only one VDTA and one capacitor. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 38(6), 1123–1132. https://doi.org/10.1109/TCAD.2018.2834399.

Shin, S., Kim, K., & Kang, S. M. (2010). Memristor applications for programmable analog ICs. IEEE Transactions on Nanotechnology, 10(2), 266–274. https://doi.org/10.1109/TNANO.2009.2038610.

Strukov, D. B., Stewart, G. S., & Williams, R. S. (2008). The missing memristor found. Nature Letters, 453, 80–83. https://doi.org/10.1038/nature06932.

Sozen, H., & Cam, U. (2016). Electronically tunable memristor emulator circuit. Analog Integrated Circuits Signal Process, 89(3), 655–663. https://doi.org/10.1007/s10470-016-0785-2.

Sanchez- Lopez, S., Mendoza-Lopez, J., Aguilar, M. A., & Montero, C. M. (2014). A floating analog memristor emulator circuit. IEEE Transactions on Circuits and Systems II: Express Briefs, 61(5), 309–313. https://doi.org/10.1109/TCSII.2014.2312806.

Vista, J., & Ranjan, A. (2019). Simple floating MOS memristor for high frequency application. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 27(5), 1186–1195. https://doi.org/10.1109/TVLSI.2018.2890591.

Biolek, D., Bajer, J., Biolkova, V., Kolka, Z. (2011). Mutators for transforming non-linear resistor into memristor. In 20th European Conference on Circuit Theory and Design (ECCTD), pp. 488-491. https://doi.org/10.1109/ECCTD.2011.6043393.

Fitch, A. L., Iu, H. H. C., Wang, X. Y., Sreeram, V., Qi, W. G. (2012). Realization of an analog model of memristor based on lightdependent resistor. In IEEE international symposium on circuits and systems, pp. 1139–1142. https://doi.org/10.1109/ISCAS.2012.6271433.

Pershin, Y. V., & Di Ventra, M. (2011). Emulation of floating memcapacitors and meminductors using current conveyors. Electronics Letters, 47(4), 243–244. https://doi.org/10.1049/el.2010.7328.

Liang, Y., Yu, D. S., & Chen, H. (2013). A novel meminductor emulator based on analog circuits. Acta Physica Sinica, 62(15), 158501. https://doi.org/10.7498/aps.62.158501.

Kanyal, G., Kumar, P., Paul, S. K., & Kumar, A. (2018). OTA based high frequency tunable resistorless grounded and floating memristor emulators. AEU-International Journal of Electronics and Communications, 92, 124–145. https://doi.org/10.1016/j.aeue.2018.05.027.

Kumar, R., Kursun, V. (2006). Impact of temperature fluctuations on circuit characteristics in 180nm and 65nm CMOS technologies. In IEEE international symposium on circuits and systems, pp. 1–5. https://doi.org/10.1109/ISCAS.2006.1693470.

Biolek, D., Biolek, Z., & Biolkova, V. (2011). PSPICE modelling of meminductor. Analog Integrated Circuits and Signal Processing, 66, 129–137. https://doi.org/10.1007/s10470-010-9505-5.

Pershin, Y. V., & Di Ventra, M. (2010). Memristive circuits simulate memcapacitors and meminductors. Electronics Letters, 46(7), 517–518. https://doi.org/10.1049/el.2010.2830.

Liang, Y., Chen, H., & Yu, D. S. (2014). A practical implementation of a floating memristor-less meminductor emulator. IEEE Transactions on Circuits and Systems-II: Express Briefs, 61(5), 299–303. https://doi.org/10.1109/TCSII.2014.2312807.

Sah, M. P., Budhathoki, R. K., Yang, C., & Kim, H. (2014). Charge controlled meminductor emulator. Journal of Semiconductor Technology And science, 14(6), 750–754. https://doi.org/10.5573/JSTS.2014.14.6.750.

Vista, J., & Ranjan, A. (2020). High frequency meminductor emulator employing VDTA and its application. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 39(10), 2020–2028. https://doi.org/10.1109/TCAD.2019.2950376.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Raj, A., Kumar, K. & Kumar, P. CMOS realization of OTA based tunable grounded meminductor. Analog Integr Circ Sig Process 107, 475–482 (2021). https://doi.org/10.1007/s10470-021-01808-z

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-021-01808-z