Abstract

The paper discusses in detail the inability of a circuit designer to design a single input single element-controlled universal memelement emulator. A Single input Single element-controlled universal memelement emulator would be such a configuration that can provide the realization of any of the three memelements (Memristor/Memcapacitor/Meminductor) by taking a circuit element as inductor (L), Capacitor (C) or Resistor (R) with the same input port. The analysis shows that no such circuit configuration can be built to realize such a highly flexible universal memelement emulator. It is found that by using such structures, only two ideal memelements can be realized at maximum. If these circuit structures are used to realize the remaining third memelement, then, the resulting element comes out to be a non-ideal memelement. Two circuit configurations to demonstrate this theory are also included for both charge-controlled and flux-controlled memelement emulation based on the approaches shown in this paper.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

The emulation circuits for memelements are attracting interest due to their use in nonlinear circuit memristive applications [4, 14, 20, 31]. As compared to the other two memelements, the memristor realization has been a well-established domain since the last decade. From the use of Op-Amp (Operational Amplifier) to the employment of OTAs (Operational Transconductance Amplifiers), the memristor emulators have been built using several kinds of active elements so far [1, 3, 5, 12, 15, 19, 21, 22, 27, 32]. Also, some other kinds of circuit structures based on diode-bridge networks have been reported to emulate the memristor characteristics [13, 30]. Unlike the memristor which became popular, other memelements, memcapacitor and meminductor, are not well studied. There are some circuit implementations of these memelement emulators, which are reported in [2, 10, 17, 23,24,25,26, 28, 34, 35].

Apart from the memelement emulators that can realize only single memelement functions [1,2,3, 5, 10, 12, 13, 15, 17, 19, 21,22,23,24,25,26,27,28, 30, 32, 34, 35], the multi-(universal/dual) memelement emulators are also gaining importance among circuit theorists [6, 7, 9, 11, 29, 33, 36]. The aim of a circuit designer always remains the emulation of maximum numbers memelement functions using a single circuit configuration based on a minimum number of circuit resources possible. And also, flexibility is a very desirable feature (freedom to have all the desired emulated memelement functions by executing the least number of changes in the circuit). The universal memelement emulators present in the existing literature [33, 36] cannot be considered easily reconfigurable, as they require multiple changes in the circuit design to switch from one memelement function to another. However, it can be proven by simple circuit logic that the realization of such a highly flexible (which requires only a single change keeping the same input port) universal emulator is not a possibility. Only two of the three memelements can be realized at most keeping the same architecture (resulting in a very flexible dual memelement emulator), the realization of the third memelement requires a lot of alterations in the design of the circuit. In the existing literature, some dual memelement emulation circuits are available [6, 7, 9, 11, 29]. It is observed in these emulators that maintaining the same circuit design (except the change of one passive element) realization of only two memelements is possible; however, the third element comes out to be a non-ideal capacitor or inductor. The work first discusses the two approaches that can be followed to obtain the simplest design of a single input single element-controlled flux/charge dependent multi-memelement emulator. Then, the limitation of these circuit concepts is discussed in the realization of a single input single element-controlled universal memelement emulator. Further, validation of this argument is demonstrated through the OTA-CCII-based circuit structures following the discussed concepts.

2 Single Input Single Element-Controlled Multi-Memelement Emulators and Their Inability to Realize all Three Memelements

The use of linear functions of flux/charge/TIF (Time integral of Flux)/TIQ (Time integral of Charge) has been common among circuit designers to realize the corresponding memelement emulators. In almost every memelement emulators given previously [1,2,3, 5,6,7, 9,10,11,12,13, 15, 17, 19, 21,22,23,24,25,26,27,28,29,30, 32,33,34,35,36], the realizing memelement functions exhibit linear dependency on the time integral of the applied current/voltage/charge/flux signal, which has a relation in the time-domain as follows:

where x(t) and y(t) represent the corresponding basic quantities of the memelements (which are voltage (vin) and current (iin) in the case of a memristor).

From Eq. (1), the memelement function becomes; \(G_{{\text{M/memcap/memind}}} = \left( {a + b\int_{0}^{t} {x\left( k \right){\text{d}}k} } \right)\), where a and b may be the coefficients depending upon the realization schemes.

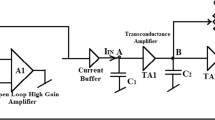

Figure 1 shows possibly the simplest circuit structure to realize a voltage-controlled multi-memelement emulator with external multiplier-less architecture. This concept is based on a transconductance (with gain g) and a transadmittance amplifier (with a transfer function Zk (s)) with two grounded passive elements. The second block (transadmittance amplifier) can be a type of filtering circuit, having a transfer function, Zk that can be tuned to be; transconductive (g), transinductive (\(sg^{\prime\prime}\)) or transcapacitive \(\left( {\frac{{g^{\prime}}}{s}} \right)\).

Upon applying basic circuit principles, the i–v relation of the above-depicted circuit idea (in Fig. 1) is revealed as follows:

The first term between the brackets denotes the transconductance of the first amplifier, biased by the voltage across C1. The transient plot for Eq. (2) between Iin (k) and Vin (k) for the sinusoidal signal application is shown in Fig. 2.

By observing Figs. 1 and 2 and using Eq. (1), it can be deduced that by selecting the gain of the transadmittance amplifier as (g) and \(\left( {\frac{{g^{\prime}}}{s}} \right)\), the realization of memristor and meminductor can be achieved, respectively. If we select this amplifier gain as \(sg^{\prime\prime}\) (transinductive), we can achieve the following kind of i–v relation:

Therefore, in this case, Eq. (1) cannot realize the ideal memcapacitor function. Due to this, it can be concluded that no such circuit configuration can be designed, which can be used to realize all three voltage-controlled memelement functions by executing only a single change and maintaining the same input connections. Some existing universal emulators provide the realization of the three popular memelements, but they require the employment of three or more passive and active components (like those reported in [6, 7, 9, 11, 29]) and need multiple changes.

On comparing with the conventional capacitive relationship (i = cdv/dt), we can understand that Eq. (3) is representing the time-domain relationship of a nonlinear voltage-controlled capacitor.

Now, Fig. 3 depicts a simple realization concept that is single input single element-controlled architecture. However, it can be proved using similar logic that it cannot be used to realize all three memelements.

For this circuit configuration, the i-v relation is found as follows:

Equation (4) suggests that selecting the impedance Z as R results in the realization of a memristor and taking it as the capacitance C provides the emulation of memcapacitor. Interestingly, the selection of the impedance Z as an inductor L does not provide the function of meminductor rather it realizes only the nonlinear inductor (current controlled).

Therefore, using the basic circuit structure of Fig. 3, we can only realize the current-controlled memristor and memcapacitor and hoping for the realization of a meminductor, the third element comes out to be a non-ideal inductor. So, even for the current-controlled elements, all three types of memelement functions cannot be realized employing such single input single element structures. At most, these compact architectures can only be used to realize two memelement functions. Nevertheless, the possibility can be explored to design such a true universal memelement emulator by using a very versatile block with several input/output ports (resulting in complex internal structures based on a large number of transistors). The realization of such a block and its use in the designing of a universal memelement emulator can be investigated in the future.

The discussed arguments in this section have been validated by implementing the above-mentioned circuit concepts (in Figs. 1 and 3) by using OTA and CCII-based configurations.

3 Implementations of the Multi-Memelement Emulators Using OTA and CCII

The employed OTA has a single current output (IO) related to its voltage inputs by the relationship:

Here, gm denotes the transconductance of OTA given by \({g}_{\mathrm{m}}=k({V}_{\mathrm{B}}-{V}_{\mathrm{SS}}-{V}_{\mathrm{t}})\), in which bias voltage is VB, and VSS is the power supply value, Vt is the transistors’ threshold voltage value depending upon the technology, and k is the process parameter.

And the CCII is chosen with dual current outputs with port relationships given as follows:

3.1 Flux-Controlled Single Input Single Element-Controlled Multi-Memelement Emulator

The designed proposed circuit configuration of the designed Flux-dependent multi-memelement emulator is depicted in Fig. 4. The circuit comprises one OTA along with CCII and three passive elements in the grounded state.

Flux-controlled multi-memelement emulator using OTA and CCII [8]

At the X port of the CCII, the connected impedance Z can be selected as: Resistor (R), Capacitor (C), and inductor (L), for the realization of the different element functions. It can be noticed from Fig. 4 that \(I_{Z + } = I_{X} = \frac{{V_{X} }}{Z},I_{Z - } = - I_{X} = - V_{X} /Z\), where ZX is the impedance present at the X terminal of the CCII. It suggests that 1/Z is acting like a transadmittance from port X to port Z. It is equivalent to the transadmittance amplifier, and the second stage of the circuit idea is depicted in Fig. 1.

By using Eqs. (5) and (6), the current Iin can be evaluated as follows:

3.1.1 Case 1: Replacing Impedance Z with Resistance R 1

On putting Z = R1, Eq. (7) is modified as follows:

By using Eq. (8), it is clear that after connecting R1, the circuit depicted in Fig. 4 emulates the behavior of a Flux-dependent memristor with memristance GM equals to:

The PSPICE simulations are performed to test the working of this circuit as a memristor emulator. The employed CMOS implementations of the used CCII and OTA are taken from the works reported in [16, 18]. The emulated memristor (realized using Eq. 8) using the designed emulator is simulated by selecting R1 = 8 K, C1 = 0.036 nF, and R = 5 K. Figure 5 demonstrates the memristor PHL curves for three operating frequencies, and it plotted between transient input voltage and current. According to the well-known memristor fingerprints, the memristor i–v contour should intersect itself at the origin, and its enclosed area should diminish upon raising the operating frequency of the applied signal.

3.1.2 Case 2: Replacing Impedance Z by Inductor L 1

On putting Z = sL, Eq. (7) can be written as follows:

Equation (10) suggests the realization of a flux-controlled meminductor if an inductor is connected at the X port of the CCII. The realized inverse meminductance LM−1 can be found as follows:

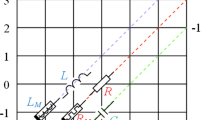

To simulate the emulated meminductor, the simulation parameters are selected as: R = 2 K, C = 0.075 nF, and L1 = 0.01 mH. The simulation results illustrated in Fig. 6 exhibit the ϕ–i (flux-current) plots of the emulated flux-controlled meminductor traced at three frequencies.

3.1.3 Case 3: Replacing Impedance Z with Capacitor C 1

In this case, the Eq. (7) should be written as follows:

On comparing Eq. (12) with the commonly used capacitive current relation Iin = Cdv/dt, the emulated nonlinear capacitance CM by the circuit depicted in Fig. 4 is found as follows:

Similarly, the realized nonlinear capacitance is tested by applying a sinusoidal signal with amplitude VP = 0.01 V with operating parameters chosen as: C = 0.01 nF, C1 = 0.075 nF, and R = 5 K. Equation (13) suggests that the characteristics of this nonlinear capacitor must be traced between Iin and dv/dt. For a sinusoidal input with a voltage signal as: v = vpsin2πFint, the x-axis variation will be controlled by dv/dt = 2πFin vpsin2πFint. It clearly suggests that span of the PHL curve along the x-axis should depend upon the input signal frequency. It can also be observed in the plots demonstrated in Fig. 7. The nonlinear capacitors have also been called dual of memcapacitor.

3.2 Charge-Controlled Single Input Single Element-Controlled Memelement Emulator

The circuit described in Fig. 8 is the implementation of the circuit block diagram discussed in Fig. 3 for current-controlled multi-memelement emulators. The depicted schematic consists of two OTAs and a CCII along with three grounded passive elements.

On performing circuital analysis by using Eqs. (4) and (5), the input current Iin is obtained as follows:

In Eq. (14), the first product term is the transconductance gain of OTA1, while gm2 represents the transconductance amplifier of OTA2.

Now, on selecting the different types of impedance Z, three different cases can be studied.

3.2.1 Case 1: When Z is Selected as Resistance R

In this case, Eq. (14) can be modified as follows:

It can be deduced from Eq. (15) that by choosing Z as resistance R, the circuit of Fig. 8 realizes the function of a charge-controlled memristor.

3.2.2 Case 2: When Z is Selected as Capacitance C

For the use of the capacitance, the i–v relationship of the circuit can be computed from Eq. (14) as follows:

On comparing Eq. (16) with the standard charge-controlled capacitance equation, we can understand that Eq. (16) is realizing the function of a charge-controlled memcapacitor.

3.2.3 Case 3: When Z is Selected as Inductance L

In this case, the input i–v relationship of the designed circuit is obtained as follows:

Equation (17) suggests the realization of only a nonlinear current-controlled inductor. Therefore, selecting the impedance Z as inductance L does not provide the emulation of a charge-controlled meminductor.

Therefore, the circuit concept of Fig. 3 is unable to realize all three memelements with a single input single element-controlled structure.

4 Conclusion

The paper discusses that a single input single element-controlled Flux-dependent multi-memelement emulator provides the realization of only the ideal memristor and ideal meminductor, and the other case results in a nonlinear voltage-controlled capacitor. Similarly, in the case of the current-controlled emulator, the ideal memristor and memcapacitor are realized but the third one is obtained as a nonlinear inductor. There is no possibility to modify these circuit configurations by executing any change in the emulator circuits into a perfect universal memelement emulator without losing the various advantages of the emulator related to flexibility. Therefore, it is proved in this article that such universal memelement emulators cannot be designed whose behavior can be switched only by executing a single change in the circuit configuration.

References

M.T. Abuelmaatti, Z.J. Khalifa, A new memristor emulator and its application in digital modulation. Analog Integrated Circuits Signal Process. 80(3), 577–584 (2014). https://doi.org/10.1007/s10470-014-0364-3

Y. Babacan, An operational transconductance amplifier-based memcapacitor and meminductor. Istanb. Univ. J. Electr. Electron. Eng. 18(1), 36–38 (2018). https://doi.org/10.5152/iujeee.2018.1806

Y. Babacan, A. Yesil, F. Kacar, Memristor emulator with tunable characteristic and its experimental results. AEU Int. J. Electron. Commun. 81, 99–104 (2017). https://doi.org/10.1016/j.aeue.2017.07.012

B. Bao, Z. Ma, J. Xu, Z. Liu, Q. Xu, A simple memristor chaotic circuit with complex dynamics. Int. J. Bifurc. Chaos 21(09), 2629–2645 (2011). https://doi.org/10.1142/s0218127411029999

B.-C. Bao, J.-P. Xu, G.-H. Zhou, Z.-H. Ma, L. Zou, Chaotic memristive circuit: equivalent circuit realization and dynamical analysis. Chin. Phys. B 20(12), 120502 (2011). https://doi.org/10.1088/1674-1056/20/12/120502

K. Bhardwaj, M. Srivastava, New multiplier-less compact tunable charge-controlled memelement emulator using grounded passive elements. Circuits Syst. Signal Process. 41(5), 2429–2465 (2021). https://doi.org/10.1007/s00034-021-01895-3

K. Bhardwaj, M. Srivastava, New electronically adjustable memelement emulator for realizing the behaviour of fully-floating meminductor and memristor. Microelectron. J. 114, 1051 (2021). https://doi.org/10.1016/j.mejo.2021.105126

K. Bhardwaj, M. Srivastava, On the investigation of frequency-related fingerprints of meminductor/capacitor and their duals realized by circuit emulators. Radioengineering 31(3), 374–381 (2022). https://doi.org/10.13164/re.2022.0374

K. Bhardwaj, M. Srivastava, New grounded passive elements-based external multiplier-less memelement emulator to realize the floating meminductor and memristor. Analog Integr. Circuits Signal Process. 110(3), 409–429 (2022). https://doi.org/10.1007/s10470-021-01976-y

D. Biolek, V. Biolková, Z. Kolka, J. Dobeš, Analog emulator of genuinely floating memcapacitor with piecewise-linear constitutive relation. Circuits Syst. Signal Process. 35(1), 43–62 (2015). https://doi.org/10.1007/s00034-015-0067-8

Z.G. Çam Taşkıran, M. Sağbaş, U.E. Ayten, H. Sedef, A new universal mutator circuit for memcapacitor and meminductor elements. AEU Int. J. Electron. Commun. 119, 153180 (2020). https://doi.org/10.1016/j.aeue.2020.153180

L. Chua, Memristor—the missing circuit element. IEEE Trans. Circuit Theory 18(5), 507–519 (1971). https://doi.org/10.1109/tct.1971.1083337

F. Corinto, A. Ascoli, Memristive diode bridge with LCR filter. Electron. Lett. 48(14), 824 (2012). https://doi.org/10.1049/el.2012.1480

T. Driscoll, Y.V. Pershin, D.N. Basov, M. Di Ventra, Chaotic memristor. Appl. Phys. A 102(4), 885–889 (2011). https://doi.org/10.1007/s00339-011-6318-z

A.S. Elwakil, M.E. Fouda, A.G. Radwan, A simple model of double-loop hysteresis behavior in memristive elements. IEEE Trans. Circuits Syst. II Express Briefs 60(8), 487–491 (2013). https://doi.org/10.1109/tcsii.2013.2268376

G. Ferri, N.C. Guerrini, Low-Voltage Low-Power CMOS Current Conveyors (Kluwer Academic Publishers, Boston, 2003)

M.E. Fouda, A.G. Radwan, Charge controlled memristor-less memcapacitor emulator. Electron. Lett. 48(23), 1454 (2012). https://doi.org/10.1049/el.2012.3151

K. Kaewdang, K. Kumwachara, W. Surakampontom, Electronically tunable floating CMOS resistor using OTA, in IEEE International Symposium on Communications and Information Technology, 2005. ISCIT (2005).https://doi.org/10.1109/iscit.2005.1566957

Z. Li, Y. Zeng, M. Ma, A novel floating memristor emulator with minimal components. Act. Passiv. Electron. Compon. 2017, 1–12 (2017). https://doi.org/10.1155/2017/1609787

B. Muthuswamy, Implementing memristor based chaotic circuits. Int. J. Bifurc. Chaos 20(05), 1335–1350 (2010). https://doi.org/10.1142/s0218127410026514

R.K. Ranjan, N. Raj, N. Bhuwal, F. Khateb, Single DVCCTA based high frequency incremental/decremental memristor emulator and its application. AEU Int. J. Electron. Commun. 82, 177–190 (2017). https://doi.org/10.1016/j.aeue.2017.07.039

R.K. Ranjan, N. Rani, R. Pal, S.K. Paul, G. Kanyal, Single CCTA based high frequency floating and grounded type of incremental/decremental memristor emulator and its application. Microelectron. J. 60, 119–128 (2017). https://doi.org/10.1016/j.mejo.2016.12.004

F.J. Romero et al., Memcapacitor emulator based on the Miller effect. Int. J. Circuit Theory Appl. 47(4), 572–579 (2019). https://doi.org/10.1002/cta.2604

F.J. Romero, M. Escudero, A. Medina-Garcia, D.P. Morales, N. Rodriguez, Meminductor emulator based on a modified Antoniou’s Gyrator circuit. Electronics 9(9), 1407 (2020). https://doi.org/10.3390/electronics9091407

M.P. Sah, R.K. Budhathoki, C. Yang, H. Kim, Charge controlled meminductor emulator. JSTS J. Semicond. Technol. Sci. 14(6), 750–754 (2014). https://doi.org/10.5573/jsts.2014.14.6.750

M.P. Sah, R.K. Budhathoki, C. Yang, H. Kim, Mutator-based meminductor emulator for circuit applications. Circuits Syst. Signal Process. 33(8), 2363–2383 (2014). https://doi.org/10.1007/s00034-014-9758-9

C. Sánchez-López, L.E. Aguila-Cuapio, A 860 kHz grounded memristor emulator circuit. AEU Int. J. Electron. Commun. 73, 23–33 (2017). https://doi.org/10.1016/j.aeue.2016.12.015

F. Setoudeh, M.M. Dezhdar, A new design and implementation of the floating-type charge-controlled memcapacitor emulator. Majlesi J. Telecommun. Devices (2020).

P.K. Sharma, R.K. Ranjan, F. Khateb, M. Kumngern, Charged controlled mem-element emulator and its application in a chaotic system. IEEE Access 8, 171397–171407 (2020). https://doi.org/10.1109/access.2020.3024769

X.-Y. Wang, A.L. Fitch, H.H.C. Iu, V. Sreeram, W.-G. Qi, Implementation of an analogue model of a memristor based on a light-dependent resistor. Chin. Phys. B 21(10), 108501 (2012). https://doi.org/10.1088/1674-1056/21/10/108501

S. Wen, Yi. Shen, Z. Zeng, Y. Cai, Chaos analysis and control in a chaotic circuit with a PWL memristor. Int. Conf. Inf. Sci. Technol. (2011). https://doi.org/10.1109/icist.2011.5765147

S. Yaner, H. Kuntman, Fully CMOS memristor based chaotic circuit. Radioengineering 23, 1140–1149 (2014)

D. Yu, X. Zhao, T. Sun, H.H.C. Iu, T. Fernando, A simple floating mutator for emulating memristor, memcapacitor, and meminductor. IEEE Trans. Circuits Syst. II Express Briefs 67(7), 1334–1338 (2020). https://doi.org/10.1109/tcsii.2019.2936453

F. Yuan, Y. Li, G. Wang, G. Dou, G. Chen, Complex dynamics in a memcapacitor-based circuit. Entropy 21(2), 188 (2019). https://doi.org/10.3390/e21020188

F. Yuan, Y. Deng, Y. Li, A multistable generalized meminductor with coexisting stable pinched hysteresis loops. Int. J. Bifurc. Chaos 30(02), 2050023 (2020). https://doi.org/10.1142/s0218127420500236

Q. Zhao, C. Wang, X. Zhang, A universal emulator for memristor, memcapacitor, and meminductor and its chaotic circuit. Chaos Interdiscip. J. Nonlinear Sci. 29(1), 013141 (2019). https://doi.org/10.1063/1.5081076

Funding

Not applicable.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Bhardwaj, K., Srivastava, M. On the Boundaries of the Realization of Single Input Single Element-Controlled Universal Memelement Emulator. Circuits Syst Signal Process 42, 6355–6366 (2023). https://doi.org/10.1007/s00034-023-02420-4

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-023-02420-4