Abstract

A novel memelement emulator configuration has been reported in the presented work. This proposed configuration can be used to realize the function of a floating meminductor as well as the memristor element through proper selection of employed passive elements. The presented emulator circuit is based on MVDCC (modified VDCC) and OTA, which are CMOS implemented electronically tunable ABBs (Active Building Blocks). The designed circuit employs only two ABBs and three grounded passive elements. As per the knowledge of the authors, no such emulation configuration with a floating architecture has been reported so far, which can realize the behaviour of two mem-elements without the use of any external multiplier IC/circuitry, passive inductor or mutation through any externally employed memelement. It can be considered as a notable design feature along with its other advantages like electronically/resistively tunable emulated response and use of only grounded passive elements. Moreover, proposed circuit has been investigated for the consideration of non-idealities and different port parasitics of employed blocks. For the verification purpose, PSPICE simulation environment with CMOS 0.18 µm TSMC technology parameters, has been selected. The functioning of the realized meminductive and memristive behaviour has also been verified through the application example circuits designed using developed emulator circuit. Afterwards, the commercial IC based realization of the proposed emulator circuit has been shown and experimental results are discussed.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Among the three memelements, memristor has been considered as the fourth fundamental element by various researchers unlike to the meminductor and memcapacitor. It is due to the fact that it was proposed for the relationship of charge and flux, which are the two of the basic electrical quantities [1]. And also, the notion of other of two memelements was motivated from the concept of memristor only, which were defined to relate the associated quantities corresponding to the conventional inductor and capacitor [2]. Nevertheless, these two new memelements have also been considered to be useful just like the memristor due to the hysteresis property, they exhibit in their related transient characteristics, which gives rise to the storage ability in these elements. Some, mathematical works can be found, which focus on the theoretical aspects of memcapacitors and meminductors [3, 4].

Now, the realization of the memristor element based on electronic circuit designing (as well as through material-based implementations), has been a popular research area since the last decade (some popular memristor emulator circuits have been reported in [5,6,7,8,9,10,11,12,13,14,15,16,17,18,19,20] and the references cited there in). But there are only limited number of articles in the open literature available on the realization of meminductor and memcapacitor [21,22,23,24,25,26,27,28,29,30,31,32,33,34,35,36,37,38,39,40,41,42,43,44,45,46,47,48,49,50,51]. These papers [21,22,23,24,25,26,27,28,29,30,31,32,33,34,35,36,37,38,39,40,41,42,43,44,45,46,47,48,49,50,51] only include the analogue circuit-based implementations as the physical architecture-based realizations of these two memelements have not been proposed so far. The emulation configurations suggested in [21,22,23,24,25,26,27,28,29,30,31,32,33,34,35,36,37,38,39,40,41,42,43,44,45,46,47,48,49,50,51] are based on different active elements like; First generation current conveyor (CCI) [33,34,35,36,37,38,39,40,41], Second Generation Current Conveyor (CCII) [33, 38, 41, 48], Operational Amplifier(OA) [15, 34, 39,40,41, 43, 45, 46, 49], Operational Transconductance Amplifier (OTA) [32, 36, 37, 48], Current Buffered Transconductance Amplifier (CBTA) [35], Voltage differencing Transconductance Amplifier (VDTA) [32,33,34,35,36,37,38,39,40,41,42], Differential Voltage Current Controlled Transconductance Amplifier(DVCCTA) [29] and some others.

Most of the emulators presented in [15, 21,22,23,24,25,26,27,28,29,30,31,32,33,34,35,36,37,38,39,40,41,42,43,44,45,46,47,48,49,50,51] are dedicated to the realization of only single memelement (memcapacitor or meminductor) with grounded or floating architectures. These also include some emulators (like those are reported in [15, 21, 22, 33, 35, 41, 47, 48, 50]), which can realize the function of any two or all the three memelements just like the proposed memelement emulator circuit. These reported circuits are not preferrable as compared to the proposed memelement emulator and as these are based upon a greater number of active and passive elements also offers no provision of electronic/resistance control facility. The use of analog multiplier IC in some of these circuits [21, 35, 41, 47] make these emulators even bulkier as compared to the circuits which are based upon multiplier-IC less structure like the proposed one.

The main claim of this work is the compact floating meminductor emulator designed using MVDCC and OTA. The realizability of the memristor can be seen as an additional advantage of the proposed circuit. The comparison has been shown in Table 1, which highlights the different design and performance related aspects of the previously reported meminductor emulators only [15, 32,33,34,35,36,37,38,39,40,41,42,43,44,45,46,47,48,49,50,51] and shows the superiority of the proposed one.

Based on the various parameters compared in Table 1, the meminductors reported in [15, 32,33,34,35,36,37,38,39,40,41,42,43,44,45,46,47,48,49,50,51] are found to be suffering from one or more of the following major issues like; emulation of only grounded architecture, use of more than two ABBs, use of external multiplier IC/ICs, no facility of tuning, use of floating passive elements, exhibition of very low operating bandwidth (few KHzs), realization through mutation using external memristor emulator, use of passive inductor and requirement of matched parameter/component values. On the other end, the proposed circuit is free from such disadvantages and realizes a floating meminductor emulator using a MVDCC and an OTA with three grounded passive elements only.

Now, as far as the performance of any memelement emulator is concerned it is generally measured by the aspects like; frequency dependency of the \(\phi\)-i curves (pinched hysteresis loops (PHLs), symmetry of the PHL lobes, maximum frequency up to which satisfactory loop can be obtained, availability of electronic tuning and presence of non-volatility in the realized memelement. There are following performance related shortcomings with the previously reported meminductor emulators [15, 32,33,34,35,36,37,38,39,40,41,42,43,44,45,46,47,48,49,50,51] as compared to the proposed one:

-

1.

In some of the meminductor emulators reported previously [33,34,35, 39, 43, 45, 47, 49], there was lack of symmetry in the PHL characteristics presented, while proposed circuit offers satisfactory symmetry in both the opposite quadrants.

-

2.

The maximum operating frequency offered by some emulators [15, 33,34,35,36,37,38,39,40,41, 43,44,45,46,47, 49] is less than 100 kHz, while presented circuit provides the maximum operating frequency up to 300 kHz.

-

3.

The works discussed in [15, 33,34,35, 37,38,39,40,41, 43,44,45,46,47, 49, 50] have not investigated the non-volatility property of the realized meminductor emulator, while presented simulation results clearly validates the non-volatility of the proposed memelement emulator.

-

4.

In the meminductor emulator given in any kind of tunability feature is not present [15, 33, 35, 37,38,39,40,41,42,43, 45,46,47,48,49,50], while our circuit is tunable through biasing voltage as well as the external resistance.

-

5.

The meminductor emulators given in [33, 34, 38, 43] do not show ideal behaviour on varying the applied signal frequency. While, this frequency dependency of the proposed meminductor emulator can be clearly witnessed from the presented simulation results.

Along with these advantages offered by the realized meminductor, its ability to exhibit the ideal memristor behaviour can also be considered as an additional remarkable benefit. Although, the main contribution of the work is the proposed compact floating meminductor, but still some of the advantages of the memristor emulation configuration over some of the previously reported memristor emulators [5,6,7,8,9,10,11,12,13,14,15,16,17,18,19,20] cannot be ignored. Like the floating memristor emulators described in [5, 6, 9, 12, 14,15,16,17] use two or more active elements and/or are based upon the large number of passive elements (more than three), whereas the proposed circuit is based on just two MVDCCs and three grounded passive elements. Also, the realized memristor emulator does not require any external voltage multiplier, which can be considered as an advantage over previously reported multiplier based memristor emulators [5, 6, 10, 14, 16, 17]. Furthermore, some of those configurations, claimed as floating memristor, are not fully floating [6, 13, 14] (i.e. two terminals cannot be used interchangeably when used as a floating element), while proposed memristor emulator simulates a fully floating memristor, which is an attractive feature of floating topology. While, memristor emulators reported in [18, 19] realize only grounded memristor emulator.

In the following discussion, we have mentioned the basic relationships of voltage-controlled and flux-controlled memristor and meminductor respectively, which are the basis for the realization of these memelements.

1.1 Memristor and meminductor

It is important to understand that all the three memelements actually relate only those quantities, which are associated to their conventional counterpart. Like, the memristor, which basically links only the current/voltage to the voltage/current (just like a resistor), but its flux/charge-dependent conductance/resistance makes all the difference.

Below, the current(i)-voltage(v) relationship of voltage controlled memristor has been given in Eq. 1, with the equivalent memductance represented as GM.

The memductance GM given in Eq. 1, is generally realized by using the expression given in Eq. 2, which is the function of integration of voltage i.e. flux ϕ.

(The \(a_{0}\) and \(a_{1}\) are memristor coefficients)

Similarly, it was argued in [2] that the capacitance and inductance, whose values depend upon the integration of charge/flux, (which are the quantities associated to conventional capacitor/inductor) can be considered as memcapacitor and meminductor, if these elements also relate the basic capacitive and inductive quantities. It is important to emphasize that it is the dependency upon the integration of the electrical quantity, that provides the storage feature in these memelements. Now, the current–voltage relationship of meminductor element is represented by the following equation;

where \(\varphi\) is the flux, given by \(\varphi \left( t \right) = \int\limits_{0}^{t} {v\left( t \right){\text{d}}t}\) and LM−1 represents the inverse meminductance, which is generally taken as Eq. 4 for the circuit-based realization of meminductor emulators.

(The \(a_{0}\) and \(a_{1}\) are meminductor coefficients)

where

2 Proposed configuration

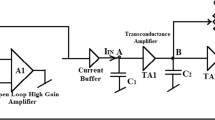

Based on the discussion presented in the previous section, we have designed the memelement emulator to realize the relationship given in Eqs. 1 and 3. The proposed realization is based on the MVDCC and OTA blocks. The MVDCC is an extension of the VDCC Voltage Differencing Current Conveyor) concept, which is explained below.

2.1 MVDCC (modified VDCC)

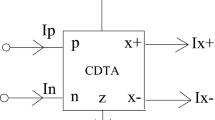

The notion of VDCC was first proposed in the seminal paper authored by Biolek et al. in 2008 [52]. Later, it was found to be applicable in several types of analog signal processing/generation circuits [53,54,55] and still remains popular among analog circuit designers. In the VDCC active element, the Z port provides the current output of input transconductance stage and developed potential at the Z terminal is transferred to the X port. The CMOS implementation of VDCC was first reported in [56]. Now, authors have realized that having a dual Z ports (with both negative and positive current output) and proportional (to this differential Z input) current at the WP and WN ports, the versatility of the VDCC can be improved. And, with these modifications in the CMOS implementation given in [56], the VDCC can be transformed into MVDCC (modified VDCC). The CMOS implementation of MVDCC and its symbolic representation can be given as Figs. 1 and 2 respectively. In [57], the application of MVDCC as a floating memristor and its CMOS implementation were first suggested. Also, the ports’ relationships of MVDCC are described in Eq. 6.

The symbol gm in Eq. 7, represents the transconductance of the input stage of MVDCC, which can be controlled by the applied bias voltage VB1 as the relationship given in Eq. 7 suggests,

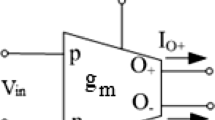

Along with VDCC, we have also used the OTA block in the realization of presented memelement emulator. The OTA is a conventional and popular active element used as a transconductance amplifier. The employed CMOS implementation of OTA is shown in Fig. 3. For OTA, the output current is IZ = gm0 (VP − VN) with gm0 being the transconductance gain, depends upon biasing voltage VB.

2.2 Proposed memelement emulator using MVDCC and OTA

Finally, the proposed circuit emulator to realize the behaviour of a floating meminductor and memristor is presented in Fig. 4. The suggested configuration is based on MVDCC and OTA and three grounded elements. The impedance Z1 present in the designed circuit can be used to select the functioning of this memelement emulator as meminductor and memristor respectively.

-

Case-1 Meminductor (When Z1 is selected as capacitance C1)

In this condition, the expression for the generated input current for the circuit given in Fig. 4 is computed as following.

For routine circuital analysis (using Eq. 6) and through application of Kirchhoff’s laws, the input currents I1 and I2 are found to be equal and opposite for the depicted circuit;

Now this Iin shown in Eq. 8, can be computed using Eqs. 6 and 7 as;

where \(\int\limits_{0}^{t} {\left( {V_{2} - V_{1} } \right){\text{d}}t}\) is the input voltage flux \(\varphi\) and \(\int\limits_{0}^{t} {\int\limits_{0}^{t} {\left( {V_{2} - V_{1} } \right){\text{d}}t{\text{d}}t} }\) is flux density \(\rho\) as explained in Eqs. 4 and 5. Also the gm0 is the transconductance of employed OTA.

From Eq. 9, it can be clearly observed that this relationship is associated to a meminductor function with the equivalent inverse meminductance can be found by comparing Eq. 9 with 3 as;

-

Case-2 Memristor (when Z1 is selected as resistance R1)

Similarly, the circuit will act as a memristor emulator, if Z1 is chosen as the resistance R1. Now, by using Eqs. 6 and 7, the admittance matrix of the memristor emulator relating the voltages V1, V2 to I1 and I2 can be evaluated as;

From Eq. 11, it can be clearly observed that the circuit presented in Fig. 4 realizes the behavior of a floating memristor with memductance GM equals to;

It can be observed from the expressions given in Eqs. 10 and 12, the behavior of the realized meminductance and memductance, can be controlled electronically by varying transconductance of employed OTA gm0, which depends upon biasing voltage VB. And most importantly, to achieve the multiplication of analog voltages/fluxes shown in the current expressions, the designed circuit does not use any external analog multiplier which is the major advantage of the proposed memelement emulator.

3 Effect of non-ideal gains and terminal parasitics of MVDCC and OTA

Now, we have investigated the effect of non-ideal gains and terminal parasitics of VDCC and OTA on the realized function of proposed memelement emulator. In Eq. 13, we have shown the matrix of VDCC with non-ideal gains, and Eq. 14 shows the current–voltage relationship of an OTA with non-ideality factor \(\alpha_{0}\).

Furthermore, the parasitic model of VDCC is shown in Fig. 5, with different parasitic resistances and capacitances connected at the terminals in different configurations. This parasitic model was discussed in [54]. Similarly, the parasitic effect in the OTA can be considered as a grounded resistance R0 connected at the output terminal.

VDCC parasitic model given in [54]

The Fig. 6 demonstrates the circuit of proposed emulator with port parasitics of VDCC and OTA.

In this circuit, the voltage Vin = V1 − V2 is applied as the input to the circuit. Due to symmetry property, we can assume, Vin/2 and − Vin/2 is applied at both the terminals of the emulator circuit respectively. For, RZ− = RZ+ = RZ, we can compute that;

On further calculation, the IIN is calculated as;

When Z1 is chosen as R1 (the case of memristor),

When Z1 is chosen as C1 (the case of meminductor),

From Eq. 17, it can be observed that under the effects of parasitics, the memristor may show the behavior of a meminductor element. And from Eq. 18, we can see that at operating frequencies significant high, we can assume; \(s\left( {C_{1} + C^{\prime}} \right)R^{\prime} \gg 1\) and also \(sR_{0} C_{2} \gg 1\) and the circuit will act can act as considerable meminductor with some non-ideal gains.

4 Simulation results

For the purpose of validation of the proposed mem-element emulator, we have performed the simulation using PSPICE environment for the CMOS implementation (depicted in Figs. 2 and 3) of MVDCC and OTA. The selected aspect ratios of the MOS transistors used in Figs. 2 and 3 are shown in Tables 2 and 3 respectively. The power supply value is taken as VDD, SS = ± 0.9 V. And the.

Initially, we have executed the simulations for realized meminductor by selecting the Z1 as capacitance C1 in the proposed design shown in Fig. 4. Now, upon application of a sinusoidal excitation, the obtained Pinched Hysteresis Loops (PHLs) are depicted from Figs. 7, 8 and 9. These hysteresis loops are plotted between the generated input current Iin and capacitance voltage VC1(volts). Ideally, we should be plotting the curve between Iin and flux of the input voltage, \(\varphi\). But, as in PSPICE, x-axis variable cannot be selected as the integration of the input voltage (i.e. \(\varphi\)), we had to choose the capacitance voltage VC1, which is the potential value proportional to the integration of input voltage (as per the configuration of the proposed circuit), which serves our purpose as the desired x-axis variable. It is important to clarify that product term (1/R2C1) along with the integration of input voltage, remains constant during the simulation and does not influence the ideal nature of the plotted hysteresis curves. These \(\varphi\)-i curves are plotted for the selected parameters as; C1 = 2 pF, C2 = 3 pF, and R2 = 1 K at input signal frequency as Fin = 200 kHz. Moreover, the peak value of the sinusoidal signal is taken as VP = 0.05 V and the biasing voltages are kept at VBS2 = 0.45 V and VBS = 0.4 V (biasing voltage of second stage of MVDCC and OTA respectively applied at the biasing terminals with respect to source supply VSS).

The plots shown in Figs. 7 and 8 illustrate the tuning facility available in the developed emulator configuration. These curves have been plotted by keeping all other parameters fixed except the resistance R2 and biasing voltage VBS respectively. It can be observed from the plot shown in Fig. 7 that emulated hysteresis behaviour in \(\varphi\)-i plane can be varied with the help of employed resistance R2. And also, as depicted by the plots given in Fig. 8, that realized meminductor behaviour can also be controlled using biasing voltage VBS. Next, we have plotted the transient characteristics of the realized meminductor at different values of the operating signal frequencies. These \(\varphi\)-i curves are shown in Fig. 9, which clearly demonstrate the change in the enclosed area of the contours with respect to variation in the applied signal frequency.

As already discussed, that potential across the capacitance C1, is proportional to the input flux ϕ, hence, transient response of the VC1 can be plotted to show the response of ϕ. So, it has been plotted in Fig. 10(a) and also, the corresponding current behavior of the meminductor is also plotted and shown in Fig. 10(b). We can observe that there is a non-symmetry appearing in the two adjacent quarter cycles of the current both in positive and negative directions. This unsymmetric behaviour is indicating the hysteresis nature of the meminductor found the transient \(\varphi\)-i curves. Similarly, we have traced the transient variation of the input inverse meminductance of the developed emulator circuit, which has been plotted in Fig. 11. The presence of the peaks in the response may be associated to the extreme parts of the transient \(\varphi\)-i curves, where the current show steep decline and rise. From Fig. 11, we can find the max. and min. value of inverse meminductance. From which, the range of the meminductance can be calculated as; 2.85H to almost 10H. (Here, we are not considering the notches of the curve, which are corresponding to the transient behavior observed at the edges of the PHLs, at which meminductance approaches to infinite for a small time period.)

Furthermore, the operation of the realized memristor element can be demonstrated through the presented simulation results. The memristor response can be achieved by choosing the grounded impedance Z1 as resistance R1. The simulations have been executed for the selected parameters as; R1 = 4 K, R2 = 2 K and C2 = 2.5 pF with peak input value as VP = 0.25 V at Fin = 150 K. And the biasing voltages are chosen as; VBS2 = 0.45 V and VBS = 0.4 V. Firstly, we have run the simulations to investigate the impact of passive elements and biasing voltage on the emulated memristive behaviour. These transient v-i curves have been illustrated in Figs. 12, 13 and 14, which have been obtained for different values of R1, C2 and biasing voltage VBS respectively. From the three plots, it can be easily determined that realized memristor function is controllable through grounded passive elements as well as the biasing voltage. Next, the frequency dependence response of the enclosed area under contour curves is studied and simulation plots are shown in Fig. 15. From the plots given in Fig. 15, it can be witnessed that area versus frequency behaviour is found to be satisfactory, which is as per the fingerprint of the memristor. The response of the input voltage and current has also been generated as shown in Fig. 16(a, b). In the current response, the zero crossing is observed only at the similar phase angles as appearing in the input voltage variation (in Fig. 16(a)), it depicts the inherent resistive nature of the realized memristor. Moreover, we have presented the transient response of the input memristance of the memristor in Fig. 17. The curve exhibits a sharp peak during a cycle of the applied signal, it may be present due to the abrupt turning of transient v-i contours at the extreme points (as can be observed in plots given in Figs. 12, 13 and 14). Moreover, from Fig. 17, the max. and min. value of memristance can be calculated as; 1 KΩ and 77 KΩ respectively.

The simulation result shown in Fig. 18 is generated for applying a pulse signal of peak value VP = 0.01 V, TW = 0.01 ns and TP = 0.1 ns. It can be noted that a high period valued voltage signal applied to the emulator circuit, will result in a capacitance voltage response having spikes present periodically, which can be considered as the desired flux variation. For such flux response, the meminductor current IIN has been measured as given in Fig. 18 and the nature of amplitude variations of each current spikes depicts the nature of inverse meminductance (L−1) variation, which is shown through red colored staircase response. It can be understood that in the absence of current output the L−1 must be at hold because the current value is found to be increased in every upcoming on-duration of the input, which is confirming its non-volatility property. Similarly, the pulse signal of parameters VP = 0.01 V, TW = 0.01 ns and TP = 0.1 ns, has been applied to the memristor to check its non-volatility. For the simulation purpose, we have configured a decremental memductor. The generated plot is shown in Fig. 19 showing the obtained current response with staircase pattern noted to show the nature of memductance (GM).

The Figs. 20 and 21 shows the obtained Monte-Carlo plots generated for 50 iterations for both realized meminductor and memristor. These plots are generated for the selected values of simulation parameters. The Monte Carlo analysis has been used to investigate the effect of the process parameters and the mismatch between transistors. The mismatch between the transistors and various process corners such as fast and slow mode operations for NMOS and PMOS transistors were taken into account. The plots given in Figs. 20 and 21 clearly shows that the proposed floating meminductor and memristor exhibit a good performance in 50 different iterations although the hysteresis loops may be slightly altered.

To illustrate the effects of different process corners, the hysteresis loops have been generated at a temperature of 27 °C and have been shown in Figs. 22 and 23 for both the realized memelements. The three different process corners are; slow NMOS and PMOS (SS), fast NMOS and PMOS (FF), and typical NMOS and PMOS (TT).

5 Application examples

The functioning of the reported emulator configuration can also be exhibited by employment of the realized memelements in the application examples, which have been illustrated in the following section.

5.1 Meminductor based neuromorphic circuit for mimicking amoeba behaviour

The use of memristor in neural applications has been a popular research interest in the last decade. Due to the unique nature of memristors of resistance variability with respect to applied excitation, it has been used in modelling of natural neurons and unicellular species. Like in [58], a passive element-based circuit configuration has been proposed to demonstrate the amoeba action. Using similar approach, this circuit can also be implemented by employing other memelements [59]. This discussed circuit in [59] has been depicted in Fig. 24, based on the floating meminductor emulator developed using MVDCC. This circuit generates the response of Amoeba exhibited during the temperature change takes place around it. The amoeba shows a change in its locomotive speed whenever there is any change in its surrounding temperature. This process of slowing down the speed takes a certain time in which temperature drops multiple times in that period, after which the movement seems to become slow. But, due to this unique nature of learning found in the amoeba, from the next time the speed starts to slow down immediately just after the temperature drop.

In Fig. 25, the input vin(t) of the developed circuit represents the temperature change in the close environment, while the vout(t) represents the variation in the locomotive speed of the amoeba. And the simulation results for the vout(t) is shown in Fig. 25(b) with the input voltage vin(t) taken as pulse signal (Vp(t) in Fig. 25(a). It can be observed from the output vout(t) that for the occurrences of multiple pulses, the output first grows then oscillations go down gradually, but for the single pulse arriving after some time, the output seems to suddenly increases but slows down instantly, so, it is confirming that the presented circuit is validating the amoeba behavior.

Response of the voltage Vout (b) for the input VIN applied as pulse excitations (a) to the circuit shown in Fig. 16 with parameters value chosen as; peak value as Vm = 10 mv and pulse width as TW = 10 µs

5.2 Proposed memristor emulator based associative learning demonstration

Next, we have shown the application example of the realized memristor element. The proposed memristor has been used to model the behaviour of a synapse architecture, which are the basic elements of any neural related applications. The synapse behaves as a communication link between two neurons and its response is decided by the signal received from the pre-synaptic neuron and signal transmitted to the post-synaptic neuron. The function of the memristor element also matches with such kind of behaviour and it has also been depicted in several works [58].

The synapse like behaviour of the memristor can be validated through a popular example of Pavlov learning experiment of associative learning. Pavlov showed this behaviour exhibited by a dog, when he periodically showed the food to the dog along with the ringing of the bell. Firstly, he gave the food to the dog and rang the bell at the same time, then he used to ring the bell only and observed that dog started to salivate even when the food is not served. He called this behaviour as the associative learning. The corresponding Op-amp based circuit is represented in Fig. 26(a), which can be used to mimic this behaviour through its two pulse voltage inputs VNS and VUCS and output voltage Vout.

We have applied pulse input voltages VNS and VUCS to this op-amp based circuit shown in Fig. 26(a), which consists of multiple pulse excitations having dissimilar time delays. The simulated transient response of voltages VNS and VUCS has been shown in Fig. 26(b) followed by the generated pulse output response. In the first phase, which is the duration before the learning, we have applied VNS and VUCS pulse input at different instants, and it can be noticed from the output that the circuit only responds to the VNS input in this phase. In the second phase, both inputs have been applied simultaneously and output is produced. Now interestingly, when the two pulse excitations (VNS and VUCS) are given at different time instants, the output is generated for both the input pulses. This nature of the circuit is confirming its ability of associative learning.

6 Experimental results

The section presents experimental results of the proposed memelement emulator implemented using commercially available ICs; LM13700, AD844 and µA741. For the implementation of the proposed circuit (in Fig. 4), we need to obtain the function of MVDCC and OTA using these ICs. The MVDCC is made up of a dual-output input transconductance stage and a second-generation current conveyor. Both of these stages can be replaced by the ICs LM13700 and AD844 respectively. As both current outputs of MVDCC (IZ+ and IZ−) are used in the circuit, we need to use two single output transconductance amplifiers. Fortunately, the LM13700 IC consists of two transconductance amplifiers. Moreover, the µA741 is also required to obtain the relationship between X, Z+ and Z− ports’ voltages, which is (VX = VZ+ − VZ−) for MVDCC. Furthermore, one more LM13700 IC needed to realize the function of OTA used in the proposed circuit. Therefore, the complete schematic diagram of the MVDCC-OTA based emulator circuit using two LM13700 ICs, a µA741 and an AD844 IC, is shown in Fig. 27 for both realized meminductor as well as the memristor. In the circuit, Z1, R2 and C2 are corresponding to the passive elements used in the proposed emulator, and the resistances R5 are R4 are needed for the biasing of two LM13700 ICs respectively. The resistance R3 is connected just to pass the current of AD844 output to ground as it has no active use in the circuit. The resistances R6, R7, R8 and R9 are the integral part to design a voltage subtractor using Op-Amp IC.

From the presented circuit shown in Fig. 27, we can observe that differential input voltages at the input terminal of the emulator circuit, V1 and V2, are applied at the buffer inputs, therefore buffer outputs are obtained as;

Now, these voltages appear at the input of subtractor through resistance R6 and R7. If, the resistances value as chosen as R6 = R7 = R8 = R9, then subtractor output is obtained as;

Now, this voltage (given in Eq. 21) is applied at the 3rd pin (Y port) of the AD844 IC and for AD844, we know,

Hence, potential at the Pin 2 (X port) of AD844 IC is found as;

The resistance R2 is connected at the X port, therefore, current through R2,

For AD844 IC the IX = IZ, therefore, the current flowing out of the Pin no. 5 will be,

Hence, voltage VZ1 will be equals to,

This voltage VZ1 is applied at the transconductance stage of LM13700, whose output is taken across the capacitor C2, hence, the voltage VC2 will be,

where G is the transconductance gain of the LM13700 IC.

Now, this voltage VC2 is applied for the biasing purpose of both the transconductance stages of another LM13700 IC. So, transconductance of the both stages will be modified and become function of VC2 voltage. For first LM13700, the transconductance gain (G’) in terms of biasing voltage is given as;

where k is constant, depends upon the LM13700 parameter.

So, as per the circuit configuration, the input currents I1 and I2 (which are fed to the outputs of LM13700) will be;

and

From Eqs. 29 and 30, we can observe that this circuit shown in Fig. 28, realizes a memelement emulator based on LM13700 and AD844. For choosing Z1 as C1 and as R1, the depicted circuit emulate the behavior of a meminductor and memristor respectively.

The experimental verification of the developed emulators has been performed and results have been discussed in Figs. 28 and 29.

For the validation of the meminductor emulator, the parameters values are chosen as; C1 = 1 pF, R2 = 1.8 K, R3 = 15 K and R5 = 25 K, R6 = R7 = R8 = R9 = 1 K and C2 = 4.7 nF with maximum i/p voltage value as VP = 0.008 V at a frequency of 7.5 kHz. Now, to obtain the \(\phi\)-i curves, here also, the voltage across the capacitor C2 is chosen, whose potential is proportional to the flux of input voltage and plot has been traced between input current and capacitor voltage. The result can be displayed on the CRO screen, which is shown in Fig. 28.

Similarly, to investigate the implemented memristor emulator, the parameters values are chosen as; R1 = 100 K, R2 = 10 K, R3 = 20 K, R4 = 24 K, R4 = 20 K, R6 = R7 = R8 = R9 = 1 K and C2 = 4.7 nF with applying peak input value of VP = 0.35 V at 10 kHz. The generated Lissajous pattern for the memristor is displayed on the CRO screen and presented in Fig. 29.

7 Conclusion

The behavior of a flux-controlled and voltage-controlled meminductor and memristor element has been realized in this work. The architecture used for the realization of these two memelements is developed by using an MVDCC and an OTA. The MVDCC active element is based on thirty CMOS transistors and nine transistors are needed for OTA and hence, the developed memelement emulator employs only thirty transistors. Additionally, from the perspective of monolithic integration, the use of grounded elements employed in the circuit adds to the preferability of the developed circuit. The analysis has also been presented for taking non-ideal gains of used ABBs and parasitic ports into account. The discussed PSPICE generated simulation results clearly depicted that hysteresis behavior observed in the transient contour curves of the realized memelements can be tuned through the use of employed passive elements and through variation of the biasing voltage as well. The functioning of the both realized elements has also been verified for the neural related applications based on the proposed emulator. And finally, we have depicted the commercial ICs based implementation of suggested emulator circuit and experimental results are demonstrated (shown in Figs. 28 and 29), confirming its operability as the meminductor and as a memristor element.

Data availability

Data sharing not applicable to this article as no datasets were generated or analysed during the current study.

References

Chua, L. O. (1971). Memristor-the missing circuit element. IEEE Transactions on Circuit Theory, 18, 507–519.

Di Ventra, M., Pershin, Y. V., & Chua, L. O. (2009). Circuit elements with memory: Memristors, memcapacitors, and meminductors. Proceedings of the IEEE, 97(10), 1717–1724. https://doi.org/10.1109/JPROC.2009.2021077

Yin, Z., Tian, H., Chen, G., & Chua, L. O. (2015). What are memristor, memcapacitor, and meminductor? IEEE Transactions on Circuits and Systems II: Express Briefs, 62(4), 402–406. https://doi.org/10.1109/TCSII.2014.2387653

Kolka, Z., Biolek, D., & Biolkova, V. (2011). Frequency-domain steady-state analysis of circuits with mem-elements. In 2011 7th International Conference on Electrical and Electronics Engineering (ELECO), Bursa, (2011) II-328-II-332.

Yu, D., Iu, H. H. C., Fitch, A. L., & Liang, Y. (2014). A floating memristor emulator based relaxation oscillator. IEEE Transactions on Circuits and Systems I, 61, 2888–96.

Sanchez-Lopez, C., Mendoza-Lopez, J., Carrasco-Aguilar, M. A., & Muniz-Montero, C. (2014). A floating analog memristor emulator circuit. IEEE Transactions on Circuits and Systems II Express Briefs, 61, 309–13.

Yesil, A., Babacan, Y., & Kacar, F. (2019). A new floating memristor based on CBTA with grounded capacitors. Journal of Circuits, Systems and Computers, 28(13), 1950217.

Ranjan, R. K., Rani, N., Pal, R., Paul, S. K., & Kanyal, G. (2017). Single CCTA based high frequency floating and grounded type of incremental/decremental memristor emulator and its application. Microelectronics Journal, 60, 119–128.

Sozen, H., & Cam, U. (2016). Electronically tunable memristor emulator circuit. Analog Integrated Circuits and Signal Processing, 89, 655–663.

Petrovic, P. B. (2018). Floating incremental/decremental flux-controlled memristor emulator circuit based on single VDTA. Analog Integrated Circuits and Signal Processing, 96, 417–433.

Yesil, A., Babacan, Y., & Kacar, F. (2020). An electronically controllable, fully floating memristor based on active elements: DO-OTA and DVCC. International Journal of Electronics and Communications. https://doi.org/10.1016/j.aeue.2020.153315

Ranjan, R., Surendra, S., Raushan, S., Garg, N., Kumari, B., & Khateb, F. (2018). High frequency floating memristor emulator and its experimental results. IET Circuits, Devices & Systems. https://doi.org/10.1049/iet-cds.2018.5191

Petrović, P. B. (2019). Tunable flux-controlled floating memristor emulator circuits. IET Circuits, Devices & Systems, 13(4), 479–486.

Li, Z., Zeng, Y., & Ma, M. (2017). A novel floating memristor emulator with minimal components. Active and Passive Electronic Components. https://doi.org/10.1155/2017/1609787

Dongsheng, Y., Xuanqi, Z., Tingting, S., Herbert, H. C., & Tyrone, F. (2019). A simple floating mutator for emulating memristor, memcapacitor, and meminductor. IEEE Transactions on Circuits and Systems II: Express Briefs. https://doi.org/10.1109/TCSII

Cam, Z., & Sedef, H. (2017). A new floating memristance simulator circuit based upon second generation current conveyor. Journal of Circuits Systems and Computers, 26(2), 1750029.

Taskiran, Z. G. C., Ayten, U. E., & Sedef, H. (2019). Dual output operational transconductance amplifier-based electronically controllable memristance simulator circuit. Circuits Systems and Signal Processing, 38(10), 26–40.

Prasad, S. S., Kumar, P., & Ranjan, R. K. (2021). Resistorless memristor emulator using CFTA and its experimental verification. IEEE Access, 9, 64065–64075. https://doi.org/10.1109/ACCESS.2021.3075341

Petrović, P. B. (2021). Simple flux-controlled grounded memristor emulator circuits based on current follower. Analog Integrated Circuits and Signal Processing, 108, 215–219. https://doi.org/10.1007/s10470-021-01847-6

Vista, J., & Ranjan, A. (2020). Flux controlled floating memristor employing VDTA: Incremental or decremental operation. IEEE Transactions on Computer Aided Design of Integrated Circuits and Systems. https://doi.org/10.1109/TCAD.2020.2999919

Sharma, P. K., Ranjan, R. K., Khateb, F., & Kumngern, M. (2020). Charged controlled mem-element emulator and its application in a chaotic system. IEEE Access, 8, 171397–171407. https://doi.org/10.1109/ACCESS.2020.3024769

Fang, Y., Guangyi, W., & Xiaowei, W. (2017). Chaotic oscillator containing memcapacitor and meminductor and its dimensionality reduction analysis. Chaos: An Interdisciplinary Journal of Nonlinear Science, 27, 033103. https://doi.org/10.1063/1.4975825

Yuan, F., Li, Y., Wang, G., Dou, G., & Chen, G. (2019). Complex dynamics in a memcapacitor-based circuit. Entropy, 21, 188. https://doi.org/10.3390/e21020188

Zhiheng, H., Yingxiang, L., Jia, L., & Juebang, Y. (2010). Chaos in a charge-controlled memcapacitor circuit. International Conference on Communications, Circuits and Systems (ICCCAS). https://doi.org/10.1109/ICCCAS.2010.5581864

Setoudeh, F., & Dezhdar, M. M. (2020). A New design and implementation of the floating-type charge-controlled memcapacitor emulator. Majlesi Journal of Telecommunication Devices, 9(2), 71–79.

Vista, J., & Ranjan, A. (2020). Simple charge controlled floating memcapacitor emulator using DXCCDITA. Analog Integrated Circuits and Signal Processing. https://doi.org/10.1007/s10470-020-01650-9

Fouda, M. E., & Radwan, A. (2012). Charge controlled memristor-less memcapacitor emulator. Electronics Letters, 48, 1454–1455. https://doi.org/10.1049/el.2012.3151

Biolek, D., Biolková, V., Kolka, Z., & Dobes, J. (2015). Analog Emulator of genuinely floating memcapacitor with piecewise-linear constitutive relation. Circuits, Systems, and Signal Processing. https://doi.org/10.1007/s00034-015-0067-8

John, V., & Ranjan, A. (2019). Design of memcapacitor emulator using DVCCTA. Journal of Physics: Conference Series, 1172, 012104. https://doi.org/10.1088/1742-6596/1172/1/012104

Francisco, R., Diego, M., Godoy, A., Francisco, R., Isabel, T., Akiko, O., & Noel, R. (2019). Memcapacitor emulator based on the Miller effect. International Journal of Circuit Theory and Applications. https://doi.org/10.1002/cta.2604

Konal, M., & Kacar, F. (2020). Electronically tunable memcapacitor emulator based on operational transconductance amplifiers. Journal of Circuits, Systems and Computers. https://doi.org/10.1142/S0218126621500821

Kumar, K., & Nagar, B. C. (2021). New tunable resistorless grounded meminductor emulator. Journal of Computational Electronics, 20, 1452–1460. https://doi.org/10.1007/s10825-021-01697-5

Yuriy, P., & Di, M. (2011). Ventra, emulation of floating memcapacitors and meminductors using current conveyors. Electronics Letters, 47, 243–244. https://doi.org/10.1049/el.2010.7328

Thongdit, P., Chunchay, S., Angkeaw, K. (2020). A meminductor emulator based on flux-controlled model using field programmable analog array. In 2020 17th international conference on electrical engineering/electronics, computer, telecommunications and information technology (ECTI-CON), Phuket, Thailand, pp. 51–54. https://doi.org/10.1109/ECTI-CON49241.2020.9158116.

Taşkıran, Z. G. C., Sağbaş, M., Ayten, U. E., & Sedef, H. (2020). A new universal mutator circuit for memcapacitor and meminductor elements. International Journal of Electronics and Communications. https://doi.org/10.1016/j.aeue.2020.153180

Konal, M., & Kacar, F. (2020). Electronically tunable meminductor based on OTA. International Journal of Electronics and Communications. https://doi.org/10.1016/j.aeue.2020.153391

Babacan, Y. (2018). An operational transconductance amplifier-based memcapacitor and meminductor. Electrica, 18(1), 36–38.

Sah, M., Udhathoki, R., Yang, C., & Kim, H. (2014). Mutator-based meminductor emulator for circuit applications. Circuits Systems and Signal Processing. https://doi.org/10.1007/s00034-014-9758-9

Romero, F., Escudero, M., Medina-Garcia, A., Morales, D., & Rodriguez, N. (2020). Meminductor emulator based on a modified Antoniou’s Gyrator circuit. Electronics, 9, 1407. https://doi.org/10.3390/electronics9091407

Sah, M., Budhathoki, R., Yang, C., & Kim, H. (2014). Charge controlled meminductor emulator. JSTS: Journal of Semiconductor Technology and Science., 14, 750–754. https://doi.org/10.5573/JSTS.2014.14.6.750

Zhao, Q., & Zhang, X. (2019). A universal emulator for memristor, memcapacitor, and meminductor and its chaotic circuit. Chaos: An Interdisciplinary Journal of Nonlinear Science, 29, 013141. https://doi.org/10.1063/1.5081076

Vista, J., & Ranjan, A. (2020). High frequency meminductor emulator employing VDTA and its application. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 39(10), 2020–2028. https://doi.org/10.1109/TCAD.2019.2950376

Yuan, F., Deng, Y., & Li, Y. (2020). A multistable generalized meminductor with coexisting stable pinched hysteresis loops. International Journal of Bifurcation and Chaos, 30, 2050023. https://doi.org/10.1142/S0218127420500236

Hasan, S., & Ugur, C. (2020). A novel floating/grounded meminductor emulator. Journal of Circuits, Systems and Computers. https://doi.org/10.1142/S0218126620502473

Yuan, F., Deng, Y., Li, Y., & Wang, G. (2019). The amplitude, frequency and parameter space boosting in a memristor–meminductor-based circuit. Nonlinear Dynamics. https://doi.org/10.1007/s11071-019-04795-z

Birong, X., Wang, G., Iu, H., Simin, Y., & Yuan, F. (2019). A memristor–meminductor-based chaotic system with abundant dynamical behaviors. Nonlinear Dynamics. https://doi.org/10.1007/s11071-019-04820-1

Liu, Y., & Iu, H. H. (2020). Novel floating and grounded memory interface circuits for constructing mem-elements and their applications. IEEE Access, 8, 114761–114772. https://doi.org/10.1109/ACCESS.2020.3004160

Raj, N., Ranjan, R. K., Khateb, F., & Kumngern, M. (2021). Mem-elements emulator design with experimental validation and its application. IEEE Access, 9, 69860–69875. https://doi.org/10.1109/ACCESS.2021.3078189

Singh, A., & Rai, S. K. (2021). Novel meminductor emulators using operational amplifiers and their applications in chaotic oscillators. Journal of Circuits, Systems and Computers. https://doi.org/10.1142/S0218126621502194

Singh, A., & Rai, S. K. (2021). VDCC-based memcapacitor/meminductor emulator and its application in adaptive learning circuit. Iranian Journal of Science and Technology, Transactions of Electrical Engineering. https://doi.org/10.1007/s40998-021-00440-x

Bhardwaj, K., & Srivastava, M. (2021). New electronically adjustable memelement emulator for realizing the behaviour of fully-floating meminductor and memristor. Microelectronics Journal, 114, 105126. https://doi.org/10.1016/j.mejo.2021.105126

Biolek, D., Senani, R., Biolkova, V., & Kolka, Z. (2008). Active elements for analog signal processing: Classification, review and new proposals. Radioengineering, 17(4), 15–32.

Prasad, D., Bhaskar, D. R., & Srivastava, M. (2014). New single VDCC-based explicit current-mode SRCO employing all grounded passive components. Electronics Journal, 18(2), 81–88.

Srivastava, M., & Prasad, D. (2016). VDCC based dual-mode quadrature sinusoidal oscillator with current/voltage outputs at appropriate impedance level. Advances in Electrical and Electronic Engineering (Czech Republic), 14(2), 168–177.

Prasad, D., Srivastava, M., Ahmad A., Mukhopadhyay, A., Sharma, B. B. (2015). Novel VDCC based low-pass and high-pass ladder filters. In: IEEE-INDICON-2015, pp. 1–4, New Delhi, India.

Kaçar, F., Yeşil, A., Minaei, S., & Kuntman, H. (2014). Positive/negative lossy/lossless grounded inductance simulators employing single VDCC and only two passive elements. AEU - International Journal of Electronics and Communications, 68(1), 73–78.

Bhardwaj, K., & Srivastava, M. (2020). Floating memristor and inverse memristor emulation configurations with electronic/resistance controllability. IET Circuits Devices and Systems, 14(7), 1065–1076.

Pershin, Y. V., Fontaine, S. L., & Ventra, M. D. (2009). Memristive model of amoeba learning. Physical Review E, 80, 021926.

Wang, F. A., Chua, L. O., Yang, X., Helian, N., Tetzlaff, R., Schmidt, T., Li, C., Carrasco, J. M. G., Chen, W., & Chua, D. (2013). Adaptive neuromorphic architecture. Neural Networks, 45, 111–116.

Funding

Not Applicable.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Bhardwaj, K., Srivastava, M. New grounded passive elements-based external multiplier-less memelement emulator to realize the floating meminductor and memristor. Analog Integr Circ Sig Process 110, 409–429 (2022). https://doi.org/10.1007/s10470-021-01976-y

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-021-01976-y