Abstract

In this paper, grounded and floating decremental/incremental memristor emulator circuits are realized using fully balanced voltage differencing buffered amplifier (FB-VDBA) and grounded capacitor. These proposed configurations are simpler in design as compared to most of the designs available in the literature. The pinched Hysteresis loops are maintained up to 1 MHz frequency. The decremental to incremental memristor emulator and vice versa can be easily attained by slightly modifying the circuits. Proposed designs of memristor emulator circuits are simulated using TSMC 0.18 µm CMOS process technology parameters of Mentor Graphics Eldo tool. The proposed decremental floating memristor emulator circuit has been embedded in the design of universal biquad filter to evaluate its performance.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

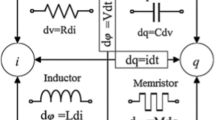

Resistor, capacitor and inductor are the three well-known fundamental elements of electrical circuits. Each element offers a relation between any two of the four circuit variables namely voltage, current, charge and flux. Resistor provides relationship between voltage and current, whereas capacitor and inductor relate charge to voltage and flux to current, respectively. There was no element that can provide relationship between charge and flux. Professor Leon Chua postulated the fourth fundamental circuit element namely memristor (short for memory and resistor) that relates flux and charge (Chua 1971). Memristor offers unique properties that cannot be offered by any of the three fundamental elements or by combinations of these elements. Despite of its unique properties, researchers and engineers were not very interested to use memristor because of its unavailability in the market as off-the-shelf component. Researchers of Hewlett Packard lab published a paper announcing the physical realization of the memristor (Strukov et al. 2008). This paper has drawn significant attention of researchers and also motivated them to work upon memristors. Memristor is still not commercially available in the device form which opens a new area of research to design memristor emulator circuits. Researchers have recently started working on memristor emulator circuits and a lot of research is going on in this direction. Various emulator circuits which mimic the properties of memristors are being reported using modern active analog building blocks such as second-generation current conveyors (CCIIs), current feedback operational amplifiers (CFOAs), differential difference current conveyor (DDCC), operational transconductance amplifier (OTA), current conveyor transconductance amplifier (CCTA), differential voltage current conveyor transconductance amplifier (DVCCTA), current backward transconductance amplifier (CBTA), voltage differencing current conveyor (VDCC), voltage differencing transconductance amplifier (VDTA), current differencing buffered amplifier (CDBA), current differencing transconductance amplifier (CDTA) and, etc. A memristor emulator circuit was realized using four CCIIs, one multiplier and six passive components (Lopez et al. 2013). Another realization of floating memristor emulator circuit was reported in which four CCIIs, one op-amp, one multiplier, and eight passive components have been used (Yu et al. 2014). The incremental/decremental memristor emulator circuits using one active building block namely DDCC, three passive components and one additional multiplier have been realized in (Yesil et al. 2014). Different values of resistors and capacitors are given for different range of frequencies of operation of memristor emulator circuits. Afterward, memristor emulator circuit has been realized using three CCIIs, five passive components and one multiplier (Kumngern 2015). Another current-controlled memristor emulator circuit was reported using two CCIIs, three passive components and two transistors (Alharbi et al. 2015). Next, grounded memristor emulator circuit using two active building blocks namely CFOAs and OTA with five passive components was reported in (Abuelma’atti and Khalifa 2015). The reported memristor emulator was embedded in the design of multivibrator circuit to verify its performance. A grounded memristor emulator circuit was reported using two CCIIs, three passive components and one multiplier (Lopez et al. 2015). Subsequently, grounded memristor emulator circuit was reported using six OTAs, three passive components and one multiplier (Kumngern and Moungnoul 2015). A simple memristor emulator circuit was realized using single CCII, three passive components and one amplifier (Alharbi et al. 2015). The amplifier was used to obtain the nonlinear behavior for the formation of pinched Hysteresis loop. A floating memristor emulator circuit employing four CFOAs and five passive components was reported in (Abuelma’atti and Khalifa 2016) and was also used in the realization of FM demodulator. Next, memristor emulator circuit using seven active building blocks (four CCIIs and three OTAs) and six passive components was reported in which the transconductance is adjusted after changing the bias voltage of one of the OTA in order to change the memristance (Sozen and Cam 2016). Another floating memristor emulator circuit of high memristance value was reported in which the subthreshold region of operation was utilized to implement the tunable resistor (Babacan and Kacar 2017). A fractional-order memristor emulator circuit was designed using two CCIIs + , three passive components and one multiplier (Rashad et al. 2017). Next, the charge-controlled memristor emulator circuit was reported in Ranjan et al. (2017) that uses one CCTA and five passive components. Incremental and decremental memristor emulator circuits for high frequency were reported in which one DVCCTA and four passive components have been used (Ranjan et al. 2017). Afterward, another incremental/decremental memristor emulator circuits using a CBTA, three passive components and a multiplier were reported in (Ayten et al. 2017). The output terminals of CBTA have been interchanged to convert incremental memristor emulator circuit into decremental memristors emulator (Babacan et al. 2017). Memristor emulator circuits utilizing two CCIIs, four passive components and a multiplier have been reported in (Cam and Sedef 2017). Both, incremental and decremental memristor emulator circuits, were presented. A memristor emulator circuit was presented using VDTA, three passive components and a multiplier (Petrovic 2018). Floating memristor emulator circuit with hard-switching behavior was reported using multiple-output OTA and a capacitor in (Yesil 2019). A MOSFET-C-based grounded memristor emulator circuit was reported in which seven MOSFETs and one capacitor have been used (Yesil 2018). A memristor emulator circuit was reported in (Ranjan et al. 2018) employing four multiple-output OTAs, three resistors and a capacitor. Subsequently, high-frequency memristor emulator circuits have been reported using two OTAs and a capacitor (Kanyal et al. 2018). A VDCC-based memristor emulator circuit was realized in (Yesil et al. 2019) that uses one VDCC, two PMOS (used as a tunable resistor) and one capacitor. A memristor emulator circuit was reported in (Yesil et al. 2019) that utilizes VDTA and one MOS capacitor. A floating-gate MOSFET (FGMOS)-based memristor emulator circuit has been reported that uses three FGMOS and a capacitor (Vista and Ranjan 2019). Grounded and floating configurations of memristor emulator circuits using OTA, CDBA and grounded capacitor are reported in (Yadav et al. 2020). Recently, memristor emulator circuits using two active building blocks (CDTA and OTA) with a grounded capacitor are reported in (Gupta and Rai 2020).

Memristors are now being used in variety of applications such as adaptive filtering (Driscoll et al. 2010; Chew and Li 2012), computation of Boolean functions (Lehtonen et al. 2010), cellular neural networks (Itoh and Chua 2019), chaotic circuit (Muthuswamy and Chua 2010; Muthuswamy 2010; Ngouonkadi et al. 2014), computation of basic arithmetic operations (Merrikh-Bayat and Shouraki 2010), data storage neuromorphic applications (Kim et al. 2012), fractional-order circuits (Petras 2010), image processing (Hu et al. 2012), logic gate implementation (Borghetti et al. 2010; Kvatinsky et al. 2011), memristive neural networks (Pershin and Di Ventra 2010; Pérez-Carrasco et al. 2010), multilevel memory (Kim et al. 2010), non-volatile memory (Yang et al. 2008; Pickett et al. 2009; Robinett et al. 2010), phase shift oscillator (Talukdar et al. 2012; Talukdar et al. 2011), programmable analog circuits (Pershin and Di Ventra 2010; Shin et al. 2010), reactance-less oscillator (Zidan et al. 2014), temperature sensor (Wang et al. 2009), twin-T oscillator (Zhi-Jun and Yi-Cheng 2013), twin-T notch filter (Iu et al. 2011), variable gain amplifier (Wey and Jemison 2011), voltage controlled relaxation oscillator (Hussein and Fouda 2013; Anjanakumari et al. 2019), Wein bridge oscillator (Talukdar et al. 2011) and Wheatstone bridge (Kim et al. 2015).

It has been observed that most of the designs of memristor emulator circuits reported in the literature use excess number of active and passive components and also use analog multiplier to obtain pinched Hysteresis loop of memristor. The range over which memristor emulator circuit works well is restricted to the frequency range of KHz in most of the designs. Therefore, objective of the paper is to design grounded and floating decremental/incremental memristor emulator circuits using less number of active and passive components that can perform satisfactorily in the frequency range of MHz. In this paper, memristor emulator circuits are proposed using one fully balanced VDBA and a grounded capacitor. Decremental memristor emulator circuits have easily been converted into incremental memristor emulator circuits and vice versa with slight modification in the circuit.

2 Fully Balanced Voltage Differencing Buffered Amplifier: Characteristics, Symbol and Circuit Diagram

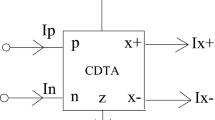

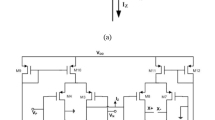

The FB-VDBA is a six terminal block out of which two are input terminals, two are intermediate terminals and remaining two are output terminals as depicted in Fig. 1. Input voltages Vp and Vn are applied to terminals p and n. The transconductance amplifier converts these voltages into currents (Iz+ and Iz−) at z + and z− terminals, respectively, as given in Eq. (1). The voltages Vz+ and Vz− are obtained by connecting impedances Zz to the z+ and z− terminals of FB-VDBA as given in Eq. (2). The voltages Vz+ and Vz− are copied by two inverted buffers to achieve two voltages Vw− and Vw+ as given in Eq. (3). The transconductance (gm) of conventional FB-VDBA is controlled by varying the bias current (IB) as given in Eq. (4). The internal structure of voltage-tunable FB-VDBA as shown in Fig. 2 has been designed by replacing the bias current IB of conventional FB-VDBA (Sotner et al. 2013) with structures of current mirror formed by MOSFETs M17-M19. The transconductance (Gm) of voltage-tunable FB-VDBA depends on voltage VB as given in Eq. (5).

where k = µn.Cox.

3 The Proposed Grounded and Floating Memristor Emulator Circuits

The realizations of grounded decremental/incremental and floating decremental/incremental memristor emulators are depicted in Fig. 3a, b, respectively. In Fig. 3a, when terminals “a” and “c” are connected to terminals “b” and “d”, respectively, then, grounded decremental memristor emulator is obtained while grounded incremental configuration of memristor emulator is obtained from the same circuit when terminals “a” and “c” are connected to terminals “d” and “b”, respectively. Similarly in Fig. 3b, floating decremental memristor emulator circuit is realized when terminals “a” and “c” are connected to terminals “b” and “d”, respectively, while floating incremental memristor emulator circuit is obtained when terminals “a” and “c” are connected to terminals “d” and “b”, respectively. In grounded decremental/incremental memristor emulator circuits, one of the input terminals of voltage-tunable FB-VDBA is kept at ground, whereas in the decremental/incremental floating memristor emulator circuits both terminals remain at different voltages (Vin1 or Vin2). In all configurations of memristor emulator circuits, w−terminals are connected to VB terminal. In floating memristor emulator circuits, one additional feedback path is provided between z2+ terminal to input terminal. The voltage Vw− follows the inverted voltage across capacitor (Vz+ or Vz1+) connected to z+ and z1+ terminals of voltage-tunable FB-VDBA in grounded and floating memristor emulator circuits, respectively. The voltage Vw− is connected to the bias voltage VB which controls the input current (Iin). Therefore, voltage across capacitor (Vz+ or Vz1+) controls the input current (Iin) and this current is used to control the voltage across capacitor. This process keeps repeating and forms a pinched hysteresis loop. The input current (Iin) gets affected by the last stored voltage across the capacitor. If the voltage across capacitor increases the current Iin in positive direction, the proposed configurations are called as incremental memristor emulator circuits, whereas if the voltage across capacitor increases the current (Iin) in negative direction, the proposed configurations are known as decremental memristors emulators.

The analysis of the circuit shown in Fig. 3a yields the equations as

With the help of Eqs. (7) and (8), we get

where Φin is the total flux obtained in the proposed circuit of memristor emulator.

The flux (Φin) of proposed circuit of memristors emulator is given in Eq. (10).

The transconductance (Gm) is obtained after solving Eqs. (5) and (9) as

The memristance M (Φ) is achieved after replacing the value of Eq. (11) into Eq. (6) as

It is observed from Eq. (12) that the memristance has two parts fixed and variable. The variable part gets subtracted from the fixed part, and therefore, it represents the memristance of decremental grounded memristor emulator circuit. It depends on the amount of flux (ϕin) and value of capacitor. Similarly, the memristance of incremental memristor emulator circuit is represented by Eq. (13) in which variable part is added with the fixed part

After applying sinusoidal signal \(V_{m} \sin \omega t\) to the input terminal of grounded memristor emulator circuit, flux Φin is obtained as

where Vm is the amplitude of sinusoidal input signal and ω represents the frequency.

The value of flux Φin obtained from Eq. (14) is substituted into Eqs. (12) and (13) which leads to

From Eq. (15), it is clearly observed that the value of memreistance varies with change in amplitude and frequency for the applied signal of proposed decremental and incremental grounded memristor emulator circuits. It is also controlled by changing the value of capacitors. The derivation of memristance of floating decremental/incremental memristor emulator circuit remains same with only change in applied voltage (Vin1 − Vin2) between input terminals of voltage-tunable FB-VDBA. The memristance M (Φ) of floating decremental/incremental memristor emulator circuits can be easily obtained directly from Eq. (15) and is given in Eq. (16).

The memristance of decremental and incremental floating memristor emulator circuits is also varied after changing the amplitude and frequency of applied sinusoidal signal.

4 Simulation Results and Discussions

The proposed decremental/incremental grounded and floating memristor emulator circuits are simulated using TSMC 0.18 µm CMOS process technology parameters of Mentor Graphics Eldo tool. The supply voltage is used as ± 0.9 V, whereas capacitor value is chosen as 40 pF. The aspect ratios of MOSFETs for the circuit diagram of voltage-tunable FB-VDBA are presented in Table 1.

4.1 Decremental Grounded Memristor Emulator Circuit

The sinusoidal signal having amplitude of 100 mV and frequency of 1 MHz is applied to decremental emulator of Fig. 3. The current–voltage response with respect to time is shown in Fig. 4. To obtain the pinched Hysteresis loops, a periodic sinusoidal waveform (Vm = 100 mV) is applied to input terminal of decremental memristor emulator of Fig. 3. These loops are obtained for different frequencies of input sinusoidal signal as depicted in Fig. 5a–d. It is clearly observed that the decremental grounded memristor emulator circuit performs satisfactorily for the wide range of frequencies. It is also seen from Fig. 5a–d that the loops shrink for increase in frequency. The pinched loops of grounded decremental memristor emulator circuit are shown in Fig. 6 for variations in temperature. It is concluded from Fig. 6 that the Hysteresis loops shrink with increase in the temperature.

4.2 Decremental Floating Memristor Emulator Circuits

The sinusoidal signal having amplitude of 100 mV and frequency of 1 MHz is applied between terminals (Vin1 and Vin2) of decremental memristor emulator of Fig. 4. Current–voltage response of proposed decremental floating memristor emulator circuit is shown in Fig. 7. The pinched loops of decremental floating memristor emulator circuit for different frequencies are shown in Fig. 8a–d. It is concluded from the figures that the pinched Hysteresis loop shrinks when frequency is increased within a suitable range. Figure 9 shows the pinched Hysteresis loops of decremental floating memristor emulator circuit when temperature is varied from − 40 to + 40 °C. It can be concluded from Fig. 9 that the Hysteresis loop of proposed decremental floating memristor emulator circuit is not deformed when temperature is varied from − 40 to +40 °C.

4.3 Behavior of Proposed Memristor Emulator Circuits at Lower Frequencies

The value of memristance depends on both the frequencies of operation and the values of capacitors used in the design of memristor emulator circuits as expressed in Eqs. (15) and (16). The memristance is inversely proportional to the product of angular frequency (ω) and the value of capacitor (C). To maintain the same Hysteresis loops (f = 1 MHz, C = 40 pF) for the lower frequencies, the values of capacitors are appropriately increased. The pinched Hysteresis loops of proposed grounded and floating decremental/incremental memristor emulator circuits are the same for frequencies of 10 Hz, 100 Hz, 1 kHz, 10 kHz and 100 kHz if the values of capacitors are chosen as 4µF, 0.4µF, 40 nF, 4 nF and 0.4 nF, respectively, as shown in Fig. 10a–d. In each case, the product of frequencies (f) and the values of capacitors (C) are the same as in the case of 1 MHz frequency with 40 pF capacitor. Thus, it is concluded that the proposed decremental/incremental memristor emulator circuits can work satisfactorily at lower frequencies with appropriate values of capacitors.

4.4 Monte Carlo Analysis of Proposed Memristor Emulator Circuits

The robustness of the proposed memristor emulator circuits has been checked by Monte Carlo analysis. Monte Carlo analysis is performed for 200 runs, and Gaussian random variations have been given for changing the device parameters such as threshold voltage, aspect ratios of MOSFETs and device parasitic capacitances. It is observed from Fig. 11 that the pinched Hysteresis curves of Monte Carlo analysis is conversed even after change in device parameters and therefore the designs of the proposed decremental and incremental memristor emulator circuits are robust.

4.5 Non-volatility Tests of Proposed Grounded Memristor Emulator Circuits

In order to verify the property of non-volatility, a voltage pulse of 1 MHz frequency has been applied to input terminals of proposed grounded decremental/incremental memristor emulator circuits. The obtained results of non-volatility tests are shown in Fig. 12a, b. It can be seen from Fig. 12a that memristance (MR) decreases from 22 to 16 kΩ during “on” period of the first cycle of input pulse and it retains the value of memristance during “off” period. For the “on” period of second cycle, memristance decreases from 16 to 13 kΩ and retains its value of memristance during “off” period. In the next cycle, the process repeats in the same manner. Therefore, it is concluded that during “off” period of input pulse, memristor emulator circuit retains the previous value of memristance. Similarly, for the incremental grounded memristor emulator circuit, the memristance increases from 14 to 18 kΩ during “on” period of first cycle and holds its value of memristance during “off” period. During “on” period of second cycle, the value of memristance increases again from 18 to 22 kΩ and retains its value of memristance during “off” period Thus, it is concluded that proposed decremental and incremental memristor emulator circuits satisfy the property of non-volatility.

5 Comparison of Proposed Memristor Emulator Circuits with Other Reported Memristor Emulator Circuits in the Literature

The proposed memristor emulator circuits have been compared with other memristor emulator circuits available in the literature as given in Table 2. The following advantages of proposed memristor emulator circuits have been observed.

-

(1)

The memristor emulator circuits reported in (Lopez et al. 2013; Yu et al. 2014; Yesil et al. 2014; Kumngern 2015; Lopez et al. 2015; Kumngern and Moungnoul 2015; Alharbi et al. 2015; Ayten et al. 2017; Babacan et al. 2017; Cam and Sedef 2017; Petrovic 2018) use both analog multiplier as well as active and passive components that results in increased complexity, whereas the proposed memristor emulator only use single active and passive component that leads to simpler configurations.

-

(2)

The frequency range over which memristor emulator works are in the range of hertz (Yu et al. 2014; Babacan and Kacar 2017; Cam and Sedef 2017) and kilohertz (Lopez et al. 2013; Kumngern 2015; Alharbi et al. 2015; Abuelma’atti and Khalifa 2015; Lopez et al. 2015; Kumngern and Moungnoul 2015; Alharbi et al. 2015; Abuelma’atti and Khalifa 2016; Sozen and Cam 2016; Babacan and Kacar 2017; Rashad et al. 2017; Ranjan et al. 2017; Ranjan et al. 2017; Ayten et al. 2017; Babacan et al. 2017; Ranjan et al. 2018; Kanyal et al. 2018), whereas proposed memristor emulator circuits work up to 1 MHz frequency.

-

(3)

The reported memristor emulator circuits in (Lopez et al. 2013; Yu et al. 2014; Yesil et al. 2014; Kumngern 2015; Alharbi et al. 2015; Abuelma’atti and Khalifa 2015; Lopez et al. 2015; Kumngern and Moungnoul 2015; Alharbi et al. 2015; Abuelma’atti and Khalifa 2016; Sozen and Cam 2016; Rashad et al. 2017; Ranjan et al. 2017; Ayten et al. 2017; Babacan et al. 2017; Ranjan et al. 2018; Yadav et al. 2020; Gupta and Rai 2020) use excess number of passive components, whereas only one capacitor is used in proposed memristor emulators.

-

(4)

Only grounded memristor emulator circuit was reported in (Alharbi et al. 2015; Abuelma’atti and Khalifa 2015; Lopez et al. 2015; Kumngern and Moungnoul 2015; Alharbi et al. 2015; Rashad et al. 2017; Ranjan et al. 2017; Ayten et al. 2017; Babacan et al. 2017; Ranjan et al. 2018), whereas both grounded and floating memristor emulator circuits are proposed in this paper.

-

(5)

Memristor emulator circuits reported in (Lopez et al. 2013; Yu et al. 2014; Yesil et al. 2014; Kumngern 2015; Alharbi et al. 2015; Abuelma’atti and Khalifa 2015; Lopez et al. 2015; Kumngern and Moungnoul 2015; Alharbi et al. 2015; Abuelma’atti and Khalifa 2016; Sozen and Cam 2016; Rashad et al. 2017; Petrovic 2018; Ranjan et al. 2018) use resistor, whereas the proposed memristor emulator circuits are resistorless.

-

(6)

Only one active building block is used in the realization of proposed memristor emulator circuits, whereas the memristor emulator circuits reported in (Lopez et al. 2013; Yu et al. 2014; Yesil et al. 2014; Kumngern 2015; Alharbi et al. 2015; Abuelma’atti and Khalifa 2015; Lopez et al. 2015; Kumngern and Moungnoul 2015; Alharbi et al. 2015; Abuelma’atti and Khalifa 2016; Sozen and Cam 2016; Babacan and Kacar 2017; Rashad et al. 2017; Babacan et al. 2017; Cam and Sedef 2017; Petrovic 2018; Yesil 2019; Ranjan et al. 2018; Kanyal et al. 2018) use more than one active building block.

6 Performance Analysis of Proposed Non-Ideal Decremental Grounded Memristor Emulator

In this section, non-ideal characteristics of FB-VDBA are presented first that is followed by the performance analysis of non-ideal grounded decremental memristor emulator circuit. In the non-ideal analysis, role of parasitic impedances become important because it affects the performance of the circuit over certain frequencies of operation.

6.1 Non-Ideal FB-VDBA

Non-ideal model of FB-VDBA (Khatib and Biolek 2013) including parasitic resistances and capacitances of different terminals is shown in Fig. 13. The parasitic resistances are represented by Rp, Rn, Rz−, Rz + , Rw− and Rw + at terminals p, n, z−, z + , w− and w +, respectively, whereas parasitic capacitances are shown by Cp, Cn, Cz− and Cz + at terminals p, n, z− and z + , respectively. Parasitic inductances are presented by Lw + and Lw- at terminals w + and w-, respectively. The parasitic resistances Rp, Rn, Rz + and Rz− appear in parallel with parasitic capacitances Cp, Cn, Cz + and Cz− at terminals p, n, z + and z−, respectively. The parasitic resistances Rw + and Rw− appear in series with parasitic inductances Lw + and Lw− at w + and w− terminals of FB-VDBA, respectively. In ideal case, transconductance (gm) and gain (β) of FB-VDBA are assumed to be constant for all frequencies of operation whereas in the non-ideal case, transconductance (gm) and gain (β) both are the function of frequency and are represented by gm (s) and β(s). Therefore, the terminal characteristics of non-ideal FB-VDBA are given as

Non-ideal model of FB-VDBA (Khatib and Biolek 2013)

where Zp, Zn, Zz−, Zz + , Zw− and Zw + are parasitic impedances of p, n, z + , z−, w + and w− terminals of FB-VDBA.

The transconductance gm(s) can be given as

where gm0 is the transconductance at lower frequencies of operation and ω is the pole frequency.

The gain of buffer amplifier of FB-VDBA can be given as

where, β(0) is the gain at lower frequencies and ωβ is the corresponding pole frequency.

6.2 Performance of Grounded Memristor Emulator Circuit Including Parasitics

Non-ideal equivalent model of proposed grounded memristor emulator circuit is shown in Fig. 14 which includes the effect of parasitic impedances. The parasitic resistance and capacitance (Rp and Cp) appear in parallel at “p” terminal of FB-VDBA and is represented by parasitic impedance Zp. Similarly, parasitic resistance and capacitance (Rn and Cn) are connected in parallel at “n” terminal of FB-VDBA and is represented by parasitic impedance Zn. Parasitic resistance and capacitance (Rz− and Cz−) appear in parallel at “z−” terminal and are represented by parasitic impedance Zz−. Similarly, parasitic resistance and capacitance (Rz+ and Cz+) are connected in parallel at “z+” terminal and are represented by parasitic impedance Zz+. The voltages (Vz+ and Vz−) at z + and z− terminals are copied with the help of internal buffer of FB-VDBA. The parasitic resistance and inductance (Rw− and Lw−) appear in series at “w−” terminal and are represented by parasitic impedance Zw−.

The values of parasitic impedances Zp, Zn, Zz−, Zz+ and Zw− are given by

The routine analysis of Fig. 14 yields the value of current Iz− at intermediate terminal “z−”of FB-VDBA as

where Rs is the source resistance of input voltage Vin.

The current Iz+ of FB-VDBA is the same as obtained in Eq. (25).

The voltage Vz + is obtained at z + terminal of FB-VDBA as

The value of Vz + is obtained with help of Eqs. (26) and (27) as given in Eq. (28).

Since the value of 1/Rz + << s(C + Cz+), Eq. (28) can be modified as

Equation. (29) can be rewritten as

The voltage Vw− can be expressed as given in Eq. (31) after considering the parasitic impedance Zw− of FB-VDBA.

The voltage transfer ratio between z + and w− terminals of FB-VDBA can be defined as

where, β (0) is the voltage transfer ratio between z + and w− terminals of FB-VDBA at dc and ωβ is the corresponding pole frequency.

Replacing the voltage Vz + from Eq. (30) into Eq. (31), the voltage VW− can be written as

The biasing voltage VB is directly connected to VW− in Fig. 14 and can be expressed as

The term \(\int {V_{in} } (t){\text{d}}t\) can be represented by flux (ϕ) and thereby Eq. (34) is now changed to

After replacing the voltage VB from Eq. (35) into Eq. (5), we get

Equation. (36) can be rearranged as

The value of input current Iin’ (t) can be obtained from Fig. 14 as

where R0 is the output resistance of z− terminal of FB-VDBA.

After replacing the current Iz− from Eqs. (25) to (38), we get

The value of memristance \(M(\varphi_{m} )\) for the non-ideal decremental grounded memristor emulator circuit is obtained from Eq. (39) as

When the value of Gm (s) is substituted from Eq. (37) into Eq. (40), we get the value of memristance \(M(\varphi_{m} )\) as

The fixed part of memristance remains same for ideal and non-ideal grounded decremental memristor emulator circuit, whereas variable part is changed due to parasitic impedances at various terminals of FB-VDBA. The value of parasitic capacitance Cz+ is very low, and therefore, the effect of Cz + on the performance of memristor emulator circuit will be negligible. The source resistance value Rs is very low, and therefore, the effect of parasitic impedance Zz− becomes negligible. The voltage gain (β) is very close to one, and it remains in acceptable range up to 1 MHz frequency. The parasitic impedance Zw− appears in series and has negligible effect on the performance of memristor emulator circuits. It is observed from Eq. (41) that the effects of parasitic impedances on the performance of memristor emulator circuits are negligible and thereby its performance is found to be satisfactory in non-ideal conditions.

7 Application of Proposed Floating Decremental Memristor Emulator

The worthiness of proposed floating decremental memristor emulator circuit is verified by using it in the realization of universal biquad filter (Pushkar et al. 2014) as shown in Fig. 15. In universal biquad filter, the floating resistor (R) has been replaced by floating memristance (MR) to verify its performance at high frequency. The average value of memristance (MR) is set to1 kΩ. The values of capacitors are chosen as C1 = C2 = 20 pF and biasing current of voltage differencing inverted buffered amplifier (VDIBA) is chosen as 100 µA. The circuit diagram of VDIBA used to implement universal biquad filter is same as given in (Pushkar et al. 2014). The center frequency (fo) of VDIBA-based universal filter is given as

Universal biquad filter reported in (Pushkar et al. 2014)

The pinched Hysteresis loop of memristor emulator shrinks with the increase in frequency, and it gets converted to a single-valued function when frequency of sinusoidal input is increased beyond a critical frequency. This single-valued function is represented by a resistor. To show the performance of proposed floating decremental memristor emulator as a resistor at high frequency, universal biquad filters have been realized using both the resistor (R) and the proposed memristor (MR). The obtained simulation results depicted in Fig. 16a, b show almost similar behavior and thus the performance of memristor as a resistor at high frequency is verified. The center frequency (f0) has been obtained as 5.7 MHz.

8 Conclusions

New decremental/incremental memristor emulator circuits have been proposed using one fully balanced voltage differencing buffered amplifier (FB-VDBA) and a capacitor. The decremental memristors can be easily obtained from incremental memristors by interchanging the input terminals of voltage-tunable FB-VDBA. These configurations work satisfactorily for wide range of frequencies. Monte Carlo and non-volatility tests have been performed on proposed memristor emulators, and the obtained results are found to be satisfactory. The performance has also been verified by embedding the proposed floating decremental memristor emulator in the design universal biquad filter.

References

Abuelma’atti MT, Khalifa ZJ (2015) A continuous-level memristor emulator and its application in a multivibrator circuit. AEU Int J Electr Commun 69(4):771–775

Abuelma’atti MT, Khalifa ZJ (2016) A new floating memristor emulator and its application in frequency-to-voltage conversion. Analog Integr Circ Sig Process 86(1):141–147

Alharbi, A. G., Khalifa, Z. J., Fouda, M. E., Chowdhury, M. H. (2015). A new simple emulator circuit for current controlled memristor. In: IEEE international conference on electronics, circuits, and systems (ICECS), pp 288–291

Alharbi AG, Fouda ME, Chowdhury MH (2015) A novel memristor emulator based only on an exponential amplifier and CCII + . In: IEEE international conference on electronics, circuits, and systems (ICECS), pp 376–379

Anjanakumari BT, Bhoomika CM, Jugale AA, Ahmed MR (2019) Memristor based relaxation oscillator for biomedical applications. In: 3rd IEEE international conference on trends in electronics and informatics (ICOEI), pp 1–5

Ayten UE, Minaei S, Sagbas M (2017) Memristor emulator circuits using single CBTA. AEU-Int J Electr Commun 82:109–118

Babacan Y, Kacar F (2017) Floating memristor emulator with subthreshold region. Analog Integr Circ Sig Process 90(2):471–475

Babacan Y, Yesil A, Kacar F (2017) Memristor emulator with tunable characteristic and its experimental results. AEU-Int J Electr Commun 81:99–104

Borghetti J, Snider GS, Kuekes PJ, Yang JJ, Stewart DR, Williams RS (2010) Memristive’switches enable ‘stateful’logic operations via material implication. Nature 464(7290):873–876

Cam ZG, Sedef H (2017) A new floating memristance simulator circuit based on second generation current conveyor. J Circ Syst Comput 26(02):1750029

Chew ZJ, Li L (2012) Printed circuit board based memristor in adaptive lowpass filter. Electron Lett 48(25):1610–1611

Chua L (1971) Memristor-the missing circuit element. IEEE Trans Circuit Theory 18(5):507–519

Driscoll T, Quinn J, Klein S, Kim HT, Kim BJ, Pershin YV, Di Ventra M, Basov DN (2010) Memristive adaptive filters. Appl Phys Lett 97(9):1–2

Gupta S, Rai SK (2020) New grounded and floating decremental/incremental memristor emulator circuits based on CDTA and its application. Wireless Personal Commun. https://doi.org/10.1007/s11277-020-07252-y

Hu X, Duan S, Wang L, Liao X (2012) Memristive crossbar array with applications in image processing. Sci China Inf Sci 55(2):461–472

Hussein AI, Fouda ME (2013) A simple mos realization of current controlled memristor emulator. In: 25th IEEE international conference on microelectronics (ICM), pp 1–4

Itoh M, Chua L (2019) Memristor cellular automata and memristor discrete-time cellular neural networks. In: Handbook of Memristor Networks, Springer, pp 1289–1361

Iu HHC, Yu DS, Fitch AL, Sreeram V, Chen H (2011) Controlling chaos in a memristor based circuit using a twin-T notch filter. IEEE Trans Circuits Syst I Regul Pap 58(6):1337–1344

Kanyal G, Kumar P, Paul SK, Kumar A (2018) OTA based high frequency tunable resistorless grounded and floating memristor emulator circuits. AEU-Int J Electr Commun 92:124–145

Khatib N, Biolek D (2013) New voltage-mode universal filter based on promising structure of voltage differencing buffered amplifier. In: 23rd IEEE international conference radioelektronika, pp 177–181

Kim H, Sah MP, Yang C, Chua LO (2010) Memristor-based multilevel memory. In: 12th International IEEE workshop on cellular nanoscale networks and their applications (CNNA), pp 1–6

Kim KH, Gaba S, Wheeler D, Cruz-Albrecht JM, Hussain T, Srinivasa N, Lu W (2012) A functional hybrid memristor crossbar-array/CMOS system for data storage and neuromorphic applications. Nano Lett 12(1):389–395

Kim Y, Yang C, Kim H (2015) Floating memristor emulator circuit. J Inst Electron Inf Eng 52(8):49–58

Kumngern M (2015) A floating memristor emulator circuit using operational transconductance amplifiers. In: IEEE international conference on electron devices and solid-state circuits (EDSSC), pp 679–682

Kumngern M, Moungnoul P (2015) A memristor emulator circuit based on operational transconductance amplifiers. In: IEEE 12th international conference on electrical engineering/electronics, computer, telecommunications and information technology (ECTI-CON), pp 1–5

Kvatinsky S, Kolodny A, Weiser UC, Friedman EG (2011) Memristor-based IMPLY logic design procedure. In: IEEE 29th international conference on computer design (ICCD), pp 142–147

Lehtonen E, Poikonen JH, Laiho M (2010) Two memristors suffice to compute all Boolean functions. Electron Lett 46(3):239–240

Lopez SC, Lopez MJ, Aguilar MAC, Lopez FEM (2013) A simple floating memristor emulator circuit based on current conveyors. In IEEE 10th international conference on electrical engineering, computing science and automatic control (CCE), pp 445–448

Lopez SC, Aguilar MAC, Muniz-Montero C (2015) A 16 Hz–160 kHz memristor emulator circuit. AEU Int J Electr Commun 69(9):1208–1219

Merrikh-Bayat F, Shouraki SB (2010) Memristor-based circuits for performing basic arithmetic operations. Procedia Comput Sci 3:128–132

Muthuswamy B (2010) Implementing memristor based chaotic circuits. Int J Bifurc Chaos 20(05):1335–1350

Muthuswamy B, Chua L (2010) Simplest chaotic circuit. Int J Bifurc Chaos 20(05):1567–1580

Ngouonkadi EM, Fotsin HB, Fotso PL (2014) Implementing a memristive van der Pol oscillator coupled to a linear oscillator: synchronization and application to secure communication. Phys Scr 89(3):1–14

Pérez-Carrasco JA, Zamarreno-Ramos C, Serrano-Gotarredona T, Linares-Barranco B (2010) On neuromorphic spiking architectures for asynchronous STDP memristive systems. In: IEEE International symposium on circuits and systems, pp 1659–1662

Pershin YV, Di Ventra M (2010a) Experimental demonstration of associative memory with memristive neural networks. Neural Netw 23(7):881–886

Pershin YV, Di Ventra M (2010b) Practical approach to programmable analog circuits with memristors. IEEE Trans Circuits Syst I Regul Pap 57(8):1857–1864

Petras I (2010) Fractional-order memristor-based Chua’s circuit. IEEE Trans Circuits Syst II Express Briefs 57(12):975–979

Petrovic PB (2018) Floating incremental/decremental flux-controlled memristor emulator circuit based on single VDTA. Analog Integr Circ Sig Process 96(3):417–433

Pickett MD, Strukov DB, Borghetti JL, Yang JJ, Snider GS, Stewart DR, Williams RS (2009) Switching dynamics in titanium dioxide memristive devices. J Appl Phys 106(7):074508

Pushkar KL, Bhaskar DR, Prasad D (2014) Voltage-mode new universal biquad filter configuration using a single VDIBA. Circ Syst Sig Process 33(1):275–285

Ranjan RK, Rani N, Pal R, Paul SK, Kanyal G (2017a) Single CCTA based high frequency floating and grounded type of incremental/decremental memristor emulator and its application. Microelectron J 60:119–128

Ranjan RK, Raj N, Bhuwal N, Khateb F (2017b) Single DVCCTA based high frequency incremental/decremental memristor emulator and its application. AEU-Int J Electr Commun 82:177–190

Ranjan RK, Sharma PK, Sagar, Raj N, Kumarai B, Khateb F (2018) Memristor emulator circuit using multiple-output OTA and its experimental results. J Circ Syst Comput. https://doi.org/10.1142/S0218126619501664

Rashad SH, Hamed EM, Fouda ME, Abdelaty AE, Said LA, Radwan AG (2017). On the analysis of current-controlled fractional-order memristor emulator. In: IEEE 6th international conference on modern circuits and systems technologies (MOCAST), pp 1–4

Robinett W, Pickett M, Borghetti J, Xia Q, Snider GS, Medeiros-Ribeiro G, Williams RS (2010) A memristor-based nonvolatile latch circuit. Nanotechnology 21(23):235203

Shin S, Kim K, Kang SM (2010) Memristor applications for programmable analog ICs. IEEE Trans Nanotechnol 10(2):266–274

Sotner R, Jerabek J, Herencsar N (2013) Voltage differencing buffered/inverted amplifiers and their applications for signal generation. Radioengineering 22(2):490–504

Sozen H, Cam U (2016) Electronically tunable memristor emulator circuit. Analog Integr Circ Sig Process 89(3):655–663

Strukov DB, Snider GS, Stewart DR, Williams RS (2008) The missing memristor found. Nature Publishing Group 453(7191):80

Talukdar A, Radwan AG, Salama KN (2011a) A memristor-based third-order oscillator: beyond oscillation. Appl Nanosci 1(3):143–145

Talukdar A, Radwan AG, Salama KN (2011b) Generalized model for memristor-based Wien family oscillators. Microelectron J 42(9):1032–1038

Talukdar A, Radwan AG, Salama KN (2012) Non linear dynamics of memristor based 3rd order oscillatory system. Microelectron J 43(3):169–175

Vista J, Ranjan A (2019) A simple floating MOS-memristor for high-frequency applications. IEEE Trans Very Large Scale Integr (VLSI) Syst 27(5):1186–1195

Wang X, Chen Y, Gu Y, Li H (2009) Spintronic memristor temperature sensor. IEEE Electron Device Lett 31(1):20–22

Wey TA, Jemison WD (2011) Variable gain amplifier circuit using titanium dioxide memristors. IET Circuits Devices Syst 5(1):59–65

Yadav Nisha, Rai SK, Pandey R (2020) New grounded and floating memristor emulator circuits using OTA and CDBA. Int J Circuit Theory Appl. https://doi.org/10.1002/cta.2774

Yang JJ, Pickett MD, Li X, Ohlberg DAA, Stewart DR, Williams RS (2008) Memristive switching mechanism for metal/oxide/metal nanodevices. Nat Nanotechnol 3(7):429–433

Yesil A (2018) A new grounded memristor emulator based on MOSFET-C. AEU-Int J Electr Commun 91:143–149

Yesil A (2019) Floating memristor employing single MO-OTA with hard-switching behavior. J Circ Syst Comput 28(02):1950026. https://doi.org/10.1142/S0218126619500269

Yesil A, Babacan Y, Kacar F (2014) A new DDCC based memristor emulator circuit and its applications. Microelectron J 45(3):282–287

Yesil A, Babacan Y, Kacar F (2019a) Electronically tunable memristor based on VDCC. AEU-Int J Electr Commun 107:282–290

Yesil A, Babacan Y, Kacar F (2019b) Design and experimental evolution of memristor with only one VDTA and one capacitor. IEEE Trans Comput Aided Des Integr Circuits Syst 38(6):1123–1132

Yu D, Lu HHC, Fitch AL, Liang Y (2014) A floating memristor emulator based relaxation oscillator. IEEE Trans Circuits Syst I Regular Papers 61(10):2888–2896

Zhi-Jun L, Yi-Cheng Z (2013) A memristor oscillator based on a twin-T network. Chin Phys B 22(4):1–6

Zidan MA, Omran H, Smith C, Syed A, Radwan AG, Salama KN (2014) A family of memristor-based reactance-less oscillators. Int J Circuit Theory Appl 42(11):1103–1122

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Yadav, N., Rai, S.K. & Pandey, R. Novel Memristor Emulators using Fully Balanced VDBA and Grounded Capacitor. Iran J Sci Technol Trans Electr Eng 45, 229–245 (2021). https://doi.org/10.1007/s40998-020-00357-x

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s40998-020-00357-x