Abstract

This paper presents grounded and floating memristor emulators based on current differencing transconductance amplifier. These emulators are realized using current differencing transconductance amplifier, operational transconductance amplifier and a grounded capacitor. Incremental to decremental memristor emulators and vice versa are easily obtained by modifying the circuit slightly. These memristor emulators are very simple in design over other complex realizations reported in the literature. The pinched hysteresis curves have been obtained without using analog multiplier for a wide range of frequency that varies from 600 kHz to 2 MHz. The property of retention has been verified for proposed design of memristor emulators after applying voltage pulse of amplitude 100 mV and frequency 1 MHz. Non-ideal analysis including the effects of parasitic impedances on the behaviour of proposed memristor emulators has also been presented. The proposed designs of memristor emulators have been simulated by Mentor Graphics Eldo simulation tool with TSMC 0.18 µm, level 53, CMOS technology parameters. The performance of proposed memristor emulator is verified by embedding it in the realization of current- mode analog filter.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

The three well-known circuit elements are resistor, capacitor and inductor. Memristor—the contraction of memory and resistor is the fourth fundamental circuit element which was postulated by Chua [1]. Initially, researchers had not shown much interest to work upon memristors due to limited resources available and lack of understanding. In May 2008, researchers of HP lab found a material namely TiO2 which exhibits the behaviour of memristor at nano-scale regime [2]. But, memristor is still unavailable in the market as off-the-shelf component due to difficulties in fabrication and cost issues that restricts its use in real time applications. Therefore, memristor emulators are being designed to mimic its properties using analog active building blocks such as current conveyers (CC), current feedback operational amplifier (CFOA), current conveyer transconductance amplifier (CCTA), current backward transconductance amplifier (CBTA), current differencing buffered amplifier (CDBA), differential difference current conveyor (DDCC), voltage differencing current conveyor (VDCC), differential voltage current conveyor transconductance amplifier (DVCCTA), operational transconductance amplifier (OTA), voltage differencing transconductance amplifier (VDTA) and etc. A floating memristor emulator employing four current conveyors of second-generation (CCII), one multiplier, five resistors and one capacitor was reported in [3]. Another circuit of floating memristor was reported in [4] using four CCIIs, single operational amplifier, single multiplier, eight resistors and a capacitor. Thereafter, incremental/decremental memristor emulators were reported using DDCC, multiplier, two resistors and a grounded capacitor [5]. Afterward, a floating memristor emulator has been reported by using three electronically tunable CCIIs, one multiplier, four resistors and a grounded capacitor [6]. Next, a current controlled memristor emulator circuit using two CCII+, two bipolar junction transistors, one resistor and a capacitor was reported in which both simulations as well as experimental results are shown to verify the realization [7]. A continuous level memristor emulator using two CFOAs, single OTA, three resistors and two grounded capacitors has been reported and is also utilized to design the multivibrator [8]. A memristor emulator was reported by using double output CCII, multiplier, two resistors and a grounded capacitor that works in the frequency range of 16 Hz–16 kHz [9]. Another memristor emulator was reported using electronically tunable DDCC (formed by 6 OTAs), one multiplier, two resistors and a grounded capacitor [10]. A simple memristor emulator design was presented by using a CCII, exponential amplifier and three resistors [11]. The non-linear behaviour of memristor was obtained using CCII and exponential amplifier. A floating memristor emulator was reported using four CFOAs, two diodes, four resistors and four capacitors which were also utilized in the design of frequency to voltage conversion [12]. Thereafter, electronically tunable memristor emulator has been reported using four current conveyors of second generation, three OTAs, six resistors and a grounded capacitor [13]. Next, a floating memristor emulator has been reported using one OTA, two PMOS and one capacitor in which MOSFETs have been used in the sub-threshold region of operation [14]. A current controlled fractional order memristor was reported using two current conveyors of second generation, multiplier, three resistors and one fractional capacitor [15]. Floating and grounded memristor emulators using CCTA, three resistors and a capacitor has been reported in [16]. Thereafter, decremental/incremental memristor emulators that work at higher frequency were designed by using DVCCTA, three resistors and one capacitor [17]. A grounded configuration of memristor emulator using CBTA, multiplier, two resistors and a grounded capacitor was reported in [18]. A tunable memristor emulator was reported in [19] by employing an OTA having multiple outputs, one multiplier and a single capacitor. The arrangement of incremental and decremental memristor emulators has also been suggested by making a slight change in the configuration of reported memristor emulator. A second generation current conveyor based floating incremental/decremental memristor emulators have been presented using four current conveyors of second generation, multiplier, three resistors and one grounded capacitor [20]. A floating memristor was realized by employing a VDTA, one multiplier, two resistors and a capacitor. Both incremental and decremental configurations can be formed with a slight change suggested in the paper [21]. A floating memristor emulator using an OTA and a grounded capacitor has been reported in which both pre-layout and post-layout simulation results have been included [22]. A memristor emulator was designed using seven MOSFETs and a grounded capacitor [23]. Next, a memristor emulator by using four OTAs, three resistors and one capacitor has been reported in [24] which were utilized in the design of high pass filter. A resistor-less grounded/floating memristor emulators using two OTAs and a capacitor has been reported in which both incremental and decremental configurations have been suggested [25]. A floating memristor emulator using VDCC, two PMOS transistors and one grounded capacitor has been reported [26]. A floating memristor emulator realized by employing VDTA and MOS-capacitor has been reported in [27]. A memristor emulator using three floating MOSFETs and a grounded capacitor has been reported in which both simulation and experimental results have been included [28]. A memristor emulator reported in [29] uses three current conveyors of second generation, one multiplier, three resistors and one grounded capacitor. Memristor emulator reported in [30] uses four CFOAs, two multipliers and nine resistors that operates only up to 10 Hz frequency. Recently, a memristor emulator is reported using OTA, CDBA and capacitor that operates up to 1 MHz frequency [31].

It has been observed that most of the reported structures of memristor emulators use multipliers to achieve the non-linear characteristics of memristor and also use passive resistors that lead to complex circuitry. Few memristor emulators that do not employ analog multiplier and passive resistors provide hysteresis loop which limited up to only few kHz frequencies. In some research papers, only grounded decremental configurations of memristor emulators have been reported. Therefore, the paper aims to design new resistor-less, high-frequency, floating and grounded decremental/incremental memristor emulators using one CDTA, one OTA and a capacitor. The proposed designs of memristor emulators are simpler as compared to other designs available in the literature because analog multiplier has not been used. CDTA and OTA both perform well at higher frequencies and therefore, in the proposed memristor emulators, pinched hysteresis curves have been formed for higher frequencies. The incremental to decremental memristor emulators and vice versa can be obtained by slight modification in the circuit. The performance of these memristor emulators has been shown by embedding it in the realization of analog filter.

The formation of paper is as follows. The paper has total eight sections comprising introduction. In Sect. 2, characteristics of both voltage tunable CDTA and voltage tunable OTA with their circuit diagrams are presented. Section 3 covers the realization of proposed floating and grounded decremental/incremental memristor emulators. Simulation results have been presented and discussed in Sect. 4. Section 5 covers the non-ideal analysis of proposed memristor emulators including parasitic impedances. In Sect. 6, performance of proposed memristor emulators has been compared with other reported memristor emulators. One application of analog filter has been included to prove the worthiness of proposed memristor emulators in Sect. 7. Concluding remarks are given in Sect. 8.

2 Characteristics of Voltage Tunable CDTA and OTA

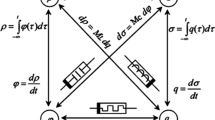

Current differencing transconductance amplifier consists of two stages namely current differencing unit (CDU) that is followed by the transconductance amplifier (TA) as shown in Fig. 1. The input impedance of CDTA is very low whereas its output impedance is high. It accepts two currents Ip and In as inputs and provides the difference of these currents at z terminal as given in Eq. (1). Voltage Vz is obtained by connecting impedance Zz at z terminal and is given by Eq. (2). Transconductor converts the voltage Vz in two currents which are equal in amplitude and opposite in phase and is given by Eq. (3). The structure of CDTA is slightly modified in which the bias current IB is obtained using a current mirror structure constituted by MOSFETs M19, M20 and M21. The transconductance of voltage tunable CDTA depends on both bias voltage (VB1) and technology parameters (μn and Cox) as given in Eq. (4). The circuit diagram of voltage tunable CDTA is given in Fig. 2.

where \(k = \mu_{n} C_{ox.} \frac{W}{L}.\)

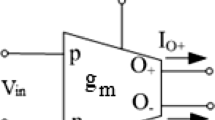

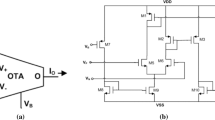

The symbol and circuit diagram of voltage tunable operational transconductance amplifier (OTA) are shown in Figs. 3 and 4, respectively. Two voltages Vin1 and Vin2 are applied to input terminals of OTA that gives two output currents Io + and Io- by its transconductance (gm) as given in Eq. (5). The structure of OTA is slightly modified in which the bias current IB is provided by structure of current mirror constituted by MOSFETs M13, M14 and M15. The variation in IB is achieved by varying the bias voltage VB2 applied at gate terminal of MOSFET M13. The transconductance of voltage tunable OTA is obtained as given in Eq. (6) where k is \(\mu_{n} C_{ox} \frac{W}{L}\).

3 Proposed Configurations of Grounded and Floating Memristor Emulators

The proposed design of grounded and floating decremental/incremental memristor emulators are shown in Fig. 5a–d. In grounded decremental memristor emulator of Fig. 5a, one terminal of OTA is grounded whereas in floating decremental memristor emulator of Fig. 5b, both terminals are kept at different voltages. These grounded and floating decremental memristor emulators of Fig. 5a, b can be converted easily into grounded and floating incremental memristor emulators of Fig. 5c, d by interchanging the ‘+’ and ‘−’ terminals of OTA. The simple analysis of the circuit of Fig. 5a lead to following equations

The voltage across capacitor is given as

After substituting the value of Ic (t) from Eq. (8) into Eq. (9), we get

where \(\phi_{in} = \int {V_{in} (t)dt}\) is flux generated in memristor emulator.

Substituting the value of VB2 from Eq. (10) into Eq. (6), the value of transconductance is obtained as given in Eq. (11)

Substituting the value of Gm from Eq. (11) into Eq. (7), the value of memristance is obtained as given in Eq. (12)

It is clearly seen from Eq. (12) that the first part of the equation is fixed whereas the second part is variable. Therefore, it can be concluded from Eq. (12) that memresistance M (Φ) of decremental memristor emulator is varied with change in flux (Φin) generated in the circuit. The decremental memristor emulators can be changed into incremental memristor emulators after modifying the Eq. (12) as results in Eq. (13). The same is obtained in the circuit after interchanging the ‘+’ and ‘−’ terminals of OTA as shown in Fig. 5a, b.

After applying sinusoidal voltage \(V_{m} \sin \omega t\) to grounded memristor emulator, the flux Φin results in

where Vm is the maximum amplitude of the applied sinusoidal signal and ω is the frequency in radian/sec.

After substituting the value of Φin from Eq. (14) into Eqs. (12) and (13), we get

From Eq. (15), it can be concluded that the memristance M (ɸ) of proposed grounded memristor emulators depend on the amplitude and operating frequency of the sinusoidal signal. It can be easily derived that the memristances M (Φ) of floating decremental and incremental memristors are

The memristances M (Φ) of floating memristor emulators are also dependent on both amplitude and frequency of the input sinusoidal signal.

4 Simulation Results

The proposed designs of memristor emulators are simulated by Mentor Graphics Eldo simulation tool with TSMC 0.18 µm, level 53, CMOS technology parameters. The supply voltages for both CDTA and OTA are chosen as ± 0.9 V. Biasing currents of CDTA are selected as IB1 = IB2 = 30 µA. The value of bias voltage VB1 is 550 mV for CDTA. The value of capacitor is 40 pF. The amplitude of sinusoidal input signal is 100 mV. The aspect ratios of MOSFETs for voltage tunable CDTA and OTA are listed in Table 1.

4.1 Simulation Results of Proposed Grounded Decremental/Incremental Memristor Emulators

To obtain the transient response, a sinusoidal input signal (Vm = 100 mV, f = 1 MHz) is applied at input terminals of proposed grounded incremental memristor emulator. It is evident from transient response of Fig. 6 that the voltage and current are opposite in phase for proposed grounded incremental configuration of memristor emulator. The voltage–current pinched hysteresis curves attained by proposed grounded decremental memristor emulators are illustrated in Fig. 7a–d for different frequencies of 600 kHz, 800 kHz, 1 MHz and 2 MHz. It is concluded from the figures that the decremental grounded memristor emulator works well for a wide range of frequency. It can be observed that the size of hysteresis curve decreases with increase in frequency. Figure 8 shows the effect of different temperatures on grounded decremental memristor emulator. It is observed that hysteresis loop shrinks with increase in temperature. The voltage-current pinched hysteresis curves of grounded incremental memristor emulators are illustrated in Fig. 9a–d. It is evident that the pinched hysteresis curves are not deformed for a wide range of frequency that varies from 600 kHz to 2 MHz. It gives satisfactory outputs for variations in temperatures from − 40 to + 40 °C as shown in Fig. 10.

4.2 Simulation Results of Proposed Floating Decremental/Incremental Memristor Emulators

A sinusoidal input signal (Vm = 100 mV, f = 1 MHz) is applied to obtain the transient response of proposed floating decremental memristor emulator. The transient response of decremental memristor emulator is shown in Fig. 11. The voltage–current pinched hysteresis curves of proposed floating decremental memristor emulator for frequencies of 600 kHz, 800 kHz, 1 MHz and 2 MHz are shown in Fig. 12a–d, respectively. The hysteresis curves of memristor emulators decrease with increase in frequency. Figure 13 shows the effect of temperature varying from − 40 to + 40 °C on the voltage–current pinched hysteresis loop of floating decremental memristor emulator. The hysteresis loop of proposed floating decremental memristor emulator is not deformed for temperature variations as can be seen from Fig. 13. The voltage–current hysteresis curves of proposed floating incremental memristor emulators are depicted in Fig. 14a–d. It can be seen that hysteresis curves shrink when operating frequency is increased. The performance of proposed floating incremental memristor emulators is satisfactory even after variations in temperature from − 40 to + 40 °C as hysteresis loop is not deformed as shown in Fig. 15.

4.3 Monte Carlo Simulation Results of Proposed Memristor Emulators

Monte Carlo analysis have been performed for 200 runs to prove the robustness of the proposed design of memristor emulators. The sinusoidal signal having amplitude of 100 mV and frequency of 1 MHz is applied at input terminals of proposed memristor emulators. The deviations in the parameters such as aspect ratios, threshold voltages and capacitances are chosen as gaussian random variations. The pinched hysteris curves obtained for proposed memristor emulators are shown in Fig. 16a–d. It is clearly observed that voltage–current pinched hysteris curves of Monte Carlo analysis are conversed and therefore the performances of proposed memristor emulators are satisfactory.

4.4 Current Versus Time Plot for Pulse Input

In order to show the property of retention, the performance of proposed grounded memristor emulators has been analysed after applying a voltage pulse of 1 MHz frequency for a fixed “on” and “off” period. The obtained current versus time plots are given in Fig. 17a, b. It is observed from Fig. 17a that the input current of grounded incremental memristor emulator starts decreasing in the “on” period of input voltage and retained its value for the “off” period. In the next cycle, the value of input current retained in the previous cycle decreases. Therefore, it is concluded that the memristance (opposite of current) increases for the “on” period and retained its value for the “off” period of input pulse for the grounded incremental memristor emulator. The same has been verified for proposed grounded decremental memristor emulator and is shown in Fig. 17b. Therefore, it is observed that the proposed memristor emulators hold the property of retention.

5 Non-ideal Analysis of Proposed Grounded Decremental Memristor Emulator

The performance of proposed grounded decremental memristor emulator is analysed after considering non-ideal effects of CDTA and OTA. Non-ideal model of CDTA and OTA including parasitic effects at different terminals are considered for non-ideal analysis. The non-ideal effects on the performance of grounded decremental memristor emulator are discussed in this section.

5.1 Characteristics of Non-ideal CDTA

The non-ideal CDTA is shown in Fig. 18. The characteristic equations of non-ideal CDTA after considering parasitic resistances and capacitances are given as

where Rp and Rn are the parasitic resistances of input terminals (p and n) of CDTA, αp and αn are current transfer ratios between p to z terminals and n to z terminals, respectively. Transconductance tracking error from z to x+ and z to x− terminals are given as β. In ideal-CDTA, parasitic resistances Rp and Rn are considered zero whereas current tracking errors (αp and αn) and transconductance tracking error (β) are considered one.

5.2 Characteristics of Non-ideal OTA

The non-ideal OTA shown in Fig. 19 includes parasitic resistance Rin+ that appears in parallel with parasitic capacitance Cin+ at input “+” terminal. Similarly, parasitic resistance Rin− that appears in parallel with parasitic capacitance Cin− at input “−” terminal. The parasitic resistance Ro+ is connected in parallel with parasitic capacitance Co+ at output “o+” terminal while parasitic resistance Ro− appears in parallel with parasitic capacitance Co− at output “o−” terminal. The transconductance of OTA cannot be maintained at constant value for all operating frequencies. Therefore, it is a function of frequency and is represented by Gm(s). Therefore, the output current Io+ is given by

where Vin is the difference of Vin+ and Vin−.

The transconductance Gm(s) can be represented by

where Gm0 is transconductance at dc that get reduced as pole frequency ω is increased.

5.3 Performance of Proposed Memristor Emulator Considering Non-ideal Effects

The non-ideal equivalent circuit of proposed memristor emulator is shown in Fig. 20. The various parasitic impedances (Zp1, Zp2, Zp3, Zp4 and Zp5) connected at different terminals of OTA and CDTA can be given as

The output currents I0−(t) and I0+ (t) at “o−” and “o+” terminals of OTA are given as

The current at intermediate terminal Z of CDTA can be expressed as

where αP represents current tracking error of P to Z terminal and RP represents parasitic resistance at input terminal “p” of CDTA.

After substituting the value of I0+ (t) from Eqs. (22) to (23), we get

The z′ terminal is directly connected to x′− terminal of CDTA in Fig. 20. Due to parasitic impedance Zp4 that appears at z′ terminal of CDTA, a current tracking error αc will be introduced between z′ and x′− terminal of non-ideal CDTA which results in

The value of Vc(t) can be easily calculated from Fig. 20 as

As the value of 1/Rx + ≪ s (C + Cx+), Eq. (26) is now approximated as

Equation (27) can be expressed as

The biasing voltage VB is equal to Vc (t) and can be expressed as

The term \(\int {V_{in} (t)dt}\) is the flux generated in memristor emulator and can be substituted by flux ɸin. Thus the Eq. (29) can be modified as

After substituting the value of VB in Eq. (6), we get

The Eq. (31) can be rearranged as

The input current Iin′ (t) is obtained from Fig. 20 as

where R0 represents the output resistance of OTA.

After substitution of current Io−(t) from Eqs. (22) to (33)

The value of memristance \(M(\phi_{m} )\) is obtained from Eq. (34) for non-ideal memristor emulator as

The value of memristance is obtained after replacing the value of Gm (s) from Eq. (32) into Eq. (35) as

Rearranging the terms of Eq. (36) results in

The value of Zp1||Zp2 is very high as compared to R0, therefore Eq. (37) is reduced to

Rearranging the terms of Eq. (38) leads to

The values of current transfer ratios αc and αp are very close to unity. The parasitic capacitance Cx+ is found to be very low as compared to capacitor C. The source resistance (Rs) value is quite low. The parasitic resistances Ro+ and Ro− are very high and are in the range of several hundred KΩ. The value of RP is very low. After taking these considerations, the value of memristance \(M(\phi_{m} )\) obtained by Eq. (39) will be in close proximity of memristance derived under ideal assumptions. Therefore, the behaviour of memristor emulator under non-ideal assumption is satisfactory.

6 Performance Comparison of Memristor Emulators

The comparison of proposed memristor emulators has been done in Table 2 on the basis of number of active and passive components used in the design of memristor emulators, range of frequency over which it works satisfactorily, supply voltage used and different types of configurations realized. Memristor emulators reported in [3, 5, 6, 9,10,11, 18, 19, 21, 29, 30] use analog multipliers and therefore circuits become complex whereas proposed memristor emulators do not employ multiplier that leads to simpler realizations. Memristor emulators reported in [3, 6, 8,9,10,11,12,13,14, 18, 19, 29, 30] work satisfactorily in the frequency range of Hz and KHz only. Memristor emulator reported in [5, 17] operate in MHz range but their frequency of operation is limited to 1 MHz frequency. Memristor emulator suggested in [25] give different frequency of operation for grounded and floating type configurations whereas proposed memristor emulators perform well up to 2 MHz frequency for both grounded and floating configurations. Excess active and passive components are used in the realization of memristor emulators reported in [3, 5, 6, 8,9,10,11,12,13,14, 17,18,19, 29, 30] whereas proposed configuration of memristor emulators use two active and one passive component only. The proposed memristor emulators realize both grounded and floating configuration whereas memristor emulator reported in references [8,9,10,11, 17,18,19, 29] realize only grounded configuration. The memristor emulators reported in [3, 5, 6, 8,9,10,11,12,13, 17,18,19, 21, 29, 30] use resistors while the proposed memristor emulators do not employ resistors. Memristor emulators reported in [3, 5, 6, 8,9,10,11,12,13,14, 17, 19, 25, 29, 30] use higher supply voltage as compared to proposed configurations of memristor emulators. Therefore, proposed memristor emulators are superior in performance as compared to other designs available in the literature.

7 Application of Grounded Memristor Emulator in Current-Mode Tow–Thomas Biquad

Tow–Thomas biquad is a standard filter realized by CDTAs as shown in Fig. 21. The proposed grounded decremental memristor emulator of Fig. 5a has been used as a memristor MR (replacing R) in the realization of Tow–Thomas biquad. The grounded memristor emulator offers average memristance (MR) of 1 KΩ for the sinusoidal input signal of amplitude (Vm) 100 mV and frequency of 2 MHz. The value of VB is adjusted to 0.9 V. The bias current of CDTA is set to 100 µA which offers the transconductance (gm) to 0.574 mA/V. The center frequency (f0) of filter is given by

Current-mode Tow–Thomas biquad realized by CDTAs [32]

Figure 22 shows the responses of low pass; band pass and high pass for Tow–Thomas biquad when 1 K resistor (R) is connected at z terminal of CDTA 1. The center frequency is obtained as 1.8 MHz. The frequency responses of low pass, band pass and high pass biquad after connecting memristor (MR) is shown in Fig. 23 which also offers the same center frequency of 1.8 MHz. Transient responses of Tow–Thomas biquad after connecting memristor (MR) are shown in Figs. 24, 25 and 26. Figure 24 shows the response of Tow–Thomas biquad when low frequency sinusoidal signal of 50 Hz is applied. It is observed that filter provides gain only for low pass output whereas band pass and high pass outputs get attenuated. Similarly, when an input sinusoidal signal of 1 MHz is applied to filter, it provides gain to low pass, band pass and high pass because it is closer to center frequency as shown in Fig. 25. When a high frequency input sinusoidal signal of 20 MHz is applied, it provides gain only to high pass while other two outputs namely low pass and high pass get attenuated as shown in Fig. 26. Therefore, it is concluded from transient responses of Tow–Thomas biquad that the behaviour of grounded memristor emulator as a memristance (MR) is good enough over a wide frequency range.

8 Conclusions

New grounded and floating configurations of decremental and incremental memristor emulators have been proposed. The designs of memristor emulators are very simple as compared to other designs available in the literature as analog multiplier has not been used. The voltage–current hysteresis curves obtained by these emulators are not deformed over a wide frequency range and ensure the operation of emulators from low to high frequency range. The performance of grounded memristor emulator has been verified by using it in the design of current-mode Tow- Thomas biquad. It gives almost the same performance and center frequency when resistor (R) is replaced by memristance (MR) offered by memristor emulators.

References

Chua, L. (1971). Memristor-the missing circuit element. IEEE Transactions on Circuit Theory,18(5), 507–519.

Strukov, D. B., Snider, G. S., Stewart, D. R., & Williams, R. S. (2008). The missing memristor found. Nature Publishing Group,453(7191), 80.

Lopez, S. C., Lopez, M. J., Aguilar, M. A. C., & Lopez, F. E. M. (2013). A simple floating memristor emulator circuit based on current conveyors. IEEE 10th international conference on electrical engineering, computing science and automatic control (CCE) (pp. 445–448).

Yu, D., Ching Iu, H. H., Fitch, A. L., & Liang, Y. (2014). A floating memristor emulator based relaxation oscillator. IEEE Transactions on Circuits and Systems I: Regular Papers,61(10), 2888–2896.

Yesil, A., Babacan, Y., & Kacar, F. (2014). A new DDCC based memristor emulator circuit and its applications. Microelectronics Journal,45(3), 282–287.

Kumngern, M. (2015). A floating memristor emulator circuit using operational transconductance amplifiers. In IEEE international conference on electron devices and solid-state circuits (EDSSC) (pp. 679–682).

Alharbi, A. G., Khalifa, Z. J., Fouda, M. E., & Chowdhury, M. H. (2015). A new simple emulator circuit for current controlled memristor. In: IEEE international conference on electronics, circuits, and systems (ICECS) (pp. 288–291).

Abuelma’atti., M. T., & Khalifa, Z. J. (2015). A continuous-level memristor emulator and its application in a multivibrator circuit. AEU-International Journal of Electronics and Communications,69(4), 771–775.

Lopez, S. C., Aguilar, M. A. C., & Muniz-Montero, C. (2015). A 16 Hz–160 kHz memristor emulator circuit. AEU-International Journal of Electronics and Communications,69(9), 1208–1219.

Kumngern, M., & Moungnoul, P. (2015). A memristor emulator circuit based on operational transconductance amplifiers. In IEEE 12th international conference on electrical engineering/electronics, computer, telecommunications and information technology (ECTI-CON) (pp. 1–5).

Alharbi, A. G., Fouda, M. E., & Chowdhury, M. H. (2015). A novel memristor emulator based only on an exponential amplifier and CCII+. In IEEE international conference on electronics, circuits, and systems (ICECS) (pp. 376–379).

Abuelma’atti, M. T., & Khalifa, Z. J. (2016). A new floating memristor emulator and its application in frequency-to-voltage conversion. Analog Integrated Circuits and Signal Processing,86(1), 141–147.

Sozen, H., & Cam, U. (2016). Electronically tunable memristor emulator circuit. Analog Integrated Circuits and Signal Processing,89(3), 655–663.

Babacan, Y., & Kacar, F. (2017). Floating memristor emulator with subthreshold region. Analog Integrated Circuits and Signal Processing,90(2), 471–475.

Rashad, S. H., Hamed, E. M., Fouda, M. E., AbdelAty, A. E., Said, L. A., & Radwan, A. G. (2017). On the analysis of current-controlled fractional-order memristor emulator. In IEEE 6th international conference on modern circuits and systems technologies (MOCAST) (pp. 1–4).

Ranjan, R. K., Rani, N., Pal, R., Paul, S. K., & Kanyal, G. (2017). Single CCTA based high frequency floating and grounded type of incremental/decremental memristor emulator and its application. Microelectronics Journal,60, 119–128.

Ranjan, R. K., Raj, N., Bhuwal, N., & Khateb, F. (2017). Single DVCCTA based high frequency incremental/decremental memristor emulator and its application. AEU-International Journal of Electronics and Communications,82, 177–190.

Ayten, U. E., Minaei, S., & Sagbas, M. (2017). Memristor emulator circuits using single CBTA. AEU-International Journal of Electronics and Communications,82, 109–118.

Babacan, Y., Yesil, A., & Kacar, F. (2017). Memristor emulator with tunable characteristic and its experimental results. AEU-International Journal of Electronics and Communications,81, 99–104.

Cam, Z. G., & Sedef, H. (2017). A new floating memristance simulator circuit based on second generation current conveyor. Journal of Circuits, Systems and Computers,26(02), 1750029.

Petrovic, P. B. (2018). Floating incremental/decremental flux-controlled memristor emulator circuit based on single VDTA. Analog Integrated Circuits and Signal Processing,96(3), 417–433.

Yesil, A. (2019). Floating memristor employing single MO-OTA with hard-switching behavior. Journal of Circuits, Systems and Computers,28(02), 1950026. https://doi.org/10.1142/S0218126619500269.

Yesil, A. (2018). A new grounded memristor emulator based on MOSFET-C. AEU-International Journal of Electronics and Communications,91, 143–149.

Ranjan, R. K., Sharma, P. K., Sagar., Raj, N., Kumari, B., & Khateb, F. (2018). Memristor emulator circuit using multiple-output OTA and its experimental results. Journal of Circuits, Systems and Computers. https://doi.org/10.1142/s0218126619501664.

Kanyal, G., Kumar, P., Paul, S. K., & Kumar, A. (2018). OTA based high frequency tunable resistorless grounded and floating memristor emulators. AEU-International Journal of Electronics and Communications,92, 124–145.

Yesil, A., Babacan, Y., & Kacar, F. (2019). Electronically tunable memristor based on VDCC. AEU -International Journal of Electronics and Communications,107, 282–290.

Yesil, A., Babacan, Y., & Kacar, F. (2019). Design and experimental evolution of memristor with only one VDTA and one capacitor. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems,38(6), 1123–1132.

Vista, J., & Ranjan, A. (2019). A simple floating MOS-memristor for high-frequency applications. IEEE Transactions on Very Large Scale Integration VLSI Systems,27(5), 1186–1195.

Hassanein, A. M., Elsafty, A. H., Said, L. A., Madian, A. H., & Radwan, A. G. (2018). Incremental grounded voltage controlled memristor emulator. In 2018 30th international conference on microelectronics (ICM) (pp. 156–159).

Xie, X., Zou, L., Wen, S., Zeng, Z., & Huang, T. (2019). A flux-controlled logarithmic memristor model and emulator. Circuits, Systems, and Signal Processing,38(4), 1452–1465.

Yadav, N., Rai, S. K., & Pandey, R. (2020). New grounded and floating memristor emulators using OTA and CDBA. International Journal of Circuit Theory and Applications. https://doi.org/10.1002/cta.2774.

Uygur, A., & Kuntman H. (2005). Design of a Current differencing transconductance amplifier (CDTA) and its application on active filters. In 13th IEEE conference on signal processing and communication applications (pp. 340–343).

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Gupta, S., Rai, S.K. New Grounded and Floating Decremental/Incremental Memristor Emulators Based on CDTA and Its Application. Wireless Pers Commun 113, 773–798 (2020). https://doi.org/10.1007/s11277-020-07252-y

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11277-020-07252-y