Abstract

This study proposes a low complex and high efficient dual-reference voltage-based pulse width modulation (DRV-PWM) scheme for three-phase five-level hybrid active neutral-point-clamped (HANPC) inverters. Although phase-shifted carrier PWM (PSC-PWM) is capable of naturally balancing dc-link and flying capacitors voltages, such a process requires a tedious and sophisticated adjustment of the phase-shift between the PWM signals, particularly in a digital signal processor (DSP). As a result, a phase-delay eventually occurs, which leads to unevenly distributed thermal losses among the three phases of the five-level HANPC inverter. Therefore, this study introduces an alternative switching scheme that has the same merits as the conventional PSC-PWM in naturally balancing the voltages without requiring voltage sensors. It also balances the thermal losses across the three phases, which enhances the reliability and efficiency of the switching devices. The proposed DRV-PWM is experimentally evaluated in comparison to conventional PSC-PWM on a TMS320F28377S DSP. The experimental results reveal that the proposed DRV-PWM effectively synchronizes the execution of the three-phase pole voltages while also keeping the thermal losses evenly distributed among the three phases.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Multilevel converters are widely used in a variety of industrial applications, including those related to renewable energy, motor drives, and power transmission [1,2,3]. These converters are preferred due to their high power density, good power quality, low dv/dt, and the low voltage stress they exert on the switching devices [4]. The neutral-point clamped (NPC) inverter is one type of multilevel converter. In contrast to other types of multilevel inverters, such as the flying capacitor and cascaded H-bridge, the NPC inverter does not require flying capacitors or isolated dc-link sources [2]. However, as the number of levels in the output voltage increases, the number of diodes required also increases, which leads to uneven distribution of switching losses and a reduction in the overall efficiency of the inverter.

To address these issues with the NPC inverter, some hybrid variations of the NPC inverter have been proposed and implemented in industries. One such variation is the five-level active NPC (ANPC) inverter, which was first introduced in 2005 [5], then commercialized by ABB in 2010 in their 800 kW 6 kV transformer-less ACS 2000 drive [6]. This type of inverter is popular due to the fact that it requires fewer active switching devices and capacitors. It is an extension of the three-level hybrid ANPC (HANPC) inverter [7,8,9,10] and incorporates an additional two active switches and one flying capacitor per phase (Cfx).

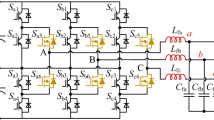

As shown in Fig. 1, this design utilizes three different cells: Cell-I, Cell-II, and Cell-III. Si IGBT switching devices are employed in Cell-I whereas SiC MOSFET switching devices are used in Cell-II and Cell-III; this is intended to achieve better performance in the high switching frequency (fsw) range. Using all SiC MOSFETs in the five-level inverter design would significantly increase the cost while only slightly improving system performance. On the other hand, if all Si IGBTs were to be used, then the cost would decrease but the performance would deteriorate at high fsw range. Therefore, the criteria for this arrangement are a balance between effective performance, reliability, and cost [11].

Prior studies have presented several modulation techniques that can be used to control the five-level HANPC inverter, including selective harmonics elimination pulse width modulation (SHE-PWM) [12], phase disposition carrier PWM (PDC-PWM) [13], and phase shifted carrier PWM (PSC-PWM) [14]. While the SHE-PWM technique is capable of balancing the voltage across the Cfx, it is complex and requires a predefined lookup table to store as many voltage control angels as possible to reduce output voltages and currents total harmonic distortion (THD) [15]. This process could result in a slow response control of the inverter and increase its complexity. On the other hand, although PDC-PWM offers fast response control with low computational requirements compared to SHE-PWM, it leads to a more distorted output voltage due to non-uniformly distributed switching and conducting losses [16].

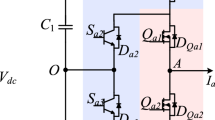

The PSC-PWM modulation technique is effective in balancing the flying capacitor voltages in comparison to the PDC-PWM technique, but it requires two inverted PWM carriers, vtri-1 and vtri-2, to create the five-level output pole voltage vxn, as shown in Figs. 2 and 3. Table 1 presents the eight possible voltage states of the five-level HANPC inverter, which can be controlled by the switching mechanism of the PSC-PWM modulation technique. As a result, natural voltage balancing is achieved in dc-link capacitors C1 and C2 at Vdc/2, and Cfx at Vdc/4, where x represents A-, B-, or C-phase. Nevertheless, implementing PSC-PWM modulation technique on a digital signal processor (DSP) is a challenging task due to the need to compensate for the time-delay (Td,PWM) caused by the PWM modulator [17].

Recently, a few studies have addressed the issue mentioned above regarding Td,PWM [18,19,20,21,22,23,24,25,26,27]. For example, in [20], the authors proposed a synchronized PSC-PWM for a cascaded H-bridge multilevel inverter. Although this approach results in reduced fsw and switching losses, it suffers from undesirable uncontrolled and noneliminated harmonics. Another approach involves using compensatory techniques such as lead-lag compensators and predictive control [17, 26, 27]. However, these methods are limited in their ability to effectively compensate for computation delay. For example, the lead-lag compensator has been found to only achieve limited compensation effects, and to amplify high-frequency noise. Meanwhile, predictive control relies on past information and the plant model to estimate future information, and it is therefore susceptible to model errors caused by changes in circuit parameters, which can lead to prediction bias and negatively impact control performance and system stability.

Moreover, PWM methods have gained attention as a mean of compensating for computation delay [20, 23, 24]. By moving the sampling instant closer to the PWM loading instant, the computation delay can be reduced substantially. Nevertheless, this approach can still introduce aliasing and switching noise problems. Asymmetric PWM is another method that has been shown to effectively compensate for computation delay, but it may limit the variable range of duty ratios and introduce extra harmonics. Moreover, real-time compensation with dual sampling mode and real-time loading has been proposed as a means of completely eliminating computation delay [18, 22]; however, this method is currently only applicable to single-phase converters due to its reliance on unipolar and frequency-doubling modulation.

Multisampling PWM techniques have been used in recent years to address computation delay in various applications [19]. However, despite their popularity in DSP platforms, multisampling technology has several key issues, such as switching noise, nonlinearities, and vertical crossing DSPs, which may affect the overall performance of the system. In addition, methods such as digital-filter-based delay compensation, including high-pass filter, Smith predictor, and linear predictor, have been proposed, but the compensation effect is limited in the high-frequency range, and high-frequency noise may even be amplified [21].

Therefore, the present paper proposes a low complexity and high efficiency dual-reference voltage-based pulse width modulation (DRV-PWM) scheme as an alternative control scheme for three-phase five-level HANPC inverters. The DRV-PWM does not require sophisticated phase adjustments to achieve a desirable control of this topology without Td,PWM. Instead, it simplifies the control structure without requiring two PWM carriers. Hence, its implementation on a DSP is less complex, and it does not require the PWM phase tuning between Cell-II and Cell-III. As a result, it is achievable to have balanced losses distributions among the three phases of the five-level HANPC inverter due to the elimination of Td,PWM. Further, switching devices could have higher reliability, and overall efficiency would increase. This is demonstrated by sets of experimental trials comparing the operation of the inverter under the conventional PSC-PWM and proposed DRV-PWM.

The rest of this paper is organized as follows. Section II presents the switching scheme and the limitations of the conventional PSC-PWM technique. Section III introduces the proposed DRV-PWM method. Section IV provides information on the intensive experimental verifications that were conducted. Finally, Section V presents the conclusions of this study.

2 Conventional PSC-PWM and its Limitations

2.1 Switching Scheme

Unlike other modulation schemes that are used to control the five-level HANPC inverter, the PSC-PWM can be considered one of the best candidates due to its robust and natural ability to balance the voltage across C1 and C2 at Vdc/2 and Cfx at Vdc/4. The switching losses are also evenly distributed among the switching devices. Figure 3 shows a demonstration diagram of the conventional PSC-PWM. For clarity of the switching mechanism of the conventional PSC-PWM, fsw has been set at 1.3 kHz. As can be seen from Fig. 2, the process of generating the switching states for the Si-IGBT Sx1–Sx4 and SiC-MOSFET Sx5–Sx8 are processed according to the fundamental frequency or line frequency (fo) of 50 Hz for each phase.

To begin, the three phases’ reference voltages v*xs can be expressed as shown in (1),

where vm represents the voltage magnitude, which corresponds to MI.

Secondly, the pole voltage (v*xn) needs to be generated by injecting a zero-sequence signal (v*sn) to extend the MI to (2/√3 ≈ 1.15), which improves the THD characteristics of the load current and reduces the switching losses [28]. v*sn can be calculated by considering the absolute values of the maximum and minimum reference voltages v*A, v*B, and v*C, respectively, as in (2),

Due to the nature of the three-phase system, v*sn is switching fo three times. Therefore, v*xn can be expressed as in (3),

To effectively simplify the algorithm of conventional PSC-PWM, v*xn needs to be normalized while considering Vdc as expressed in (4),

where TBPRD is the time-based period peak value of PWM counter in the DSP. The next step is to convert T*x into T*xx as depicted in the block diagram in Fig. 2. This process could reduce the number of the required PWM carriers to half of the original number. T*xx can be calculated as shown in (5),

To satisfy the requirements for generating five-level output vxn, two PWM triangular carriers, vtri-1 and vtri-2, need to be included in the structure of the switching scheme with a 180° phase-shift, as shown in Fig. 3. The switching principle for Sx1–Sx4 in Cell-I depends on T*x. This means they are switching at fo. Hence, the switching rules are given by (6),

By contrast, Cell-II and Cell-III turn ON and OFF in a complementary manner, when comparing T*xx with vtri-1 and vtri-2, respectively, as expressed in (7),

However, this scheme results in a generation of vxn with balanced voltage across Cfx as well as C1 and C2, and the implementation process for a three-phase five-level HANPC inverter is going to be complicated due to the need to generate the switching signals from a single DSP without Td,PWM.

2.2 Limitations of Implementing PSC-PWM on DSPs

It should be noted that the three-phase five-level HANPC inverter requires twenty-four switching signals. Therefore, it is excessively complicated to generate those switching signals from a single DSP due to the limitation of PWM channels and/or other factors such as synchronization process. As a result, a twenty-four PWM-channel single DSP TMS320F28377S from Texas Instruments [29] is selected to perform the execution of the control algorithm. Although this DSP provides switching for all switching devices of the three-phase five-level HANPC inverter, the synchronization process between Cell-II and Cell-III is complex, as shown in Fig. 4. There is also a delay due to the implementation process, as shown in Fig. 5.

To implement the synchronization process to maintain the same switching principle of generating interleaved PWM carriers, as shown in Fig. 5, there is a need to eliminate the Td,PWM, which is a challenging task. It is necessary to have interrupt signals for vtri-1 and vtri-2 to ensure the same switching scheme as the conventional PSC-PWM method. To satisfy this condition, dual-synchronization is implemented as shown in Fig. 4. The first synchronization is related to vtri-1, while the second one is for vtri-2. Updating those interrupt signals twice at the same time creates a time delay, which results in undesirable switching that does not satisfy the control of the five-level HANPC inverter.

3 Proposed DRV-PWM

3.1 Proposed Switching Scheme

Due to the limitations of the conventional PSC-PWM presented in the previous section, there is a need for an effective yet less complex alternative control algorithm for the five-level HANPC inverter. The proposed switching scheme is based on generating dual-reference voltage signals T*xx-1 and T*xx-2 to avoid the complexity involved in implementing the conventional PSC-PWM in a single DSP. T*xx-1 and T*xx-2 are both extracted simultaneously from (5), as shown in Fig. 6, and expressed mathematically as shown in (8),

The proposed DRV-PWM approach maintains a similar switching principle achieved by (6) for Cell-I due to switching at fo. However, Cell-II and Cell-III are turning ON and OFF at fsw in a complementary manner by comparing T*xx-1 and T*xx-2 with only one triangular carrier, vtri-1, as expressed in (9),

This process satisfies the requirements for operating the five-level HANPC inverter without the need for two PWM carriers or complex phase shift tuning inside the DSP. The new switching states generated by the proposed DRV-PWM are tabulated in Table 2.

3.2 Implementation on DSPs

Regardless of the advancements that have been achieved in DSPs used to controlling the three-phase five-level hybrid active NPC inverter, it is necessary to support twenty-four PWM channels. The proposed DRV-PWM does not require any phase-shift tuning between Cell-II and Cell-III of this topology, as shown in Fig. 7. Moreover, the reference voltages are designed alternatively to achieve the desired five-level vxn without any abnormal distortion among the three phases. It is worth noting that the switching signals sent to Cell-III do not require any phase-shifting or time-based synchronization; instead, T*xx-2 is compared with vtri-1 as indicated in (9) and shown in Fig. 8, so a simple hardware implementation is achieved.

Further, Fig. 8 shows a time-based implementation of the proposed DRV-PWM. Unlike the conventional PSC-PWM, the interrupt signals for loading and sampling the switching signals for Cell-II and Cell-III required to implement the proposed DRV-PWM are less complex. This process simplifies the whole system and eliminates the Td,PWM that might appear during the generation of Sx5–Sx8.

4 Experimental Results and Discussion

4.1 Experimental Hardware Setup

To verify the effectiveness of the proposed DRV-PWM for a three-phase five-level hybrid active NPC inverter, the experimental hardware setup shown in Fig. 9 is used. It consists of a combination of three cells, control, and power parts. Cell-I consists of six Si IGBT module (SK75GBB066T), developed by SEMIKRON, where each module consists of four Si IGBT devices and their gate drives. The other two cells (i.e., Cell-II and Cell-III) contain the SiC MOSFET (C2M0040120D) developed by CREE. It is worth noting that there is one Cfx per phase, which is connected in parallel between Cell-II and Cell-III. The type of Cfx is selected to be a film capacitor type to handle high fsw with lower capacitance ratings than electrolytic capacitors [11].

In the control part, a single TMS320F28377S DSP board is used as a control board, which is supplied by a 5 V DC power supply. There are also two boards connected to the DSP board and used for the PWM signals and the analogue-to-digital converter (ADC). In the power part, C1 and C2 are used to smooth the DC power supplied to the inverter and connected to two voltage sensors that send their signals to the ADC and then on to the DSP control board. The complete list of experimental specifications is presented in Table 3. To achieve high fsw at 30 kHz, TBPRD is denoted as expressed in (10),

where EPWMCLK is the maximum clock used for EPWM in the TMS320F28377S DSP [29].

4.2 Hardware Execution Time of Conventional and Proposed Methods

The experimental results of hardware execution time for the conventional PSC-PWM and proposed DRV-PWM techniques are shown in Fig. 10. It can be seen from the figure that the proposed DRV-PWM requires less computational time than the conventional PSC-PWM. This difference is not substantial, because the TMS320F28377S DSP is an advanced microcontroller, which includes some predefined functions such as TBPHS for setting the phase-shift. However, there is still a Td,PWM because of the sophisticated tuning of the phase-shift between the three-phases, particularly in Cell-II and Cell-III, as illustrated in the aforementioned section.

The proposed DRV-PWM has the merits of maintaining the simplicity of the hardware coding for generating the switching signals. As explained in the previous section, the proposed method does not require any complex phase-shift tuning between Cell-II and Cell-III to achieve the desired output signals to construct vxn. Conversely, the conventional technique requires an additional coding to create a phase-shift between the switching signals sent to Cell-II and Cell-III. This increases the system complexity and restricts its flexibility from executing other functions properly. Undesirable switching signals are also present in the output waveforms.

4.3 Comparative Experimental Results of Conventional PSC-PWM and Proposed DRV-PWM

Figure 11 shows the experimental validation of the conventional and proposed switching techniques when MI is 1.15. In Fig. 11a, it can be seen that the conventional PSC-PWM can be implemented with sophisticated tuning of phase-shift among switching signals to achieve a similar form of vxn with undesirable switching that leads to high distortion in vxn. Nevertheless, the proposed DRV-PWM solves the issue of Td,PWM as shown in Fig. 11b. This results in less distorted vxn with a 5.7% improvement in the THD, as can be clearly seen from the fast Fourier transform (FFT) analysis of vxn in Fig. 11a and b for the conventional and proposed switching methods, respectively.

Other sets of experimental results are given in Figs. 12 and 13 for the conventional and proposed techniques, respectively. These results show the three-phase output voltage and current waveforms. It can be seen from these figures that the conventional PSC-PWM suffers from Td,PWM issue, which results in asynchronous switching. This leads to higher voltage stress on some switching devices, which in turn degrades system reliability. Meanwhile, the proposed DRV-PWM generates a synchronous output voltage and current waveforms as desired. Moreover, the results shown in Fig. 14a highlight the effects of Td,PWM in disturbing the switching signals in the difference phases, where it can be seen that the A phase has clearer effects as the peaks of the vtri-1 and vtri-2 and other PWM signals are generated with respect to it, as shown in Fig. 4. The black-line triangular in this figure is magnified in Fig. 15a. In addition, the area near zero crossing (i.e., circle black-line area) also showed the disturbance on the switching signals and output vxn. The proposed method effectively eliminates the effects of the uneven losses distribution and PWM switching signals as shown in Figs. 14b and 15b, respectively. Thus, voltage stress and losses can be evenly distributed among three-phase switching devices.

4.4 Numerical Comparative Analysis of Thermal Losses for Conventional PSC-PWM and Proposed DRV-PWM

To verify the capability of the proposed DRV-PWM technique to balance the thermal losses among the among three-phase switching devices, the system was operated at full MI for an hour using the conventional PSC-PWM. This procedure was repeated for the proposed PSC-PWM after allowing the system to completely cool down. The results were taken using a thermal camera, and are shown in Figs. 16, 17, and 18.

Figure 16 depicts the effectiveness of the proposed DRV-PWM in reducing and balancing the thermal losses of Sx7 and Sx8 among the three phases of the five-level HANPC inverter. To obtain a detailed thermal measure of Sx7 and Sx8 in each phase, close-up measurements were taken as shown in Figs. 17 and 18 for the conventional and proposed techniques, respectively. It can be seen in Fig. 17 that the conventional PSC-PWM results in unevenly distributed thermal losses among three phases.

For example, SC7 and SC8 have the highest thermal losses, where the junction temperature TJ reaches a maximum value of 90.4 °C, and where the maximum temperature obtained in other two phases are at ≈ 66 °C. On the other hand, the proposed DRV-PWM maintains the maximum TJ at 72.7 °C for SC7 and SC8, whereas A-phase and B-phase achieve relatively lower temperatures of 63.1 °C and 60.9 °C, respectively. This is due to the total control time-delay of whole system. A summary of the thermal losses comparison between the conventional and proposed switching schemes is presented in Fig. 19. It can be seen that the proposed DRV-PWM technique manages to balance the thermal losses among the switching devices of the three-phase five-level HANPC inverter. Conversely, the conventional PSC-PWM method results in more stress on the C-phase. Therefore, the reliability and efficiency of system is enhanced by implementing the proposed DRV-PWM.

5 Conclusion

This study presents a less complex but still effective and efficient DRV-PWM scheme for three-phase five-level HANPC inverters that can be used as an alternative to the conventional phase shifted PSC-PWM method. The proposed DRV-PWM simplifies the control structure by eliminating the need for complex phase adjustments and additional PWM carriers; therefore, it is recommended for various microcontrollers. The proposed switching scheme also results in a balanced distribution of thermal losses among the three phases, along with improved reliability and efficiency of the switching devices. The implementation process of the proposed DRV-PWM was explained and experimentally validated using a TMS320F28377S DSP. The results showed that the execution of the three-phase pole voltages was effectively synchronized, and that a balanced distribution of thermal losses was maintained. Further, the proposed DRV-PWM simplifies the hardware coding for generating the switching signals and improves the THD by 5.7%. Overall, the proposed DRV-PWM can be effectively implemented in three-phase five-level HANPC inverters to balance the switching losses and achieve optimal control of this topology.

References

Kouro S et al (2010) Recent advances and industrial applications of multilevel converters. IEEE Trans Ind Electron 57(8):2553–2580

Abu-Rub H, Holtz J, Rodriguez J, Baoming Ge (2010) Medium-voltage multilevel converters—State of the art, challenges, and requirements in industrial applications. IEEE Trans Ind Electron 57(8):2581–2596

Rodriguez J, Bernet S, Steimer PK, Lizama IE (2010) A survey on neutral-point- clamped inverters. IEEE Trans Ind Electron 57(7):2219–2230

Lee K-B, Lee J-S (2017) Reliability improvement technology for power converters. Springer, Singapore

Barbosa P, Steimer P, Steinke J, Winkelnkemper M, Celanovic N (2005) Active neutral-point-clamped (ANPC) multilevel converter technology. In: Proceeding of the European conference on power electronics and applications, Dresden, Germany, 2005, pp 1–10

Kieferndorf F, Basler M, Serpa LA, Fabian JH, Coccia A, Scheuer GA 2010 ANPC-5L technology applied to medium voltage variable speed drives applications. In: Proceedings of the IEEE SPEEDAM 2010, pp 1718–1725

Guan Q-X et al (2018) An extremely high efficient three-level active neutral-point-clamped converter comprising SiC and Si hybrid power stages. IEEE Trans Power Electron 33(10):8341–8352

Halabi LM, Alsofyani IM, Lee KB (2021) Multi open/short circuit fault-tolerance using modified SVM technique for three-level HANPC converters. IEEE Trans Power Electron 36:13621–13633

Halabi LM, Alsofyani IM, Lee KB (2021) Hardware implementation for hybrid active NPC converters using FPGA-based dual pulse width modulation. J Power Electron 21:1669–1679

Hakami SS, Halabi LM, Lee KB (2023) Dual-carrier-based PWM method for DC-link capacitor lifetime extension in three-level hybrid ANPC inverters. IEEE Trans Ind Electron 70:3303–3314

Hakami SS, Lee KB (2022) Proper flying capacitor selection for performance enhancement of five-level hybrid active neutral-point-clamped inverters. J Power Electron 22:1687–1698

Pulikanti SR, Agelidis VG (2011) Hybrid flying capacitor based active neutral-point-clamped five-level converter operated with SHE-PWM. IEEE Trans Ind Electron 58(10):4643–4653

Wang K, Zheng Z, Li Y, Liu K, Shang J (2013) Neutral-point potential balancing of a five-level active neutral-point-clamped inverter. IEEE Trans Ind Electron 60(5):1907–1918

Li C, Wang S, Guan Q, David Xu (2017) Hybrid modulation concept for five-level active-neutral-point-clamped converter. IEEE Trans Power Electron 32(12):8958–8962

Dahidah MS, Konstantinou G, Agelidis VG (2015) A review of multilevel selective harmonic elimination PWM: formulations, solving algorithms, implementation and applications. IEEE Trans Power Electron 30:4091–4106

Kim M-S, Lee D-C (2023) Balancing control scheme of DC-link capacitor voltages for five-level hybrid T-type inverters without auxiliary circuit. J Power Electron 23:467–477

Nussbaumer T, Heldwein ML, Gong G, Round SD, Kolar JW (2008) Comparison of prediction techniques to compensate time delays caused by digital control of a three-phase buck-type PWM rectifier system. IEEE Trans Ind Electron 55:791–799

Lin Z, Ruan X, Zhang H, Liguo Wu (2022) A generalized real-time computation method with dual-sampling mode to eliminate the computation delay in digitally controlled inverters. IEEE Trans Power Electron 37(5):5186–5195

He S, Zhou D, Wang X, Zhao Z, Blaabjerg F (2022) A review of multi-sampling techniques in power electronics applications. IEEE Trans Power Electron 37(9):10514–10533

Yan B, Huang H, Wang H (2023) PSC-PWM modulated MPC for cascaded H-bridge power supplies. J Power Electron 23:746–757

Zhu K, Sun P, Wang L, Zhou L, Xiong Du (2019) Control delay compensation scheme based on non-instantaneous loading and pulse-width equivalence for active damping of LCL-type inverters. IET Power Electron 12(9):2389–2399

Yang D, Ruan X, Heng Wu (2015) A real-time computation method with dual sampling mode to improve the current control performance of the LCL-Type grid-connected inverter. IEEE Trans Ind Electron 62(7):4563–4572

Deng H, Oruganti R, Srinivasan D (2005) PWM methods to handle time delay in digital control of a UPS inverter. IEEE Power Electron Lett 3:1–6

Wang C, Xiao L, Wang C, Xin M, Jiang H (2019) Analysis of the unbalance phenomenon caused by the PWM delay and modulation frequency ratio related to the CPS-PWM strategy in an MMC system. IEEE Trans Power Electron 34(4):3067–3080

Xu T, Gao F, Zhou L (2016) Practical implementation of global synchronous pulse width modulation with time delay compensation and distributed calculation capabilities. In: Proceedings of the 2016 IEEE energy conversion congress and exposition 2016, pp1–6

Jo S-I, Lee W-J (2023) Compensation method of PWM inverter output voltage under low sampling-to-fundamental frequency ratio operating conditions. J Power Electron 23:904–912

Elhassan G, Zulkifli SA, Pathan E, Khan MH, Jackson R (2021) A comprehensive review on time-delay compensation techniques for grid-connected inverters. IET Renew Power Gener 15:251–266

Kim S-H (2017) Electric motor control: DC, AC, and BLDC motors. Elsevier, Amsterdam

Texas Instruments. TMS320F2837XS microcontrollers technical reference manual. https://www.ti.com/product/TMS320F28377S

Acknowledgements

This work was supported in part by the Korea Institute of Energy Technology Evaluation and Planning (KETEP) and the Ministry of Trade, Industry & Energy (MOTIE) of the Republic of Korea under Grant 20206910100160 and Grant 20225500000110.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Hakami, S.S., Halabi, L.M. & Lee, KB. High Efficiency and Low Complexity Dual-Reference Voltage-Based Pulse Width Modulation for Three-Phase Five-Level HANPC Inverters. J. Electr. Eng. Technol. 19, 3047–3057 (2024). https://doi.org/10.1007/s42835-023-01763-x

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s42835-023-01763-x