Abstract

In this paper, a balancing control scheme of DC-link capacitor voltages for five-level hybrid T-type (5L-HT) inverters is proposed, where existing auxiliary balancing circuit is eliminated. The 5L-HT inverter has a significant advantage of the reduced number of devices compared with other five-level inverter topologies. However, this inverter requires an auxiliary balancing circuit, which is used to rectify the voltage imbalance at the DC-link capacitors, and thus negates the competitiveness of this topology in terms of device count and converter volume. To eliminate the auxiliary circuit, a carrier-overlapped PWM (COPWM) is applied in place of the conventional level-shifted PWM (LSPWM) to control the neutral-point currents, where the duty ratios of switches are adjusted by PI controllers. As a result, although the THD of the output voltage is rather increased, the cost and volume are saved by 27% and 52%, respectively, for a 1-MW/6.6-kV system. The effectiveness of the proposed balancing control method for the 5L-HT inverter has been verified through the simulation and experimental results for the prototype hardware.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Various types of multi-level inverter (MLI) topologies have been studied and developed for medium and high-voltage applications for several decades since they have several advantages, such as lower total harmonic distortion (THD), reduced voltage stress of devices, low dv/dt, reduced electromagnetic interference (EMI), etc. [1,2,3,4].

There are three typical types of MLI topologies, namely neutral-point-clamped (NPC), flying-capacitor (FC) and cascaded H-bridge (CHB) inverters. The three typical topologies have a common disadvantage that the number of required devices increases significantly as the voltage level becomes higher. In addition, the NPC inverter has the drawback that the loss of the switches is distributed unequally, the FC inverter has the complexity of control and the CHB inverter requires an independent isolated DC source for each bridge circuit [5,6,7,8]. Therefore, lots of researchers have explored and developed various topologies with the reduced number of devices, modulation technique and capacitor voltage balancing control for various applications such as photovoltaic (PV) inverters, motor drives, grid-connected systems and electric vehicles (EV) [9,10,11,12,13,14,15,16,17].

A five-level hybrid T-type (5L-HT) inverter topology, which consists of two half-bridge (HB) cells and one 3L-T-type cell per phase, has been proposed in [18]. The number of devices and power loss of the 5L-HT inverter are significantly reduced compared with other types of five-level inverters [19,20,21,22,23,24]. However, it is difficult to maintain the voltages of DC-link capacitors with the conventional level-shifted pulse-width modulation (LSPWM) over the full range of the modulation index (MI) [19, 24, 25]. Hence, an auxiliary balancing circuit (ABC) had to be used in [18]. The ABC consists of two active switches, two inductors and one diode. This circuit supports to boost the middle capacitor voltages as a boost DC–DC converter. However, the rated voltage of the auxiliary devices is relatively high, and the large volume of the inductors is a burden.

Meanwhile, a carrier-overlapped pulse-width modulation (COPWM) has been proposed to control the DC-link capacitor voltage for NPC type of inverters [26, 27]. In the COPWM, two carriers are basically level-shifted, and the other carriers are modified by being bent at particular points between two level-shifted carriers. In the LSPWM, all voltage levels are generated in a fundamental period (50/60 Hz). To change the voltage level, the large change of duty ratio is required in the LSPWM. On the other hand, in the COPWM, all voltage levels are generated in a carrier period. So, the COPWM can create different voltage levels with a very small change in duty ratio, which makes it possible to control the neutral-point current generated according to each voltage level. Therefore, the COPWM has the flexibility to control the DC-link capacitor voltage without significantly affecting THD of output current.

In this article, a balancing control scheme of the DC-link capacitor voltage for the 5L-HT inverter without the auxiliary balancing circuit is proposed. For this purpose, the COPWM is applied to control the duty ratio of each switch. The effectiveness of the balancing capability of the DC-link capacitor voltage for the 5L-HT inverter is verified by the various simulation results for medium-voltage and high-power applications. Moreover, the experimental verification for a prototype hardware set-up is provided.

2 Structure and operation scheme of 5L-HT inverter

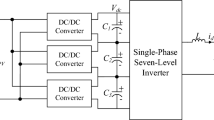

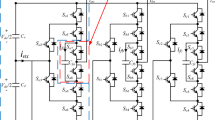

Figure 1 shows the three-phase circuit diagram of the 5L-HT inverter. The inverter consists of a 3L-T-type cell and two HB cells per phase and four common DC-link capacitors. The 5L-HT inverter requires only 24 active switches and four DC-link capacitors without any clamping diode and flying capacitor. Comparing with other type of 5L-inverters, the number of devices is significantly reduced. A comparison of several five-level inverter topologies is listed in Table 1 [19,20,21,22,23,24].

Figure 1a shows the 5L-HT inverter with the auxiliary balancing circuit (ABC) needed for the DC-link capacitor voltage control. The ABC consists of two active switches, one diode and two inductors. Since the middle capacitors (\({C}_{1}, {C}_{2})\) of the 5L-HT inverter are naturally discharged when the LSPWM is applied, the ABC is utilized to boost the capacitor voltages. Likewise, the voltage balancing control can be easily achieved with the ABC, but the additional cost should be paid and the system volume is bulky.

The auxiliary switches (\({S}_{\mathrm{aux}1},{S}_{\mathrm{aux}2}\)) and diode (\({D}_{\mathrm{aux}})\) require the high-voltage rated devices. The blocking voltage of additional devices is calculated as:

where \({V}_{{S}_{\mathrm{auxn}}}\), \({V}_{\mathrm{Laux}}\) and \({V}_{{D}_{\mathrm{aux}}}\) are the voltage stress of auxiliary active switches, inductor and diode, respectively. The maximum voltage stresses across active switches and diode are approximately \({V}_{\mathrm{dc}}/2\) and \({V}_{\mathrm{dc}}\), respectively.

The voltage fluctuation of the DC-link capacitors is caused due to neutral-point (NP) currents. The switching states for the 5L-HT inverter and the NP currents according to the voltage level are listed in Table 2, where the letter “x” means the phase and the “1” and “0” indicate ON and OFF state of switches, respectively. When the voltage level is either \({V}_{\mathrm{dc}}\) or 0, the NP current does not flow through DC-link capacitors, and thus barely affects the capacitor voltages. However, NP currents \({i}_{N1}\), \({i}_{N2}\) and \({i}_{N3}\) flow through each neutral point when the voltage level is \({3V}_{\mathrm{dc}}/4\), \({V}_{\mathrm{dc}}/2\) and \({V}_{\mathrm{dc}}/4\), respectively. These NP currents causes the capacitor voltage imbalance. So, the NP currents need to be controlled to suppress the voltage imbalance, by which the ABC can be eliminated. The 5L-HT inverter without the ABC is shown in Fig. 1b.

From Table 2, the pole voltage VxN is expressed by the sum of four switching states as.

where \({S}_{\mathrm{xn}}\) is the state of switch in phase x.

3 Modulation and balancing control of DC-link capacitor voltage scheme

If the LSPWM is applied to the 5L-HT inverter, the DC-link capacitor voltage is not able to be controlled only by modulation technique. Since the modulation technique has the carriers with the different level in the same phase, the duty ratio of each device cannot be adjusted as long as the reference voltage waveform is not modified in a carrier period. Therefore, in this work, a carrier-overlapped PWM (COPWM) is applied to the 5L-HT inverter to eliminate the ABC, which has the distorted and level-shifted carriers [26,27,28]. Since these modified carriers can produce all voltage levels from 0 to Vdc in a switching period, the duty ratio can be adjusted with no voltage distortion which is an issue in the LSPWM.

The concept of the COPWM is shown in Fig. 2. The COPWM for five-level inverters has two level-shifted and two bent carriers. It is hard to implement in DSP due to the distorted characteristics of carriers. Alternatively, the equivalent transformation with a single carrier and multi-reference voltages is performed rather than multi-carriers and a single reference voltage. The reference voltage is given by

where m, \(\omega\) and \(\theta\) is the modulation index (MI), fundamental angular frequency and phase angle of the voltage. The offset voltage is injected into the reference voltage, which can extend the utilization of the DC-link voltage by 15.5%. The offset component is given by [19]

The equivalent transformation from multi-carriers to multi-references is calculated according to the polarity of the reference voltage as

where \({v}_{\mathrm{ref}xn}\) and \({v}_{\mathrm{ref}xn}\) are multi-reference voltage and duty ratios of switches, respectively\(.\)

The multi-reference voltages are normalized between 0 and 1 through the equivalent transformation, which means that the multi-reference voltages are equal to duty ratios of switches.

The NP currents flow through the \({N}_{1}\), \({N}_{2}\) and \({N}_{3}\) when the voltage level is \({3V}_{dc}/4\), \({V}_{dc}/2\) and \({V}_{dc}/4\), respectively. From Fig. 2a and b, the NP currents in a carrier period are expressed as

where \({i}_{N1x}\), \({i}_{N2x}\) and \({i}_{N2x}\) are NP currents flowing through \({N}_{1}\), \({N}_{2}\) and \({N}_{3}\), respectively. The NP currents are expressed as the product of the difference between duty ratios of the two consecutively numbered switches and the output current of each phase, which means that the NP currents are determined according to the duty ratio and the output current (\({i}_{ox}\)).

The voltage fluctuations at the DC-link capacitors are caused by the NP currents. Figure 3 shows the flow of NP currents according to the voltage level. Assuming that the DC-link capacitance is \({C}_{1}={C}_{2}={C}_{3}={C}_{4}=C\), the deviation voltage of capacitors is expressed as

where \({T}_{s}\) is a sampling period. The fluctuation of capacitor voltages is affected by NP currents.

For balancing the DC-link capacitor voltages in the 5L-NPC inverter with the COPWM [27], three voltage relations are controlled by adjusting the duty ratios, so that \({\Delta V}_{c2}\) = \(\Delta {V}_{c3}\) and \({(\Delta V}_{c2}+{\Delta V}_{c3})\) = \({(\Delta V}_{c1}+{\Delta V}_{c4})\) can be achieved. In addition, \(\Delta {V}_{c1}\) = \(\Delta {V}_{c4}\) can be obtained by injecting the zero-sequence voltage (ZSV), which is complex to implement. In this work, however, the balancing algorithm is simplified by controlling equally the deviations of the two adjacent capacitor voltages (\({\Delta V}_{c1}\) = \({\Delta V}_{c2}, {\Delta V}_{c2}\) = \({\Delta V}_{c3}\) and \({\Delta V}_{c3}\) = \({\Delta V}_{c4})\) without the injection of ZSV. The difference of voltage deviation in the two adjacent DC-link capacitors is expressed by

where n means the device number, which is ranged from 1 to 3.

In (10), parameters \({T}_{s}\) and C are constant values. So, capacitor voltage can be regulated only by adjusting the duty ratios \({d}_{x(n+1)}\) and \({d}_{x(n)}\) depending on the polarity of the output current \({i}_{ox}\). If the polarity of the output current is positive and \({\Delta V}_{c(n+1)}>{\Delta V}_{c(n)}\), the capacitor voltages \({V}_{c(n)}\) and \({V}_{c(n+1)}\) need to be charged and discharged, respectively. Accordingly, the variance of duty ratio \({\Delta d}_{ad(n)}\) is added to \({d}_{x(n+1)}\) and subtracted from \({d}_{x(n)}\). Since the variance of total duty ratio needs to be zero to avoid the deviation in the average output voltage, both the amounts of the increased duty ratio and the decreased one should be equal.

Let’s consider that there is an imbalance condition between \({V}_{c2}\) and \({V}_{c3}\), where it is assumed that \({V}_{c2}\) is higher than \({V}_{c3}\). The difference between two voltages is calculated as

and, if the polarity of \({i}_{\mathrm{ox}}\) is positive, \({d}_{x2}\) needs to be increased and \({d}_{x3}\) to be decreased. Then, the adjusted amount of duty ratios is expressed as

Since the increment and decrement in duty ratios are equal, there is no change in the total duty ratio.

Next, it is necessary to control the difference between the sum of the outer capacitor voltages and that of the inner capacitor voltages, which is the same process as the aforementioned example. The adjustment of duty ratio for balancing control is summarized in Table 3 and the control block diagram is shown in Fig. 4. The adjustments (\({\Delta d}_{\mathrm{ad}1}, {\Delta d}_{\mathrm{ad}2})\) of duty ratio are performed by PI controllers. The letter “sgn” indicates the signum function to determine the output current polarity.

Finally, the adjusted amounts of duty ratio are added to the original duty ratio. So, the resultant duty ratio is given by

4 Evaluation of THD of output voltage and cost

In this section, the THD of output voltage is analyzed in the cases with and without the auxiliary circuit and the cost evaluation is performed for a 1-MW/6.6-kV system. The system parameters are listed in Table 4.

The comparison of THDs of the line-to-line voltage between the LSPWM with the ABC and the COPWM without the ABC is shown in Fig. 5. At the low modulation MIs, the THD of line-to-line voltage in both cases are similar. At the medium and high MIs, the THD in the COPWM case is worse since the bent carriers are used for the modulation process. However, harmonic components of output current are simply filtered by inductive loads. So, THD of output current is enough low [26,27,28].

The auxiliary balancing circuit requires the additional devices, which are two active switches, one diode, and two inductors. The voltage rating of additional devices is high, which is known from (1) and (2). To operate the ABC, it is required that the active switches should be able to withstand the half of the DC-link voltage and that the diodes do the full DC-link voltage. The auxiliary inductor is designed as [29]:

where \(\overline{{I }_{\mathrm{aux}}}\) is the average current of inductor. The inductance is determined depending on the allowable range of current ripple (x %) and maximum duty ratio \({d}_{\mathrm{max}}\) of the additional switches.

For the 1-MW/6.6-kV 5L-HT inverter, FF450R33T3E3 (3300 V/450A) model and DD500S65K3 (6500 V/500A) are selected for dual IGBT switches [30] and dual diode module [31] and C44UOGT7110M52K (900 V/1.1mF) are selected for the DC-link capacitors [32]. However, two diodes need to be connected in series to withstand the entire input voltage. For an auxiliary inductor, the allowable range of current ripples is set to 40%. The maximum duty ratio is limited to 0.8 and the average current from the simulation is obtained as about 200 A, but it is set to 400 A for the margin of safety. As a result, the auxiliary inductance is selected as 2.5 mH and the HCS-801 M is selected as the auxiliary inductors which has parameters of 0.8 mH and 350 A [33]. The estimation of cost and volume for the 5L-HT inverter and the auxiliary balancing circuit are listed in Table 5.

As listed in Table 5, the significant savings of cost and volume can be achieved by eliminating the auxiliary circuit. For example, for the 5L-HT inverter with 1-MW/6.6-kV system, the total cost and volume are saved by 27% and 52%.

5 Simulation results

To verify the performance of the 5L-HT inverter, simulations have been conducted under diverse conditions. The simulation parameters are summarized in Table 4.

Figure 6 shows the simulation result at a MI for the 5L-HT inverter without the ABC. Figure 6a and b show the line-to-line voltage and output current, where their THDs are 32.2% and 1.18%, respectively. The ripple of the outer capacitor voltage is larger than that of the inner one since the utilization of the outer capacitor is dominant when generating the high-voltage levels. Figure 6c shows the outer capacitor voltages. Voltage ripples of both outer capacitors are 1.5%. The voltage fluctuation is within the allowable range of \(\pm\) 10% of the reference value. Figure 6d shows the inner capacitor voltages. Both inner capacitor voltages are regulated with smaller ripples compared to those of the outer capacitor voltages. So, the four DC-link capacitor voltages are well controlled by adjusting the duty ratio without the auxiliary balancing circuit.

Figure 7 shows the simulation result at the low MI (MI = 0.2). The THD of line-to-line voltage and output current is 77% and 1.14%, respectively. The THD value is similar to that of LSPWM with the ABC. In the low modulation index region, the voltage of the four DC-link capacitors is still well regulated, and the voltage ripple is low.

Figure 8 shows the simulation result at the variable modulation index, where the amplitude modulation index and frequency modulation index vary equally (\({m}_{a}={m}_{f}=MI)\). The MI is increased by 0.2 from 0.1 to 0.9 every 0.1 s. The voltages of the four DC-link capacitors are well controlled while the amplitude and frequency of reference voltage are changed. The maximum ripple of the capacitor voltage is similar to the ripple at a unity MI. For the variable-voltage and variable-frequency operation, the balancing control ability allows the reasonable range of the voltage ripple (\(\pm\) 10% of the reference value). Figure 9 shows the simulation result at the load transient condition. At t = 0.05, the load is increased from 50 to 100% of rated power in a step. The proposed control scheme for the 5L-HT inverter is effective against the load variation. The outer capacitor voltage is controlled with the 1.8% of voltage ripple. The inner capacitor voltage ripple is 0.5%, approximately. Note that the voltage fluctuation in aforementioned conditions is still within the allowable range, which is \(\pm\) 10% of the reference value.

6 Experimental results

To verify the effectiveness of the capacitor voltage balancing control without the auxiliary balancing circuit, the prototype of the 5L-HT inverter has been built. A control board with DSP (TMS320F28335) and FPGA (Xilinx XC3S400) is used. The down-scaled parameters for the experiment are listed in Table 6. A photo of the hardware set-up is shown in Fig. 10.

Figure 11 shows the experimental performance at a unity MI. The line-to-line voltage and output current is illustrated in Fig. 11a and b, respectively, which show similarities to the simulation ones. The outer and inner capacitor voltages are shown in Fig. 11c and d, respectively. Each of the split DC-link capacitor voltages is well controlled at the reference value. The voltages are regulated by adjusting the duty ratio from the PI controllers. The voltage ripples of the outer and inner capacitors are around 4.8% and 4%, respectively. Figure 12 shows the experimental performance at the low MI (MI = 0.2). The line-to-line voltage and output current is shown in Fig. 12a and b, respectively, which are similar to the simulation results. At low MI, the four capacitor voltages are regulated at the reference value (50 V). The voltage ripple of four capacitors is lower than that of at a unity MI.

Figures 13 and 14 show the effectiveness of the balancing control method for the 5L-HT inverter at transient-state conditions. The experiments are conducted under the similar conditions with those of simulation. The outer and inner capacitor voltages are shown in Fig. 13c and d, respectively. The peak-to-peak ripple of the voltages is less than 10% of the reference value, which is lower than the allowable range. In Fig. 14, the load resistor is changed from 50 Ω to 25 Ω in a step, during which the four DC-link capacitor voltages are well controlled at the reference voltage 50 V. Also, the ripple of four voltages does not exceed 10% of the reference voltage. The balancing control method without the ABC for the 5L-HT inverter is still effective under the various operating conditions.

7 Conclusions

In this paper, the balancing control scheme of DC-link capacitor voltages for 5L-HT inverter has been proposed. The existing 5L-HT inverter requires an auxiliary balancing circuit which is bulky and expensive to control the DC-link capacitor voltage. To eliminate this circuit, the recent COPWM has been utilized. With this control algorithm, the balanced DC-link capacitor voltages have been achieved by adjusting the duty ratio of switches to control NP currents. As a result, the THD of the output voltage becomes rather higher at the medium and high modulation indices. Although the THD of voltage is increased, that of load currents is quite a low since the high frequency components of voltage can be easily suppressed by load inductance. Furthermore, the total cost and volume for the 1-MW/6.6-kV system can be saved by 27% and 52%, respectively. The effectiveness of the balancing control algorithm for the 5L-HT inverter has been verified through the simulation and experimental results.

Data availability

The datasets generated during and/or analysed during current study are not publicaly available but may be available from the corresponding author if the request is reasonable.

References

Koshti, A. K., Rao M. N.: A brief review on multilevel inverter topologies. In: Proc. IEEE international conference on data management, analytics and innovation, pp. 187–193 (2017)

Gupta, K.K., Ranjan, A., Bhatnagar, P., Sahu, L.K., Jain, S.: Multilevel inverter topologies with reduced device count: a review. IEEE Trans. Power Electron. 31(1), 135–151 (2016)

El-Hosainy, A., Hamed, H. A., Azazi, H. Z., El-Kholy, E. E.: A review of multilevel inverter topologies, control techniques, and applications. In: Proc. IEEE International Middle East Power Systems Conference, pp. 1265–1275 (2017)

Omer, P., Kumar, J., Surjan, B.S.: A review on reduced switch count multilevel inverter topologies. IEEE Access 8, 22281–22302 (2020)

Soto, D., Green, T.C.: A comparison of high-power converter topologies for the implementation of FACTS controllers. IEEE Trans. Ind. Electron. O. 49(5), 1072–1080 (2002)

Wu, B.: High-power converters and AC drives. Wiley, Hoboken (2007)

Rodriguez, J., Lai, J.-S., Peng, F.-Z.: Multilevel inverters: a survey of topologies, controls, and applications. IEEE Trans. Ind. Electron. 49(4), 724–728 (2002)

Yuan, X., Barbi, I.: Fundamentals of a new diode clamping multilevel inverter. IEEE Trans. Power Electron. 15(4), 711–718 (2000)

Hakami, S.S., Lee, K.-B.: Proper flying capacitor selection for performance enhancement of five-level hybrid active neutral-point-clamped inverters. J. Power Electron. 22, 1687–1698 (2022)

Saberi, S., Rezaie, B.: Computationally efficient direct predictive speed control of PMSMs fed by three-level NPC convertors with guaranteed stability. J. Power Electron. 22, 1131–1141 (2022)

Anthon, A., Zhang, Z., Andersen, M.A.E., Holmes, D.G., McGrath, B., Teixeira, C.A.: The benefits of SiC MOSFETs in a T-Type inverter for grid-tie applications. IEEE Trans. Power Electron. 32(4), 2808–2821 (2017)

Aliaga, R., Rojas, D., Muñoz, J., et al.: 27-Level asymmetric multilevel inverter for photovoltaic energy conversion. J. Power Electron. 20, 904–915 (2020)

Zhuge, H., Zhang, L., Lou, X., et al.: Evaluation of DPWM schemes for Si/SiC three-level hybrid active NPC inverters. J. Power Electron. 22, 1825–1835 (2022)

Hua, T., Ye, Y., Wang, X.: A new 7-level inverter for active and reactive power compensation using PEV in grid-connected applications. In: Proc. IEEE international conference on power electronics systems and applications, pp. 1–6 (2020)

Durgasukumar, G., Pathak, M. K.: THD reduction in performance of multi-level inverter fed induction motor drive. In: Proc. IEEE IICPE, pp. 1–6 (2011)

Mondal, G., Gopakumar, K., Tekwani, P. N., Levi, E.: A five-level inverter scheme with common-mode voltage elimination by cascading conventional two-level and three-level NPC inverters for an induction motor drive. In: Proc. IEEE European Conference on Power Electronics and Applications, pp. 1–10 (2007)

Jahan, H. K., Mohammadpour Shotorbani, A., Rostami Noshahr, M. R., Peimani, M., Sabahi, M., Blaabjerg, F.: Partial two-stage four-level inverter for grid-tied PV application. In: Proc. IEEE power electronics, drive systems, and technologies conference, pp. 264–268 (2022)

Tirupathi, A., Annamalai, K., Veeramraju Tirumala, S.: A three-phase inverter circuit using half-bridge cells and T-NPC for medium-voltage applications. Int J Circ Theor Appl. 48, 1744–1765 (2020)

Dao, N.D., Lee, D.-C.: Operation and control scheme of a five-level hybrid inverter for medium-voltage motor drives. IEEE Trans. Power Electron. 33(12), 10178–10187 (2018)

Narimani, M., Wu, B., Zargari, N.R.: A novel five-level voltage source inverter with sinusoidal pulse width modulator for medium-voltage applications. IEEE Trans. Power Electron. 31(3), 1959–1967 (2016)

Karthik, A., Loganathan, U.: A reduced component count five-level inverter topology for high reliability electric drives. IEEE Trans. Power Electron. 35(1), 725–732 (2020)

Davis, T.T., Dey, A.: Investigation on extending the dc bus utilization of a single-source five-level inverter with Single capacitor-fed H-bridge per phase. IEEE Trans. Power Electron. 34(3), 2914–2922 (2019)

Wang, Z., Gao, C., Chen, C., Xiong, J., Zhang, K.: Ripple analysis and capacitor voltage balancing of five-level hybrid clamped Inverter (5L-HC) for medium-voltage applications. IEEE Access 7, 86077–86089 (2019)

Pribadi, J., Le, D.D., Lee, D.-C.: Novel control scheme for fvelevel hybrid fying-capacitor inverters without DC-link balancing circuits. IEEE Trans. Power Electron. 37(7), 8133–8145 (2022)

Saeedifard, M., Iravani, R., Pou, J.: Analysis and control of DC-capacitor-voltage-drift phenomenon of a passive front-end five-level converter. IEEE Trans. Ind. Electron. 54(6), 3255–3266 (2007)

Wang, K., Zheng, Z., Xu, L., Li, Y.: A generalized carrier-overlapped PWM method for neutral-point-clamped multilevel converters. IEEE Trans. Power Electron. 35(9), 9095–9106 (2020)

Wang, K., Zheng, Z., Xu, L., Li, Y.: Neutral-point voltage balancing method for five-level NPC inverters based on carrier-overlapped PWM. IEEE Trans. Power Electron. 36(2), 1428–1440 (2021)

Kim, M.-S., Lee, D.-C.: DC-link capacitor voltage balancing control without auxiliary circuits for five-level hybrid t-type neural-point clamped inverters. In: IEEE International Conference on Communications and Electronics, pp. 421–425 (2022)

Singh, S., Sonar, S.: A new SVPWM technique to Reduce the inductor current ripple of three-phase Z-source inverter. IEEE Trans. Ind. Electron. 67(5), 3540–3550 (2020)

https://www.infineon.com/cms/en/product/power/igbt/igbt-modules/ff450r33t3e3/ (2022). Accessed 24 Sept 2022

https://www.infineon.com/cms/en/product/power/igbt/igbt-modules/dd500s65k3/ (2022) Accessed 24 Sept 2022

https://www.mouser.kr/ProductDetail/KEMET/C44UOGT7110M52K?qs=Cb2nCFKsA8p2K3edRsKtNQ%3D%3D (2022) Accessed 24 Sept 2022

https://www.coilws.com/index.php?main_page=index&cPath=208_212_366 (2022) Accessed 24 Sept 2022

Acknowledgements

This research was supported by the Yeungnam University Research Grants in 2020.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Kim, MS., Lee, DC. Balancing control scheme of DC-link capacitor voltages for five-level hybrid T-type inverters without auxiliary circuit. J. Power Electron. 23, 467–477 (2023). https://doi.org/10.1007/s43236-023-00592-5

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s43236-023-00592-5