Abstract

In this paper, floating memcapacitor and meminductor emulators have been proposed using voltage differencing current conveyors, memristor and grounded capacitor. Meminductor emulator has been easily obtained from memcapacitor emulator and vice versa by interchanging the positions of memristor and capacitor. The proposed designs of memcapacitor and meminductor emulators are very simple as compared to most of the designs available in the literature. Proposed emulators perform satisfactorily for a wide range of frequency and also satisfy the non-volatility test. The performance of proposed memcapacitor and meminductor emulators has been verified by embedding the memristor emulator circuit and the SPICE model of memristor. The performance of proposed emulators is found to be satisfactory in both the cases. The proposed designs have been simulated by LTspice tool using 0.18 µm CMOS technology parameters. Adaptive learning circuits have also been designed using proposed memcapacitor and meminductor emulators that fully verify the workability of the design.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Mem-elements are getting phenomenal attention from researchers due to their unique features and wide range of applications especially in neural networks, nonlinear circuits and dense non-volatile memories. Mem-elements are now considered as basic elements of electrical circuits in addition to the well-known elements, namely resistors, capacitors and inductors. The first mem-element is memristor that relates the charge with flux, whereas other two mem-elements are memcapacitor and meminductor that relate charge with voltage, and flux with current, respectively. The three basic elements resistors, capacitors and inductors are well known for a long time, while the first mem-element, namely memristor, came into picture in 1971 with Prof. Chua’s prediction (Chua 1971). It remained a hypothetical element until the possibility of physical realization of memristor that was reported in 2008 (Strukov et al. 2008). After 2008, it became an interesting topic of research that motivated engineers to work upon these elements. A lot of research is going on to explore the possibilities of its physical realization and usage in multiple areas of electrical and electronics engineering. Researchers at HP Lab suggested the physical realization of TiO2-based memristor, but it is still not commercially available in the market. To fulfil the gap and to develop the different applications using memristors, researchers have suggested memristor emulator circuits in many research papers (Kim et al. 2012; Yesil et al. 2014; Sanchez-Lopez and Carrasco-Aguilar 2015; Sanchez-Lopez and Aguila-Cuapio 2017; Sozen and Cam 2016; Ranjan et al. 2017; Kanyal et al. 2018; Yadav et al. 2020a, b; Gupta et al. 2020). After the sufficient work done in the realization of memristor emulators, researchers are now trying to mimic the properties of two other mem-elements, namely memcapacitors and mem-inductors. There are two approaches to design memcapacitor and meminductor emulators. In the first approach, properties of memcapacitor and meminductor are mimicked with the help of memristor and some active/passive components. In the second approach, the active inductor circuits available in literature are converted into meminductors in view of making an arrangement which realizes the inductor with memory. Memcapacitor and meminductor emulators were realized first in 2010 using memristor, operational amplifier, resistor and capacitor (Pershin and Ventra 2010). Meminductor emulator has been obtained from memcapacitor emulator by interchanging the positions of capacitor and memristor. Subsequently, a mutator circuit has been reported to transform the memristor into memcapacitor. To serve the purpose of transformation, the mutator circuit has been realized using two AD844 and one resistor. In order to mimic the behaviour of memcapacitor, memristor is terminated at port 2 of the mutator while measuring the input impedance of the circuit at port 1 (Biolek and Biolkova 2010). Floating memcapacitor and meminductor emulators are realized using two single-output or double-output current conveyors, memristor and two passive components (Pershin and Ventra 2011). Thereafter, memristor-less memcapacitor emulator has been reported using multiplier, four op-amps, resistors, capacitors and current-controlled current source (Fouda and Radwan 2012). Next, light-dependent resistor-based memristor model has been utilized to design a memcapacitor emulator in which five op-amps, few resistors and a capacitor are used (Wang et al. 2012). A mutator-based expandable memcapacitor emulator has been reported in which the mutator is designed using two CFOAs, resistor and capacitor. Memristor emulator circuit has been used to terminate the output port of the mutator. Parallel, series and parallel-series combinations of memristor emulators have been connected to the mutator circuit in order to get the respective combinations of memcapacitor emulators (Sah et al. 2013). A floating memcapacitor emulator circuit has been reported using four current-conveyors, memristor emulator, few resistors and capacitor. Memristor emulator has been realized using two op-amps, few resistors, a capacitor and a multiplier (Yu et al. 2013). Next, meminductor and memcapacitor emulators have been reported using memristor emulator, two AD844s, one resistor and a capacitor. Memristor emulator utilized in the designs of meminductor and memcapacitor has been realized using two operational amplifiers, two AD844s, few resistors and capacitors (Y D-Sheng et al. 2014). A floating memristor-less meminductor emulator has been realized using four current-conveyors, resistors, capacitors and a buffer (Liang et al. 2014). A charge-controlled meminductor emulator has been reported using three operational amplifiers, multiplier, few MOSFETs, inductor and capacitor (Sah et al. 2014a). Memristor-less current and voltage-controlled meminductor emulator has been reported using three current-conveyors, multiplier, adder, few resistors and capacitors (Fouda and Radwan 2014). A mutator-based meminductor emulator has been reported using two current conveyors, three operational amplifiers, multiplier, buffer, current sources, few resistors and capacitors (Sah et al. 2014b). Another mutator-based meminductor emulator has been reported using current conveyor, op-amps, buffer, few resistors and capacitor. Memristor emulator has been designed using op-amps, buffer, multiplier, current sources, resistor and capacitor (Sah et al. 2014c). A universal mutator has been reported in which memristor, memcapacitor and meminductor have been obtained using three off-the-shelf active devices, few resistors and a capacitor (Yu et al. 2014). A floating memcapacitor emulator has been realized using an instrumentation amplifier, binary capacitor, switches and resistors (Biolek et al. 2016). A meminductor emulator has been reported using a gyrator that uses two op-amps, memristor, four resistors and a capacitor (Wang 2016). A mutator circuit has been reported using four AD844, one op-amp, four resistors and a capacitor that is capable of emulating memristor, memcapacitor and meminductor (Yu et al. 2019). A universal grounded and floating emulator for memristor, memcapacitor and meminductor has been reported using five CCIIs, one analog multiplier, one op-amp, few resistors and capacitors (Zhao et al. 2019). A meminductor emulator has been reported in which Antoniou’s inductance simulation circuit has been modified (Romero et al. 2020). A mutator circuit for memcapacitor and meminductor emulators has been designed using current backward transconductance amplifier, memristor and a capacitor (Taskiran et al. 2020). A universal mutator has been realized using four AD844s, one varactor diode, four resistors and one capacitor (Zheng et al. 2019). Meminductor emulators using two operational amplifiers, one memristor, three resistors and one capacitor have been reported in Singh and Rai (2021). Another meminductor emulator based on Riordan gyrator has been realized using three operational amplifiers, eight resistors, one capacitor and one LED coupled with photoresist (Romero et al. 2021). Recently, a meminductor emulator using two CCIIs, three capacitors and one resistor has been reported in Yesil and Babacan (2020).

It has been observed in the literature survey of mem-element emulators that most of the circuits reported so far in the literature are very complex. In many emulator circuits, analog multipliers have been used. This paper reports a very simple circuit of memcapacitor and meminductor emulator which uses only one active block, namely voltage differencing current conveyor, memristor and a capacitor. The memristor emulator circuit and SPICE model of memristor both have been utilized to check the workability of the design of memcapacitor and meminductor emulators. The performance of proposed memcapacitor and meminductor emulators has also been verified by designing adaptive learning circuits.

The paper is organized in eight sections including introduction. In Sect. 2, the mem-elements and their inter-relations have been reviewed. The symbolic notation, characteristics and circuit diagram of VDCC are presented in Sect. 3. The proposed designs of memcapacitor and meminductor emulators are discussed in Sect. 4. Simulation results and their discussions are given in Sect. 5. Section 6 covers the performance comparison of proposed emulators with other emulators available in the literature. Adaptive learning circuits using proposed memcapacitor and meminductor emulators are presented in Sect. 7. Concluding remarks are given in Sect. 8.

2 Basic Review of Mem-elements

Mem-elements refer to the family of elements comprising memristor, memcapacitor and meminductor. The memristor was postulated as the two terminal missing circuit elements by Chua (1971). Memristive system shows nonlinear relationship between flux ϕ(t) and charge q(t). Therefore, memristance (\({M}_{R})\) is defined by the following relation

which can be rewritten as

where V(t) and I(t) represent the voltage and current of the memristive system. The pinch hysteresis loop between V(t) and I(t) is plotted to determine the system’s memristive behaviour. The memcapacitive and meminductive systems are defined by the variables σ and ρ, where ρ is the time integral of the flux and σ is the time integral of the charge as given in Eqs. (3) and (4):

Thus, the unique memory property pertaining to the memristive systems can now be easily implied in the capacitive and inductive systems making them memcapacitive and meminductive in nature. Memcapacitive systems are generally defined by the relation as

where MC is the memcapacitance of the system. Redefining above equation we get

where q(t) and V(t) are the charge and its corresponding voltage of the memcapacitive system, respectively. The pinched hysteresis loop in memcapacitive system is plotted between q(t) and V(t). Similarly, a meminductive system is characterized by the following relation

where ML is the meminductance of the system. Equation (7) can be rewritten as:

where \(\phi\)(t) and I(t) are the induced flux and its corresponding current in the meminductive system, respectively. The pinched hysteresis loop for the meminductive system is observed between \(\phi\)(t) and I(t).

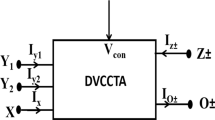

3 Voltage Differencing Current Conveyor (VDCC) and Its Properties

The voltage differencing current conveyor (VDCC) is a six terminal block out of which two terminals P and N are input terminals, Z and X are intermediate terminals and WP and WN are output terminals. It combines the advantages of both voltage differencing unit and current conveyor. The impedances of all terminals are very high except “X” terminal. The input currents Ip and In are zero as given in Eq. (9). Two voltages (Vp and Vn) are applied to the input terminals P and N, current Iz is obtained at intermediate terminal “Z” as given in Eq. (10). An impedance is connected to “Z” terminal to obtain the voltage Vz that is copied to “X” terminal of VDCC as given in Eq. (11). Current Ix of “X” terminal is conveyed to two output terminals “WP” and “WN” as given in Eq. (12). The symbolic notation and circuit diagram of VDCC are given in Figs. 1 and 2. The transconductance of VDCC is controlled by the bias current IB1 as given in Eq. (13).

Circuit diagram of VDCC (Kacar et al. 2014)

4 Proposed Floating Memcapacitor/Meminductor Emulator

The proposed floating memcapacitor/meminductor emulator circuit using single voltage differencing current conveyor, a memristor and a grounded capacitor is shown in Fig. 3. The emulator of Fig. 3 has been designed on the principle of mutator in which terminals “a” and “c” are connected to terminals “b” and “d”, respectively, to realize memcapacitor emulator, whereas terminals “a” and “c” are connected to terminals “d” and “b”, respectively, to realize meminductor emulator. This proves the universality of our design. The VDCC-based memristor emulator shown in Fig. 4 is utilized in the design of proposed memcapacitor and meminductor emulators.

4.1 Analysis of the Proposed Memcapacitor

Figure 3 represents the proposed memcapacitor emulator circuit when terminals “a” and “c” are connected to terminals “b” and “d” respectively. The routine analysis of the circuit yields the following equation:

where Vin (t) = Vin1 (t) – Vin2 (t).

The voltage VX can also be written as:

The input current Iin1 can easily be obtained as:

From Eqs. (14), (15) and (16), we get

that leads to the value of charge qin (t) as

Comparing Eq. (18) with Eq. (6), the value of memcapacitance (MC) is deduced as

Equation (19) is further analysed using SPICE model of HP memristor (Biolek et al. 2009). The memristance of the HP memristor is given as

where ROFF and RON are the equivalent resistances of the HP memristor when it is undoped and doped, respectively, the state variable x(t) is represented by \(\frac{W(t)}{D}\), W(t) is the state variable for the length of doped \({\mathrm{T}}_{\mathrm{i}}{\mathrm{O}}_{2}\), D is the total \({\mathrm{T}}_{\mathrm{i}}{\mathrm{O}}_{2}\) length in HP memristor.

After substituting the value of MR from Eq. (20) to Eq. (19), we get

It is inferred from Eq. (21) that the memcapacitance of proposed memcapacitor emulator designed using HP memristor comprised two parts, namely fixed and variable. The fixed part depends on the transconductance of the VDCC. It also depends on the values of capacitor and off-resistance (ROFF) of the memristor used in proposed memcapacitor emulator. The variable part depends on both internal state x(t) and on the values of on-resistance and off-resistance (RON and ROFF) of HP memristor. It also depends on the value of capacitor used in the design. When VDCC-based memristor emulator circuit (Fig. 4) is embedded in place of memristor (MR) used in the proposed memcapacitor emulator circuit of Fig. 3, the value of memristor (MR) is obtained as given in Eq. (22)

where \(K = \mu _{n} C_{{ox}} \frac{W}{L}\), \({V}_{B}=\frac{{\phi }_{1}}{R{C}_{2}}\) and \(\varphi _{1}\) is the flux of VDCC-based memristor emulator.

Replacing the value of MR from Eq. (22) to Eq. (19), we obtain

Substituting the value of \({V}_{B}=\frac{{\phi }_{1}}{R{C}_{2}}\) and rearranging Eq. (23) results in

From Eq. (24), it is clear that memcapacitance of the proposed memcapacitor emulator depends on the flux (\(\Phi_{1}\)) and the values of resistor (R) and capacitor (C2) used in the memristor emulator. It also depends on value of the capacitor (C1) used in the proposed memcapacitor emulator and on various technology parameters.

4.2 Analysis of the Proposed Meminductor

The meminductor emulator circuit (Fig. 3) is realized when terminals “a” and “c” are connected to terminals “d” and “b”, respectively. The routine analysis of meminductor emulator shown in Fig. 3 yields the following equations:

The voltage Vz can also be represented as:

With the help of Eqs. (27) and (28), the value of flux ϕin can be represented as:

Rewriting Eq. (29), we get:

Comparing Eq. (30) with Eq. (8), the meminductance (\({M}_{L}\)) is deduced as:

Equation (31) is further analysed using SPICE model (Biolek window) of HP memristor.

Substituting the value of memristor MR from Eq. (20) into Eq. (31), we get

It is deduced from Eq. (32) that the meminductance of proposed meminductor emulator designed using HP memristor is comprised of two parts, namely fixed and variable. The fixed part depends on the values of capacitor (C1) and off-resistance of memristor (ROFF). The variable part depends on internal state x(t) as well as on-resistance and off-resistance (RON and ROFF) of HP memristor. When VDCC-based memristor emulator circuit (Fig. 4) is embedded in place of memristor (MR) used in the proposed meminductor emulator circuit of Fig. 3, the value of memristor (MR) is obtained as given in Eq. (22).

Replacing the value of memristor (MR) from Eq. (22) into Eq. (31), we get

Substituting \({V}_{B}=\frac{{\Phi}_{1}}{R{C}_{2}}\) and rearranging the terms result in the value of meminductance as:

It can be concluded from Eq. (34) that the meminductance of proposed meminductor emulator depends on the values of flux (Φ1), resistor (R) and the value of capacitor (C2) used in the memristor emulator. It also depends on the value of the capacitor (C1) used in the proposed meminductor emulator.

5 Simulation Results and Discussions

The proposed floating memcapacitor/meminductor emulator circuit is simulated using LTspice tool with TSMC 180 nm CMOS technology parameters. The supply voltage is chosen as ± 0.9 V. The value of resistor (R) shown in Fig. 4 is chosen as 2 kΩ. The aspect ratios of MOSFETs used in the design of VDCC are given in Table 1.

5.1 Simulation Results of Proposed Memcapacitor Emulator

The proposed memcapacitor emulator shown in Fig. 3 is simulated employing both the SPICE model of HP memristor (Biolek window) and the VDCC-based memristor emulator shown in Fig. 4. The plots depicting transient response and the pinched hysteresis loop for the proposed memcapacitor emulator using SPICE model of HP memristor (Biolek window) are shown in Fig. 5a, b. Pinched hysteresis loop is obtained between voltages VX and Vin that indirectly plots the curves between charge (q) and voltage (V). These responses are obtained for the input sinusoidal voltage having amplitude of 100 mV and frequency of 0.6 Hz. The value of capacitor C1 is chosen as 50 pF. Figure 6a depicts the pinched hysteresis curves at different frequencies when simulated using SPICE model of HP memristor. Pinched hysteresis loops of memcapacitor emulator have also been obtained using VDCC-based memristor emulator for different frequencies extending from hertz to several hundreds of kilohertz range as shown in Fig. 6b–d. These loops have been obtained by appropriately scaling the values of capacitors C1 and C2. The pinched hysteresis loops of Fig. 6b are obtained when the values of capacitors C1 and C2 are selected as 10 μF and 18 μF, respectively. Pinched hysteresis loops of Fig. 6c are obtained for the values of capacitors C1 = 20 nF and C2 = 85 nF. Similarly, the pinch hysteresis loops shown in Fig. 6d are obtained when values of capacitors C1 and C2 are chosen as 50 pF and 18 pF, respectively Therefore, it can be concluded that proposed memcapacitor emulator works satisfactorily for low to high frequency range. It is observed from Figs. 6a–d that the pinched hysteresis loop shrinks when frequency is increased.

The non-volatility property of the proposed memcapacitor emulator is verified by applying the pulse input (Vin) of 20 mV amplitude and 0.55 Hz frequency to the memcapacitor circuit designed using the SPICE model of HP memristor. The memory retaining property is shown in Fig. 7 by plotting the voltage (VX) at X terminal of memcapacitor emulator as it is the value corresponding to the charge (qin). It can be observed from Fig. 7 that during “on” period of the input pulse the voltage (VX) decreases from the value 18 mV to 15 mV, while for the “off” period, it retains the same voltage 15 mV and starts decreasing it for the “on” period of next cycle of the input pulse. The same effect can be observed for the four cycles of the input pulse. Thus, the proposed memcapacitor emulator verifies the non-volatility property.

5.2 Simulation Results of Proposed Meminductor Emulator

The proposed meminductor emulator shown in Fig. 3 has been simulated employing both the SPICE model of HP memristor (Biolek window) and the VDCC-based memristor emulator shown in Fig. 4. The transient response and the pinched hysteresis loop for the proposed meminductor emulator using SPICE model of HP memristor are shown in Fig. 8a, b. These responses have been obtained by applying the input current signal of 25 µA amplitude and 0.6 Hz frequency, and the value of capacitor C1 is chosen as 20 pF. The simulations of the proposed meminductor emulator designed using VDCC-based memristor are done by applying input sinusoidal voltage having amplitude of 100 mV. It can be deduced from Eq. (27) that flux \((\Phi_{\text{in}})\) is proportional to voltage (VZ) at Z terminal of the meminductor emulator. Thus, for the ease of plotting, pinched hysteresis loop is plotted between voltage (VZ) and current (Iin) of the proposed meminductor emulator.

The pinched hysteresis loops for different frequencies obtained by using the SPICE model of HP memristor are shown in Fig. 9a. Pinched hysteresis loops for different frequencies ranging from hertz to several hundreds of kilohertz are also plotted for the meminductor emulator using VDCC-based memristor. These loops are plotted by appropriately adjusting the values of capacitors C1 and C2. The pinched hysteresis loops of Fig. 9b are obtained when the values of capacitors C1 and C2 are selected as 10 μF and 40 μF, respectively. Pinched hysteresis loops of Fig. 9c are obtained for the values of capacitors C1 = 10 nF and C2 = 40 nF. Similarly, the pinch hysteresis loops shown in Fig. 9d are obtained when values of capacitors C1 and C2 are chosen as 10 pF and 50 pF, respectively Therefore, it can be concluded that proposed meminductor emulator works satisfactorily for low to high frequency range. It is observed from Fig. 9a–d that the pinched hysteresis loop shrinks when frequency is increased.

The non-volatility property of the proposed meminductor emulator is verified by applying the current pulse input (Iin) of amplitude 5 μA and frequency of 0.55 Hz to the meminductor emulator designed using SPICE model of HP memristor. The memory retaining property is shown in Fig. 10 by plotting the voltage (VZ) at Z-terminal of meminductor emulator as it is the value corresponding to the charge \((\Phi_{\text{in}})\). It can be observed from Fig. 10 that during “on” period of the input pulse the voltage VZ decreases from 16 to 12 mV, while it retains the value of voltage VZ for the “off” period. When the next input pulse arrives, the voltage VZ starts decreasing again for the “on” period of input pulse and retained its value for the “off” period of input pulse. The non-volatility property is shown in Fig. 10 for four cycles of the input pulses. Therefore, proposed meminductor emulator verifies the property of non-volatility.

6 Comparison of Proposed Emulators with Other Reported Emulators in the Literature

The proposed memcapacitor and meminductor emulators have been compared with other reported memcapacitor/meminductor emulators in the literature. The comparison is done on the basis of number of active and passive components, range of frequency, floating/grounded configurations of emulators and types of realizations. The following conclusions have been drawn on the basis of Table 2.

-

1.

The proposed emulators use only one active block and two passive components, whereas other emulators reported in references (Biolek and Biolkova 2010; Pershin and Ventra 2011; Fouda and Radwan 2012, 2014; Wang et al. 2012; Sah et al. 2013, 2014a, b, c; Yu et al. 2013, 2019; Sheng et al. 2014; Liang et al. 2014; Yu et al. 2014; Biolek et al. 2016; Wang 2016; Zhao et al. 2019; Romero et al. 2020, 2021; Zheng et al. 2019; Singh and Rai 2021; Yesil and Babacan 2020) use large number of active and passive components.

-

2.

Proposed circuits realize both memcapacitor and meminductor emulators, whereas emulators reported in references (Biolek and Biolkova 2010; Fouda and Radwan 2012, 2014; Wang et al. 2012; Sah et al. 2013, 2014a, b, c; Yu et al. 2013; Liang et al. 2014; Biolek et al. 2016; Wang 2016; Romero et al. 2020, 2021; Singh and Rai 2021; Yesil and Babacan 2020) realize either memcapacitor or meminductor emulator.

-

3.

Proposed emulators are floating type, whereas reported emulators in references (Pershin and Ventra 2010; Biolek and Biolkova 2010; Fouda and Radwan 2012, 2014; Wang et al. 2012; Sah et al. 2014a, b; Wang 2016; Romero et al. 2020; Singh and Rai 2021) realize only grounded configuration.

-

4.

Pinched hysteresis loop of proposed emulators is maintained up to 700 kHz, whereas emulators reported in references (Pershin and Ventra 2010,2011; Biolek and Biolkova 2010; Fouda and Radwan 2012, 2014; Wang et al. 2012; Sah et al. 2013, 2014a, b, c; Yu et al. 2013; Y D-Sheng et al. 2014; Liang et al. 2014; Yu et al. 2014) form pinched hysteresis loop in the frequency range of Hz only. The emulators reported in references (Biolek et al. 2016; Yu et al. 2019; Zhao et al. 2019; Romero et al. 2020, 2021; Zheng et al. 2019; Yesil and Babacan 2020) provide pinched hysteresis loops in kHz range but varies only from 1 to 180 kHz.

7 Application of Proposed Memcapacitor and Meminductor Emulators in Adaptive Learning Circuit

Mem-elements are widely being used in various fields and applications. One of the popular applications is adaptive neuromorphic circuits and neural networks (Pershin et al. 2009; Pershin and Ventrai 2010; Wang et al. 2013; Erokhin 2020; Sangwan and Hersam 2020; Alexander et al. 2021). In this section, adaptive learning circuit using proposed memcapacitor and meminductor emulators is realized as shown in Fig. 11a, b. This model of the neuromorphic adaptive learning circuit is derived from the behavioural response of the amoeba (a unicellular organism) (Pershin et al. 2009; Wang et al. 2013). Amoeba generally reacts to changes in its environmental conditions like temperature and humidity by slowing down its locomotive speed. In this process, it memories past events and nearly predicts the timing of future events having periodicity with the past ones (Wang et al. 2013). The adaptive learning circuits shown in Figs. 11a, b are the electronic analogous model of the amoeba’s behavioural response. Input voltage (Vin) shown in Fig. 12a corresponds to the temperature changes in amoeba’s environment, and output voltages (Vout1 and Vout2) correspond to variation in the locomotive speed of the amoeba in response to temperature changes. The values of meminductor and memcapacitor element change with respect to variation in the values of the input signal across them. This finally results in the tuning of the designed adaptive learning circuit with that of input voltage (temperature variation) frequency. Component values for the adaptive learning circuit as shown in Fig. 11a are R = 1 Ω, L = 1 μH, and its memcapacitor is having component values of C1 = 1 nF with Biolek window-based SPICE model of HP memristor. In Fig. 11b, the values of the components are R = 1 Ω, C = 0.1 pF and its meminductor is having component values of C1 = 300 pF with HP memristor based on the Biolek window SPICE model. Figure 12b, c shows the simulation results for the circuits shown in Fig. 11a, b, respectively. From Fig. 12b, c, it is observed that at each point of the temperature drop the corresponding output locomotive speed also drops. With periodic drop in input voltage (temperature drop), the locomotive speed, i.e. Vout1 and Vout2, drops further as compared to its previous drop value. This verifies the adaptive learning process. From these adaptive learning circuit realization, our proposed circuits qualify for the neuromorphic applications.

8 Conclusion

In this work, memcapacitor and meminductor emulators have been proposed using voltage differencing current conveyor, memristor and a capacitor. The proposed emulators have been designed using both SPICE model of memristor and VDCC-based memristor emulators. The obtained pinched hysteresis loops indicate the workability of the proposed design for a wide range of frequencies. The performance of proposed emulators has been verified by designing an adaptive learning circuit. The output responses of the adaptive learning circuits using memcapacitor and meminductor emulators verify their performance. The proposed memcapacitor and meminductor emulators have been compared with existing memcapacitor and meminductor emulators in the literature. It is concluded that the proposed design is very simple over most of the designs available in the literature.

References

Biolek D, Biolkova V (2010) Mutator for transforming memristor into memcapacitor. Electron Lett 46(21):1428–1429

Biolek Z, Biolek D, Biolkova V (2009) SPICE model of memristor with nonlinear dopant drift. Radioengineering 18(2):1–5

Biolek D, Biolkova V, Kolka Z, Dobes J (2016) Analog emulator of genuinely floating memcapacitor with piecewise-linear constitutive relation. Circuits Syst Signal Process 35(1):43–62

Chua L (1971) Memristor-the missing circuit element. IEEE Trans Circuit Theory 18(5):507–519

Erokhin V (2020) Memristive devices for neuromorphic applications: comparative analysis. BioNanoSci 10:834–847

Fouda ME, Radwan AG (2012) Charge controlled memristor-less memcapacitor emulator. Electron Lett 48(23):1454–1455

Fouda ME, Radwan AG (2014) Memristor-less current and voltage-controlled meminductor emulators. In: 21st IEEE international conference on electronics, circuits and systems (ICECS), pp 279–282

Gupta S, Rai SK, Pandey R (2020) New grounded and floating decremental/incremental memristor emulators based on CDTA and its application. Wirel Pers Commun 113:773–798

Kacar F, Yesil A, Minaei S, Kuntman H (2014) Positive/negative lossy/lossless grounded inductance simulators employing single VDCC and only two passive elements. AEU Int J Electron Commun 68(1):143

Kanyal G, Kumar P, Paul SK, Kumar A (2018) OTA based high frequency tunable resistorless grounded and floating memristor emulators. AEU Int J Electron Commun 92:124–145

Kim H, Sah MP, Yang C, Cho S, Chua L (2012) Memristor emulator for memristor circuit applications. IEEE Trans Circuits Syst I 59(10):2422–2431

Liang Y, Chen H, Yu DS (2014) A practical implementation of a floating memristor-less meminductor emulator. IEEE Trans Circuits Syst II Express Briefs 61(5):299–303

Morozov AY, Abgaryan KK, Reviznikov DL (2021) Mathematical model of a neuromorphic network based on memristive elements. Chaos Solitons Fractals 143:110548

Pershin YV, Di Ventra M (2010) Memristive circuits simulate memcapacitors and meminductors. Electron Lett 46(7):517

Pershin YV, Di Ventra M (2011) Emulation of floating memcapacitors and meminductors using current conveyors. Electron Lett 47(4):243–244

Pershin YV, Ventrai DM (2010) Experimental demonstration of associative memory with memristive neural networks. Neural Netw 20:881886

Pershin YV, Fontaine SL, Ventra MD (2009) Memristive model of amoeba learning. Phys Rev E 82:021926

Ranjan RK, Raj N, Bhuwal N, Khateb F (2017) Single DVCCTA based high frequency incremental/decremental memristor emulator and its application. AEU Int J Electron Commun 82:177–190

Romero FJ, Escudero M, Garcia AM, Morales DP (2020) Meminductor emulator based on a modified Antoniou’s gyrator circuit. Electronics 9(9):1407

Romero FJ, Garcia AM, Escudero M, Rodriguez DN (2021) Design and implementation of a floating meminductor upon Riordan gyrator. AEU Int J Electron Commun 133:153671

Sah MP, Budhathoki RK, Yang C (2013) Expandable circuits of mutator-based memcapacitor emulator. Int J Bifurc Chaos 23(5):1–17

Sah MP, Budhathoki RK, Yang C, Kim H (2014a) Charge controlled meminductor emulator. J Semicond Technol Sci 14(6):750–754

Sah MP, Budhathoki RK, Yang C, Kim H (2014b) A mutator-based meminductor emulator circuit. In: IEEE international symposium on circuits and systems (ISCAS), pp 2249–2252

Sah MP, Budhathoki RK, Yang C, Kim H (2014c) Mutator-based meminductor emulator for circuit applications. Circuits Syst Signal Process 33(8):2363–2383

Sanchez-Lopez C, Aguila-Cuapio LE (2017) A 860 kHz grounded memristor emulator circuit. AEU Int J Electron Commun 73:23–33

Sanchez-Lopez C, Carrasco-Aguilar MA (2015) A 16 Hz–160 kHz memristor emulator circuit. AEU Int J Electron Commun 69(9):1208–1219

Sangwan VK, Hersam MC (2020) Neuromorphic nanoelectronic materials. Nat Nanotechnol 15:517–528

Singh A, Rai SK (2021) Novel meminductor emulators using operational amplifiers and their applications in chaotic oscillators. J Circuits Syst Comput 30(12):2150219

Sozen H, Cam U (2016) Electronically tunable memristor emulator circuit. Analog Integr Circ Sig Process 89(3):655–663

Strukov DB, Snider GS, Stewart DR, Williams RS (2008) The missing memristor found. Nature 453(7191):80–83

Taskiran ZGC, Sagbas M, Ayten UE, Sedef H (2020) A new universal mutator circuit for memcapacitor and meminductor elements. AEU Int J Electron Commun 119:153180

Wang SF (2016) The gyrator for transforming nano memristor into meminductor. Circuit World 42(4):197–200

Wang XY, Fitch AL, Iu HHC, Qi WG (2012) Design of a memcapacitor emulator based on a memristor. Phys Lett A 376(4):394–399

Wang FZ, Chua LO, Yang X, Helian N, Tetzlaff R, Schmidt T et al (2013) Adaptive neuromorphic architecture. Neural Netw 45:111–116

Yadav N, Rai SK, Pandey R (2020a) New grounded and floating memristor emulators using OTA and CDBA. Int J Circuit Theory Appl 48(7):1154–1179

Yadav N, Rai SK, Pandey R (2020b) Novel memristor emulators using fully balanced VDBA and grounded capacitor. Iran J Sci Technol Trans Electr Eng. https://doi.org/10.1007/s40998-020-00357-x

Yesil A, Babacan Y (2020) Electronically controllable memcapacitor circuit with experimental results. IEEE Trans Circuits Syst II Express Brief 68(4):1443–1447

Yesil A, Babacan Y, Kacar F (2014) A new DDCC based memristor emulator circuit and its applications. Microelectron J 45(3):282–287

Yesil A, Babacan Y, Kacar F (2019) Electronically tunable memristor based on VDCC. AEU Int J Electron Commun 107:282

Yu DS, Liang Y, Chen H, Iu HHC (2013) Design of a practical memcapacitor emulator without grounded restriction. IEEE Trans Circuits Syst II Express Briefs 60(4):207–211

Yu D-S, Liang Y, Iu HHC, Hu Y-H (2014a) Mutator for transferring a memristor emulator into meminductive and memcapacitive circuits. Chin Phys B 23(7):1–11

Yu D, Liang Y, Iu HHC, Chua L (2014b) A universal mutator for transformations among memristor, memcapacitor, and meminductor. IEEE Trans Circuits Syst II Express Briefs 61(10):758–762

Yu D, Zhao X, Sun T, Iu HHC, Fernando T (2019) A simple floating mutator for emulating memristor, memcapacitor, and meminductor. IEEE Trans Circuits Syst II Express Briefs 67(7):1334

Zhao Q, Wang C, Zhang X (2019) A universal emulator for memristor, memcapacitor, and meminductor and its chaotic circuit. Chaos inTerdiscip J Nonlinear Sci 29(1):1–14

Zheng C, Yu D, Iu HHC, Fernando T, Sun T, Eshraghian JK, Guo H (2019) A novel universal interface for constructing memory elements for circuit applications. IEEE Trans Circuits Syst I 66(12):4793

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Singh, A., Rai, S.K. VDCC-Based Memcapacitor/Meminductor Emulator and Its Application in Adaptive Learning Circuit. Iran J Sci Technol Trans Electr Eng 45, 1151–1163 (2021). https://doi.org/10.1007/s40998-021-00440-x

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s40998-021-00440-x