Abstract

In this work, a charge-based memristor emulator is designed using a single active current mode component Differential Voltage Current Conveyor Transconductance Amplifier with one capacitor and two resistors as passive components. Importantly, the proposed circuit topology can be changed to either grounded or floating configuration using a single switch. Moreover, the proposed memristor design can be operated either in incremental or decremental configuration by using another switch. Therefore, using only two switches, the same circuitry can be utilized to design the floating/grounded incremental/decremental memristor. The pinched hysteresis loop area can be controlled by applying different biasing voltages. Further, the mathematical analysis is performed to drive the theoretical TiO2 based results for the proposed memristor emulator. In addition, simulations confirming the theoretical analysis are conducted in PSPICE using the 180 nm TSMC technology with a supply voltage of ± 0.9 V by varying frequencies and capacitances to obtain a pinched hysteresis loop. The presented circuit performs effectively for frequencies upto 500 MHz while operating with grounded type memristor and 300 MHz with floating type design. To check the ability to remember the history of the proposed memristor, the non-volatility test is performed for both the incremental and decremental configurations. Moreover, the suggested memristor design is applied in an adaptive learning circuit to prove its feasibility in neuromorphic applications.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Until 1971, only three fundamental components were known i.e., resistor (defining relation between voltage and current), inductor (current and magnetic flux), and capacitor (charge and voltage). In [1], the author proposed a fourth fundamental nonlinear element by forming a missing relationship between charge and flux, which is known as a memristor. The memristor exhibits a hysteresis curve pinched at the origin within the voltage and current plane that changes with the operating frequency [2]. The pinched hysteresis curve represents the memory in the memristor, hence it is observed as an inherent non-volatile characteristic. Apart from the non-volatility property of the memristor, other features like lower energy consumption [3, 4], higher operating speed [5], better scaling for high integration density [6] etc. have created widespread interest among researchers. Importantly, the memristor can be most beneficial to overcome the major limitation of Von Neumann’s architecture which is a separate memory requirement from the logic design. Note that a non-volatile memristor not only provides storage capability but also it can implement various analog and digital logic when connected using specific architecture [7]. Hence, this important characteristic of the memristor has led to the development of hybrid architecture comprising memory and logic functionalities to enhance memory storage capabilities [8], enabling more efficient memory computation. Remarkably, the first prototype of a solid state memristor was developed by a team of researchers at HP Laboratories in the year 2008 [9]. Here, a thin film of titanium dioxide is situated between two platinum contacts to produce the memristor. Additionally, various other materials such as (metal insulator metal) MIM structure [10], oxides such as WOx, FeOx, SiOx etc. [11,12,13], chalcogenides [14] and ferroelectric materials [15] are also used to construct memristor. However, commercialization of memristor is still not popular due to the limitations in performance of the device, difficulty in nanoscale fabrication, and most importantly, its high manufacturing cost.

Therefore, to overcome this limitation, the behavior of the memristors can be studied by designing a memristor emulator circuit with readily available components. Importantly, this memristor emulator has ability to mimic the required characteristics such as non-volatility and current-voltage relationship as shown in TiO2 model proposed by HP labs [3]. Specifically, various designs of memrisor emulators based on HP’s TiO2 linear ion model are discussed in the literature using various analog components. Particularly, design of the emulator is demonstrated using Operational Amplifier (OPAMP) [16, 17] and current mode building blocks such as Operational Transconductance Amplifier (OTA) [18, 19], Differential Voltage Current Conveyor Transconductance Amplifier (DVCCTA) [20], Current Conveyor Transconductance Amplifier (CCTA) [21], Current Backward Transconductance Amplifier (CBTA) [22], and Voltage Difference Transconductance Amplifier (VDTA) [23, 24]. Further, these memristor emulator will assist the research community to explore the potential use of memristors in various applications e.g., as synapse in artificial neural networks (ANN) [25], logical operations [26, 27], resistive RAM [28], memristor based SRAM [29], chaotic oscillator [30, 31], chaotic neural networks (CNN) [32], image compression [33].

Apart from this, a memristor operation can be divided based on either flux controlled (Memductance) and charge controlled (Memristance) [1]. Additionally, the emulator circuits can be categorized into grounded configuration and floating configuration based on the application. In the literature, the charge based grounded configuration is discussed in [20, 22, 34,35,36], and [37] is a flux controlled memristor emulator. Also, flux based floating configuration is discussed in the papers [19, 26, 33, 38] and charge based floating configuration memristor is discussed in [39]. However. there is still need for a generic emulator capable of functioning in both floating and grounded configuration. This limitation can be overcome in [21, 32, 40,41,42] where authors discussed both floating/grounded configuration. However, the implemented circuits in [18, 40, 42] require separate circuitry for grounded/floating configuration. Therefore, design of a versatlie memristor emulator circuit is required capable of working on both grounded and floating configuration using unified circuit approach. This will increase the memristor application for future technolology. Moreover it is desirable for the memristor emulator to achieve the highest values possible of speed or frequency of operation. However, circuits proposed in [17, 22] encounter limitation in operating frequency. For [19] operating speed is limited to 1 MHz. Here, based on our current knowledge, the highest operating speed achieved by any memristor emulator is discussed by Vista et. al. in [41] is 50 MHz. However, feasibility of the circuit is not tested. In addition, the area of the designed memristor emulator proposed in [17, 35, 36] is quite large for physical implementation. Also, the memristor design discussed in [17, 35, 38] and [41] require high power consumption thereby imposing constraints on overall system capabilities. Therefore, designing the memristor emulator to operate at high frequencies while minimizing power consumption and reducing size is essential.

Therefore, motivated by the above, there is need to design generic menrsitor which can be operated in floating/grounded configuration in single circuitry with higher operating frequency, smaller area and lower power consumption. This paper presents the design of a charge-based memristor emulator utilizing the TiO2 model [9]. The emulator employs a single active component, the DVCCTA, along with two resistors and one capacitor. Unlike [19], the presented emulator circuit uses a single circuitry for floating and grounded configuration with incremental/decremental cases. It can be adjusted electronically by changing the bias voltage. The rest of the paper is organized as follows: Sect. 2 describes the detailed mathematical description to develop a theoretical model of the memristor emulation circuit under consideration. Moreover, at increased frequencies, parasitic resistances and capacitances becomes crucial. Hence, the effect of nonidealities at the port of DVCCTA, parasitic resistances, and capacitances are also studied in this section. Further, the effect of variation on frequencies, capacitor values, amplitude, and biasing voltages on implemented memristor emulator circuit is studied in Sect. 3. In addition, to confirm the retention property, a non-volatiltiy test for incremental and decremental configuration has been included in the same section. A comparative analysis between the designed circuit and previous literature work is done in Sect. 4. The proposed circuit workability is tested in the adaptive learning circuit in Sect. 5. The Sect. 6 discusses summary and conclusion of the presented circuit.

2 Mathematical description and implementation of proposed emulator model

The emulator circuit presented in this design is composed of a single Differential Voltage Current Conveyor Transconductance Amplifier (DVCCTA) as an active component with one capacitor and two resistors as passive components.

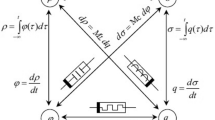

2.1 Port relationship of DVCCTA

The port relationship of DVCCTA shown in Fig. 1 is given by Iy1 = 0, Iy2 = 0, Vx = Vy1−Vy2, Iz ± = ± Ix, and Io ± = ± gmVz1. The MOSFET based implementation of DVCCTA is illustrated in Fig. 2 is taken from [44]. The value of transconductance gain is shown as

where Vc is the externally applied voltage, Vss is the supply voltage, VT is the threshold voltage and k is given by \(\frac{{\mu_{n} C_{{{\text{ox}}}} }}{\sqrt 2 }\sqrt {\left( \frac{W}{L} \right)_{{M_{25} }} \left( \frac{W}{L} \right)_{{M_{28} }} }\). μn given here is the mobility of electrons, Cox is the oxide capacitance, \(\left( \frac{W}{L} \right)_{{M_{25} }}\) and \(\left( \frac{W}{L} \right)_{{M_{28} }}\) are the aspect ratios of MOSFET. The values of MOSFETs are shown in Table 1.

2.2 Theoretical analysis of presnted memristor emulator (MRE)

The proposed memristor emulator design presented in Fig. 3 is built upon linear ion drift model [9]. Here characteristics equation is taken and compared with the results mentioned by the authors in this paper. It can be made to operate in incremental type or decremental type floating/grounded configuration by using two simple switches S1 and S2 as shown in Table 2. The W/L ratio is selected through gm/Id methodology to ensure that all the transistors work in the saturation region. The generalised equation mentioned in [9] is shown below:-

Here

Here Rset is the low resistance value and Rreset is the high resistance value. x(t) depends on width w(t) of the inner oxide layer which moves w.r.t applied voltage V(t). The w(t) depends on q(t) (charge). Overall memristance equation is given by

where k depends on mobility of charge carriers, thickness of the device and Rset values.

Applied voltage in Fig. 3 is represented as

Here the differential voltage applied at the Y1 and Y2 is utilized to make the emulator circuit work in a floating configuration. For grounded configuration, Y2 terminal is connected to ground. Input current (Iin(t)) flows from Z–terminal (direction of current is reversed) is copied to Z1 port, X port and Z2 port.

Voltage at Z1 port is Iin(t)R2. Therefore, current at O ± terminal is given by

Charge at Z2 terminal is obtained as,

Substituting the value of Vc. The Eq. (6) is modified as:-

On doing circuit analysis for port X, the equation is represented as:-

Generalized Memristance equation for decremental/incremental configuration is obtained by replacing Io± by Eq. (3) and rearranging the above equation,

The above mentioned M(q(t)) is in the form of linear ion drift Based model mentioned in Eq. (4). Incremental memristance is given by

Decremental Memristance is given by

For analysing the behaviour of memristor emulator in frequency domain, input voltage is excited by applying sinusoidal signal with amplitude Am. Memristance equation can be modified as

where τ is the time constant of the proposed emulator circuit represented as

To validate the three fingerprint characteristics explained in [2], time constant criteria has to be satisfied.

-

(i)

If frequency decreases, i.e., τ < 1/f, then hysteresis characteristics property is lost as mentioned in [24].

-

(ii)

If the frequency of the excitation voltage is increased, then the pinched hysteresis curve area decreases as the τ value decreases. This is the second fingerprint mentioned in [2].

-

(iii)

If frequency tends to be infinite, then the time variant portion disappears and the memristor behaves like a normal linear resistor. This is the third fingerprint mentioned in [2].

2.3 Nonideal analysis of proposed memristor emulator

Considering nonidealities at the port \(V_{x} = \eta_{1} V_{y1} - \eta_{2} V_{y2}\), \(I_{z1} = \rho_{1} I_{x}\),\(I_{z2} = \rho_{2} I_{x}\),\(I_{z - } = \rho_{ - } I_{x}\), \(I_{o\; \pm } = \lambda_{ \pm } \;g_{m} \;V_{z1}\) and effect of parasitics at various terminals. The proposed memristor emulator with nonidealities is shown in Fig. 4. At higher frequencies, non idealities and parasitic resistance and capacitance comes into effect. Rx is the series parasitic resistance at X terminal, Ry1, Ry2, Rz1, Rz2, Rz-, Rz+, Ro- and Ro+ are the parallel parasitic resistance at Y1, Y2, Z1, Z2, Z-, Z+, O- and O+ terminals respectively. Cy1, Cy2, Cz1, Cz2, Cz-, Cz+, Co- and Co+ are the parasitic capacitances at Y1, Y2, Z1, Z2, Z-, Z+, O- and O+

terminals respectively. Considering η1 = η2 = η, Eq. (4) is represented as

Transconductance gain at O ± terminal is considered as

where \(R_{{{\text{eq}}1}} = R_{z1} ||R_{2} ||\frac{1}{{C_{z1} s}}\).

The voltage at Z2 is obtained as

Using Eq. (6), Substituting this value in Eq. (16)

Considering ƿ1 = ƿ2 = ƿ+ = ƿ- = ƿ.

Port analysis at X terminal yields,

where \(R_{{{\text{eq2}}}} = (R_{x} + R_{1} )||R_{o\; \pm } ||\frac{1}{{C_{{_{O\; \pm } }} s}}\).

The generalized Memristance equation is modified as

3 3. Simulation results and discussion

The implementation of the proposed emulator circuit using TSMC 180nm Level 7 MOSFET parameters in PSPICE environment is shown in Fig. 3. The aspect ratios of MOSFET used for active element DVCCTA is shown in Table 1. The DC power supply and bias Voltage(Vbias) is taken as ±0.9V, and -0.3V, respectively. However, the aspect ratios mentioned in Table 1 are chosen in a way so that all the transistors work in the saturation region. Furthermore, the resistance values are taken as R1=12 kΩ and R2=16 kΩ. The input current and voltage waveform to the applied to the memristor emulator is illustrated in Fig. 5 having a time period of 20 nsec for 5 cycles. Similar to the curve mentioned in [9], Fig. 5 illustrates the zero crossing of appied voltage and current. Likewise Pinched hysteresis loop [2] which is an important characteristic of any memristor circuit is depicted in Fig. 6 for varying capacitors, wherein Floating type incremental/ decremental configuration is shown in Fig. 6 a and b, and Grounded incremental/decremental in Fig. 6 c and d, respectively. From Fig. 3, it can be observed that switch S2 regulates whether the emulator circuit will be grounded/floating type while S1 for Incremental/decremental configuration. The direction of switches S1 and S2 is listed in Table 2. Figure 6 exhibits that the hysteresis lobe area decreases as the capacitor (C) value is increased which satisfies Eq. (14) mentioned in Sect. 2. Concordly, the value of the time constant (τ) decreases as the C is increased leading to a decrease in lobe area. In addition, Figs. 7 and 8 indicate the variation of the pinched hysteresis loop with frequencies (f) for incremental configuration operating in floating/grounded mode. It can be perceived that the area of the curve is maximum for lower f but for higher f, the curve area reduces and eventually became a straight line on further increase. As the f is increased such that τ < 1/f, the pinched hysteresis curve property is lost and the memristor behaves like a normal resistor. It verifies the second and third criteria mentioned in [2] for any circuit to act like a memristor. It happens due to the reduction of τ mentioned in Eq. (14). The Pinched hysteresis loop for incremental and decremental configuration in Floating/Grounded case is illustrated in Fig. 9. It can be seen that the incremental mode has an enhanced loop area in comparison to the decremental mode. For due to τ being directly proportional to Am mentioned in Eq. (14), the Pinched hysteresis loop is expanded with an increase in Amplitude Am as shown in Fig. 10. The electronic tunability is checked by applying different Vbias to the memristor emulator circuit for floating/grounded in Figs. 11 a and b, respectively. It can be seen that the curve area decreases as Vbias is increased. Another important 12(b) working in incremental and decremental configuration by applying 11 consecutive input characteristic of the memristor is the retention property, where the data are retained even in the absence of any input signal. This property is checked for both floating/grounded type in Fig. 12a and input voltage pulses with the time period of 167 nsec having 6% duty cycle. It can be observed from both the figures that memristance M(q(t)) remains unchanged in the absence of an applied voltage pulse. The memristance value is increased when the next pulse is applied in Fig. 12a and decreased for the decremental configuration in Fig. 12b. This proves that the presented memristor emulator shows non-volatility property.

4 Comparative study of proposed design with existing literature

The conclusions from Table 3 depict the comparison of the proposed design with existing literature as follows:

-

[17, 22, 34,35,36, 38, 43] require more components to design memristor emulator circuits. However, [24] requires only one VDTA, and [39] requires one DXCCTA but it can be operated only in the floating configuration. The presented design requires single active component and few passive components to work as memristor emulator in both grounded and floating configuration.

-

[20, 22, 34,35,36, 43] can be operated only in the grounded configuration while [17, 24, 38, 39] operate only in the floating configuration. Moreover, [18, 21, 40,41,42] can be operated in both the configuration. However, in [18, 21], and [40], separate circuits are needed for grounded and floating configuration due to which monolithic ICs operating in grounded/floating configuration cannot be manufactured. Simple switching allows the circuit to work in both floating and grounded configuration.

-

Maximum frequency of operation for [17, 22, 35, 36, 38] is in the kHz range, and [18, 20, 21, 34, 40, 42] operate within 10 MHz range, with others operating upto 60 MHz range. The presented design operates upto 300 MHz range for the floating type and 500 MHz range for the grounded type.

-

Compared to [17, 34,35,36, 43] power consumption of proposed memristor is less. In contrast, while the power consumption of the proposed design exceeds that of references [24, 39], and [41], it operates at a higher frequency, indicating a trade-off between power consumption and operating frequency in these cases. Also, for [24] only floating topology is proposed whereas proposed circuit can operate in both floating and grounded configuration.

-

The proposed design uses less number of MOSFETs compared to references outlined in [17, 22] and [39].

-

While comparing with [21] and [24], number of MOSFETs used in the proposed circuit is greater. However, both the literature requires separate circuit designs for the implementation of grounded and floating configuration thereby lacking generalized circuit design.

From all the factors, it can be observed that simple generic floating/grounded memristor working in incremental and decremental configuration is constructed in this paper with higher operating frequency.

5 Application in adaptive learning

Memristor’s ability to mimic synaptic behavior has led to its application in neuromorphic circuits [24] and [45]. The memristor’s resistance adjusts in accordance to the received electrical signals. This permits them to simulate the properties of synapses in biological neural networks. To better understand the primitive learning process and behavior of the brain, researchers are trying to imitate the learning process of simple unicellular organisms like amoeba. It can sense the change in environment i.e., humidity or temperature and slow down its speed. Next time when unfavorable condition occurs, amoeba slows down spontaneously. This learning behavior of amoeba can be used to train the neuromorphic circuit. The electronic RLC circuit depicting the amoeba's skill in recognizing patterns and anticipating future events is shown in Fig. 13a. The oscillation produced with resonant frequency f which is determined by the equation below

Additionally, the memristor (M(q(t)) component encapsulates the memory mechanisms responsible for memory storage within the amoeba. The variation of temperature due to which amoeba moves is represented in the form of external Voltage i.e., input voltage spikes as given in Fig. 13b. The response i.e., velocity or motion of amoeba with respect to variation in temperature can be observed in Fig. 13c. The amoeba slows down in response to drop in temperature. To test the workability of the memristor, both incremental type and decremental type have been used and its response is presented in Fig. 13c with values chosen as R = 800Ω, L = 800uH and C = 130 pF. It can be seen that amoeba slows down or oscillations are observed when the fourth spike in the input voltage is present. It can be observed that incremental configuration memristor emulator output response shows greater response value compared to decremental configuration. Therefore, functionality of the suggested circuit is verified by the neuromorphic circuit.

6 Conclusion

The charged-based memristor emulator is proposed in this paper, wherein a single current mode active element DVCCTA, two resistors and one capacitor are used. In addition, two switches are used to alter the mode of operation while one switch is used to change type to either floating or grounded. Another switch is used to change the configuration to incremental or decremental. Theoretical analysis performed in this paper and the procured simulation results agree with the derived time constant τ described in Sect. 2. Further, the behavior of parasitic resistance and capacitance on τ is also performed. The circuit presented here is electronically tunable w.r.t. bias voltage (Vbias). The effect of variation in input amplitude (Am) for floating/grounded type is also studied. The memory retention property is tested by applying input pulse for incremental and decremental configuration. Finally, to check the feasibility of the presented design, was evaluated by incorporating it in neuromorphic circuit.

Data availability

All relevant data supporting the findings of this study are included within the article and its supplementary information files. However, raw data are available from the authors upon reasonable request and with the permission of the data providers.

References

Chua, L.O.: Memristor: the missing circuit element. IEEE Trans. Circuit Theory 18(5), 507–512 (1971)

Adhikari, S.P., Sah, M.P., Kim, H., Chua, L.O.: Three fingerprint of memristor. IEEE Trans. Circuits Syst. I: Regul. Pap. 60(11), 3008–3021 (2013)

Saleh, S., Koldehofe, B.: On memristors for enabling energy efficient and enhanced cognitive network functions. IEEE Access 10, 129279–129312 (2022)

Liu, X., Zeng, Z.: Memristor crossbar architectures for implementing deep neural networks. Complex Intell. Syst. 8(2), 787–802 (2022)

Li, H.H., Chen, Y., Liu, C., Strachan, J.P., Davila, N.: Looking ahead for resistive memory technology: a broad perspective on ReRAM technology for future storage and computing. IEEE Consum. Electron. Mag. 6(1), 94–103 (2017)

Xue, X., Wang, C., Liu, W., Lv, H., Wang, M., Zeng, X.: A RISC-V processor with area-efficient memristor-based in-memory computing for hash algorithm in blockchain applications. Micromachines 10(8), 541 (2019)

Benatti, L., Zanotti, T., Pavan, P., Puglisi, F.M.: Ultra-low power logic in memory with commercial grade memristors and FPGA-based smart-IMPLY architecture. Microelectron. Eng. 280, 112062 (2023)

Shirinzadeh, S., Soeken, M., Gaillardon, P.-E., Drechsler, R.: Logic synthesis for RRAM-based in-memory computing. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 37(7), 1422–1435 (2018)

Strukov, D.B., Snider, G.S., Stewart, D.R., Williams, R.S.: The missing memristor found. Nature 453, 80–83 (2008)

Ilyas, N., Li, D., Li, C., et al.: Analog switching and artificial synaptic behavior of Ag/SiOx:Ag/TiOx/p++-Si memristor device. Nanoscale Res. Lett. 15, 30 (2020)

Chien W.C. et. al.: A Multi-level 40 nm WOX resistive memory with excellent reliability. 2011 International electron devices meeting Tech. Dig., 5–7(2011)

Wang, C., He, W., Tong, Y., et al.: Investigation and manipulation of different analog behaviors of memristor as electronic synapse for neuromorphic applications. Sci. Rep. 6, 22970 (2016)

Chang, Y.F., Fowler, B., Chen, Y.C., et al.: Demonstration of synaptic behaviors and resistive switching characterizations by proton exchange reactions in silicon oxide. Sci. Rep. 6, 21268 (2016)

Gogoi, H.J., Mallajosyula, A.T.: A comparative study on the forming methods of chalcogenide memristors to optimize the resistive switching performance. J. Phys. D: Appl. Phys. 53(44), 445108 (2020)

Chanthbouala, A., Garcia, V., Cherifi, R.O., et al.: A ferroelectric memristor. Nat. Mater. 11(10), 860–864 (2012)

Kim, H., Sah, M.P., Yang, C., Cho, S., Chua, L.O.: Memristor emulator for memristor circuit applications. IEEE Trans. Circuits Syst. I Reg. Pap. 59(10), 2422–2431 (2012)

Yu, D., Iu, H.H.-C., Fitch, A.L., Liang, Y.: A floating memristor emulator based relaxation oscillator. IEEE Trans. Circuits Syst. I: Reg. Pap. 61(10), 2888 (2014)

Kanyal, G., Kumar, P., Paul, S.K., Kumar, A.: OTA based high frequency tunable resistorless grounded and floating memristor emulators. AEU-Int. J. Electron. C. 92, 124–145 (2018)

Kumar, K., Nagar, B.C., Pradhan, G.: Single OTA-based tunable resistorless grounded memristor emulator and its application. J. Comput. Electron. 22, 549–559 (2023)

Ranjan, R.K., Niranjan, R., Bhuwal, N., Khateb, F.: Single DVCCTA based high frequency incremental/decremental memristor emulator and its application. AEU—Int. J. Electron. Commun. 82, 177–190 (2017)

Ranjan, R.K., Rani, N., Pal, R., Paul, S.K., Kanyal, G.: Single CCTA based high frequency floating and grounded type of incremental/decremental memristor emulator and its application. Microelectron. J. 60, 119–128 (2017)

Ayten, U.E., Minaei, S., Sagba, M.: Memristor emulator circuits using single CBTA. AEU Int. J. Electron. Commun. 82, 109–118 (2017)

Petrović, P.B.: Floating incremental/decremental flux-controlled memristor emulator circuit based on single VDTA. Anal. Integr. Circuits Signal Process 96(3), 417–433 (2018)

Vista, J., Ranjan, A.: Flux controlled floating memristor employing VDTA: incremental or decremental operation. IEEE Trans. Computer-Aided Des. Int. Circuits Syst. 40(2), 364–372 (2021)

Liu, X., Zeng, Z., Wen, S.: Implementation of memristive neural network with full-function Pavlov associative memory. IEEE Trans. Circuits Syst. I, Reg. Pap. 63(9), 1454–1463 (2016)

Borghetti, J., Snider, G.S., Kuekes, P.J., Yang, J.J., Stewart, D.R., Williams, R.S.: Memristive’ switches enable ‘stateful’ logic operations via material implication. Nature 464(7290), 873–876 (2010)

Zhang, Y., Shen, Y., Wang, X.P., Cao, L.N.: A novel design for memristor-based logic switch and crossbar circuits, IEEE Trans. Circuits Syst. I Reg. Papers 62(5), 1402–1411 (2015)

Waser, R., Dittmann, R., Staikov, G., Szot, K.: Redox-based resistive switching memories—Nanoionic mechanisms, prospects, and challenges. Adv. Mater. 21(25–26), 2632–2663 (2009)

Baghel V. S. and Akashe S.: Low Power Memristor Based 7T SRAM Using MTCMOS Technique. 2015 Fifth International Conference on Advanced Computing & Communication Technologies, Haryana, India, 222–226(2015).

Itoh, M., Chua, L.O.: Memristor oscillators. Int. J. Bifurcation Chaos 18(11), 3183–3206 (2008)

Bao, B.C., Liu, Z., Xu, J.P.: Steady periodic memristor oscillator with transient chaotic behaviours. Electron. Lett. 46(3), 237–238 (2010)

Pan, C., Hong, Q., Wang, X.: A novel memristive chaotic neuron circuit and its application in chaotic neural networks for associative memory. IEEE Trans. Comput-Aided Des. Integr. Circuits Syst. 40(3), 521–532 (2021)

Halawani, Y., Mohammad, B., Al-Qutayri, M., Al-Sarawi, S.F.: Memristor-based hardware accelerator for image compression. IEEE Trans. Very Large Scale Integr. Syst. 26(12), 2749–2758 (2018)

Yesil, A., Babacan, Y., Kaçar, F.: A new DDCC based memristor emulator circuit and its applications. Microelectron. J. 45(3), 282–287 (2014)

Abuelma’atti, M.T., Khalifa, Z.J.: A continuous-level memristor emulator and its application in a multivibrator circuit. AEU-Int J Electron. Commun. 69(4), 771–775 (2015)

Sánchez-López, C., Carrasco-Aguilar, M.A., Muñiz-Montero, C.: A 16Hz–160kHz memristor emulator circuit. AEU-Int. J. Electron. C. 69(9), 1208–1219 (2015)

Vista, J., Ranjan, A.: A simple floating MOS-memristor for high-frequency applications. IEEE Trans.Very Large Scale Integr. Syst. 27(5), 1186–1195 (2019)

Sözen, H., Çam, U.: Electronically tunable memristor emulator circuit. Analog Integr. Circ. Sig. Process 89, 655–663 (2016)

Kumar N., Kumar M. & Pandey N.: Single DXCCTA based Charge Controlled Floating Incremental/Decremental Memristor Emulator. 2022 8th International Conference on Signal Processing and Communication (ICSC), Noida, India, 663–668(2022).

Gupta, S., Rai, S.K.: New grounded and floating decremental/incremental memristor emulators based on CDTA and its application. Wireless Pers. Commun. 113(2), 773–798 (2020)

Petrovic, P.: A universal electronically controllable memelement emulator based on VDCC with variable configuration. Electronics 11, 3657 (2022)

Ghosh, M., Mondal, P., Borah, S.S., Kumar, S.: Resistorless memristor emulators: floating, grounded using OTA and VDBA for high frequency applications. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 42, 978–986 (2022)

Raj, N., Ranjan, R.K., Khateb, F.: Flux-controlled memristor emulator and its experimental results. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 28(4), 1050–1061 (2020)

Shankar, C., Singh, S.V., Imam, R.: SIFO–VM/TIM universal biquad filter using single DVCCTA with fully CMOS realization. Analog Integr. Circ. Sig. Process 109, 33–46 (2021)

Memristive model of amoeba learning. Phys. Rev. E, Stat. Phys. Plasmas Fluids Relat. Interdiscip. Top.80, 2009, Art. no. 021926.

Acknowledgements

The authors would like to acknowledge Swati Verma for her valuable insights and suggestions.

Funding

This research was conducted without receiving any funding from public, commercial, or not-for-profit sectors.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors would like to assert that there are no conflicts of interest regarding this research study.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Bhuwal, N., Majumder, M.K. & Gupta, D. Floating/grounded charged controlled memristor emulator using DVCCTA. J Comput Electron 23, 899–909 (2024). https://doi.org/10.1007/s10825-024-02176-3

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-024-02176-3