Abstract

As an emerging nanodevice, Quantum-dot cellular automata (QCA) is a hopeful candidate for conventional complementary metal oxide semiconductor devices. XOR, one of the most vital gates, occupies a significant positon in digital logic circuits. In order to improve the property performance of XOR, a novel five-input majority gate is put forward first. Then, an efficient XOR employing a NAND-NOR-Inverter (NNI) and the proposed five-input majority voter is realized in the paper. Compared with previous counterparts based on gates, the proposed design requires fewer cells, occupies less area, and consumes less average energy consumption. Specifically, it improves by 11.11% in cell count, 2.11% in area, and 9.51% (1.5Ek) in energy consumption when compared to the state-of-the-art design. The clock delay of the XOR in the article keeps the same with the minimum of them. Additionally, the proposed design has the lowest QCA cost, including area-delay cost, QCA-specific cost, and energy-delay cost. Moreover, the design is coplanar, without any crossing types. All these make it an outstanding design. To demonstrate its practicality, n-bit parity generators using the proposed XOR are implemented. The novel 4-bit parity generator excels in cell count, area, and average energy dissipation, achieving optimization of up to 10.6%, 6.0%, and 38.6% (0.5Ek), respectively, compared to previous optimum values. The significance of these optimization results becomes more pronounced as the bit of parity generators increases, indicating a promising future for constructing complex circuits.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

The feature size of traditional devices is scaling and the integration density is increasing with the rapid development of CMOS technologies, which leads to ever-growing problems, quantum effects, high leakage current and energy dissipation for instance (Sheikhfaal et al. 2015a). Searching for alternatives like novel nanodevices may be an efficient solution. Nanodevices include Carbon Nano Tube (CNT) (Bachtold et al. 2001), Single Electron Transistor (SET) (Kastner 1992), Tunneling-phase-logic (TPL) (Fahmy and Kiehl 1999), Quantum-dot Cellular Automaton (QCA) (Lent et al. 1993) and so on. Among them, QCA utilizing the Coulomb interaction between electrons doesn’t have traditional transistors and possesses the characteristics of high switching rate (Seminario et al. 2004), high integration density (DeHon and Wilson 2004), low energy dissipation (Farazkish et al. 2008) etc., which makes it one of the most promising candidates (Henderson et al. 2004). In recent years, QCA has been intensively studied and achieves a rapid development.

XORs are considered as one of the important modules in digital circuit design since they are frequently used in full adders, parity generators, shifting registers, default detecting circuits etc. (Kumar et al. 2017). Thus, a XOR with high performance is of great importance in improving circuit efficiency. As a complicated gate, XOR can be constituted with elementary gates, majority gates, NOT and NNI gates for example. The proposed gate-based XORs are manifold and can be classified into five different constructions according to components: (1) using three three-input majority gates (M3) and NOT gates (Jagarlamudi et al. 2011; Shah et al. 2012; Roohi et al. 2011; Suresh and Ghosh 2014; Kianpour et al. 2014; Mohammadi et al. 2017; Khosroshahy et al. 2017; Chabi et al. 2014; Singh et al. 2016; Mustafa and Beigh 2013; De et al. 2016; Teja et al. 2008; Beigh et al. 2013); (2) consist of four three-input majority gates and NOT gates (Mustafa and Beigh 2013; Beigh et al. 2013; Poorhosseini and Hejazi 2018); (3) based on a three-input majority gate, a five-input majority gate (M5) and NOT gates (Chabi et al. 2014; Singh et al. 2016; Angizi et al. 2014; Sasamal et al. 2018; Sheikhfaal et al. 2015b; Mohammadi and Navi 2018); (4) realized using four NNIs (Poorhosseini and Hejazi 2018); (5) employing a five-input majority gate and NNI (Zhang et al. 2020). In the hard work of researchers to seek for more efficient circuits, the properties of XORs are obtained optimization continuously.

The main contributions of the work in the article are summarized as follows. (1) A novel five-input majority gate is proposed to construct an efficient XOR using the fifth structure mentioned above (a five-input majority gate and NNI); (2) Compared with the existing designs, XOR put forward in the paper shows superiority with respect to physical properties; (3)Also, n-bit parity generators implemented utilizing the state-of-the-art XOR describe a bright application prospect.

The paper proceeds as follows. Section 2 reviews the basics of QCA. In Sect. 3, previous XOR designs are categorized into five types according to the rule referred to in Sect. 1. The new scheme of XOR and one of its applications-parity generators are presented and discussed in Sect. 4. And Sect. 5 concludes the work.

2 QCA basics

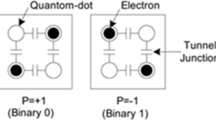

The elementary unit of QCA is QCA cells. As shown in Fig. 1a, a standard cell comprises four quantum dots and two free electrons. The electrons can tunnel between these quantum dots and are liable to occupy the diagonal positions because of the Coulomb interaction. Thus, the cell exists two steady states, namely polarization value \(P = - 1\) and \(P = + 1\), described in Fig. 1b, which is used to represent binary logic “0” and logic “1” respectively.

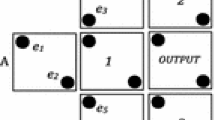

As the primary gates in QCA, the majority voter and NOT gate can be used to realize all the complicated circuits theoretically. The inputs of majority voters include three inputs and five inputs. Figure 2a is a three-input majority voter (M3), whose logic function is shown in Eq. (1). A AND logic will be achieved if fixing one of the three inputs to the polarity value \(P = - 1\), as presented in Fig. 2b. Similarly, if the fixed polarity value is replaced by \(P = + 1\), a OR function will be acquired, as illustrated in Fig. 2c. Equation (2) is the expression of the five-input majority gate (M5), and its QCA structures have numerous forms. NNI can also be regarded as an elementary gate, whose logic function is shown in Eq. (3) (Sen and Sikdar 2007). Figure 3a exhibits the QCA structure of NNI. The truth table of NNI is shown in Table 1, which is in accord with the simulation results shown in Fig. 3b using the simulation tool QCADesigner. The bistable approximation simulation engine parameters of the tool is presented in Table 2. Based on these most basic gates above, any complicated circuits can be achieved in theory.

QCA clock is applied to control the direction of the information flow normally (Lent and Tougaw 1997). QCA clock employing the quasi-adiabatic switch clock scheme contains four phases, namely switch, hold, release and relax, as shown in Fig. 4. \(\pi {/2}\) delay exists each of these adjacent phases. A complete clock cycle has four clock zones called clock 0, clock 1, clock 2 and clock 3. And the information transmits according to the direction of clock \({0} \to {1} \to {2} \to {3} \to {0} \to {1} \to \cdot \cdot \cdot\). The QCA clock scheme guarantees that the data will be flow follow the scheduled path.

3 Classification of existing XORs

Existing XORs can be grouped into five types according to the components utilized, as presented in Table 3.

4 New design schemes

4.1 Novel five-input majority voter

The novel XOR is designed using the fifth construction (a NNI and a five-input majority voter) in Table 3 with the logic function shown in Eq. (4). In order to achieve high-performance XOR, an excellent five-input majority voter is needed. Figure 5a exhibits the QCA structure of the five-input majority voter proposed in the paper. Since two inputs of the five-input majority voter are the same, as shown in Eq. (4), these two equal inputs are designed to share a common input called D. The other three inputs are A, B and C, and F is the output of the proposed five-input majority voter. Thus, the voter can gain the majority function among A, B, C, D and D, as is shown in Table 4. Figure 5b shows the simulation result of the proposed voter.

4.2 Novel XOR

A new XOR is designed based on the five-input majority voter proposed above and NNI, as shown in Fig. 6a. Figure 6b presents the simulation result, which demonstrates the correctness of the function. In order to illustrate the superiority of the design, XOR in the paper is compared with previous ones in terms of cell count, area, clock delay, cross structure and average energy dissipation, as shown in Tables 5, 6 and Figs. 7, 8, 9 and 10. Through the analysis of these figures, XOR in the article has the least cell count (24 cells), the least area (0.0186 µm2), the least clock delay (0.75) and the least average energy dissipation. At the same time, the novel XOR design can easily be accessed with no crossover (Chaudhary et al. 2007). Figure 11 presents the power dissipation map for the proposed XOR gate at 0.5Ek tunneling energy level and 2.0 K temperature.

The cost of a QCA circuits is also an important parameter for performance analysis. Area-delay cost (ADC), QCA-specific cost (QSC) and Energy-delay cost (EDC) are calculated respectively according to the formulas presented in Khan and Arya (2022). The area delay cost can be obtained using (Area) × (latency)2. The QCA-specific cost is (MV2 + IN + CV2) × CK2, where MV, IN, CV and CK represent the number of utilized majority voters, inverters, crossovers and clocks, respectively. E2 × D2 is used to calculate the energy-delay cost, where E is the dissipated energy and D is the latency. The cost calculation results of XORs are shown in Table 7 and the graphical view of comparisons are shown in Figs. 12, 13 and 14, respectively. Through these comparisons, Area-delay cost, QCA-specific cost and Energy-delay cost of the proposed XOR always keep the minimum.

All these comparisons certify that the proposed XOR possesses the excellent properties.

4.3 Proposed parity generators

Utilizing the proposed XOR above, n-bit parity generators are implemented to illustrate the practicability. Figure 15a is the QCA circuit of 4-bit parity generator with 76 cells and 0.0820 µm2. A 0.25 clock delay (clock 3) is added to the connection between adjacent XORs so as to hold the original clock design of the XOR, which provides convenience to construct high-bit parity generators. The simulation result of the proposed 4-bit parity generator is shown in Fig. 15b.

A comparison between the 4-bit parity generator in the paper and existing designs in cell count, area and average energy dissipation is needed to demonstrate the performance. Since the structure of the proposed circuit is coplanar with no rotated cells, the selected counterparts have the same characteristics, as shown in Fig. 16. The results can be seen from Table 8 and Figs. 17, 18 and 19. By contrasting the data, the novel 4-bit parity generator has the least values in term of cell count, area and average energy dissipation, up to 10.6%, 6.0% and 38.6% (0.5Ek) optimization compared to previous optimum values respectively. Therefore, the 4-bit parity generator based on XORs proposed in the paper has an excellent performance. Since the XOR is the elementary unit to construct the n-bit parity generators, the bit is higher, the optimization results are more significant. Figure 20 is the QCA design of the 32-bit parity generator.

5 Conclusion

XOR occupies a significant position in algorithmic logic. To improve the physical properties of XOR, an efficient five-input majority voter is designed. Based on the proposed five-input majority voter and NNI, a novel XOR is implemented. The proposed coplanar XOR has an excellent performance with less cell count, area, energy dissipation, and QCA cost. Moreover, the inputs and output of the design are easier to access without any crossovers since they locate on the outside of the structure. The 4-bit parity generator utilizing the novel XOR also presents outstanding physical property improvement in cell count, area and energy dissipation compared to its counterparts. Since the XOR is the elementary unit to construct the n-bit parity generators, the bit is higher, the optimization results will be more significant. Based on the proposed XOR and 5-input majority gate, high-efficiency full adders will be constructed in the future.

Data availability

The data used in the paper are available from the corresponding author on reasonable request.

References

Angizi, S., Alkaldy, E., Bagherzadeh, N., et al.: Novel robust single layer wire crossing approach for exclusive OR sum of products logic design with quantum-dot cellular automata. J. Low Power Electron. 10(2), 259–271 (2014)

Bachtold, A., Hadley, P., Nakanishi, T., Dekker, C.: Logic circuits with carbon nanotube transisitors. Science 294(5545), 1317–1320 (2001)

Beigh, M.R., Mustafa, M., Ahmad, F.: Performance evaluation of efficient XOR structures in quantum-dot cellular automata (QCA). Circ. Syst. 4(2), 147–156 (2013)

Chabi, A.M., Sayedsalehi, S., Angizi, S., et al.: Efficient QCA exclusive-or and multiplexer circuits based on a nanoelectronic-compatible designing approach. Int. Sch. Res. Notices 2014, 1–9 (2014)

Chaudhary, A., Chen, D.Z., Hu, X.S., Niemier, M.T., et al.: Fabricatable interconnect and molecular QCA circuits. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 26(11), 1978–1991 (2007)

De, D., Purkayastha, T., Chattopadhyay, T.: Design of QCA based programmable logic array using decoder. Microelectron. J. 55(2), 92–107 (2016)

DeHon A., Wilson M.J.: Nanowire-based sublithographic programmable logic arrays. In: Proceedings International Symposium on Field-Programmable Gate Arrays, 123–132 (2004)

Fahmy H. A., Kiehl R. A.: Complete logic family using tunneling-phase-logic devices. In: Proceedings of the IEEE International Conference Microelectronics, Kuwait City, Kuwait, 22–24 (1999)

Farazkish, R., Azghadi, M.R., Navi, K., Haghaparast, M.: New method for decreasing the number of quantum dot cells in QCA circuits. World Appl. Sci. J. 4(6), 793–802 (2008)

Henderson, S.C., Johnson, E.W., Janulis, J.R., Tougaw, P.D.: Incorporating standard CMOS design process methodologies into the QCA logic design process. IEEE Trans. Nanotechnol. 3(1), 2–9 (2004)

Jagarlamudi, H.S., Saha, M., Jagarlamudi, P.K.: Quantum dot cellular automata based effective design of combinational and sequential logical structures. Int. J. Comput. Electr. Autom. Control Inf. Eng. 5(12), 1529–1533 (2011)

Kastner, M.A.: The single-electron transistor. Rev. Mod. Phys. 64, 849–858 (1992)

Khan, A., Arya, R.: Towards cost analysis and energy estimation of simple multiplexer and demultiplexer using quantum dot cellular automata. Int. Nano Lett. 12, 67–77 (2022)

Khosroshahy, M.B., Moaiyeri, M.H., Angizi, S., et al.: Quantum-dot cellular automata circuits with reduced external fixed inputs. Microprocess. Microsyst. 50, 154–163 (2017)

Kianpour, M., Sabbaghi-Nadooshan, R., Navi, K.: A novel design of 8-bit adder/subtractor by quantum-dot cellular automata. J. Comput. Syst. Sci. 80(7), 1404–1414 (2014)

Kumar, D., Mitra, D., Bhattacharya, B.B.: On fault-tolerant design of exclusive-OR gates in QCA. J. Comput. Electron. 16(3), 896–906 (2017)

Lent, C.S., Tougaw, P.D.: A device architecture for computing with quantum dots. Proc. IEEE 85(4), 541–557 (1997)

Lent, C.S., Tougaw, P.D., Porod, W., Bemstein, G.H.: Quantum cellular automata. Nanotechnology 4(1), 49–57 (1993)

Mohammadi, H., Navi, K.: Energy-efficient single-layer QCA logical circuits based on a novel XOR gate. J. Circ. Syst. Comput. 27(14), 1–19 (2018)

Mohammadi, M., Gorgin, S., Mohammadi, M.: Design of non-restoring divider in quantum-dot cellular automata technology. IET Circuits Devices Syst. 11(2), 135–141 (2017)

Mustafa, M., Beigh, M.R.: Design and implementation of quantum cellular automata based novel parity generator and checker circuits with minimum complexity and cell count. Indian J. Pure Appl. Phys. 51(1), 60–66 (2013)

Poorhosseini, M., Hejazi, A.R.: A fault-tolerant and efficient XOR structure for modular design of complex QCA circuits. J. Circ. Syst. Comput. 27(7), 1–24 (2018)

Roohi, A., Khademolhosseini, H., Sayedsalehi, S., et al.: A novel architecture for quantum-dot cellular automata multiplexer. Int. J. Comput. Sci. Issues 8(6), 55–60 (2011)

Sasamal, T.N., Singh, A.K., Ghanekar, U.: Design and analysis of ultra-low power QCA parity generator circuit. Adv. Power Syst. Energy Manag. 436, 347–354 (2018)

Seminario, J.M., Derosa, P.A., Cordova, L.E., et al.: A molecular device operating at terahertz frequencies: theoretical simulations. IEEE Trans. Nanotechnol. 3(1), 215–218 (2004)

Sen B., Sikdar B. K.: Characterization of universal nand-nor-inverter. VDAT. In: Proceedings of 11th IEEE VLSI Design and Test Symposium (2007)

Shah, N.A., Khanday, F.A., Iqbal, J.: Quantum-dot cellular automata (QCA) design of multi-function reversible logic gate. Commun. Inf. Sci. Manag. Eng. 2(4), 8–18 (2012)

Sheikhfaal, S., Navi, K., Keivan, A., et al.: Designing high-speed sequential circuits by quantum-dot cellular automata: memory cell and counter study. Quantum Matter 4(2), 190–197 (2015a)

Sheikhfaal, S., Angizi, S., Sarmadi, S., Moaiyeri, M.H.: Designing efficient QCA logical circuits with power dissipation analysis. Microelectron. J. 46(6), 462–471 (2015b)

Singh, G., Sarin, R.K., Raj, B.: A novel robust exclusive-OR function implementation in QCA nanotechnology with energy dissipation analysis. J. Comput. Electron. 15(2), 455–465 (2016)

Suresh, K., Ghosh, B.: Ripple carry adder using two XOR gates in QCA. Mater. Sci. Mech. Eng. 467, 531–535 (2014)

Teja, V.C., Polisetti, S., Kasavajjala, S.: QCA based multiplexing of 16 arithmetic & logical subsystems-A paradigm for nano computing. IEEE Int. Conf. Nano/micro Eng. Mol. Syst. 1–3, 758–763 (2008)

Zhang, Y.Q., Deng, F.F., Cheng, X., Xie, G.J.: Coplanar XOR using NAND-NOR-inverter and five-input majority voter in quantum-dot cellular automata technology. Int. J. Theor. Phys. 59(2), 484–501 (2020)

Funding

The authors have not disclosed any funding.

Author information

Authors and Affiliations

Contributions

MS contributed to all the work of the paper.

Corresponding author

Ethics declarations

Conflict of interest

The author declares no conflict of interests.

Ethical approval

The author declares that there is no conflict with publication ethics.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Sun, M. An efficient XOR design based on NNI and five-input majority voter in quantum-dot cellular automata. Opt Quant Electron 56, 159 (2024). https://doi.org/10.1007/s11082-023-05729-1

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s11082-023-05729-1