Abstract

Quantum-dot cellular automata (QCA) is a rapidly intensifying nanotechnology that promises ultra-low power consumption, high speed, and ultra-small area requirements. Multiplexer and demultiplexer are the two fundamental and unavoidable blocks in quantum computation or nano communication using QCA. Two significant factors in evaluating the performance of a QCA circuit are energy dissipation and cost function. The total energy dissipation of the QCA multiplexer is 13 meV, whereas, the total energy dissipation of the demultiplexer is 10.4 meV utilizing QDE. The total energy dissipation of the multiplexer employing QCAPro at a fixed temperature of 2 K and a tunneling level of γ = 0.5EK is 21.67 meV, while the same for demultiplexer is 32.86 meV. The Runge–Kutta approximation approach was used to estimate energy using the tool QDE in the Coherence vector energy mode. In addition, the costs of both experimental objects have been determined. Multiplexer and demultiplexer area-delay costs (m2-cc) are 0.002 and 0.005, respectively; multiplexer QCA-specific cost is 90 scp, and demultiplexer QCA-specific cost is 20 scp; multiplexer and demultiplexer energy-delay costs (seV–scc) are 0.000206 and 0.000429, respectively.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

Introduction

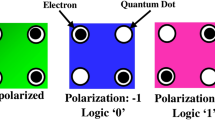

Formerly, complementary metal–oxide–semiconductor (CMOS) technology has been the leading technology to design Very Large Scale Integrated circuits or nano-electronic circuits. But currently, CMOS technology is impending to its physical limitations [1, 2]. One of the best alternatives to carry forward nano-level design is the emerging quantum-dot cellular automata (QCA). It was introduced by Lent et al. [1, 2]. This QCA technology is mainly based on tunneling two electrons inside four quantum dots QCA cell [2]. A cell, as shown in Fig. 1, is the smallest unit of QCA technology. Two electrons inside a cell may choose any of the four dots located at each corner of the square. However, due to Coulombic interaction, those two electrons always elect diagonal positions [1, 2]. Therefore, as shown in Fig. 1, two arrangements are possible: polarization ‘− 1’ or logic 0 and polarization ‘ + 1’ or logic 1. QCA was first fabricated in 1997 [3].

The fundamental blocks of QCA are majority voter, wire, and inverter, which can be used to design different logic circuits. A majority voter has three inputs and one output, as shown in Fig. 2 [4]. The middle cell of the majority voter is called the driver cell. Among three inputs, one of them may be fixed at polarization ‘ − 1’ then it works as AND gate, and if one of the inputs is set at polarization ‘ + 1’, it acts as OR gate [4]. As shown in Fig. 2, it follows the equation AB + BC + CA for three inputs A, B, and C. As shown in Fig. 3, when few cells are positioned back to back, they form a chain, called wire and the input polarization reaches at the output without alteration [5]. As shown in Fig. 4, when two cells are located diagonally, it acts as a NOT gate, called QCA inverter [4].

No separate supply of bias voltage is necessary for these circuit operations; instead, QCA can perform processes using four internal clocks, which assured low power depletion [5]. There are four phases of each clock as shown in Fig. 5, and they are known as the switch phase, the hold phase, the release phase, and the relax phase [6].

In the QCA field, extensive research work has been done yet, primarily in the design and simulation of digital circuits. Logic gates [7, 8], adders [9, 10], subtractors [11, 12], Adder–subtractors [13, 14], flip-flops and memories [15, 16], registers [17,18,19], counters [20, 21], Arithmetic Logic Units [22, 23] etc. already been reported. Recently researchers are focusing on nano communication, where multiplexer and demultiplexer are the unavoidable design units. One simple multiplexer [24] and one simple demultiplexer [25] are the experimental objects of this article. It should be mentioned that both the experimental entities, i.e., multiplexer and demultiplexer, are elementary as they occupied a minimal area, and their complexity is low too. This multiplexer has a complexity of 17, cell area of 0.005508 μm2 and a total area of 0.01 μm2; whereas, demultiplexer has the complexity of 21, cell area 0.006804 μm2, and total area of 0.02 μm2 [24, 25]. The calculation of energy dissipation and the cost of simple circuits are the recent trends of QCA technology, which accelerate us to do this research work. Most semiconductor and electronics industries that work on quantum computation, nano-computation, and nano-communication, for example, are active in the development and implementation of QCA-based circuits. It is worth mentioning that QCA multiplexer and demultiplexer have devoted applications in nano communication and nano computation, like nanoswitch, nano router, reversible computing circuits, etc.

Former works and gaps

The QCA literature is clogged with multiplexers and demultiplexers. There have been a few good designs in the last few years that have been mentioned. Roohi et al. (2011) used three clocks with a complexity of twenty-seven to create a 2:1 multiplexer [26]. Kianpour et al. (2013) offered a basic multiplexer with twenty-two cells and three clocks [27], whereas, Chabi et al. (2014) proposed a similar multiplexer with twenty-three cells and the same three clock zones [28]. Similarly, Sen et al. (2015) used twenty-three cells but just two clocks to construct an efficient 2:1 multiplexer [29]. Rashidi et al. [30] developed a fifteen-cell multiplexer with a cell area of 0.01 µm2. Das et al. used three majority voters and one inverter to demonstrate a 2:1 multiplexer. They calculated that 47.22% of the available area was used [31]. Rashidi et al. used two AND gates, one OR gate, and one NOT gate to create a multiplexer [32]. Asfestani et al. created an efficient QCA multiplexer structure without utilizing majority votes [33]. Khosroshahy et al. looked at a different method of lowering the number of external inputs in multiplexers [34]. Ahmad proposed an n-bits multiplexer design strategy, while Ahmadpour et al. built fault-tolerant multiplexers employing four clocks with a complexity of 36 [35, 36]. Mosleh [37] discusses a multilayer design method based on the new majority voter (MV32) concept. Xingjun et al. reported a 2:1 multiplexer with only 22 cells and a 0.03 µm2 surface area [38]. AlKaldy et al. recently constructed an optimal multiplexer with only 11 cells and no majority voters [39]. Similarly, there are many more design examples of QCA multiplexers in the literature, leading to a lengthy discussion. It is not, however, valid for the QCA demultiplexer unit. There is a dearth of contributions to demultiplexer design despite the abundance of multiplexers in the QCA literature. To keep the flow of this part going, we're bringing up a few good demultiplexers here. For higher-order circuit design, Shah et al. presented a modular demultiplexer with 56 cells [40]. Iqbal et al. [41] suggested another modular 1:2 demultiplexer with a complexity of 27. A demultiplexer for nano communication applications was designed by Sardinha et al. [42]. Safoev et al. contributed to a multilayer layout of a 1: 2 demultiplexer [43], which used two clocks and 21 cells. Ahmad presented a 21-cell demultiplexer, while Das et al. recommended a 32-cell demultiplexer [35, 44]. Except for the QCA demultiplexers listed above, there are few designs and analyses of demultiplexers in the literature. The number of research papers with demultiplexers, on the other hand, is never more remarkable than the research of the QCA multiplexer.

It is worth mentioning that the experimental multiplexer architecture was reported at [24], and the energy dissipation was computed using the QDE Coherence vector mode applying the Euler technique at [45]. The energy dissipation using the Ranga Kutta approximation, on the other hand, has yet to be done. Similarly, an exhaustive cost analysis for this multiplexer is still unavailable. On the other hand, the experimental demultiplexer was proposed in [25], and the energy dissipation was estimated using the Euler technique in the same study [25]. Nonetheless, thorough cost analysis and energy dissipation in a QDE context applying the Ranga Kutta approximation are still needed for the demultiplexer.

As a result, the energy analysis of basic multiplexer/demultiplexer adopting Ranga Kutta approximation using QCADesigner-E (QDE) is still vacant in the QCA literature. None of the research fully described the several forms of costs associated with QCA circuits for a more precise analysis.

This study addressed all of the aforementioned gaps in the literature by examining one primary multiplexer and one simple demultiplexer. The originality of this work includes the energy estimation by QDE in Coherence vector mode employing Ranga Kutta approximation. In addition, different cost functions and other design elements have been incorporated for a higher evaluation.

Projected experimental objects

This article's experimental entities are a QCA multiplexer [24] and a QCA demultiplexer [25]. Using the QCA methodology, the arrangement of both units is simple to design. In a 2:1 multiplexer, the select line is ‘S’ the inputs are ‘M’ and ‘N’ and the output is ‘O’ In a 1:2 demultiplexer, the select line is ‘S’ the input data is ‘O’ and the outputs are ‘M’ and ‘N’ The relevant truth table is shown in Table 1, and the projected experimental objects are Figs. 6 and 7 [24, 25]. The multiplexer has a complexity of 17, and the demultiplexer has a complexity of 21, which is relatively low in terms of design perspective. The multiplexer's cell area is 5508 nm2, while the demultiplexer's cell area is 6804 nm2, indicating the minimal area requirements [24, 25]. Figures 8 and 9 illustrate the simulation output of the multiplexer and demultiplexer, respectively.

Simple QCA multiplexer unit [24]

Simple QCA demultiplexer unit [25]

Simulation output of QCA multiplexer [24]

Simulation output of QCA demultiplexer [25]

Parameters analysis of projected items

The decisive variables for measuring the performance of QCA circuits include cell complexity or cell count, area needed for designing the circuit, percentage of cell area used from the total area, delay or latency, number of gates used to design the circuit, and number of employed crossovers. This sub-section goes over all of the critical parameters for the present experimental objects.

This 2:1 multiplexer's cell complexity, or the number of employed cells, is 17, while this 1:2 demultiplexer's cell-complexity is 21.

The multiplexer requires 0.005508 μm2 of cell area, whereas, the demultiplexer requires 0.006804 μm2. The projected multiplexer requires 0.01 μm2 of total space, while the demultiplexer requires 0.02 μm2. Therefore, the area usage of the projected multiplexer is 55.08%, and the area usage of the demultiplexer is 34.02%.

Latency, often known as delay, is the time difference between the output and the input. The input-to-output latency is what it's known as. The number of clocks used for successful simulation of the multiplexer and the demultiplexer is three and two. Therefore, the latency for both of the experimental items is 0.5 clock-cycle. It's worth noting that one clock cycle is equal to four clock zones or clock phases.

The number of majority voters or majority gates and the number of inverters utilized in the multiplexer architecture is 3 and 1, respectively. The number of majority voters and inverters used in the demultiplexer are 2 and 1, respectively.

There was no crossover employed in the construction of the QCA arrangement for both experimental items.

Current experiments and evaluations

This work is unique in that it performs extensive energy calculations and calculates the cost of the projected items. The energy calculation methods for 2:1 MUX and 1:2 DeMUX are described in this section.

Energy calculations

Energy estimation has been popular in QCA circuit analysis recently. QCAPro [46] is a standard energy calculation tool. It is a widely used and well-known energy computation tool. It would not work with any newer versions of QCADesigner, unfortunately. QCAPro works with an older version of QCADesigner, which the proprietor has discontinued. As a result, QCADesigner 2.0.3 does not currently support QCAPro on top of it.

QCADesigner-E, or QDE, on the other hand, is a relatively new tool that is fast gaining traction. Using this program, we computed the energy dissipation of the multiplexer and demultiplexer. To compute energy dissipation using QDE, both approximations (the Euler technique or the Ranga–Kutta approach) can be utilized. The energy was previously computed using the Euler approach in [25, 45]. However, the same has yet to be reported using the Ranga–Kutta approximation.

To maintain the continuity of the discussion, a little amount of discussion on QCAPro is required. Using the QCAPro tool, we can evaluate the non-adiabatic power loss or energy dissipation of QCA circuits. It is based on the popular Hartree–Fock approximation [46, 48, 49]. The overall energy of the QCA cell is determined using the following Hamiltonian matrix [46] as described in Eq. (1), which represents the Coulombic interaction between cells:

Here Ci indicates the polarization of ith adjacent cell, fi,j is the geometrical factor related to electrostatic interaction between ith cell and jth cell and γ is tunneling energy between two cell states [46, 48, 49]. For every clock cycle, the expectation energy value of the cell is derived from Eq. (2) below:

The instantaneous power of a QCA cell is given as:

where λ is the coherence vector, Γ is the energy vector (three-dimensional), and \({\hbar}\) is the reduced Planck’s constant.

The first term of Eq. (3) is \(\frac{{\hbar} }{2} \left[ \frac{ {\rm d}\Gamma } {{\rm d}t.\lambda } \right]\). It is the combination of the cell-to-cell power and clock-in–out power [50].

The second term of the Eq. (3) is \(\frac{{\hbar} }{2}\left[ {\Gamma .\frac{{{\text{d}}\lambda }}{{{\text{d}}t}}} \right]\) and it is our interest as it is instantaneous dissipated power [50]. For a time interval [− T, + T], the energy dissipation is expressed as:

Using a similar fashion, we can calculate the leakage energy dissipation and switching energy dissipation using Eqs. (5) and (6), respectively [50]:

The power dissipation may be determined in different tunneling energy levels (e.g., γ = 0.5EK, γ = 1.0EK, γ = 1.5EK, etc.) at fixed temperature using QCAPro. However, this work explored the energy dissipations exclusively for two tunneling levels, γ = 0.5EK, γ = 1.0EK and temperature kept fixed at 2 K. At 2 K temperature and 0.5EK tunneling level, the total energy dissipation of the multiplexer and demultiplexer is 21.67 meV, and 32.86 meV, respectively. At 1.0EK, the same is 28.70 meV and 41.41 meV, respectively. The leakage energy dissipations and switching energy dissipations can also be calculated using a similar method; however, this article only looked at the overall energy dissipations.

QCADesigner-E, often known as QDE [47], is a new energy estimation tool that is based on the famous QCADesigner [51]. The energy dissipation was computed using the Runge–Kutta approach [47]. The QCA circuit can be thought of as an array of cells, with coordinate numbers assigned to each cell. During operation, the cell can be considered an energy bath. Let, E_BATH is the sum of all energy transfers to the ‘bath’ of all QCA cells separated for each clock cycle, and the total energy dissipation is \(\sum _{\mathrm{a}\mathrm{l}\mathrm{l}}E\_\mathrm{B}\mathrm{A}\mathrm{T}\mathrm{H}\) [52, 53]. \(\sum _{\mathrm{a}\mathrm{l}\mathrm{l}}E\_\mathrm{B}\mathrm{A}\mathrm{T}\mathrm{H}\) is the addition of three components of energy dissipation, and it is expressed as \(\sum _{\mathrm{a}\mathrm{l}\mathrm{l}}E\_\mathrm{B}\mathrm{A}\mathrm{T}\mathrm{H}={E}_{\mathrm{C}\mathrm{K}}+{E}_{\mathrm{E}\mathrm{V}}+{E}_{\mathrm{I}\mathrm{O}}\), where ECK is the sum of all energy transfers between QCA cells and the clock separated for each clock cycle, EEV is the energy that transfers QCA cells to the environment, and EIO is the energy transfer amongst QCA cells [52, 53]. Note that EIO = EIN – EOUT for QCA wire, where EIN = energy entering in the QCA cell and EOUT = energy leaving the QCA cell. ERR is the sum of all QCA cell’s energy analysis errors for each clock cycle, ERR = EEV − (ECK + EIO) [52, 53]. The positive energy value indicates that energy has been transferred to EEV, EIO, and ECK. The energy has been calculated using ‘array coordinates’ as introduced QDE, and we have used the Runge–Kutta approximation [52, 53]. The array coordinates are assigned as ‘[column number] [row number]’. At the coherence vector energy simulation mode, the simulation was performed on 500,000 samples. For the QCA multiplexer, the total energy dissipation is 13 meV with a slight error of − 0.639 meV. The average energy dissipation of the multiplexer per cycle is 1.18 meV with a minor error of − 0.0581 meV. In contrast, the total energy consumption of the demultiplexer is 10.40 meV, including a minor error of − 0.382 meV, and the average energy dissipation per cycle is 0.948 meV with a slight error of − 0.0348 meV.

Cost calculations

The cost of a QCA circuit is an important parameter to consider while evaluating its performance. It is also one of the recent QCA research trends to determine the cost of a circuit for a better performance evaluation.

Area-delay cost

It is the general cost of QCA circuits, and it is the metric that most researchers seek to find. It is determined by the overall area used to build the QCA layout as well as the output delay. This delay is also referred to as latency, the output delay in relation to the input. This latency or delay is expressed in the number of clocks. The latency of our experimental multiplexer and demultiplexer are the same, and it is 0.5 clock-cycle or 0.5 cc, which means half of a clock cycle. The area delay cost is expressed as (Area) × (latency)2 [50]. For our multiplexer the total area is 0.01 μm2 and the latency is 0.5 cc; therefore, the area-delay cost is ((0.01 × 10−12) × (0.5)2) = 0.002 × 10−12 m2-cc. Hence the calculated area-delay cost (× 1012) for the multiplexer is 0.002 m2-cc. Now the total area of our demultiplexer is 0.02 μm2 and the latency is 0.5 cc; thus, the area-delay cost is ((0.02 × 10−12) × (0.5)2) = 0.005 × 10−12 m2-cc. So, the area-delay cost (× 1012) of our demultiplexer is 0.005 m2-cc.

QCA-specific cost

This cost is primarily considered for QCA circuits. The figure of Merit (FoM) is another name for it [54, 55]. To build a QCA architecture, the number of utilized majority voters (MV), used inverters (IN), used clocks (CK), and used crossover (CV) are taken into account. The formula to calculate the QCA-specific cost or FoM is = ((MVm + IN + CVn) × CKp) [50, 54]. Here, m, n, and p are the experimental weightings for majority voter, crossover, and clock count (number of clock phase). In general, m = n = p = 2 considered as standard value [50, 54]. Because the number of majority voters, inverters, and crossovers are unit-less, QCA-specific cost is represented in square clock phases (scp). For our multiplexer, the QCA-specific cost is (32 + 1 + 0) × 32 = 90 scp and the QCA-specific cost of our demultiplexer is (22 + 1 + 0) × 22 = 20 scp. It’s important to know that one clock cycle means four clock phases (or four clock zones).

Energy-delay cost

We calculated the energy dissipation using QDE, but we also used QCAPro to determine the energy-delay cost based solely on the energy dissipation (eV) at the 1.0 EK tunneling level. It is worth noting that the same calculations can be applied to two more tunneling levels 0.5 EK and 1.5 EK. The energy-delay cost is calculated as (Ex × Dy), where E is the dissipated energy, D is the delay or latency, x = y = experimental weightings [49, 53]. The standard value of x = y = 2 is taken for our calculation [49, 53]. The unit of energy-delay cost is square eV–square clock cycles, or seV–scc, if energy dissipation is measured in eV and delay is measured in clock cycles (cc). Total energy dissipation of our multiplexer and demultiplexer at 2 K temperature with tunneling level 1.0 EK is 28.70 meV and 41.41 meV, respectively. The latency of the multiplexer and the demultiplexer is 0.5 cc. Therefore, the energy-delay cost of multiplexer is (28.70 × 10−3)2 × (0.5)2 = 2.06 × 10−4 seV–scc. Similarly, the energy-delay cost of demultiplexer is (41.41 × 10−3)2 × (0.5)2 = 4.29 × 10−4 seV–scc. Hence, the energy-delay cost (× 103) is 0.206 seV–scc and 0.429 seV–scc for multiplexer and demultiplexer, respectively.

Comparisons and discussion

For comparisons, we selected a few good designs from the QCA literature over the last five years (2016–2010). The computation of energy dissipation is one of the parameters that may be used to make better comparisons. However, most previously published studies did not account for the dissipated energy of the multiplexer or demultiplexer. Only Alkaldy et al. [36] and Ahmad [35] used QCAPro to calculate the multiplexer's dissipated energy. Furthermore, none of the previous work included an energy calculation for the demultiplexer. Interestingly, one of the key benefits of our work is that we employed Ranga–Kutta approximation using QDE to find the dissipated energy.

Another essential factor to consider is the cost. This parameter has been extensively discussed. We investigated three different forms of costs, but none of the previous work addressed them. According to area-delay cost (m2-cc), our multiplexer and demultiplexer are excellent designs as its area delay cost (× 1012) is 0.002 and 0.005, respectively. Similarly, the calculated QCA-specific cost or FoM (scp) of our multiplexer and demultiplexer are 90 and 20; these are also moderately good values. The energy-delay cost (× 103) in seV–scc of our multiplexer and demultiplexer are 0.206 and 0.429. It is worth noting that no previous research has estimated all of the cost parameters for multiplexers and demultiplexers. A detail of these values is presented in Table 2. Several graphical representations have been utilized to explain the results better; Figs. 10, 11, and 12 are pictorial views of comparisons for multiplexers, and Figs. 13, 14, and 15 are graphical views of comparisons for demultiplexers. Table 2 also includes a few generic metrics such as complexity, size, area consumption, clocks count, latency, and gate count to help comparisons. If all of the discussed parameters are measuring, we can conclude that our experimental items are efficient designs.

Conclusion and future scope

The QCA layouts of multiplexer and demultiplexer used in this experiment were made as small as possible in terms of circuit complexity, area requirements, and cost. The experimental research on energy estimation using QCAPro and QDE tools revealed that both circuits have low energy dissipation. This article is extremely important in today's QCA technology because it completely follows current design trends. This article measures three different sorts of costs. The basic multiplexer and simple demultiplexer's area-delay, QCA-specific, and energy-delay costs are addressed, proving that the objects are efficient enough. As a result, these little blocks devised a means for creating higher-order nano computational circuits, notably nano-communication devices such as nano-routers, where multiplexer and demultiplexer are unavoidable blocks.

References

Lent, C.S., Tougaw, P.D., Porod, W., Bernstein, G.H.: Quantum cellular automata. Nanotechnology 4(1), 49–57 (1993). https://doi.org/10.1088/0957-4484/4/1/004

Lent, C.S., Tougaw, P.D.: A device architecture for computing with quantum dots. Proc. IEEE 85(4), 541–557 (1997). https://doi.org/10.1109/5.573740

Orlov, A.O., Amlani, I., Bernstein, G.H., Lent, C.S., Snider, G.L.: Realization of a functional cell for quantum-dot cellular automata. Science 277(5328), 928–930 (1997). https://doi.org/10.1126/science.277.5328.928

Tougaw, P.D., Lent, C.S.: Logical devices implemented using quantum cellular automata. J. Appl. Phys. 75(3), 1818–1825 (1994). https://doi.org/10.1063/1.356375

Lent, C.S., Tougaw, P.D.: Lines of interacting quantum-dot cells: a binary wire. J. Appl. Phys. 74(10), 6227–6233 (1993). https://doi.org/10.1063/1.355196

Tóth, G., Lent, C.S.: Quasiadiabatic switching for metal-island quantum-dot cellular automata. J. Appl. Phys. 85(5), 2977–2984 (1999). https://doi.org/10.1063/1.369063

Kavitha, S. S., Kaulgud, N.: Quantum dot cellular automata (QCA) design for the realization of basic logic gates. In: 2017 International Conference on Electrical, Electronics, Communication, Computer, and Optimization Techniques (ICEECCOT), Mysuru, 2017, pp. 314–317 (2017). https://doi.org/10.1109/ICEECCOT.2017.8284519.

Balakrishnan, L., Godhavari, T., Kesavan, S.: Effective design of logic gates and circuit using quantum cellular automata (QCA). In: 2015 International Conference on Advances in Computing, Communications and Informatics (ICACCI), Kochi, 2015, pp. 457–462 (2015). https://doi.org/10.1109/ICACCI.2015.7275651.

Hashemi, S., Navi, K.: A novel robust QCA full-adder. Proc. Mater. Sci. 11(2015), 376–380 (2015). https://doi.org/10.1016/j.mspro.2015.11.133

Mohammadi, M., Mohammadi, M., Gorgin, S.: An efficient design of full adder in quantum-dot cellular automata (QCA) technology. Microelectron J 50(April 2016), 35–43 (2016). https://doi.org/10.1016/j.mejo.2016.02.004

Lakshmi, S. K., Athisha, G., Karthikeyan, M., Ganesh, C.: Design of subtractor using nanotechnology based QCA. In: 2010 international conference on communication control and computing technologies, Ramanathapuram, 2010, pp. 384-388 (2010). https://doi.org/10.1109/ICCCCT.2010.5670582

Ramachandran, S. S., Kumar, K. J. J.: Design of a 1-bit half and full subtractor using a quantum-dot cellular automaton (QCA). In: 2017 IEEE International Conference on Power, Control, Signals and Instrumentation Engineering (ICPCSI), Chennai, 2017, pp. 2324–2327 (2017). https://doi.org/10.1109/ICPCSI.2017.8392132.

Zoka, S., Gholami, M.: A novel efficient full adder–subtractor in QCA nanotechnology. Int Nano Lett 9, 51–54 (2019). https://doi.org/10.1007/s40089-018-0256-0

Raj, M., Gopalakrishnan, L., Ko, S.: Design and analysis of novel QCA full adder-subtractor. Int. J. Electron. Lett. (2020). https://doi.org/10.1080/21681724.2020.1726479

Hashemi, S., Navi, K.: New robust QCA D flip flop and memory structures. Microelectron. J. 43(12), 929–940 (2012). https://doi.org/10.1016/j.mejo.2012.10.007

Patidar, M., Gupta, N.: An efficient design of edge-triggered synchronous memory element using quantum dot cellular automata with optimized energy dissipation. J. Comput. Electron. 19, 529–542 (2020). https://doi.org/10.1007/s10825-020-01457-x

Kummamuru, R.K., Orlov, A.O., Ramasubramaniam, R., Lent, C.S., Bernstein, G.H., Snider, G.L.: Operation of a quantum-dot cellular automata (QCA) shift register and analysis of errors. IEEE Trans. Electron Devices 50(9), 1906–1913 (2003). https://doi.org/10.1109/TED.2003.816522

Purkayastha, T., De, D., Chattopadhyay, T.: Universal shift register implementation using quantum dot cellular automata. Ain Shams Eng. J. 9(2), 291–310 (2018). https://doi.org/10.1016/j.asej.2016.01.011

Taskin, B., Chiu, A., Salkind, J., Venutolo, D.: A shift-register-based QCA memory architecture. ACM J. Emerg. Technol. Comput. Syst. 5(1), 4.1-4.18 (2009). https://doi.org/10.1145/1482613.1482617

Yang, X., Cai, L., Zhao, X., Zhang, N.: Design and simulation of sequential circuits in quantum-dot cellular automata: falling edge-triggered flip-flop and counter study. Microelectron. J. 41(2010), 56–63 (2010). https://doi.org/10.1016/j.mejo.2009.12.008

Angizi, S., Moaiyeri, M.H., Farrokhi, S., Navi, K., Bagherzadeh, N.: Designing quantum-dot cellular automata counters with energy consumption analysis. Microprocess Microsyst. 39(7), 512–520 (2015). https://doi.org/10.1016/j.micpro.2015.07.011

Heikalabad, S.R., Gadim, M.R.: Design of improved arithmetic logic unit in quantum-dot cellular automata. Int. J. Theor. Phys. 57, 1733–1747 (2018). https://doi.org/10.1007/s10773-018-3699-1

Babaie, S., Sadoghifar, A., Bahar, A.N.: Design of an efficient multilayer arithmetic logic unit in quantum-dot cellular automata (QCA). IEEE Trans. Circ. Syst. II Express Briefs 66(6), 963–967 (2019). https://doi.org/10.1109/TCSII.2018.2873797

Khan, A., Mandal, S.: Robust multiplexer design and analysis using quantum dot cellular automata. Int. J. Theor. Phys. 58(3), 719–733 (2018). https://doi.org/10.1007/s10773-018-3970-5

Khan, A., Arya, R.: Optimal demultiplexer unit design and energy estimation using quantum dot cellular automata. J. Supercomput. (2020). https://doi.org/10.1007/s11227-020-03320-z

Roohi, A., Khademolhosseini, H., Sayedsalehi, S., Navi, K.: A novel architecture for quantum-dot cellular automata multiplexer. Int. J. Comput. Sci. Issues 8(1), 55–60 (2011)

Kianpour, M., Sabbaghi-Nadooshan, R.: Optimized design of multiplexor by quantum-dot cellular automata. Int. J. Nanosci. Nanotechnol 9(1), 15–24 (2013)

Chabi, A.M., Sayedsalehi, S., Angizi, S., Navi, K.: Efficient QCA exclusive-or and multiplexer circuits based on a nanoelectronic-compatible designing approach. Int. Schol. Res. Not. 2014(463967), 1–9 (2014). https://doi.org/10.1155/2014/463967

Sen, B., Goswami, M., Mazumdar, S., Sikdar, B.K.: Towards modular design of reliable quantum-dot cellular automata logic circuit using multiplexers. Comput Elect Eng 45(July 2015), 42–54 (2015). https://doi.org/10.1016/j.compeleceng.2015.05.001

Rashidi, H., Rezai, A., Soltany, S.: High-performance multiplexer architecture for quantum-dot cellular automata. J Comput Electron 15(September 2016), 968–981 (2016). https://doi.org/10.1007/s10825-016-0832-3

Das, J.C., De, D.: Optimized multiplexer design and simulation using quantum dot-cellular automata. Indian J. Pure Appl. Phys. 54(12), 802–811 (2016)

Rashidi, H., Rezai, A.: Design of novel efficient multiplexer architecture for quantum-dot cellular automata. J. Nano Electron. Phys. 9(1), 01012 (2017). https://doi.org/10.21272/jnep.9(1).01012

Asfestani, M.N., Heikalabad, S.R.: A unique structure for the multiplexer in quantum-dot cellular automata to create a revolution in design of nanostructures. Phys. B Phys. Conden. Matter 512(May 2017), 91–99 (2017). https://doi.org/10.1016/j.physb.2017.02.028

Khosroshahy, M.B., Moaiyeri, M.H., Angizi, S., Bagherzadeh, N., navi, K. : Quantum-dot cellular automata circuits with reduced external fixed inputs. Microprocess. Microsyst. 50(May 2017), 154–163 (2017). https://doi.org/10.1016/j.micpro.2017.03.009

Ahmad, F.: An optimal design of QCA based 2n:1/1:2n multiplexer/demultiplexer and its efficient digital logic realization. Microprocess. Microsyst. 56(February 2018), 64–75 (2017). https://doi.org/10.1016/j.micpro.2017.10.010

Ahmadpour, S., Mosleh, M.: A novel fault-tolerant multiplexer in quantum-dot cellular automata technology. J. Supercomput. 74(9), 4696–4716 (2018). https://doi.org/10.1007/s11227-018-2464-9

Mosleh, M.: A novel design of multiplexer based on nano-scale quantum-dot cellular automata. Concurr Comput Pract Exp 2018(e5070), 1–16 (2018). https://doi.org/10.1002/cpe.5070

Xingjun, L., Zhiwei, S., Hongping, C., Haghighi, M.R.J.: A new design of QCA-based nanoscale multiplexer and its usage in communications. Int. J. Commun Syst 33(4), 1–12 (2019). https://doi.org/10.1002/dac.4254

AlKaldy, E., Majeed, A.H., Zainal, M.S., Nor, D.B.M.: Optimum multiplexer design in quantum-dot cellular automata. Indones. J. Elect. Eng. Comput. Sci. 17(1), 148–155 (2020). https://doi.org/10.11591/ijeecs.v17.i1.pp148-155

Shah, N.A., Khanday, F.A., Bangi, Z.A., Iqbal, J.: Design of quantum-dot cellular automata (qca) based modular 1 to 2n demultiplexers. Int. J. Nanotechnol. Appl. 5(1), 47–58 (2011)

Iqbal, J., Khanday, F. A., Shah, N. A.: Design of quantum-dot cellular automata (qca) based modular 2n-1–2n mux-demux. In: Proceedings of IMPACT-2013, Aligarh, pp 189–193 (2013). https://doi.org/10.1109/MSPCT.2013.6782116.

Sardinha, L.H.B., Costa, A.M.M., Neto, O.P.V., Vieira, L.F.M., Vieira, M.A.M.: NanoRouter: a quantum-dot cellular automata design. IEEE J. Sel. Areas Commun. 31(12), 825–834 (2013). https://doi.org/10.1109/JSAC.2013.SUP2.12130015

Safoev, N., Jeon, J.: Low area complexity demultiplexer based on multilayer quantum-dot cellular automata. Int. J. Control Automat. 9(12), 165–178 (2016). https://doi.org/10.14257/ijca.2016.9.12.15

Das, J.C., De, D.: Circuit switching with quantum-dot cellular automata. Nano Commun. Netw. 149(December 2017), 16–28 (2017). https://doi.org/10.1016/j.nancom.2017.09.002

Khan, A., Arya, R.: Energy Dissipation and Cell Displacement Analysis of QCA Multiplexer for Nanocomputation. In: 2019 IEEE 1st International Conference on Energy, Systems and Information Processing (ICESIP), Chennai, India 2019, pp. 1–5 (2019). https://doi.org/10.1109/ICESIP46348.2019.8938359.

Srivastava, S., Asthana, A., Bhanja, S., Sarkar, S.: QCAPro—an error-power estimation tool for QCA circuit design. Proc. IEEE Int. Symp. Circ. Syst. (ISCAS) (2011). https://doi.org/10.1109/ISCAS.2011.5938081

QCADesigner-E: (2017). Accessed: March 12, 2019. [Online]. Available at: https://github.com/FSillT/QCADesigner-E.

Srivastava, S., Sarkar, S., Bhanja, S.: Estimation of upper bound of power dissipation in QCA circuits. IEEE Trans. Nanotechnol. 8(1), 116–127 (2009). https://doi.org/10.1109/TNANO.2008.2005408

Timler, J., Lent, C.S.: Power gain and dissipation in quantum-dot cellular automata. J. Appl. Phys. 91(2), 823–831 (2002). https://doi.org/10.1063/1.1421217

Bahar, A.N., Wahid, K.A.: Design of an efficient N × N butterfly switching network in quantum-dot cellular automata (qca). IEEE Trans. Nanotechnol. 19, 147–155 (2020). https://doi.org/10.1109/TNANO.2020.2969166

Walus, K., Dysart, T.J., Jullien, G.A., Budiman, R.A.: QCADesigner: a rapid design and simulation tool for quantum-dot cellular automata. IEEE Trans. Nanotechnol. 3(1), 26–31 (2004). https://doi.org/10.1109/TNANO.2003.820815

Torres, F.S., Wille, R., Niemann, P., Drechsler, R.: An energy-aware model for the logic synthesis of quantum-dot cellular automata. IEEE Trans. Comput. Aided Des. Integr. Circ. Syst. 37(12), 3031–3041 (2018). https://doi.org/10.1109/TCAD.2018.2789782

Torres, F. S., Niemann, P., Wille, R., Drechsler, R.: Breaking Landauer’s limit using quantum-dot cellular automata. Accessed online on January 12, 2019. https://arxiv.org/pdf/1811.03894.pdf.

Liu, W., Lu, L., O’Neill, M., Swartzlander, E.E.: A first step toward cost functions for quantum-dot cellular automata designs. IEEE Trans. Nanotechnol. 13(3), 476–487 (2014). https://doi.org/10.1109/TNANO.2014.2306754

Khosroshahy, M.B., Moaiyeri, M.H., Navi, K., Bagherzadeh, N.: An energy and cost efficient majority-based ram cell in quantum-dot cellular automata. Results Phys. 7, 3543–3551 (2017). https://doi.org/10.1016/j.rinp.2017.08.067

Author information

Authors and Affiliations

Corresponding authors

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Khan, A., Arya, R. Towards cost analysis and energy estimation of simple multiplexer and demultiplexer using quantum dot cellular automata. Int Nano Lett 12, 67–77 (2022). https://doi.org/10.1007/s40089-021-00352-y

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s40089-021-00352-y