Abstract

In this paper, two floating memcapacitor emulator circuits, one based on a second-generation current conveyor (CCII) and the other on an operational transconductance amplifier (OTA), are proposed. The first floating memcapacitor contains a single CCII, one multiplier, and four transistors, while the second one comprises a single OTA, one multiplier, and only two transistors. External transistors are operated as electronically controllable grounded capacitors and resistors. Therefore, the inverse memcapacitances of the circuits are adjusted electronically by applying appropriate bias voltages. Both emulator circuits can be operated to have incremental or decremental characteristics. The analyses of frequency response, electronic adjustability, temperature behavior, and non-volatile behavior of the circuits, as well as Monte Carlo analysis, are performed. Furthermore, an adaptive learning circuit is utilized to demonstrate the applicability of the proposed memcapacitor. Additionally, the CCII-based emulator circuit is constructed on a printed circuit board using discrete circuit elements and tested experimentally. The non-volatility feature of the circuit was tested for both incremental and decremental memcapacitors. The simulation and experimental results agree with the expected results.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

The relationship between charge (q) and flux (φ) of a memristor, a fourth fundamental circuit element, was defined by Chua [16]. However, the memristor did not attract researchers’ attention until 2008, when the HP research team announced the fabrication of a natural TiO2 memristor [47]. The realization of memristors marked the starting point for memristor-based studies. These studies can be categorized into three types: I. memristor emulator circuit design [3, 4, 6, 7, 14, 24, 29, 31, 33, 40, 41, 62], II. memristor-based circuit design [1, 5, 59, 63, 64, 67], and III. fabrication of the memristors [6, 18, 28, 42, 47]. However, apart from these studies, researchers are also interested in higher-order memelements such as meminductors [22, 27, 34, 44, 46, 58] and memcapacitors [8,9,10, 12, 13, 19,20,21, 23, 25, 26, 30, 35,36,37,38, 43, 45, 48, 50, 51, 53, 54, 56, 57, 61, 65, 66, 68]. Both the memcapacitor and meminductor elements exhibit nonlinear pinched hysteresis characteristics in their relationships between charge and voltage and flux and current, respectively.

Memcapacitor emulator design is a new research area because it is difficult to obtain memcapacitors on the market as a discrete circuit element. Research into the advantages of memcapacitor-based circuits is vital for circuit designers. Effectiveness, high accuracy, low energy consumption, electronic controllability, simple structure, and compatibility with VLSI designs are important parameters for designing memcapacitor emulator circuits. Active-circuit elements can fulfill these requirements and are suitable for designing memcapacitor emulators. Therefore, different types of active-circuit-element-based memcapacitor emulators have been reported in the literature [8,9,10, 12, 13, 19,20,21, 23, 25, 26, 30, 35,36,37,38, 43, 45, 48, 50, 51, 53, 54, 56, 57, 61, 65, 66, 68]. Konal et al. [25] designed a voltage differencing current conveyor (VDCC)-based memcapacitor emulator circuit with electronically controllable properties. The circuit operates in low-frequency ranges and is realized using discrete circuit elements. However, the application of the emulator is limited because the circuit has a grounded structure. Vista and Ranjan [50] designed a memcapacitor emulator based on a differential voltage current conveyor transconductance amplifier (DVCCTA). The circuit has a simple structure but is grounded. Yesil and Babacan [61] presented a second-generation current conveyor (CCII)- and operational transconductance amplifier (OTA)-based memcapacitor emulator circuit. The circuit is electronically controllable, implemented using discrete circuit elements, and demonstrates a strong memory effect and a charge–voltage relationship with pinched hysteresis. However, because the proposed structures are grounded, their applications are limited. The aforementioned CCII-based memcapacitor emulator circuit was implemented using two AD844s and one AD633. Hosbas et al. [21] designed a voltage differencing transconductance amplifier (VDTA)-based memcapacitor using a VDTA-based memristor emulator. The memcapacitor circuit is electronically controllable and exhibits a strongly pinched hysteresis loop. However, it has a grounded structure. Fouda and Radwan [19] proposed a grounded memristor-less memcapacitor emulator circuit that used four OPAMPs, a multiplier, and a single current-controlled current source. They provided the PSpice results for the circuit but noted that it has not yet been experimentally tested. Romero et al. [37] designed a memcapacitor emulator circuit based on the Miller effect. The designed circuit was tested in both a simulation program and a field-programmable analog array (FPAA) and comprised an OPAMP, buffer, capacitor, and memristor owing to its mutator structure. A memcapacitor emulator circuit using one VDTA element and two grounded capacitors was designed by Petrović [35]. The circuit was experimentally tested in a simulated environment using off-the-shelf components. Owing to the VDTA element, the circuit is electronically adjustable but grounded. Vista and Ranjan [51] proposed a circuit that can emulate the behavior of a floating memcapacitor. The circuit is electronically adjustable both incrementally and decrementally. Although the circuit was implemented using an adaptive learning circuit, experimental results were not provided. Singh and Rai presented a VDCC-based floating structure memcapacitor emulator circuit [45]. The circuit contains only one VDCC, one capacitor, and one memristor owing to its mutator structure. However, only the simulation results of the circuit are available. Sah et al. [38] designed a floating memcapacitor emulator using off-shelf devices. Two OPAMPs and a multiplier circuit were used. The experimental results were obtained by building a circuit on a breadboard; however, the circuit did not have an electronically adjustable structure. Wang et al. proposed a memcapacitor emulator circuit using a mutator structure [54]. The circuit was designed using five OPAMPs, an LDR, LED, a diode, 12 resistors, and two capacitors. A large number of active and passive elements were used in the circuit, and the circuit was not electronically adjustable. Sharma et al. [43] proposed an emulator circuit that can function as both a memristor and memcapacitor using two CCIIs and a multiplier circuit. The study presents the experimental results, and the circuit can be operated as both grounded and floating circuits. Although this circuit can operate both incrementally and decrementally, it does not exhibit electronically adjustable properties. Bhardwaj et al. [9] presented a universal memelements emulator with one each of a CCII, OTA, a resistor, and two capacitances. Although the simple and universal structure of the circuit is a crucial advantage, experimental studies on this circuit have not yet been conducted. Bhardwaj and Srivastava [10] designed a grounded multiplier-less charge-controlled memelements emulator consisting of one VDCC, one OTA, two capacitors, and a resistor. Although the circuit is electronically adjustable, the fixed and variable components cannot be adjusted independently.

A floating emulator circuit [66] was designed to obtain a memristor, memcapacitor, and meminductor. The circuit for the memcapacitor consists of four AD844s, one OPAMP, one varactor diode, six resistors, and two capacitors. Zheng et al. [68] presented a universal interface that could be used as a memristor, memcapacitor, or meminductor. In the universal structure, four AD844s, a varactor diode, two capacitors, and two resistors are employed to form a memcapacitor emulator circuit. As a universal structure was presented in these studies [66, 68], a large number of elements were used in the circuits. Wang et al. designed a floating memcapacitor emulator circuit [53] using a real memristor. The circuit contained three AD844s, three passive elements, and a memristor produced by Knowm. Simulations and experiments were conducted using the designed circuit. Yu et al. designed a floating memcapacitor emulator circuit with a mutator structure [63]. The circuit consisted of four AD844s, two OPAMPs, a multiplier circuit, and 10 passive elements. Although the simulation and experimental results of the circuit have been presented, the number of elements used in the circuit is high, and the circuit has no electronic tunability. In the floating memcapacitor emulator designed by Biolek et al. [12], one AD8421, two LM311s, one MAX4523, one Op27, four capacitors, five resistors, and one potentiometer were used. Both simulation and experimental studies have been conducted on circuits that require numerous components. Gur et al. [20] designed a simple MO-OTA-based memcapacitor emulator circuit. Although the circuit is fully floating and electronically controllable, the number of elements is large because it contains two MO-OTAs, four transistors, a capacitor, and a resistor. Additionally, only the simulation results were included in this study, and no experimental studies were conducted. In a study by Tatović and Petrović [48], a floating memcapacitor emulator circuit was proposed using one VDCC, two MOSFETs, and two capacitors. The proposed circuit was electronically tunable; however, it was only tested in a simulation environment. However, no experimental studies have been conducted on these circuits.

In summary, the circuits designed in many studies [8,9,10, 19, 21, 25, 26, 35,36,37, 50, 54, 61] are grounded; therefore, their application areas are relatively limited compared to those for floating structures. However, some studies on floating memcapacitor emulators [12, 13, 20, 23, 38, 45, 48, 51, 53, 56, 57, 65, 66, 68] have not provided experimental results [13, 20, 23, 45, 48, 51], whereas in other studies, the circuits lack electronic adjustability features [12, 38, 53, 65, 66, 68]. Memcapacitor emulators, both grounded and floating, have also been designed [30, 43]; however, their active and passive element counts are high.

In this study, two floating memcapacitor emulator circuits, one CCII-based and the other OTA-based, are proposed. The CCII-based memcapacitor circuit comprises only one CCII, a single analog multiplier, and four MOSFETs. The OTA-based memcapacitor circuit contains a single OTA, single analog multiplier, and two MOSFETs. Using MOSFETs and the transconductance gain of the OTA, the memcapacitance of the proposed circuits can be electronically adjusted both incrementally and decrementally. Both the proposed circuits were simulated using the LTspice program. Furthermore, an adaptive learning circuit was implemented to demonstrate the applicability of the proposed memcapacitor. A CCII-based emulator circuit was developed on a PCB using an AD844 multiplier, resistor, and two capacitors and tested. The results obtained from the experimental and simulation studies are compatible with each other and with the mathematical equations.

2 Proposed CCII-Based Memcapacitor Emulator Circuit

Memcapacitors are defined using the relationship between the charge integral (σ) and flux (φ). This relationship is expressed in Eq. (1).

The voltage-controlled and charge-controlled memcapacitor elements are defined in Eqs. (2) and (3) [49]. The emulator circuits proposed in this study are controlled by charge.

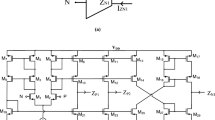

The CCII-based memcapacitor emulator circuit contains one CCII, one multiplier, and four MOSFETs, as shown in Fig. 1. The transistors have the capability to function as capacitors [2, 15, 17]. In this circuit, the MC1 and MC2 MOSFETs are used as grounded and electronically adjustable capacitors. The MR1 and MR2 transistors are used as grounded and electronically adjustable resistors that formed the equivalent resistance Req [55], defined in Eq. (4).

The current–voltage relationships between the terminals of the CCII element are shown in Eq. (5). In the equation, α and β represent the current and voltage gains of a CCII element, respectively. In an ideal CCII element, the values of α and β are equal to one and are independent of frequency.

As shown in Fig. 1, an input voltage is applied to terminals A and B of the proposed circuit. The input current that flows through terminal A is related to the charge on capacitor C1, as expressed in Eq. (6). This is because the current flows completely through capacitor C1, and no current flows from terminal Y. The voltage at terminal X is β times the voltage at terminal Y, as shown in Eq. (5). The current flowing through terminal X is expressed as \(I_{X} (t) = {{V_{x} (t)} \mathord{\left/ {\vphantom {{V_{x} (t)} {R_{{{\text{eq}}}} }}} \right. \kern-0pt} {R_{{{\text{eq}}}} }}\). Since the current flowing through terminal X is α times the current flowing from terminal Z, Eqs. (7) and (8) are obtained.

If the equation for the voltage at the output terminal of the multiplier is positive, the expression for VMUL(t) is as shown in Eq. (9). A floating structure is obtained when the output terminal of the multiplier is connected to terminal B of the input voltage. The relationship between the input voltages at terminals A and B is given by Eqs. (9) and (10): The expression γ refers to the constant coefficient of the multiplier element.

When the expression in Eq. (10) is rearranged, the inverse memcapacitance in the incremental structure is derived, as shown in Eq. (11). However, when the output of the multiplier is negative, Eq. (12) yields an inverse memcapacitance in the decremental structure.

The main reason for using MOSFETs instead of resistors and capacitors in the circuit design is that their resistance and capacitance cannot be altered electronically. By contrast, MOSFET-based designs offer the opportunity to adjust these values electronically. As indicated by Eqs. (10) and (11), the fixed and variable parts of the inverse memcapacitor equations can be modified separately. Since the values of the passive elements can be changed electronically, the fixed part with C1 and the variable part with Req and C2 can be adjusted independently. Capacitances C1 and C2 can be changed by adjusting the bulk voltages of transistors MC1 and MC2, which function as MOS capacitors [2, 15, 17]. Similarly, voltage VC can be adjusted to alter the equivalent electronic resistance Req of transistors MR1 and MR2 [55].

An additional benefit of designing a circuit using MOSFETs rather than directly using passive elements is the ability to build the circuit directly within the integrated circuit, as the proposed circuit has no external components such as resistors and capacitors.

3 Proposed OTA-Based Memcapacitor Emulator Circuit

The proposed OTA-based floating memcapacitor emulator circuit is shown in Fig. 2. The circuit consists of one OTA, one multiplier, and two MOSFETs. As mentioned in the previous section, MOSFETs MC1 and MC2 function as the grounded MOS capacitors C1 and C2, respectively.

The terminal relationships of OTA can be represented as \(I_{{\text{z}}} \left( t \right) = g_{{\text{m}}} \left( {V_{{\text{P}}} \left( t \right) - V_{{\text{N}}} \left( t \right)} \right)\) and \(I_{{\text{P}}} (t) = I_{{\text{N}}} (t) = 0\). The gm value of the OTA element is denoted as \(g_{{\text{m}}} = K(V_{{{\text{REF}}}} - V_{{{\text{SS}}}} - V_{{{\text{TH}}}} )\), and the expression for K in this equation is represented as \(K = B\mu_{{\text{n}}} C_{{{\text{ox}}}} \sqrt {{\raise0.7ex\hbox{$1$} \!\mathord{\left/ {\vphantom {1 2}}\right.\kern-0pt} \!\lower0.7ex\hbox{$2$}}\left( {{\raise0.7ex\hbox{$W$} \!\mathord{\left/ {\vphantom {W L}}\right.\kern-0pt} \!\lower0.7ex\hbox{$L$}}} \right)_{{{\text{M}}_{1} }} \left( {{\raise0.7ex\hbox{$W$} \!\mathord{\left/ {\vphantom {W L}}\right.\kern-0pt} \!\lower0.7ex\hbox{$L$}}} \right)_{{{\text{M}}_{9} }} }\)[60]. The parameters \(\mu_{{\text{n}}}\), \(C_{{{\text{ox}}}}\), and \(V_{{{\text{TH}}}}\) represent carrier mobility, gate oxide capacitance per unit area, and threshold voltage, respectively. B is defined as the gain of the current mirror between transistors \(M_{5,3}\) and \(M_{6,4}\), and according to this OTA structure, the value of B is 2. As shown in Fig. 2, an input voltage is applied between terminals A and B in the emulator circuit. As no current flows from terminal N, the input current flows through capacitor C1, yielding the charge expression in Eq. (13). The current flowing from terminal Z can be described as \(I_{{\text{z}}} (t) = - g_{{\text{m}}} V_{{\text{N}}} (t)\) because terminal P is connected to ground. Current Iz(t) flowing through capacitor C2 is given by Eq. (14).

When the multiplier circuit is used as a positive multiplier, voltage VB(t) is obtained, as shown in Eq. (15). Equation (16) is obtained when an input voltage is applied between terminals A and B. In the equations, γ represents the constant coefficient of the multiplier element.

When Eq. (16) is rearranged, the inverse memcapacitance expression of the decremental structure is obtained as shown in Eq. (17). If the input voltage is applied to the P terminal instead of the N terminal of the OTA element or the output of the multiplier is set to be negative, the inverse memcapacitance is obtained incrementally, as in Eq. (18).

In the proposed emulator circuit, capacitors C1 and C2 are formed by MOSFETs MC1 and MC2. This design allows the capacitance values to be adjusted by changing the bulk voltage of the MOSFETs. The value of gm can be adjusted by changing the bias voltage VREF of the OTA element in the circuit. These properties provide the circuit with an electronically adjustable structure.

4 Simulation Results

Two proposed floating memcapacitor circuits are simulated using the Taiwan Semiconductor Manufacturing Company (TSMC) 0.18-µm process model parameters in the LTspice program. In simulation studies, the circuit's responses at various frequencies, electronic tunability, behavior at different temperatures, and memory effects were examined, and Monte Carlo analysis was also performed.

4.1 Simulation Results for the CCII-Based Floating Memcapacitor Emulator Circuit

The internal structure of the CCII element used in the CCII-based memcapacitor emulator circuit is illustrated in Fig. 3. The CCII element is designed using the LTspice program and TSMC 0.18-µm process model parameters. The dimensions of the MOSFET elements in the CCII are listed in Table 1. The supply voltages of the CCII element are set to VDD = − VSS = 0.9 V, and its bias voltage is fixed at 350 mV. In the CCII element, the bulk terminals of the p-type MOSFETs are connected to the source, whereas the bulk terminals of the n-type MOSFETs are connected to a minimum voltage of − 0.9 V. The dimensions of the MOS capacitor elements in the circuit are chosen using \({W \mathord{\left/ {\vphantom {W L}} \right. \kern-0pt} L} = {{100{\mu m}} \mathord{\left/ {\vphantom {{100{\mu m}} {4{\mu m}}}} \right. \kern-0pt} {4{\mu m}}}\), and those of the transistors in the electronic resistor structure are selected as \({W \mathord{\left/ {\vphantom {W L}} \right. \kern-0pt} L} = {{60{\mu m}} \mathord{\left/ {\vphantom {{60{\mu m}} {2{\mu m}}}} \right. \kern-0pt} {2{\mu m}}}\).

In all the simulation studies conducted on the CCII-based circuit, unless specified otherwise, the input signal is selected as a sinusoidal wave at 5 MHz and 60 mV. Since the voltage of the electronic resistor VC is set to 460 mV, the equivalent resistance in the circuit is maintained at 6 kΩ. The bulk voltages of the capacitors in the circuit are fixed at 0 V, and their capacitance values vary between 1 and 1.3 pF.

The CCII-based emulator circuit can operate incrementally and decrementally, as described in Eqs. (11) and (12), respectively. These operational modes are determined by setting the multiplier element to either a positive or a negative output. When the multiplier is set to positive, the emulator circuit operates in the incremental mode, as shown in Fig. 4a. Conversely, when the multiplier element is set to negative, the emulator circuit operates in decremental mode, as shown in Fig. 4b. In all simulation studies conducted on CCII-based circuits, with the exception of the non-volatility behavior test, the multiplier element is chosen as positive, and the simulation outcomes are achieved using the incremental structure.

The hysteresis loops depicted in Fig. 5 are obtained by varying the input voltage frequency between 4, 5, and 30 MHz. As the operating frequency increases, the hysteresis loops become more linear. To demonstrate the electronic tunability of the proposed emulator circuit, the values of Req and C2 are varied electronically. The voltage VC of the electronic resistor is set to three different values: 440 mV (corresponding to Req = 8.1 kΩ), 460 mV (Req = 6 kΩ), and 480 mV (Req = 4.6 kΩ). The resistance decreased with an increase in VC. This decrease in resistance increased the variable part of the memcapacitance, as described by Eq. (11). The changes in the variable part are illustrated by the hysteresis curves shown in Fig. 6.

The capacitance of MOS capacitors is affected by both the bulk voltage (VBulk) and the gate-source voltage (VGS). The relationship between capacitance and VGS varies based on the bulk voltage, as shown in Fig. 7a. When the CCII-based emulator circuit is operated at a frequency of 5 MHz and the bulk voltage of the MOS capacitor is set to 0 V, VGS on the MOS capacitors varies from − 223 to 360 mV. Correspondingly, as illustrated in Fig. 7a, the capacitance varies between 1 and 1.3 pF. The capacitance graph obtained by maintaining a constant VGS voltage at an average value of 70 mV and varying the bulk voltage between 0 and 900 mV is shown in Fig. 7b. As the bulk voltage of the MOS capacitor increases, there is a corresponding decrease in the capacitance of capacitor C2. This decrease leads to an increase in the variable part of the memcapacitor in accordance with Eq. (11). The effect of these changes on the emulator circuit is demonstrated by the hysteresis loops shown in Fig. 7c.

The temperature stability of the circuit is examined by applying an input voltage of 60 mV at a frequency of 5 MHz. Results at temperatures of − 25 °C, 27 °C, and 80 °C are presented in Fig. 8. An examination of the results shown in Fig. 8 indicates that although the amplitude of the hysteresis loop varies with temperature, the overall characteristic structure of the circuit remains relatively stable. In the Monte Carlo analysis, 100 iterations were conducted on the width (W) and length (L) values (with 5% tolerance) of the MOSFETs, which acted as capacitors and electronic resistors in the circuit. The resulting hysteresis loops depicted in Fig. 9 demonstrate that even with a 5% tolerance for the specified parameters, the circuit continues to exhibit its fundamental characteristics.

To assess the non-volatile behavior of the proposed circuit, positive pulses with an amplitude of 60 mV and width of 10 ns are applied at intervals of 10 ns. Figure 10a and b shows the voltage and charge graphs of the increasing and decreasing structures, respectively. Although the amplitude of the applied voltage remains constant, a change in charge can be observed. Based on the equation C = q/V, a change in charge with a constant voltage suggests a directly proportional change in the capacitance. The charge measurement in the circuit is determined by the voltage across capacitor C1, as indicated in Eq. (6). When the voltage applied to the circuit is reduced to zero, the voltage across the C1 capacitor also appears to be zero, resulting in the charge being immeasurable and displaying zero. However, upon reapplying the voltage, the charge continues from where it left off, in accordance with the increasing–decreasing structure. This behavior demonstrated the non-volatile nature of the circuit.

4.2 Simulation Results for OTA-Based Floating Memcapacitor Emulator Circuit

The internal structures of the OTA elements are shown in Fig. 11. The OTA element is designed using MOSFETs, according to the TSMC 0.18-µm process parameters, with the MOSFET dimensions listed in Table 2. The lengths of the transistors are chosen to be large enough to increase the parasitic resistance at the Z terminal of the OTA \(({r}_{{\text{o}}6}//{r}_{o8})\). Notably, the output resistance of MOSFET is proportional to the length of MOSFET; accordingly, as the lengths of the transistors increase, the voltage on the capacitance is minimally affected by the parasitic resistance at the Z terminal. In the simulation, the output resistance is measured as 767 kΩ.

The supply voltages of the OTA element are set to VDD = − VSS = 0.9 V. In the OTA structure, the bulk terminals of the p-type MOSFETs are connected to the source, while the bulk terminals of the n-type MOSFETs are connected to a minimum voltage of − 0.9 V. The dimensions of the transistors that comprise the MOS capacitors in the circuit are chosen as \({W \mathord{\left/ {\vphantom {W L}} \right. \kern-0pt} L} = {{100{\mu m}} \mathord{\left/ {\vphantom {{100{\mu m}} {4{\mu m}}}} \right. \kern-0pt} {4{\mu m}}}\).

In all analyses of the OTA-based circuit, unless otherwise specified, the input signal is set to a 60-mV, 4-MHz sinusoidal signal. The VREF voltage is maintained at − 200 mV, and the gm value of the circuit is fixed at 39.73 µA/V. In addition, the voltage at the bulk terminals of the MOS capacitors within the circuit is 0 V.

By setting the multiplier element in the circuit shown in Fig. 2 to positive and negative values, the circuit can be transformed into a decremental or incremental structure. In these studies, because the multiplier element is chosen to be positive, a decreasing structure is used for the simulations.

The voltage–charge graph of the OTA-based decremental circuit is depicted in Fig. 12a, while the graph for the incremental circuit is shown in Fig. 12b. To examine the response of the circuit at various frequencies, the input signal frequency is set to 2, 4, and 30 MHz, respectively. The hysteresis loops that result from these frequency adjustments are shown in Fig. 13. As the frequency increases, the hysteresis loops exhibit a more linear behavior.

The proposed emulator circuit can be electronically adjusted by changing the gm value of the OTA element and the capacitance value of the MOS capacitor C2. To change the gm value of the OTA element, the voltage VREF can be adjusted to − 400 mV (gm = 5 µA/V), − 200 mV (gm = 39.73 µA/V), or 0 V (gm = 85.83 µA/V). As shown in Eqs. (16) and (17), there is a direct correlation in which the gm value of the OTA element increases with VREF. This relationship is visually represented in Fig. 14, which shows that an increase in gm corresponds to an increase in the variable part of the memcapacitance.

The relationship between the bulk voltage and capacitance of the MOS capacitor C2 is shown in Fig. 7a. The MOS capacitors utilized in both the CCII- and OTA-based emulator circuits are identical in size. The hysteresis loops corresponding to the bulk voltages of 0, 450, and 900 mV are shown in Fig. 15. As the bulk voltage increases, a decrease in the capacitance of C2 is observed, increasing the fixed part of the memcapacitance. In operational conditions where the circuit is set to a frequency of 4 MHz and the bulk voltage of the MOS capacitor is maintained at 0 V, the voltage VGS on the MOS capacitors fluctuates between − 444 and 121 mV. This results in a capacitance range of 1.13–2.76 pF. To investigate the temperature stability of the circuit, temperatures of − 25 °C, 27 °C, and 80 °C are selected in the LTspice program, and the results are shown in Fig. 16.

For the Monte Carlo analysis, the tolerance values for the width (W) and length (L) of the MOS capacitors used in the circuit are set to 5%. The analysis results for 100 hysteresis loops, presented in Fig. 17, indicate that there is minimal change in the behavior of the circuit at the 5% tolerance level.

To evaluate the non-volatile behavior of the circuit, positive pulses with an amplitude of 60 mV and a width of 20 ns were applied at intervals of 20 ns. When the signal is applied to the decremental structure of the memcapacitor circuit, a progressive decrease occurs in the charge for each pulse, as illustrated in Fig. 18a. Conversely, when the signal is applied to the incremental structure, the charge increases incrementally with each pulse, as shown in Fig. 18b. The circuit retains its last charge value and resumes operation from the point of interruption between two consecutive positive pulses.

5 Emulating Amoeba Behavior with Adaptive Learning Using Memcapacitor Emulator Circuits

Saigusa et al. [39] demonstrated that amoeba-like cells possess the ability to learn and modify their behavior in anticipation of upcoming stimuli. Serial RLC circuits with memory elements were used in previous studies [10, 11, 32, 51, 52] to electrically simulate this behavior. To demonstrate the effectiveness of the memcapacitor emulator circuits proposed in this study, a series RLC circuit is established, and the adaptive learning behavior of the amoeba is modeled by connecting the proposed memcapacitor emulator instead of the capacitor. In Fig. 19, the adaptive learning behavior of an amoeba is modeled to demonstrate the effectiveness of both the CCII-based and OTA-based memcapacitor emulator circuits.

Both circuits are tested using the same procedure. The resistance value in the circuit is 1 kΩ, and the inductance value is 1 µH. Input signals with − 100 mV amplitude and duration of 40 ns are applied to the circuits.

For the CCII-based circuit, Fig. 20a shows that for a delay of 320 ns between the first and the second input signals, the corresponding output signals are − 141 mV and − 146 mV, respectively. In another scenario shown in Fig. 20b, when three signals are applied at intervals of 20 ns, the output signal initially increases up to − 187 mV for the first three signals. Thereafter, when an input signal is applied again after a delay of 320 ns, the output voltage is measured as − 165 mV.

In the OTA-based circuit, two signals are initially applied with an interval of 320 ns between them, as illustrated in Fig. 21a, similar to the approach used in the CCII-based circuit. When the first signal is applied, it can be observed that the output signal of the circuit is − 94 mV and the second output signal is − 117 mV. In the second simulation, as illustrated in Fig. 21b, three signals are initially applied to gauge the system response, followed by an additional signal after a delay of 320 ns. When three signals are applied in the simulation, it is observed that the output of the third signal reaches − 230 mV. Subsequently, after a 320 ns delay and damping of the entire system, another signal was applied. Upon measuring at this stage, the output signal is found to be − 208 mV.

In simulation studies performed by waiting for 320 ns after a single signal, it is observed that the circuit cannot fully learn the stimulus and tends to forget it. In contrast, in the second experiment, in which three signals are first applied and the signal is reapplied after waiting for 320 ns, it is revealed that the circuit learns the stimulus following the first three stimuli. Consequently, a more pronounced reaction can be observed than in the first experiment when the same signal is reapplied after the same delay.

6 Experimental Results

In the proposed circuit, MOSFETs are employed instead of passive elements, and simulation studies are conducted to analyze the performance of the circuit without using passive elements. To conduct experimental tests on this circuit, it must be produced as an integrated circuit. Owing to the unavailability of integrated circuit production equipment, experimental studies have been conducted using discrete elements on PCB. Although MOS capacitor structures are suitable for integrated circuits, the desired values cannot be obtained on a PCB. Therefore, ceramic capacitors are employed instead of MOS capacitors in these experiments. However, using discrete components on the PCB instead of integrated circuits not only limits the frequency of the circuit to the limits of elements, such as AD633 and AD844, but also requires operating the circuit at lower frequencies to mitigate parasitic effects. This frequency reduction necessitates the use of capacitors larger than those used in the simulations, resulting in the selection of larger capacitor sizes for experimental studies.

The proposed circuit is composed of one AD844, one AD633, a 10 kΩ resistor, and two 470 pF capacitors. As shown in Eqs. (11) and (12), the inverse capacitance is defined in terms of the input voltage and charge. While the input voltage is measured directly as floating, the charge is obtained by multiplying the voltage at the Y terminal by the capacitance C1, as shown in Eq. (6). Figure 22a displays the macromodel used in this experimental study. Figure 22b and c presents the structure of this macromodel on the PCB and the results obtained during circuit operation, respectively.

The circuit operates with a supply voltage of ± 12 V, and a sinusoidal input signal with an amplitude of 100 mV and a frequency of 700 Hz is applied. Based on (11) and (12), the circuit can be configured to exhibit increasing and decreasing behaviors, respectively. When the multiplier element in the circuit is set to a positive value, it results in an incremental structure, as shown in Fig. 23a. Conversely, setting the multiplier element to a negative value leads to a decremental structure, as illustrated in Fig. 23b. The blue and yellow lines on the oscilloscope display correspond to the applied voltage and charge, respectively. To evaluate the frequency response of the circuit, the operating frequencies are set to 500 Hz, 700 Hz, 1 kHz, and 4 kHz, and the resulting hysteresis loops are shown in Fig. 24. An analysis of the results reveals that, as expected, the hysteresis loops of the circuit tend to become more linear as the frequency increases. Despite the variations in frequency, the hysteresis curve largely retains its symmetrical structure. In addition, the slight shift in the origin of the curve observed at lower frequencies diminishes as the frequency increases, resulting in the midpoint of the hysteresis loop approaching the origin.

To analyze the impact of the passive components within the circuit, the values of the resistor Req and the capacitor C2 are adjusted. Req is set to three different values: 6.8 kΩ, 10 kΩ, and 15 kΩ. The oscilloscope images shown in Fig. 25 display the results of these modifications. The capacitance of C2 capacitor was set to 330, 470, and 680 pF, respectively. Oscilloscope images that capture the results of these variations are presented in Fig. 26. As demonstrated in Eq. (11), an increase in the values of Req and C2 decreases the fixed part of the memcapacitor.

The experimental results indicate that an increase in the values of Req and C2 decreases the fixed part of the circuit, resulting in a more linear hysteresis.

To examine the non-volatile behavior, a 2 kHz square signal with an amplitude of 100 mV is applied to the emulator circuit. In the oscilloscope screenshot depicted in Fig. 27, the measured input voltage is displayed in blue. As the memcapacitor expression cannot be directly shown, the charge is derived by measuring the voltage across capacitor C1, in accordance with Eq. 6. Since the capacitance of C1 is constant, dividing the voltage by the capacitance of C1 according to the q = CV formula allows the charge shown in yellow on the oscilloscope screenshot to be displayed. Figure 27a and b shows the non-volatile behavior of the circuit in the incremental and decremental structures, respectively. The results reveal that as the direction of the input voltage changes, the charge expression resumes from its previous position and displays symmetry about the x-axis.

7 Conclusion

In this study, two electronically controllable floating memcapacitor emulator circuits based on CCII and OTA are presented. The first proposed circuit contains a single CCII, analog multiplier, and four MOSFETs, while the second comprises a single OTA, analog multiplier, and two MOSFETs. In the first proposed circuit, two MOSFETs (MR1 and MR2) work as electronically tunable grounded resistors, whereas two MOSFETs (MC1 and MC2) act as electronically tunable grounded capacitors. For the second proposed circuit, two MOSFETs (MC1 and MC2) act similarly as electronically tunable grounded capacitors, while the transconductance gain of the OTA can be tuned by the bias voltage (VREF). Therefore, the inverse memcapacitance of both proposed circuits can be controlled electronically. Simulation results are presented considering different performance parameters to examine the performance of both circuits. Furthermore, temperature and Monte Carlo analyses were performed in simulation studies of both circuits. The non-volatile behavior of the circuits was analyzed in both the incremental and decremental structures, and the memory effect of the circuit was demonstrated. Considering their memory properties, memelements have significant potential for applications in neuromorphic circuits and biological system mimics. As an example of the application of the proposed memcapacitor circuits, an RLC circuit was established to mimic an amoeba-like cell, utilizing a memcapacitor instead of a conventional capacitor to exploit its adaptive capabilities. In addition to the simulation studies, experimental studies were conducted by implementing a CCII-based circuit on a PCB. As the circuit was constructed on a PCB rather than on an integrated circuit, it is designed using passive circuit elements instead of MOSFETs. Frequency analyses of this circuit were performed, and the effects of changing the passive circuit elements on the circuit were demonstrated. In conclusion, the simulation, experimental, and application results agree well with those of previous studies.

Data availability

Data sharing is not applicable to this article, as no datasets were generated or analyzed during the current study.

References

M.T. Abuelma’atti, Z.J. Khalifa, A new memristor emulator and its application in digital modulation. Analog Integr. Circuits Signal Process. 80(3), 577–584 (2014). https://doi.org/10.1007/s10470-014-0364-3

P.E. Allen, D.R. Holberg, CMOS Analog Circuit Design (Oxford Press, Oxford, 2016)

U.E. Ayten, S. Minaei, M. Sağbaş, Memristor emulator circuits using single CBTA. AEU-Int. J. Electron. C. 82, 109–118 (2017). https://doi.org/10.1016/j.aeue.2017.08.008

Y. Babacan, F. Kaçar, Floating memristor emulator with subthreshold region. Analog Integr. Circuits Signal Process. 90(2), 471–475 (2017). https://doi.org/10.1007/s10470-016-0888-9

Y. Babacan, F. Kaçar, K. Gürkan, A spiking and bursting neuron circuit based on memristor. Neurocomputing 203, 86–91 (2016). https://doi.org/10.1016/j.neucom.2016.03.060

Y. Babacan, A. Yesil, F. Gul, The fabrication and MOSFET-only circuit implementation of semiconductor memristor. IEEE Trans. Electron Devices 65(4), 1625–1632 (2018). https://doi.org/10.1109/ted.2018.2808530

Y. Babacan, A. Yesil, F. Kacar, Memristor emulator with tunable characteristic and its experimental results. AEU-Int. J. Electron. C. 81, 99–104 (2017). https://doi.org/10.1016/j.aeue.2017.07.012

K. Bhardwaj, A. Kumar, M. Srivastava, Universal memelement emulator using only off-the-shelf components. Analog Integr. Circuits Signal Process. 114(2), 175–193 (2023). https://doi.org/10.1007/s10470-022-02075-2

K. Bhardwaj, M. Srivastava, On the boundaries of the realization of single input single element-controlled universal memelement emulator. Circuits Syst. Signal Process. 42(10), 6355–6366 (2023). https://doi.org/10.1007/s00034-023-02420-4

K. Bhardwaj, M. Srivastava, New multiplier-less compact tunable charge-controlled memelement emulator using grounded passive elements. Circuits Syst. Signal Process. 41(5), 2429–2465 (2022). https://doi.org/10.1007/s00034-021-01895-3

K. Bhardwaj, M. Srivastava, Compact floating dual memelement emulator employing VDIBA and OTA: a novel realization. Circuits Syst. Signal Process. 41(11), 5933–5967 (2022). https://doi.org/10.1007/s00034-022-02067-7

D. Biolek, V. Biolková, Z. Kolka, J. Dobeš, Analog emulator of genuinely floating memcapacitor with piecewise-linear constitutive relation. Circuits Syst. Signal Process. 35(1), 43–62 (2016). https://doi.org/10.1007/s00034-015-0067-8

Z.G. Çam Taşkıran, M. Sağbaş, U.E. Ayten, H. Sedef, A new universal mutator circuit for memcapacitor and meminductor elements. AEU Int. J. Electron. Commun. (2020). https://doi.org/10.1016/j.aeue.2020.153180

Z.G. Cam, H. Sedef, A new floating memristance simulator circuit based on second generation current conveyor. J. Circuits Syst. Comput. 26(02), 1750029 (2017). https://doi.org/10.1142/s0218126617500293

S. Chatterjee, T. Musah, Y. Tsividis, P. Kinget, Weak inversion MOS varactors for 0.5 V analog integrated filters. in Digest of Technical Papers. 2005 Symposium on VLSI Circuits, 2005. (IEEE, n.d.), pp. 272–275

L. Chua, Memristor-The missing circuit element. IEEE Trans. Circuit Theory 18(5), 507–519 (1971). https://doi.org/10.1109/tct.1971.1083337

E. Demir, A. Yesil, Y. Babacan, T. Karacali, Operational transconductance amplifier-based electronically controllable memcapacitor and meminductor emulators. J. Circuits Syst. Comput. (2021). https://doi.org/10.1142/s0218126621502224

H. Efeoglu, S. Güllülü, T. Karacali, Resistive switching of reactive sputtered TiO2 based memristor in crossbar geometry. Appl. Surf. Sci. 350, 10–13 (2015). https://doi.org/10.1016/j.apsusc.2015.03.088

M.E. Fouda, A.G. Radwan, Charge controlled memristor-less memcapacitor emulator. Electron. Lett. 48(23), 1454 (2012). https://doi.org/10.1049/el.2012.3151

M. Gur, F. Akar, K. Orman, Y. Babacan, A. Yesil, F. Gul, Electronically controllable fully floating memcapacitor circuit. Circuits Syst. Signal Process. 42(11), 6481–6493 (2023). https://doi.org/10.1007/s00034-023-02448-6

M.Z. Hosbas, F. Kaçar, A. Yesil, Memcapacitor emulator using VDTA-memristor. Analog Integr. Circuits Signal Process. 110(2), 361–370 (2022). https://doi.org/10.1007/s10470-021-01974-0

V. Indhrani, A.K. Srinivasan, P.K. Vaishali, RETRACTED ARTICLE: floating and grounded meminductor using VDTA and neuromorphic circuit based on amoeba behaviour. Trans. Electr. Electron. Mater. 23(4), 414–418 (2022). https://doi.org/10.1007/s42341-021-00362-9

A.H. Kaya, A. Yesil, Y. Babacan, A floating CCCII and DDCC based memcapacitor circuit with electronically controllable behavior. Erzincan Üniversitesi Fen Bilimleri Enstitüsü Dergisi 15(1), 93–105 (2022). https://doi.org/10.18185/erzifbed.989494

H. Kim, M.P. Sah, C. Yang, S. Cho, L.O. Chua, Memristor emulator for memristor circuit applications. IEEE Trans. Circuits Syst. I Regul. Pap. 59(10), 2422–2431 (2012). https://doi.org/10.1109/tcsi.2012.2188957

M. Konal, F. Kacar, Y. Babacan, Electronically controllable memcapacitor emulator employing VDCCs. AEU-Int. J. Electron. C. 140, 153932 (2021). https://doi.org/10.1016/j.aeue.2021.153932

M.O. Korkmaz, A. Yesil, FDCCII based new memcapacitor emulator circuit with electronically tunable. Mühendislik Bilimleri ve Araştırmaları Dergisi 5(1), 127–134 (2023). https://doi.org/10.46387/bjesr.1259980

K. Kumar, B.C. Nagar, New tunable resistorless grounded meminductor emulator. J. Comput. Electron. 20(3), 1452–1460 (2021). https://doi.org/10.1007/s10825-021-01697-5

M. Laurenti, S. Porro, C.F. Pirri, C. Ricciardi, A. Chiolerio, Zinc oxide thin films for memristive devices: a review. Crit. Rev. Solid State Mater. Sci. 42(2), 153–172 (2017). https://doi.org/10.1080/10408436.2016.1192988

Q. Li, A. Serb, T. Prodromakis, H. Xu, A memristor SPICE model accounting for synaptic activity dependence. PLoS ONE 10(3), e0120506 (2015). https://doi.org/10.1371/journal.pone.0120506

Y. Liu, H.H.C. Iu, Z. Guo, G. Si, The simple charge-controlled grounded/floating mem-element emulator. IEEE Trans. Circuits Syst. II Express Briefs 68(6), 2177–2181 (2021). https://doi.org/10.1109/tcsii.2020.3041862

S. Minaei, I.C. Göknar, M. Yıldız, E. Yuce, Memstor, memstance simulations via a versatile 4-port built with new adder and subtractor circuits. Int. J. Electron. 102(6), 911–931 (2015). https://doi.org/10.1080/00207217.2014.942890

Y.V. Pershin, S. La Fontaine, M. Di Ventra, Memristive model of amoeba learning. Phys. Rev. E 80(2), 021926 (2009). https://doi.org/10.1103/physreve.80.021926

P.B. Petrović, Floating incremental/decremental flux-controlled memristor emulator circuit based on single VDTA. Analog Integr. Circuits Signal Process. 96(3), 417–433 (2018). https://doi.org/10.1007/s10470-018-1177-6

P.B. Petrović, A new electronically controlled floating/grounded meminductor emulator based on single MO-VDTA. Analog Integr. Circuits Signal Process. 110(1), 185–195 (2022). https://doi.org/10.1007/s10470-021-01946-4

P.B. Petrović, Electronically adjustable grounded memcapacitor emulator based on single active component with variable switching mechanism. Electronics (Basel) 11(1), 161 (2022). https://doi.org/10.3390/electronics11010161

N. Raj, R.K. Ranjan, A. James, Chua’s oscillator with OTA based memcapacitor emulator. IEEE Trans. Nanotechnol. 21, 213–218 (2022). https://doi.org/10.1109/tnano.2022.3168154

F.J. Romero, D.P. Morales, A. Godoy, F.G. Ruiz, I.M. Tienda-Luna, A. Ohata, N. Rodriguez, Memcapacitor emulator based on the Miller effect. Int. J. Circuit Theory Appl. 47(4), 572–579 (2019). https://doi.org/10.1002/cta.2604

M.P. Sah, C. Yang, R.K. Budhathoki, H. Kim, H.J. Yoo, Implementation of a memcapacitor emulator with off-the-shelf devices. Elektronika Ir Elektrotechnika 19(8), 54–58 (2013). https://doi.org/10.5755/j01.eee.19.8.2673

T. Saigusa, A. Tero, T. Nakagaki, Y. Kuramoto, Amoebae anticipate periodic events. Phys. Rev. Lett. 100(1), 018101 (2008). https://doi.org/10.1103/physrevlett.100.018101

C. Sánchez-López, M.A. Carrasco-Aguilar, C. Muñiz-Montero, A 16 Hz–160 kHz memristor emulator circuit. AEU-Int. J. Electron. C. 69(9), 1208–1219 (2015). https://doi.org/10.1016/j.aeue.2015.05.003

C. Sanchez-Lopez, J. Mendoza-Lopez, M.A. Carrasco-Aguilar, C. Muniz-Montero, A floating analog memristor emulator circuit. IEEE Trans. Circuits Syst. II Express Briefs 61(5), 309–313 (2014). https://doi.org/10.1109/tcsii.2014.2312806

A. Sawa, Resistive switching in transition metal oxides. Mater. Today 11(6), 28–36 (2008). https://doi.org/10.1016/s1369-7021(08)70119-6

P.K. Sharma, R.K. Ranjan, F. Khateb, M. Kumngern, Charged controlled MEM-element emulator and its application in a chaotic system. IEEE Access 8, 171397–171407 (2020). https://doi.org/10.1109/access.2020.3024769

A. Singh, S.K. Rai, New meminductor emulators using single operational amplifier and their application. Circuits Syst. Signal Process. 41(4), 2322–2337 (2022). https://doi.org/10.1007/s00034-021-01886-4

A. Singh, S.K. Rai, VDCC-based memcapacitor/meminductor emulator and its application in adaptive learning circuit. Iran. J. Sci. Technol. Trans. Electr. Eng. 45(4), 1151–1163 (2021). https://doi.org/10.1007/s40998-021-00440-x

H. Sozen, U. Cam, A novel floating/grounded meminductor emulator. J. Circuits Syst. Comput. 29(15), 2050247 (2020). https://doi.org/10.1142/s0218126620502473

D.B. Strukov, G.S. Snider, D.R. Stewart, R.S. Williams, The missing memristor found. Nature 453(7191), 80–83 (2008). https://doi.org/10.1038/nature06932

M. Tatović, P.B. Petrović, Realization of a memcapacitance emulator utilizing a singular current-mode active block. J. Electr. Eng. 74(5), 390–402 (2023). https://doi.org/10.2478/jee-2023-0047

M. Di Ventra, Y.V. Pershin, L.O. Chua, Circuit elements with memory: memristors, memcapacitors, and meminductors. Proc. IEEE 97(10), 1717–1724 (2009). https://doi.org/10.1109/jproc.2009.2021077

J. Vista, A. Ranjan, Design of memcapacitor emulator using DVCCTA. J. Phys. Conf. Ser. 1172(1), 012104 (2019). https://doi.org/10.1088/1742-6596/1172/1/012104

J. Vista, A. Ranjan, Simple charge controlled floating memcapacitor emulator using DXCCDITA. Analog Integr. Circuits Signal Process. 104(1), 37–46 (2020). https://doi.org/10.1007/s10470-020-01650-9

F.Z. Wang, L.O. Chua, X. Yang, N. Helian, R. Tetzlaff, T. Schmidt, C. Li, J.M.G. Carrasco, W. Chen, D. Chu, Adaptive neuromorphic architecture (ANA). Neural Netw. 45, 111–116 (2013). https://doi.org/10.1016/j.neunet.2013.02.009

F. Wang, F. Wang, Floating memcapacitor based on knowm memristor and its dynamic behaviors. IEEE Trans. Circuits Syst. II Express Briefs 69(12), 5134–5138 (2022). https://doi.org/10.1109/tcsii.2022.3201225

X.Y. Wang, A.L. Fitch, H.H.C. Iu, W.G. Qi, Design of a memcapacitor emulator based on a memristor. Phys. Lett. A 376(4), 394–399 (2012). https://doi.org/10.1016/j.physleta.2011.11.012

Z. Wang, 2-MOSFET transresistor with extremely low distortion for output reaching supply voltages. Electron. Lett. 26(13), 951 (1990). https://doi.org/10.1049/el:19900620

A. Yr, G.S. Satyanarayan, G. Trivedi, A high frequency MOS-based floating charge-controlled memcapacitor emulator. IEEE Trans. Circuits Syst. II Express Briefs 70(3), 1189–1193 (2023). https://doi.org/10.1109/tcsii.2022.3221334

A. Yr, G.S. Satyanarayan, G. Trivedi, An optimized MOS-based high frequency charge-controlled memcapacitor emulator. IEEE J. Emerg. Sel. Top. Circuits Syst. 12(4), 793–803 (2022). https://doi.org/10.1109/jetcas.2022.3221314

N. Yadav, S.K. Rai, R. Pandey, New high frequency memristorless and resistorless meminductor emulators using OTA and CDBA. Sādhanā 47(1), 8 (2022). https://doi.org/10.1007/s12046-021-01785-z

X. Yang, B. Taylor, A. Wu, Y. Chen, L.O. Chua, Research progress on memristor: from synapses to computing systems. IEEE Trans. Circuits Syst. I Regul. Pap. 69(5), 1845–1857 (2022). https://doi.org/10.1109/tcsi.2022.3159153

A. Yesil, Floating memristor employing single MO-OTA with hard-switching behavior. J. Circuits Syst. Comput. 28(02), 1950026 (2019). https://doi.org/10.1142/s0218126619500269

A. Yesil, Y. Babacan, Electronically controllable memcapacitor circuit with experimental results. IEEE Trans. Circuits Syst. II Express Briefs 68(4), 1443–1447 (2021). https://doi.org/10.1109/tcsii.2020.3030114

A. Yesil, Y. Babacan, F. Kacar, Design and experimental evolution of memristor with only one VDTA and one capacitor. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 38(6), 1123–1132 (2019). https://doi.org/10.1109/tcad.2018.2834399

D.S. Yu, Y. Liang, H. Chen, H.H.C. Iu, Design of a practical memcapacitor emulator without grounded restriction. IEEE Trans. Circuits Syst. II Express Briefs 60(4), 207–211 (2013). https://doi.org/10.1109/tcsii.2013.2240879

D. Yu, H.H.-C. Iu, A.L. Fitch, Y. Liang, A floating memristor emulator based relaxation oscillator. IEEE Trans. Circuits Syst. I Regul. Pap. 61(10), 2888–2896 (2014). https://doi.org/10.1109/tcsi.2014.2333687

D. Yu, Y. Liang, H.H.C. Iu, L.O. Chua, A universal mutator for transformations among memristor, memcapacitor, and meminductor. IEEE Trans. Circuits Syst. II Express Briefs 61(10), 758–762 (2014). https://doi.org/10.1109/tcsii.2014.2345305

D. Yu, X. Zhao, T. Sun, H.H.C. Iu, T. Fernando, A simple floating mutator for emulating memristor, memcapacitor, and meminductor. IEEE Trans. Circuits Syst. II Express Briefs 67(7), 1334–1338 (2020). https://doi.org/10.1109/tcsii.2019.2936453

Y. Zhang, X. Wang, E.G. Friedman, Memristor-based circuit design for multilayer neural networks. IEEE Trans. Circuits Syst. I Regul. Pap. 65(2), 677–686 (2018). https://doi.org/10.1109/tcsi.2017.2729787

C. Zheng, D. Yu, H.H.C. Iu, T. Fernando, T. Sun, J.K. Eshraghian, H. Guo, A novel universal interface for constructing memory elements for circuit applications. IEEE Trans. Circuits Syst. I Regul. Pap. 66(12), 4793–4806 (2019). https://doi.org/10.1109/tcsi.2019.2938094

Acknowledgments

This work was supported by The Scientific and Technological Research Council of Turkey (TUBITAK) under Project 119E458 and also by Scientific Research Projects Coordination Unit of Bandırma Onyedi Eylül University, Project Number: BAP-23-1013-001. The author wishes to thank all the anonymous reviewers for their constructive comments and useful suggestions.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The corresponding author declares no conflicts of interest regarding the publication of this paper.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Korkmaz, M.O., Babacan, Y. & Yesil, A. CCII- and OTA-Based Tunable Memcapacitor Emulator Circuits Without Using Passive Elements. Circuits Syst Signal Process 43, 4093–4120 (2024). https://doi.org/10.1007/s00034-024-02681-7

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-024-02681-7