Abstract

A high energy-efficient and reference voltage self-adaptive switching scheme for a triple-capacitive array successive approximation register analog-to-digital converters is proposed. The proposed switching time scheme includes Bi-level and Tri-level modes. The operating mode can be automatically switched by the reference voltage self-adaptive module according to the number of reference voltages of the peripheral circuits. The proposed timing scheme has the advantage of automatic compatibility with Bi/Tri-level reference voltage, which can be better adapted to the requirements of different hybrid ADC architectures. In Bi/Tri-level mode, two-step method, and monotonic switching scheme, floating capacitor technology is used to achieving 99.6% and 99.9% savings in average switching energy and a 73.4% reduction in total capacitance compared to the conventional scheme when applied to a 10-bit SAR ADC. The INL and DNL for both the Bi-level reference mode and the Tri-level reference mode are 0.350, 0.347 and 0.177, 0.172, respectively. In addition, the scheme eliminates to reset energy while regulating M to achieve a compromise between energy, area, and linearity. The post-simulation results show that the 10-bit SAR ADC with the proposed switching scheme can achieve a signal-to-noise distortion ratio (SNDR) of 60.53 dB and a spurious-free dynamic range (SFDR) of 68 dB at a sampling rate of 20 MS/s in a 65 nm CMOS process. The area of this ADC is only 0.2392 mm2.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

The development of analog-to-digital converters (ADCs) has changed from the traditional design ideas of low-power successive approximation registers (SARs), high-speed Pipelined SARs, and high-accuracy Delta-Sigma ADCs to a high power-efficiency development, resulting in ADCs such as high-accuracy time-to-digital converters (TDCs) and VCO-SARs. DAC capacitive switching circuits are one of the main energy consuming components of many ADCs, such as VCO-SAR [2], Pipelined-SAR [6, 14], and MASH ADC [13]. For example, reference [15] presented a switched-capacitor array applied to an SAR ADC in which the comparator, digital logic control circuit, and DAC capacitor array account for 8.9%, 8.6%, and 53%, respectively.

SAR-based architectures are gaining importance because they do not require high-energy consumption amplifiers and are being adopted in new types of MASH ADC, VCO-SAR [31], and Pipeline SAR ADCs [14]. The key to high power-efficiency designed of SAR ADCs is in the switching strategy of the DAC array. The DAC timing strategy from the traditional monotonic structure is gradually researched. In addition to power consumption, the linearity, the number of DAC capacitors, and other issues are gradually given attention. A number of switching solutions have been proposed to address power consumption, linearity, and area issues.

Low-power consumption Digital-to-analog converters have been the focus on attention, with the key points being energy-efficient switching technology and reduced capacitor count [1, 10, 12, 18, 20, 22, 23]. The two-level reference voltage switching scheme is not ideal for energy saving [12, 23]. So, the third level reference voltage Vcm (1/2Vref) is introduced [3, 12, 21, 27, 30, 33, 34, 36]. Compared to traditional switching energy consumption can be saved by more than 80%. To further to reduce the switching energy, several switching methods are used, including floating capacitor techniques [7, 11, 29], the introduction of a fourth reference voltage Vaq (1/4Vref) [24], monotonic structure [17], and two-step structure schemes [3, 4, 8, 9]. However, each method has its disadvantages. Higher DAC logic complexity is required [5, 32], more than enough reference voltage is needed [16, 26], excessive common-mode voltage swing [27].

In terms of the number of external reference voltages, there are two common switching strategies with Bi-level and Tri-level reference voltages. Although increasing the number of reference voltages can effectively reduce power consumption and improve linearity, the problem is that adding an additional number of references adds a burden on the peripheral circuitry and additional circuit overhead.

The idea of considering only the harsh conditions of increasing reference levels in many switching scheme papers without compatibility with external applications can make it difficult for these switching strategies to be more widely used. Thus, it is not only necessary to consider how to optimize the structure of the switching scheme, but also the external conditions to improve the compatibility of the timing scheme against the external reference level.

Therefore, a switch structure that can be adjusted according to the number of external levels is proposed. This increases the compatibility of DAC switching technology and allows it to be freely selected in different external configurations. The proposed reference voltage self-adaptive switching structure has good linearity and very low power consumption in Tri-level mode and excellent compatibility in Bi-level mode with only two reference levels. In addition, there is no reset energy consumption of both modes in the proposed switching strategy.

The rest of the paper is structured as follows: Section 2 describes the proposed reference voltage self-adaptive switching scheme. Sect. 3 discusses the proposed switching strategy of common-mode voltage variation. Section 4 and Sect. 5 mainly compare and analyze the energy consumption of the switching mode in this paper with various previous switching schemes. Section 6 analyzes and compares the advantages and disadvantages of the linearity of Bi-level reference mode and Tri-level reference mode switch technology. Section 7 draws conclusions.

2 Proposed Switching Strategy

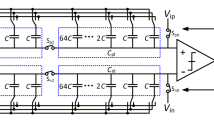

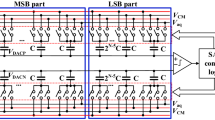

Although the proposed timing technique can support a minimum of a 4-bit SAR structure, to reflect the scalability of the structure, a 10-bit SAR is used as an example in this paper. This technique has a two-step structure divided into two stages of coarse quantization and fine quantization. The proposed novel switch array is a reference voltage self-adaptive structure of the option to adopt Bi-level reference voltage modes and Tri-level reference voltage modes. The proposed switching scheme adds a balancing capacitor to the finely quantized capacitor array so that each bit of the finely quantized capacitor can match the corresponding conversion bit inversion voltage.

In the proposed structure, M controls the length of the coarsely and finely quantized capacitor arrays of both capacitor arrays. Different values of M can be set from 2 to 7, and different values of M have various energy consumption and linearity. Figure 1 shows the architecture of the proposed 10-bit SAR ADC, where C is the unit capacitor. The ADC includes a coarse quantization capacitor array (CCA), two fine quantization capacitor arrays (FCA), a four-input comparator, and SAR logic control circuitry. These include Tri-level reference voltages, Vcm (1/2 of Vref), Vaq (1/4 of Vref), and gnd. The number of three references is kept constant when the Tri-level reference switching mode is adopted, and the Vaq reference voltage is turned off when the Bi-level reference mode is chosen, as shown in Fig. 2.

2.1 Switching Mode for Bi-Level

Figure 2 shows the structure of the proposed Bi-level voltage mode of the reference voltage self-adaptive switching scheme. When only two external reference voltages are available, the DAC array can use the proposed "Bi-level" switching mode, increasing the adaptability of the overall structure. The Bi-level reference mode uses two reference levels, Vcm and gnd, and disables the dependence on an additional reference voltage (Vaq). The Bi-level switching scheme combines partial floating capacitor technology with single-ended capacitor floating technology to implement the conversion process.

The proposed Bi-level reference mode consists of three phases: input sampling, coarse quantization, and fine quantization. During the sampling phase, the top plates of the capacitors in the CCA are connected to the input signal, and the bottom plates of all capacitors in the CCA are connected to Vcm. At the same time, the bottom plates of the SP1 and SN2 capacitors in the FCA are reset to Vcm and the bottom plates of the SP2 and SN1 capacitors are reset to gnd.

Figures 3 and 4 show the voltage reversal of the proposed five-bit Bi-level voltage capacitor switching scheme. At the end of the first comparison, if Vip > Vin, the SP1 and SN1 capacitor bottoms in the FCA are interconnected at this time, realizing that the voltage at the positive end of the comparator drops by 1/4 and the voltage at the negative end of the comparator rises by 1/4.

When D [1] = 1, the energy consumed by the voltage flipped is zero, as the following equation proves:

The coarse quantization of the capacitor array single-ended flip is performed next, and when Vcp > Vcn, the high capacitance bottom base plate voltage of the capacitor array at Vcn will be connected from Vcm to gnd.

As D [2] = 1 consumes 1/8CVref2switching energy, it is proven in the following equations:

The N-terminal capacitor array has no energy consumption, and the total power consumption is:

The capacitor array of the fine quantization stage uses a double-ended capacitor flip. When VCP > VCN, D [3] = 1 capacitor array using a double-ended capacitance flip results in the flip as shown in Fig. 4 'a,' consuming energy as follows:

The last bit uses a floating capacitor technique where the voltage at one end is reduced to gnd and the other end is held. The above equation proves that the total energy consumption is smaller. The energy consumption of the proposed Bi-level reference voltage model is reduced by 99.6% compared to the conventional structure.

2.2 Switching Mode for Tri-level

When an external reference voltage is sufficiently provided, the DAC array can use the proposed Tri-level reference voltage technique to further to improve linearity and switching power consumption. Figure 5 shows the overall structure of the Tri-level reference voltage.

During the sampling phase, the top plates of the capacitors in the CCA are connected to the input signal, and the bottom plates of all capacitors in the CCA are connected to Vaq. Meanwhile, the bottom plates of the SP1 and SN2 capacitors in the FCA are reset to Vcm and the bottom plates of the SP2 and SN1 capacitors are reset to gnd.

Figures 6 and 7 show the voltage reversal of the proposed five-bit Tri-level reference voltage capacitor switching scheme. At the end of the first comparison, if Vip > Vin, the SP1 and SN1 capacitor bottoms in the FCA are reset to Vaq at this time, thus achieved a 1/4 drop in the voltage at the positive side of the comparator and a 1/4 rises in the voltage at the negative side of the comparator.

In the first comparison cycle, when D [1] = 1, the consumed switching energy is calculated by:

The second capacitor array flip, D [2] = 1, is performed next when VCP > VCN, at which point the SP1 capacitor base in the FCA is reset to gnd, achieving a voltage drop of 1/4 on the positive side of the comparator. This process has no energy consumption. Total power consumption is zero.

When VCP > VCN, D [3] = 1, the coarse quantization capacitor array uses single-ended capacitance flipping, and the high capacitance voltage is flipped from Vaq to gnd. The result of the way flip is shown as 'a' in Fig. 5. In this bit-cycle, the switching energy is consumed by:

The N-terminal capacitor array consumes zero energy. Total energy consumption is:

When VCP > VCN and D [4] = 1, the capacitor array uses a single-ended capacitance float. The voltage at the high side of the capacitor array bottom plate at the VCN end will be connected to Vcm by Vaq. Similarly, the energy of this process is calculated as follows:

The P-terminal capacitor array consumes zero energy. So, the energy consumption expression is:

The proposed Tri-level reference voltage mode consumes 99.9% less energy than the conventional structure. The Tri-level voltage mode has higher energy efficiency compared to the Bi-level voltage mode.

2.3 Reference Voltage Self-Adaptive Scheme

Figure 8 illustrates the reference voltage self-adaptive judgment module. The two dynamic comparators start operating when the ADC resets clock signals to arriving. Vaq is connected to the judgment module and to VDD through a pull-up resistor. The static power consumption can be greatly reduced since the pull-up resistor is a PMOS pseudo-resistor (resistance of GΩ level). When Vaq is overhung, the pull-up resistor causes the voltage at the comparator input to be VDD, and both comparators compare to 1. The judgment result returned through to the XOR gate is 0, which means that no additional external reference level is determined, and Bi-level reference mode is used. When Vaq is connected to the ADC, the upper and lower comparator outputs result in 0 and 1, and the judgment result returned through the XOR gate is 1, using Tri-level reference mode. Therefore, the proposed periphery level judgment module can self-adapt to the external reference situation for the timing strategy change. In addition, since a coarse dynamic comparator and a pseudo-resistor are used and compared only once during the reset phase, the power consumption is basically negligible compared to the DAC switching energy consumption.

2.4 DAC Control Logic Complexity Analysis

The control circuit of the overall circuit structure includes a Tri-level reference mode control circuit and a Bi-level reference mode control circuit. The reference voltage self-adaptive module is highly adaptable because it selects either the Bi-level voltage mode or the Tri-level voltage mode based on the voltage reference provided by the external circuit.

The control circuit of the Bi-level voltage switching mode uses a single-ended flip switching scheme to lower the bottom plate of the switching array of the low voltage end to Vcm to gnd in the coarse quantization stage. A double-ended flip technique is used in the fine quantization stage, and for the last bit, a single-ended flip other end hold is used.

The coarse quantization staged and the fine quantization stage of the control circuit of the Tri-level switching mode both use single-ended flipped conversion. The difference is that in the coarse quantization stage, the switch array bottom plate at the low voltage end is lowered from Vaq to gnd. The fine quantization stage will fix one end of the capacitor array voltage either up or down. The control logic of the proposed switching structure is not complex compared to many recent ideas, e.g., TSDC [3], TSMS [9].

2.5 The Proposed Four-Input Comparator

Traditional four-input comparators have only one stage structure with large offset and delay, so this paper proposes a novel type of two-stage four-input comparator. The proposed four-input comparator is designed as shown in Fig. 9. The proposed comparator consists of a pre-amplification stage, a comparison stage and a latching stage. The pre-amplification stage sets the bias voltage to keep the Vgs voltage of the differential input pair the same as the common-mode variation and to reduce the effect of Vcm and Vaq on gain and offset [8].

Figure 10 shows 500-run Monte Carlo simulations for the coarsely quantized port. It can be seen that the offset at the coarse quantization port is 665 μV, and this offset is a fixed offset due to the design while the dynamic offset is 3σ = 3*19 μV = 57 μV (process & mismatch).

Figure 11 shows 500-run Monte Carlo simulations for the finely quantized port. It can be seen that the fixed offset is 137.6 μV, and the dynamic offset is 3σ = 3*3.67 μV = 11.01 μV.

3 Analysis of Common-Mode Voltage in Timing Switches

The input common-mode voltage range puts demand on the comparator performance, and a large range of common-mode voltage swing can lead to increased comparator noise. Figure 12 shows the 10-bit DAC output waveform of the proposed Bi-level reference voltage capacitor switching scheme in M = 5. At the end of the first comparison, since Vip > Vin, all capacitor arrays of fine quantization are connected to each other at this point, and the voltage at the positive side of the comparator achieves a 1/4 Vref voltage dropped and the voltage at the negative side of the comparator achieves a 1/4 Vref voltage rise. At the end of the second comparison, the voltage at the positive end of the comparator achieves a voltage drop of 1/4 Vref due to Vip > Vin when the bottom plate of the capacitor array of the positive end of the comparator is connected to gnd. The D [2:5] digital code is implemented by inverting the CCA. The D [6:10] digital code is implemented by inverting the with FCA.

Figure 13 shows the 10-bit DAC output waveform of the proposed Tri-level reference voltage capacitor switching scheme in M = 5. At the end of the first comparison, since Vip > Vin, SP2, SN2 turn off, and FCA bottom voltage are connected to Vaq, the voltage at the positive side of the comparator achieves a 1/4 Vref voltage drop, and the voltage at the negative side of the comparator achieves a 1/4 Vref voltage rise. At the end of the second comparison, since Vip > Vin, the array of capacitors with fine quantization at the positive side of the comparator is connected to gnd at this time, and the voltage at the positive side of the comparator achieves a voltage drop of 1/4 Vref. The D [3:6] digital code is implemented by inverting the capacitor array of CCA. The D [7:10] digital code is implemented by inverting the code with FCA. The pressure on the common-mode offset is less for the comparator, and comparators with high common-mode range requirements can be used in our approach.

Figures 12 and 13 show each voltage inversion for both Bi-level and Tri-level modes. Both proposed structures have a maximum common-mode offset of less than 0.25 Vref due to the first double-ended inversion mode. The structure in references [1, 27] uses a single-ended inversion case; therefore, the maximum common-mode voltage offset is less than 0.5 Vref. Therefore, the proposed technique requires less comparators, reduces the difficulty of circuit designed, and improves compatibility.

4 Dynamic Performance Analysis

4.1 Effects of Capacitor Mismatch

The dynamic performance of the ADC is influenced by the accuracy per unit capacitance. Figures 14 and 15 show the FFT analysis after 500-run Monte Carlo simulations of a 10-bit SAR ADC with Tri-level and Bi-level in the capacitance mismatch range of 0–1%. Figure 15 illustrates that the dynamic performance decreases with increasing capacitance mismatch. When the capacitance mismatch is 1%, the SFDR and SNDR are reduced by 12.1 and 3.1 dB for the Bi-level switching scheme and 9.4 and 0.7 dB for the Tri-level switching scheme, respectively.

4.2 Effects of Voltage Mismatch

The dynamic performance of the ADC is also affected by the accuracy of the reference voltages Vcm and Vaq. Figures 16 and 17 show the FFT analysis after 500-run Monte Carlo simulations of a 10-bit SAR ADC with Tri-level and Bi-level in the voltage mismatch range of 0–0.5%. Figure 17 illustrates that the dynamic performance decreases with increasing capacitance mismatch. When the capacitance mismatch is 0.5%, the SFDR and SNDR decreased by 9.8 and 3.02 dB, respectively, for the Bi-level switching scheme, and by 13.4 and 4.29 dB, respectively, for the Tri-level switching scheme.

4.3 The Effect of Mismatch on FFT

The proposed switched-capacitor array introduces CCA and FCA to establish a two-step structure framework, and the energy consumption of the two-step switching scheme is 37.5CVref2, which is 97.2% saving compared to the conventional switching scheme. To verify the effect of non-ideal factors, a 10-bit SAR ADC model was built in MATLAB.

Figures 18 and 19 show 500 points of SFDR, SNDR, and ENOB for the proposed switching scheme in Bi-level mode and Tri-level mode at a sampling rate of 1 MS/s and an input signal frequency of 243.652 kHz. The number of FFT points simulated in Figs. 18 and 19 is 2048. There is almost no spurious and harmonics in the Bi-level mode and the Tri-level mode proposed by the ideal model in Figs. 18a and 19a. The SNDR and SFDR dropped to 61.7 dB and 78.1 dB for adding the voltage mismatch Bi-level mode as seen in Fig. 18b. The SNDR and SFDR dropped to 59 dB and 73.5 dB for adding the capacitive mismatch Tri-level mode in Fig. 18c. Figure 18d shows that when capacitance mismatch (1%), Vcm and Vaq mismatch (0.1%) are added to the ideal model simultaneously, SNDR and SFDR decrease to 58.6 and 64.3 dB, respectively.

Figure 19d shows that the Tri-level model reduces the SNDR and SFDR to 58.5 dB and 67.2 dB, respectively; when capacitance mismatch (1%), Vcm and Vaq mismatch (0.1%) are added to the ideal model at the same time. The switched-capacitor scheme still has good stability when the noise increases.

4.4 Post-Simulation Results

To verify the implementation of the proposed switched-capacitor array, we designed a 10-bit 10 MS/s SAR ADC with the proposed switching scheme. The SAR ADC with the proposed switching scheme is designed in a 65 nm CMOS process with a 1.2 V supply. Figure 20 shows the layout of the SAR ADC with an effective area of 0.2392 mm2. The unit capacitance size is 20 fF.

Figure 21 shows the power consumption of each module of the proposed SAR ADC. The total power is 548.5 μW, of which clock circuit, CDAC, S/H, Dynamic SAR logic, comparator, and voltage buffers are 177.7, 164, 2.1, 128, 76.7, and 103.5 μW, respectively. It is proved that the switching scheme has very low power consumption. Figure 22 shows the post-simulation results of the SAR ADC with SND, SFDR, SNDR, and ENOB of 60.528 dB, 68 dB, 60.525 dB, and 9.76 bits, respectively, at 1.015625 MHz input frequency. The number of FFT points simulated in Fig. 22 is 256. Through the SNDR and SFDR of the post-simulation results, it can be seen that the switching scheme has good linearity.

5 Analysis of Energy Consumption in Timing Switches

In order to facilitate the analysis and comparison, this section presents the energy consumption analysis in both the Bi-level reference mode and Tri-level reference mode cases, respectively. The proposed two-step structure is divided into a coarse quantization stage and a fine quantization stage, each of which implements a portion of the digital code conversion. M determines the number of bits in each of the two quantization segments. In the theoretical analysis, M can be set to 2 to 7, but considering the noise, the sampling array cannot be too short, so M cannot be too small. Therefore, only the cases of "M = 4, 5, 6" are analyzed in this section. The behavioral simulation of the proposed switching method is carried out in MATLAB and proposed to this paper for the case of a 10-bit SAR ADC with different M values. In order to simplify the analysis, the modeling analysis here does not have the influence of non-ideal factors caused by the parasitic capacitance, and the analysis of the non-ideal influence of parasitic capacitance is discussed in later section.

Figure 23 shows the switching energy consumption of the Bi-level reference mode for different M values. The conclusion is that the smaller the value of M, the lower the energy consumption of the switch. As shown in Table 1 below, Bi-level reference voltage switching schemes.

The energy consumption and linearity of the proposed Bi-level reference voltage switching scheme for M = 4, 5, and 6 are summarized in Table 1. It can be seen from the table that the energy consumption gradually increases as the value of M increases due to the increase in the capacitance array in the coarse quantization stage. The overall linearity gradually improves.

In Tri-level mode, the Vaq reference voltage is increased and a single-ended voltage flip technique is used with no energy consumption during the first three flip cycles. Figure 24 shows the energy consumption of the proposed Tri-level reference voltage switching strategy in the three cases of M = 4, 5, and 6.

Tri-level reference voltage switching schemes are shown in Table 2 below.

The energy consumption and linearity of the proposed Tri-level reference voltage switching scheme for M = 4, 5, and 6 are summarized in Table 2. From comparing Table 1, it can be seen that the energy consumption and linearity of the Tri-base are better than that of the reference voltage self-adaptive structure regardless of the value of M. Therefore, it is concluded that the linearity becomes progressively better as the value of M increases.

Therefore, at the cost of increased external level reference voltage, the proposed Tri-level reference mode is more suitable to save circuit power consumption and improve linearity.

Figure 25 shows the simulated energy consumption plots of the proposed 10-bit SAR ADC switching method and several switching schemes with lower power consumption. A ramp signal is created under MATLAB simulation software, and the energy consumed by various capacitive switching schemes is calculated and compared by creating the inversion models of HSRS, MSB-split, Tri-level, Vcm-monotoic, Five-level, Hybrid, Proposed Bi-level mode, and Proposed Tri-level mode switching schemes for A/D conversion of the input signal. Figure 25 in the text shows the energy consumption of each switching scheme.

5.1 Reset Energy Consumption

Reset energy consumption is also one of the key points affecting the energy consumption of the switching strategy. Reset energy consumption is to change the final state of the flip of the capacitor array of the initial state. The reset voltage flipped when Vip > Vin using the Bi-level reference switch scheme is shown in Fig. 26.

The reset voltage flip when Vip > Vin using the Tri-level reference switching scheme is shown in Fig. 27.

It can be demonstrated by the equations in the Appendix that the proposed Bi-level reference voltage switching scheme and the Tri-level reference voltage switching scheme both have zero reset energy consumption. The proposed timing structure has a very high energy utilization.

5.2 Parasitic Capacitance

The presence of parasitic capacitance of the comparators and switches in the circuit also has a non-negligible impact on the energy consumption of the switching scheme. In order to simulate the actual capacitor array more accurately, the energy consumption of four switching schemes, Vcm-monotonic [36], Five-level [16], Hybrid [30], and the proposed reference voltage self-adaptive switching mode were simulated with parasitic capacitors, respectively.

Figure 28 illustrates the parasitic capacitance present in the capacitor array for the Tri-level reference switching scheme. Ideally, the average power consumption of the analyzed capacitor array is zero when the bottom plate voltage of all capacitors of the inefficient capacitor array is increased from gnd to Vcm. However, in the actual circuit, the power consumption is not zero because of the presence of the top board parasitic capacitor Cpt and the bottom board parasitic capacitor Cpb.

Figures 29 and 30 show the effect of parasitic capacitance on the switching energy. Compared to the four switching schemes, it can be seen that the energy consumption of the switch becomes larger after the addition of the parasitic capacitor. The addition of parasitic capacitors results in energy savings of 97.1%, 97.4%, 97.6%, 99.7%, and 99.8% for the Vcm-monotonic, Five-level, Hybrid, and novel reference voltage self-adaptive switching schemes, respectively, compared to conventional switching arrays. By observing Figs. 29 and 30, it can be concluded that the proposed novel switching scheme still has the best energy efficiency.

6 Linearity Analysis in Timing Switches

To improve energy utilization efficiency, the unit capacitance area is kept as small as possible, but the matching between capacitor arrays will greatly affect the overall conversion linearity. Figures 31, 32, 33, 34 depict behavioral simulation results of 500 Monte Carlo runs of the proposed reference voltage self-adaptive switching scheme for INL (Integral Nonlinearity) and DNL (Differential Nonlinearity) with σu/Cu = 0.01. Since the case of M = 5 is an excess of the cases of M = 4 and M = 6, it will not be discussed in detail. The linearity of M = 5 is better than that of M = 4, but not as good as that of M = 6.

Figures 31 and 32 show the linearity simulation results for Bi-level reference voltages and Tri-level reference voltages for the case of M = 4. It can be seen from the plots that the INL and DNL of the tri-base switching scheme is 0.337 and 0.332, respectively, while the INL and DNL of the two-base switching scheme is 0.634 and 0.598, respectively. The linearity of the tri-base switching scheme is better than that of the two-base switching scheme.

Figures 33 and 34 show simulation results of the reference voltage self-adaptive switching method. The root mean square (RMS) INL and RMS DNL of the proposed architecture with Tri-level reference mode are only 0.177LSB and 0.172LSB, separately, while the RMS INL and RMS DNL of Bi-level reference mode are 0.350LSB and 0.347LSB, respectively. The linearity of the Tri-level reference voltage switching scheme is better than that of the Bi-level reference voltage switching scheme.

From the analysis of the above three cases, it is concluded that the linearity of the overall structure becomes better and better due to the increase in the capacitance array of the coarse quantization stage caused by the increase in M.

Table 3 summarizes the average energy consumption, linearity, and capacitance area of the different switching schemes in previous works. As can be seen from the table, the proposed structure has low energy consumption and good linearity in the Bi-level reference voltage mode. In the Tri-level reference voltage mode, the proposed structure has extremely low energy consumption and very good linearity compared with other switching structures. The structure can be adjusted to the reference to the periphery circuit to improve the overall circuit compatibility.

Table 4 summarizes performance indicators such as technology, power supply, sampling rate, and active area of different switching schemes in previous work. The figure-of-merit (FOM) is as below:

where fs is the Sampling rate, Power represents that the power consumption of the ADC and the ENOB is the effective number of bits at Nyquist frequency sampling rate. The proposed SAR ADC achieves an FOM of 31.6 fJ/conversion-step. It can be concluded that the proposed switching scheme has better FOM in medium and high-speed ADCs.

Figure 35 compares the three aspects of energy consumption, linearity, and the number of capacitors per unit, and it can be seen that the Tri-level mode is very good in terms of both energy consumption and linearity. The Bi-level reference voltage switching mode also consumes less energy than most switching schemes. Therefore, the proposed energy consumption timing technique has very good external compatibility and is suitable for energy-efficient SAR-based ADCs.

7 Conclusion

A high energy-efficient and reference voltage self-adaptive switching scheme for hybrid ADC is proposed. With the reference voltage self-adaptive module, the compatibility of the proposed switching timing scheme can be improved to a large extent. This is a better trade-off between energy efficiency, number of capacitors, common-mode voltage range, complexity of the logic control circuit, and linearity in our technique. The proposed reference voltage self-adaptive switching strategies achieved 99.7% and 99.9% savings in average switching energy and 73.4% reduction in total capacitance compared to the conventional scheme. The INL and DNL for both the Bi-level reference mode and the Tri-level reference mode are 0.350, 0.347 and 0.177, 0.172, respectively. The post-simulation results show that the 10-bit SAR ADC with the proposed switching scheme can achieve a signal-to-noise distortion ratio (SNDR) of 60.53 dB and a spurious-free dynamic range (SFDR) of 68 dB at a sampling rate of 20 MS/s in a 65 nm CMOS process. The area of this ADC is only 0.2392mm2. Furthermore, the proposed two modes have no reset energy. Therefore, the proposed reference voltage self-adaptive switching scheme is suitable for realizing high energy-efficient and high area utilization VCO-SAR, Pipelined-SAR, or MASH ADC.

Data availability

Data sharing is not applicable to this article as no datasets were generated or analyzed during the current study.

References

S. Baek, K. Lee, M. Lee, Energy-efficient switching scheme for SAR ADC using zero-energy dual capacitor switching. Analog Integr. Circ. Sig. Process 94(4), 317–322 (2018). https://doi.org/10.1007/s10470-017-1101-5

J. Borgmans, E. Sacco, P. Rombouts, G. Gielen, Methodology for readout and ring oscillator optimization toward energy-efficient VCO-based ADCs. IEEE Trans. Circ. Syst. I Regul. Pap. 69(3), 985–998 (2022). https://doi.org/10.1109/TCSI.2021.3129919

T.T. Chen, J.P. Cai, High-efficient two-step switching scheme for SAR ADC with dual-capacitive arrays and four-input comparator. Analog Integr. Circ. Sig. Process 101(4), 363–373 (2019). https://doi.org/10.1007/s10470-019-01536-5

Y.S. Chen, Y.Q. Zhuang, A 99.8% energy-reduced two-stage mixed switching scheme for SAR ADC without reset energy. Circuits Systems Signal Process. 38(04), 5426–5447 (2019). https://doi.org/10.1007/s00034-019-01151-9

L. Ding, S.X. Dong, S.J. Liu, A novel split capacitor array switching scheme with proportional coefficient for SAR ADC. Analog Integr. Circ. Sig. Process 98(4), 597–605 (2019). https://doi.org/10.1007/s10470-018-1373-4

R. Ding, L. Dang, H. Lin, D. Sun, S. Liu, Z. Zhu, A 7b 400 MS/s pipelined SAR ADC in 65 nm CMOS. Microelectron. J. 95(3), 0026–2692 (2020). https://doi.org/10.1016/j.mejo.2019.104680

R.X. Ding, D.P. Sun, Shubin Liu, Energy-efficient switching scheme based on floating technique for SAR ADC. Analog Integr. Circ. Sig. Process 97(9), 115–122 (2018). https://doi.org/10.1007/s10470-018-1242-1

A. Gusev, D. Osipov, S. Paul, An energy efficient SAR ADC architecture with DAC Separation. IEEE International New Circuits and Systems Conference (NEWCAS) pp 118–121 (2020). Doi: https://doi.org/10.1109/NEWCAS49341.2020.9159764.

J. Huang, J. Wu, A. Wu, Two-step Vcm-based MS switching method with dual-capacitive arrays for SAR ADCs. Analog Integr. Circ. Sig. Process 94(9), 155–160 (2018). https://doi.org/10.1007/s10470-017-1082-4

L. Huang, L. Zhang, M. Chen, J. Li, J. Wu, A low-energy and area-efficient vaq-based switching scheme with capacitor-splitting structure for SAR ADCs. Circuits Syst. Signal Process. 40(12), 4106–4126 (2021). https://doi.org/10.1007/s00034-021-01666-0

Y. Huang, L.L. Huang, J.H. Wu, An energy-efficient switching scheme based on the improved semi-resting DAC structure and floating-capacitor technique for SAR ADC. Analog Integr. Circ. Sig. Process 108(4), 679–687 (2021). https://doi.org/10.1007/s10470-021-01910-2

B. Jajodia, A. Mahanta, S. Ahamed, Energy-efficient DAC switching technique for single-ended SAR ADCs. Microelectron. J. 124, 1434–8411 (2022). https://doi.org/10.1016/j.aeue.2020.153334

W. Jin, K. Pun, A DEM-free sturdy MASH delta-sigma modulator with a highly-linear tri-level DAC. In: IEEE International Conference on Electron Devices and Solid-State Circuits (EDSSC) pp. 1–2 (2019). doi: https://doi.org/10.1109/EDSSC.2019.8754500

X. Jin, H. Pan, F. Foster, A dual-residue pipelined SAR ADC using only zero-crossing signals. Analog Integr. Circ. Sig. Process 108(12), 229–239 (2021). https://doi.org/10.1007/s10470-021-01860-9

J. Li, X. Li, L. Huang, J. Wu, An energy-efficient switching scheme with low common-mode voltage variation and no-capacitor-splitting DAC for SAR ADC. Analog Integr. Circ. Sig. Process 104(4), 93–101 (2020). https://doi.org/10.1007/s10470-020-01661-6

X.Y. Li, J.S. Li, Low-power switching scheme with quarter reference voltage sources for SAR ADCs. J. Electromagnet. Eng. Sci. 22(2), 129–137 (2022). https://doi.org/10.26866/jees.2022.2.r.69

C.C. Liu, S. Chang, G.Y. Huang, Y.Z. Lin, A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure. IEEE J. Solid-State Circuits 45(4), 731–740 (2010). https://doi.org/10.1109/JSSC.2010.2042254

Y. Lu, T. Zhou, J. Huang, L. Wang, M. Chen, Y. Li, MSB-split VCM-based charge recovery symmetrical switching with set-and-down asymmetrical switching method for dual-capacitive arrays SAR ADC. Analog Integr. Circ. Sig. Process 106(4), 669–681 (2021). https://doi.org/10.1007/s10470-020-01789-5

J. Luo, Y. Liu, J. Li et al., A low voltage and low power 10-bit Non-Binary 2b/Cycle time and voltage based SAR ADC. IEEE Trans. Circuits Syst. I Regul. Pap. 67(4), 1136–1148 (2020). https://doi.org/10.1109/TCSI.2019.2949072

M. Momeni, M. Yavari, Shifting the sampled input signal in successive approximation register analog-to-digital converters to reduce the digital-to-analog converter switching energy and area. Int. J. Circuit Theory Appl. 48(11), 1873–1886 (2020). https://doi.org/10.1002/cta.2852

E. Rahimi, M. Yavari, Energy-efficient high-accuracy switching method for SAR ADCs. Electron. Lett. 50(7), 499–501 (2014). https://doi.org/10.1049/el.2013.3451

A. Rasool, M. Saberia, R. Lotfi, A low-power capacitor switching scheme with low common-mode voltage variation for successive approximation ADC. Microelectron. J. 61, 0026–2692 (2017). https://doi.org/10.1016/j.mejo.2016.12.009

B. Rikan, H. Abbasizadeh, Y. Park, A 10-bit 1 MS/s segmented Dual-Sampling SAR ADC with reduced switching energy. Microelectron. J. 70, 0026–2692 (2017). https://doi.org/10.1016/j.mejo.2017.11.005

M. Sotoudeh, F. Rezaei, A four-level switching scheme for SAR ADCs with 87.5% area saving and 97.85% energy-reduction. Circuits Syst. Signal Process. 39, 4792–4809 (2020). https://doi.org/10.1007/s00034-020-01405-x

X. Tang, M.M. Song, Y. Chen, A 10-Bit 120 kS/s SAR ADC without reset energy for biomedical electronics. Circuits Systems Signal Process. 38(4), 5411–5425 (2019). https://doi.org/10.1007/s00034-019-01138-6

Y. Tang, W.P. Zhang, C.S. Li, Low-energy and area-efficient switching scheme for SAR A/D converter. Analog Integr. Circ. Sig. Process 80(1), 153–157 (2014). https://doi.org/10.1007/s10470-014-0300-6

X.Y. Tong, M. Zhao, X. Xin, High energy efficiency and linearity switching scheme without reset energy for SAR ADC. Circuits Syst. Signal Process. (2022). https://doi.org/10.1007/s00034-022-02038

H. Wang, Vaq-assisted low-power capacitor-splitting switching scheme for SAR ADCs. Circuits Syst. Signal Process. (2022). https://doi.org/10.1007/s00034-022-02097-1

A.D. Wu, J.H. Wu, Energy-efficient switching scheme for ultra-low voltage SAR ADC. Analog Integr. Circ. Sig. Process 90(2), 507–511 (2017). https://doi.org/10.1007/s10470-016-0892-0

L.B. Xie, G.J. Wen, J.X. Liu, Y. Wang, Energy-efficient hybrid capacitor switching scheme for SAR ADC. Electron. Lett. 50(1), 22–23 (2014). https://doi.org/10.1049/el.2013.2794

Y. Xie, Y. Liang, M. Liu, S. Liu, Z. Zhu, A 10-Bit 5 MS/s VCO-SAR ADC in 0.18- m CMOS. IEEE Trans. Circuits Syst. II Express Briefs 66(1), 26–30 (2019). https://doi.org/10.1109/TCSII.2018.2833866

T. Yousefi, A. Dabbaghian, M. Yavari, An energy-efficient DAC switching method for SAR ADCs. IEEE Trans. Circuits Syst. II Express Briefs 65(1), 41–45 (2018). https://doi.org/10.1109/TCSII.2017.2676048

C. Yuan, Low-energy and area-efficient tri-level switching scheme for SAR ADC. Electron. Lett. 48(9), 482–483 (2012). https://doi.org/10.1049/el.2011.4001

H.S. Zhang, H. Zhang, R.Z. Zhang, Energy-efficient higher-side-reset-and-set switching scheme for SAR ADC. Electron. Lett. 53(18), 1238–1240 (2017). https://doi.org/10.1049/el.2017.2186

Y. Zhu, Z.H. Chen, S.R. Xin, A 10-bit 100-MS/s reference-free SAR ADC in 90 nm CMOS. IEEE J. Solid-State Circuits 45(6), 1111–1121 (2010). https://doi.org/10.1109/JSSC.2010.2048498

Z.M. Zhu, X. Yu, X.L. Song, VCM-based monotonic capacitor switching scheme for SAR ADC. Electron. Lett. 49(5), 327–329 (2013). https://doi.org/10.1049/e1.2012.3332

Acknowledgements

This work was supported by the National Natural Science Foundation of China (61804124), the Natural Science Basic Research Plan in Shaanxi Province of China (2021JQ-718).

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Appendix: Without Reset Energy Consumption of Eqs. (16)–(33)

Appendix: Without Reset Energy Consumption of Eqs. (16)–(33)

The reset energy consumption of the proposed Bi-level reference voltage capacitor switching structure is shown in the following mathematical derivation.

The value of the VFP2 voltage changed and the energy consumed by the voltage flip for this process is zero, as evidenced by the following equation:

The value of the voltage changes of VCP2 and the energy consumed by the voltage flip as shown in (19):

The value of the voltage changes of VFN2 and the energy consumed is:

The value of the voltage changes of VCN2 and the energy consumed by the voltage flip is proved and is calculated below:

Thus, the total energy consumption of the Bi-level reference voltage scheme is:

The reset energy consumption of the proposed Tri-level reference voltage capacitor switching structure is calculated by the following equation.

The value of the VFP2 voltage changed and the energy consumed by the voltage flip for this process is zero, as evidenced by the following mathematical derivation:

The value of the voltage changes of VCP2 and the energy consumed by the voltage flip is proved by the following equation:

The value of the voltage changes of VFN2 and the energy consumed by the voltage flipped is proved and calculated below:

The value of the voltage changes of VCN2 and the energy consumed by the voltage flipped is proved by the following expression:

The total energy consumption of the Tri-level-based voltage scheme is:

Conclusion: The proposed Bi-level reference voltages and Tri-level reference voltages have no reset energy consumption. The analysis shows that there is no switch to the ports of the capacitor array and the comparator and that the voltage of each capacitor on the bottom plate of the capacitor array is not consistent. This will exist to reset the energy consumption.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Dong, S., Liu, C., Bu, S. et al. A Bi/Tri-level Self-Adaptive Two-Step DAC Switching Scheme for High-Power Efficiency SAR-Based ADCs. Circuits Syst Signal Process 42, 4470–4505 (2023). https://doi.org/10.1007/s00034-023-02352-z

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-023-02352-z