Abstract

A high energy efficiency and linearity switching scheme is proposed for the successive approximation register (SAR) analog-to-digital converter (ADC). With the tri-level switching scheme, the capacitor area is reduced by 75% compared with the conventional switching scheme. In addition, the proposed switching scheme also combines the most significant bit (MSB) splitting method and the monotonic switching scheme for linearity and energy efficiency improvement. Furthermore, by inserting a connection switch between the MSB splitting capacitors and the least significant bit (LSB) capacitors, the reset energy can be avoided. The MATLAB simulation results show that compared to the monotonic switching scheme, the proposed switching scheme achieves a 93.29% reduction in average switching energy and 50% capacitor area saving without the reset energy when the parasitic capacitance is taken into consideration. Meanwhile, the linearity is enhanced by √2 × from the Monte Carlo simulation. The post-simulation results indicate that a 10-bit SAR ADC with the proposed switching scheme can achieve a signal-to-noise distortion ratio (SNDR) of 57.81 dB and a spurious-free dynamic range (SFDR) of 68.63 dB at the sampling rate of 1 MS/s in a 180-nm CMOS process. The SAR ADC consumes 15.25 μW power at a 1 V supply, resulting in a figure of merit (FoM) of 24.03 fJ/conv.-step. The active area of this ADC is only 0.057 mm2.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Recently, charge redistribution successive approximation register (SAR) analog-to-digital converter (ADC) has been a dominant implementation in biomedical electronics, wireless sensor networks, and wearable detection devices due to its low power consumption and digital-like structure [1, 9, 20, 24, 25]. The power consumption of the digital circuit is significantly diminished, but the switching energy of the capacitive digital-to-analog converter (DAC) array is still not satisfactory even in the advanced process.

Different switching schemes have been presented to reduce the switching energy [1, 4, 10, 14, 17, 19, 20, 24]. Compared with the conventional switching scheme, the methods based on Hybrid [4, 15], and Vcm-based-like scheme [18] dissipate the additional reset energy which occupies a dominant proportion of total switching energy, leading to the average switching energy reduction only to 89.47, 96.50, and 89.07%, respectively. Furthermore, the closed-loop charge recycling method presented in [7] realizes 100% switching energy reduction at the expense of the capacitor area. Tong [16] saves 75% area overhead with only √2 × INL performance enhancement. Besides, the switching energy reduction in [4] and [11] is also attenuated by 0.56 and 0.89% due to the parasitic capacitance, respectively. Overall, it is a challenge to meet the excellent energy efficiency and linearity performance requirement simultaneously when the reset energy and parasitic capacitance are taken into account.

To cope with the above-stated drawbacks, a novel switching scheme is proposed in this paper for the low-power SAR ADC. Taking advantage of the tri-level switching scheme, the capacitor area is decreased by 75% compared with the conventional switching scheme. Besides, the MSB capacitor splitting method and monotonic switching scheme are adopted to improve linearity and energy efficiency. In addition, the reset energy can be avoided by inserting a connection switch between the MSB splitting capacitors and the LSB capacitors. The behavioral simulation results indicate that compared to the monotonic switching method, the proposed switching scheme obtains a 93.29% reduction in average switching energy and 50% capacitor area saving with the parasitic capacitance consideration. The linearity performance has a √2 × improvement from the Monte Carlo simulation. The simulation results are aligned with the theoretical analysis. The post-simulation results show that an SNDR of 57.81 dB and an SFDR of 68.63 dB can be realized in a 10-bit SAR ADC with the proposed switching scheme at the sampling rate of 1 MS/s in a 180-nm CMOS process. The SAR ADC consumes 15.25 μW power at a 1 V supply, resulting in an FoM of 24.03 fJ/conv.-step. The active area of this ADC is only 0.057 mm2.

The organization of this paper is as follows. Section 2 presents the structure of the proposed switching scheme. Analysis and discussion about the switching scheme and a SAR ADC are demonstrated in Sect. 3. Section 4 gives the simulation results. Finally, the conclusion is drawn in Sect. 5.

2 The Proposed Switching Scheme

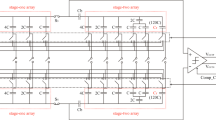

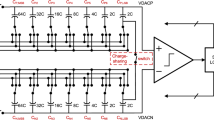

The SAR ADC with the proposed switching scheme in Fig. 1 consists of the sample-and-hold circuits (Sp1/Sn1 and Sp0/Sn0), the connection switches (Sp2 and Sn2), the capacitive DAC array (Cpm, Cpl, Cnm, Cnl), a comparator, and a dynamic SAR logic. For an N-bit conventional SAR ADC, 2 N flip-flops are required at least in SAR logic [16]. In this paper, the dynamic SAR control logic in [26] is adopted to reduce power and complexity. The MSB capacitor 128C is split into 8 capacitors (64, 32, 16, 8, 4, 2C, C, C), which have the identical binary form to the LSB capacitors. Cpl and Cnl are the LSB capacitors, and Cpm and Cnm are the MSB splitting capacitors.

Figure 2 shows the proposed switching scheme in a 4-bit capacitive DAC array. In the sampling phase, the MSB splitting capacitors and the LSB capacitors are separated by the connection switches Sp2/Sn2, and they sample the input signal through the switches Sp1/Sn1 and Sp0/Sn0, respectively. Meanwhile, the bottom plates of the Cpm/Cnm and Cpl/Cnl are connected to Vref and Vcm, respectively. After the sampling phase, the Sp2 and Sn2 are closed, and the MSB bit is obtained immediately. There is no energy consumption during the first comparison. Based on the MSB bit result, if Vip > Vin, Vip is decreased by Vref/2 through switching the bottom plate voltages of the Cpm and Cpl to Vcm and Gnd, respectively. Meanwhile, the voltage Vin remains unchanged. Or vice versa in the case of the Vip < Vin. There is still no energy consumption in this process because the voltage change on each capacitor is 0.

We take MSB bit = 1 as an example and suppose that the top plate voltage of the P-terminal capacitive DAC array is V1 and V2 before and after the second comparison, respectively, as shown in Fig. 3. According to the law of charge conservation, there is

thus, V2 = V1-Vcm can be obtained. During this conversion process, the reference voltage Vcm consumes the energy (E) as follows:

By doing this, the sub-MSB bit can be resolved. According to the sub-MSB bit result, if Vip > Vin, Vip is diminished by Vref/4 through switching the bottom plate voltage of the Cpm from Vcm to Gnd (Case: A) or from Vref to Vcm (Case: C), respectively. Otherwise, Vin is reduced by Vref/4 through converting the bottom plate voltage of the Cnm from Vref to Vcm (Case: B) or Vcm to Gnd (Case: D), respectively. The switching energy isn’t dissipated during the second conversion process due to the same magnitude and opposite polarity in voltage fluctuation of the MSB splitting capacitors and LSB capacitors. To generate the rest of the bits, only monotonic switching is required and only one capacitor’s bottom plate voltage is altered during each comparison until the rest of the bits are obtained. The proposed method is different from the method in [25], further reducing power consumption.

The contributions of the proposed switching scheme have been summarized in terms of power and linearity over other methods. Firstly, compared to the monotonic switching scheme in [9], the proposed switching scheme has the same common-mode voltage variation, but the linearity performance has a √2 × improvement. It achieves good linearity because the generation of the MSB bit and the sub-MSB bit doesn’t depend on the capacitor mismatch. The reference voltage of the capacitor bottom plate is not changed during the MSB bit generation and the voltage change on each capacitor is 0 during the sub-MSB bit generation. Secondly, the proposed switching scheme has higher energy efficiency than the monotonic switching scheme. Besides, compared to the switching scheme in [11], switching energy is increased by only 4.57CVref2 when the parasitic capacitance is taken into consideration. Thirdly, the tri-level switching scheme in [22] has the common-mode voltage variation from Vcm to VDD. Therefore, the noise and static offset of the comparator can become more and more severe because the common-mode voltage is gradually increased during the all-bits generation process. In the proposed switching scheme, this issue is solved and the average switching energy reduction has an obvious advantage over that of the tri-level switching scheme (96.89%). Finally, except for the splitting of the MSB capacitor and the inclusion of the connection switches, the switching scheme combining the tri-level and monotonic switching schemes in [11] has two common-mode voltage variation situations (from Vcm to VDD or Gnd) while the proposed switching scheme has a unique common-mode voltage variation situation (from Vcm to Gnd). Hence, it relaxes the design requirement of the dynamic comparator.

3 Analysis and Discussion

3.1 Common-Mode Voltage Variation

The dynamic comparator is indispensable for the SAR ADC design. The static offset voltage of the Strong-Arm comparator in Fig. 4 only can shrink the dynamic range while the dynamic offset caused by the common-mode voltage variation can worsen the linearity and bring in distortions. The common-mode voltage variation of the proposed switching scheme in the conversion process varies from the common-mode level (Vcm) to Gnd in the worst case from Fig. 5.

The operation process of the Strong-Arm comparator can be divided into a pre-amplification and a latch. The root mean square (RMS) of the input-referred offset Vos and the gain of pre-amplification (G) can be expressed as from [2].

where Cx and Co are the parasitic capacitances at Vx1,2 node and Voutp,n node, respectively.

From the (3) and (4), the gain of pre-amplification can be intensely influenced by the common-mode level, and it is increased with the decline of the common-mode level and the overdrive voltage of the input pair (M1/M2) during the conversion process. Thus, the RMS of latch offset voltage (σos,latch) can be attenuated, which optimizes the dynamic offset.

Figure 6a shows the variation of the comparator offset voltage with Vcm at a 1 V supply. The dynamic offset voltage is decreased with the reduction of Vcm. The behavioral model of a 10-bit SAR ADC is used to verify dynamic offset voltage variation sensitivity. Figure 6b delineates that the effective number of bits (ENOB) changes with the influence factor α, which is determined by the comparator dynamic offset.

3.2 Reset Energy

The most of the previous switching schemes only focused on the energy of the capacitive DAC array during the sampling phase and the conversion phase. In fact, the reset energy of many switching schemes is far greater than the switching energy of the conversion phase.

We suppose that the final state of the capacitive DAC array bottom plate is [V1, V2…Vn] and the initial state is [V0, V0…V0]. The voltage of the top plate is changed from VA to VB by reset operation. According to the law of charge conservation, we can get

It can be concluded from (5)

The expression of the reset energy is

By substituting (6) into (7), we can get

It can be concluded that if the initial voltages of the bottom plates are the same, there is no reset energy between two sampling cycles, which is independent of the final states of the bottom plates. However, the initial voltages of the bottom plates are different, which leads to nonzero reset energy. Therefore, the scheme shown in Fig. 7 is adopted to avoid the reset energy. After the LSB bit is obtained, the connection switches Sp2/Sn2 are turned off, and then the Cpm and Cpl are reset to Vref and Vcm in Fig. 7b, respectively. The analysis from (5) to (8) shows that the process doesn’t consume any energy. To avoid charge redistribution in this procedure, the Cpm and Cpl sample the input signal individually as shown in Fig. 7c. Once the sampling phase is completed, the connection switches Sp2/Sn2 are turned on and the conversion phase begins. This process is illustrated in Fig. 7d. It can be seen from the above analysis that the reset energy of the proposed switching scheme is zero.

3.3 Switching Energy

The average switching energy of the proposed switching scheme for an N-bit SAR ADC can be calculated as

According to (9), it can be calculated as only 10.54CV2ref, which achieves 99.23% and 95.87% average switching energy reduction over the conventional and monotonic schemes, respectively. Figure 8 displays the behavioral simulation of the switching energy (including reset energy) of the proposed switching scheme and other schemes for 10-bit SAR ADC. The proposed method has the lowest average switching energy.

3.4 Parasitic Capacitance Effect on Switching Energy

The parasitic capacitance is a major source of energy consumption. As shown in Fig. 9, when the reference voltage of the bottom plate is switched from [Vcm, Vcm, Gnd, Gnd] to [Vcm, Vcm, Vcm, Gnd], the switching energy of the ideal case is

Due to the existence of parasitic capacitance, the switching energy can be rewritten as:

By substituting (12) into (11), Eq. (11) can be calculated as:

where C, Cpt, and Cpb represent the unit capacitor, the top plate parasitic capacitance, and the bottom plate parasitic capacitance of the corresponding weight capacitor.

By comparing (10) and (13), it can be concluded that the switching energy is affected by the parasitic capacitance. The top plate parasitic capacitance reduces the switching energy in the down transition, while it increases the switching energy in the up transition. Besides, the bottom plate parasitic capacitance also consumes energy during charging. When the parasitic capacitance is considered, the energy of the proposed switching scheme and previous switching schemes is simulated in Fig. 10 with the assumption that Cpt = 10%Ctot (Ctot is the total capacitance) and Cpb = 15%C. The average switching energy of the proposed switching scheme is only 15.11CV2ref, which achieves a 99.10 and a 93.29% energy reduction over the conventional method and monotonic method, respectively. From Table 1, the proposed switching scheme has the highest energy efficiency and area reduction. Moreover, the increasing switching energy is the lowest (4.57CVref2) when parasitic capacitance is considered except for the monotonic switching scheme [9].

3.5 Parasitic Capacitance Effect on Gain Error

When the bottom plate voltage is switched from Gnd to Vcm in Fig. 9, the top plate voltage change of the capacitive DAC array is

Therefore, the gain error is obtained as:

Assuming that the ratio of parasitic capacitance to total capacitance is β = 0.1, the parasitic capacitance can be got as:

Therefore, the gain error can be expressed as:

Figure 11 shows that parasitic capacitance only causes the gain error, which doesn’t affect the linearity.

3.6 Linearity

It is unfair that some switching schemes ignore the linearity requirement in pursuit of low power. To improve energy efficiency and speed, the unit capacitance is expected to be as small as possible. However, the mismatch and the sampling noise limit the unit capacitance size. Therefore, the selection of the unit capacitance should trade off the switching energy, speed, linearity, and sampling noise. Ideally, the capacitors in each capacitive DAC array are binary weighted with Ci = 2iC, i = 0, 1… N-4.

To analyze the linearity of the proposed switching scheme, we assume that the capacitor mismatch obeys Gaussian distribution with the normal variance σ20, where σ0 represents the standard deviation of the unit capacitor. The variation of error related to capacitor Ci can be expressed as 2iσ20.

The generation of the MSB bit and sub-MSB bit is not affected by the capacitor mismatch. Thus, the worst case of INL and DNL occurs at 1/8Vref, 3/8Vref, 5/8Vref, and 7/8Vref, which means that the code transition happens at [00011…11] to [00100…00], [01011…11] to [01100…00], [10011…11] to [10100…00], and [11011…11] to [11100…00]. For a specific digital code, the analog output of DAC is:

where bi, bi,split, b0, b0,split are composed of Gnd, Vref, and Vcm. By neglecting the mismatch of the total capacitance, we can get the following results:

The linearity of the monotonic switching scheme can be analyzed with the above method. The RMS INL and RMS DNL can be calculated as follows:

Figure 12 presents the 500-run Monte Carlo simulation results of the proposed switching scheme and the monotonic switching scheme with unit capacitor mismatch of σ0/C = 1%. The RMS DNL and the RMS INL of the proposed switching scheme are only 0.152 LSB and 0.161 LSB, respectively. Therefore, the linearity is enhanced by √2 × over the monotonic switching scheme, which can match theoretical analysis. Table 2 compares the linearity of the proposed switching scheme with the other switching schemes. It can be concluded that the proposed switching scheme has the best linearity.

To meet the linearity requirement of N-bit ADC, according to the three-sigma law of normal distribution, there is

Combining (28) with (31), we can obtain

The capacitor mismatch model is

where C = KC × A, σ(∆C/C), A, Kσ, and KC stand for the standard deviation of the capacitor mismatch, the capacitor area, the matching coefficient, and the capacitance density parameter. There is

According to (32), (33), and (34), the unit capacitance can be expressed as

Besides the capacitor mismatch, the capacitance should also be designed to satisfy the sampling noise, which is generally smaller than the quantization noise (\(e_{{{\text{rms}}}}^{{2}}\)). The quantization noise power can be expressed as

where Δ = Vref/2 N, Vref represents the peak-to-peak voltage swing of the input signal.

The relationship between the sampling noise and the quantization noise can be expressed as

where k is the Boltzmann constant, T is the Kelvin temperature.

Through (36) and (37), the unit capacitance can be obtained.

The unit capacitance can be calculated as 5.21 fF with the sampling noise requirement, while it is 17.44 fF for the linearity requirement. Thus, the unit capacitance is selected as 17.44 fF in our design for 10-bit SAR ADC.

3.7 Sensitive to the V cm Variation

The dynamic performance of the ADC is affected by the accuracy of the reference voltage Vcm. To illustrate the impact of the reference voltage accuracy on the dynamic performance, Fig. 13 shows the FFT analysis after the 500-run Monte Carlo simulation of 10-bit SAR ADC with a Vcm mismatch range of 0–0.5%. Figure 13 illustrates that dynamic performance decreases as the Vcm mismatch increases. When the Vcm mismatch is 0.5%, the SFDR and SNDR are reduced by 7.87 and 3.34 dB, respectively. Fortunately, in the ADC measurement process, the reference voltage can be regulated by the off-chip low-dropout regulator (LDO).

3.8 Logical Complexity and Non-Ideal Factors

In the conversion process, except for the first three conversions, the other conversions adopt the monotonic switching scheme, and only the bottom plate voltage of one capacitor is changed in each conversion. Therefore, logical complexity is acceptable.

The connection switches Sp2 and Sn2 can bring non-ideal factors such as charge injection, clock feed-through, and clock jitter, which can deteriorate the total harmonic distortion (THD) and SNDR. The differential structure can suppress the non-ideal factors significantly [3, 21].

4 Simulation Results

4.1 MATLAB Simulation Results

To verify the influence of different noise sources and non-ideal factors, a 10-bit SAR ADC model is established in MATLAB. There are almost no spurs and harmonics in the ideal model from Fig. 14a. Hence, the SFDR has a high value while the SNDR is limited to 61.95 dB due to the intrinsic quantization noise. The SFDR is affected by spurs and harmonics, and the SNDR is affected by noise and harmonics. Compared to Fig. 14a, the SFDR remains nearly unchanged and the SNDR is decreased to 61.92 dB in Fig. 14b and 61.19 dB in Fig. 14c. When the capacitor mismatch (1%), Vcm mismatch (0.1%), and Vref mismatch (0.1%) are added to the ideal model further, the SFDR and SNDR are decreased to 78.46 and 60.65 dB, respectively.

Figure 15 also shows the SFDR and SNDR with different input signal frequencies at the sampling rate of 1 MS/s from the 500-run Monte Carlo simulation. Figure 15a, b, and c shows the ideal model, the model with kT/C noise, the model with kT/C and comparator noise, the SNDR is decreased because the kT/C and the comparator noise raise the noise floor. The SFDR is almost unchanged in Fig. 15a and b. Furthermore, the SFDR in Fig. 15c is significantly decreased because common-mode voltage variation brings in harmonics. In addition, the SFDR and SNDR are further decreased in Fig. 15d because of the distortions caused by the reference voltage mismatch and the capacitor mismatch. The results are also consistent with Fig. 14.

4.2 Post-simulation Results

The SAR ADC with the proposed switching scheme is designed in a 180-nm CMOS process at a 1 V supply. Figure 16 shows the SAR ADC layout, which occupies an active area of 0.057 mm2. The custom unit metal–oxide–metal (MOM) capacitor is 17.46 fF from the parasitic extraction and the single-side total capacitor is 4.47 pF. Figure 17 shows the power consumption of each block for the proposed SAR ADC. The total power is 15.25 μW, where the power of the S/H circuit, the comparator, the DAC array, and the digital circuit is 0.31, 2.35, 6.05, and 6.54 μW, respectively. Figure 18 shows the relationship between sampling rate and power consumption. It can be concluded that power consumption has a nearly linear relationship with the sampling rate.

The post-simulation results show that the comparator dynamic offset due to common-mode voltage variation and the capacitor mismatch affects the linearity. The SFDR, SNDR, and ENOB are 68.63, 57.81 dB, and 9.31 bit at the Nyquist input frequency in Fig. 19, respectively. Figure 20 presents the variation of the SNDR and SFDR with different input signal frequencies at the sampling rate of 1 MS/s. When the input signal frequency varies from low frequency to the Nyquist frequency, the SFDR is over 68.63 dB, and the SNDR is over 57.81 dB, which means that the ENOB is over 9.31 bit.

Table 3 summarizes the proposed SAR ADC performances and compares key metrics with several previous works. The FoM is defined as below [16]:

where fs is the sampling rate, and ENOB is the effective number of bits at the Nyquist input frequency. The proposed SAR ADC achieves an FoM of 24.03 fJ/conv.-step. It can be concluded that the proposed SAR ADC has a small active area and a competitive FoM.

5 Conclusion

The SAR ADC with the proposed switching scheme has been designed in a 180-nm CMOS process. Taking advantage of the tri-level scheme, the capacitor area is reduced by 75% compared to the conventional switching scheme. By combining the MSB splitting and monotonic switching schemes, linearity and energy efficiency are enhanced. Moreover, the connection switch between the MSB splitting capacitors and LSB capacitors avoids the reset energy. The average switching energy is 10.54CV2ref, which achieves a 99.23% reduction over the conventional switching scheme. The RMS DNL and RMS INL are only 0.152 LSB and 0.161 LSB, respectively. The post-simulation results show that the power consumption of the proposed SAR ADC is 15.25 μW, and the active area is 0.057 mm2 at the sampling rate of 1 MS/s. The SAR ADC with the proposed switching scheme can realize an SNDR of 57.81 dB and an FoM of 24.03 fJ/conv.-step at near Nyquist frequency, which is very suitable for low-power applications.

Data availability

Date sharing is not applicable to this article as no datasets were generated or analyzed during the current study.

References

S.U. Baek, K.Y. Lee, M. Lee, Energy-efficient switching scheme for SAR ADC using zero-energy dual capacitor switching. Analog Integr. Circ. Signal Process. 94(2), 317–322 (2018)

L Chen, A Sanyal, J Ma et al. (2016) Comparator common-mode variation effects analysis and its application in SAR ADCs. In: IEEE International symposium on circuits and systems (ISCAS), Montreal, pp. 2014–2017

T. Chen, J. Cai, X. Li et al., High-efficient two-step switching scheme for SAR ADC with dual-capacitive arrays and four-input comparator. Analog Integr. Circ. Signal Process. 101, 363–373 (2019)

A.R. Ghasemi, M. Saberi, R. Lotfi, A low-power capacitor switching scheme with low common-mode voltage variation for successive approximation ADC. Microelectron. J. 61, 15–20 (2017)

S. Hsieh, C. Hsieh, 0.4-V 13-bit 270-kS/s SAR-ISDM ADC with Opamp-Less Time-Domain integrator. IEEE J. Solid-State Circuits 54(6), 1648–1656 (2019)

M. Hu, J. Jin, Y. Guo et al., A power-efficient SAR ADC with optimized timing-redistribution asynchronous SAR logic in 40-nm CMOS. Circuits. Syst. Signal Process. 40, 3125–3142 (2021)

Y. Hu, A. Liu, B. Li, Z. Wu, Closed-loop charge recycling switching scheme for SAR ADC. Electron. Lett. 53(2), 66–68 (2016)

J. Lin, C. Hsieh, A 0.3-V 10-bit 1.17 f SAR ADC with merge and split switching in 90 nm CMOS. IEEE Trans. Circuits. Syst. I Regul. Pap. 62(1), 70–79 (2015)

C.C. Liu, S.J. Chang, G.Y. Huang, Y.Z. Lin, A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure. IEEE J. Solid-State Circuits. 45(4), 731–740 (2010)

S. Liu, H. Han, R. Ding, Z. Zhu, Energy-efficient switching scheme for SAR ADC with only two reference voltages. Analog Integr. Circ. Signal Process. 97(3), 603–613 (2018)

S. Liu, Y. Shen, Z. Zhu, A 12-Bit 10 MS/s SAR ADC with high linearity and energy-efficient switching. IEEE Trans. Circuits. Syst. I Regul. Pap. 63(10), 1616–1627 (2016)

J. Luo, Y. Liu, J. Li et al., A low voltage and low power 10-bit Non-Binary 2b/Cycle time and voltage based SAR ADC. IEEE Trans. Circuits. Syst. I Regul Pap. 67(4), 1136–1148 (2020)

Y. Shen, X. Tang, L. Shen et al., A 10-bit 120-MS/s SAR ADC with reference ripple cancellation technique. IEEE J. Solid-State. Circuits. 55(3), 680–692 (2020)

X. Tang, X. Yang, W. Zhao et al., 13.5-ENOB, 107-µW Noise-Shaping SAR ADC with PVT-Robust Closed-Loop dynamic amplifier. IEEE J. Solid-State. Circuits. 55(12), 3248–3258 (2020)

X. Tong, Y. Chen, Low-Power High-Linearity switching procedure for Charge-Redistribution SAR ADC. Circuits Syst. Signal Process. 36(9), 3825–3834 (2017)

X. Tong, M. Song, Y. Chen, S. Dong, A 10-Bit 120-kS/s SAR ADC without reset energy for biomedical electronics. Circuits Syst. Signal Process. 38(12), 5411–5425 (2019)

A. Wu, J. Wu, J. Huang, Energy-efficient switching scheme for ultra-low voltage SAR ADC. Analog Integr. Circ. Signal Process. 90(2), 507–511 (2017)

L. Xie, Y. Wang, J. Su et al., Switching scheme with 984% switching energy reduction and high accuracy for SAR ADCs. Analog Integr. Circ. Signal Process. 90(3), 681–686 (2017)

X. Xin, J. Cai, T. Chen, Q. Yang, A 04-V 10-bit 10-kS/s SAR ADC in 018-µm CMOS for low energy wireless senor network chip. Microelectron. J. 83, 104–116 (2019)

C. Yang, E. Olieman, A. Litjes et al., An area-efficient SAR ADC with mismatch error shaping technique achieving 102-dB SFDR 90.2-dB SNDR over 20-kHz bandwidth. IEEE Trans. Very Large Scale Integr. Syst. 29(8), 1575–1585 (2021)

W. Yu, S. Sen, B.H. Leung, Distortion analysis of MOS track-and-hold sampling mixers using time-varying Volterra series. IEEE Trans. Circuits Syst. II Express. Briefs. 46(2), 101–113 (1999)

C. Yuan, Y. Lam, Low-energy and area-efficient tri-level switching scheme for SAR ADC. Electron. Lett. 48(9), 482–483 (2012)

H. Zhang, H. Zhang, R. Zhang, Energy-efficient higher-side-reset-and-set switching scheme for SAR ADC. Electron. Lett. 53(18), 1238–1240 (2017)

Y. Zhang, Y. Li, Z. Zhu, A charge-sharing switching scheme for SAR ADCs in biomedical applications. Microelectron. J. 75, 128–136 (2018)

Y. Zhu, C.H. Chan, U.F. Chio et al., A 10-bit 100-MS/s reference-free SAR ADC in 90 nm CMOS. IEEE J. Solid-State Circuits. 45(6), 1111–1121 (2010)

Z. Zhu, Z. Qiu, M. Liu et al., A 6-to-10-bit 05 V-to-09 V reconfigurable 2 MS/s power scalable SAR ADC in 018-µm CMOS. IEEE Trans. Circuits Syst. I Regul. Pap. 62(3), 689–696 (2015)

Acknowledgements

This work was supported by the National Natural Science Foundation of China under Grant 62104193 and Grant 61674122.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Tong, X., Zhao, S. & Xin, X. High Energy Efficiency and Linearity Switching Scheme Without Reset Energy for SAR ADC. Circuits Syst Signal Process 41, 5872–5894 (2022). https://doi.org/10.1007/s00034-022-02038-y

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-022-02038-y