Abstract

This paper presents a new systematic design of a grounded memristor emulator circuit. It uses only one active device, namely an operational transconductance amplifier, and one passive element, namely a capacitor. Moreover, the used capacitor is grounded, which is suitable for monolithic integration. The proposed memristor is simple in design and can be used for both incremental and decremental memristor emulators by changing a switch positions. An application of the proposed grounded memristor as a first-order high-pass filter is also realized. Furthermore, the comparison of the proposed memristor emulator with available literature has been included. The proposed memristor emulator provides the following advantageous features such as low active and passive component counts, resistorless, grounded capacitor suitable for monolithic integration, low power consumption, and small area. The obtained results are included which are verified on Cadence Virtuoso at 180-nm Generic Process Design Kit CMOS technology parameter. The proposed emulator occupies the (76.94)·(33.75) µm2 layout area excluding the capacitor. The pre-layout and post-layout simulation results of the memristor emulator are also presented.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

In circuit theory, three basic elements, resistor, capacitor, and inductor, define the relationship between charge, voltage, current, and flux. In 1971, Leon O. Chua postulated the existence of a fourth fundamental two-terminal circuit element called a memristor, which defines the missing relation between charge and flux [1]. Memristors are useful for a wide range of applications, which include amplifier [2], digital logic [3], memory [4], neuromorphic computing [5], neural network [6, 7], synaptic circuit [8], chaotic circuits [9], and oscillators [10].

The first physical memristor was implemented in the HP laboratory in 2008, but unfortunately, this is not commercially available [11]. Over the years, researchers have developed a large number of memristor emulators using various analog building blocks (ABBs) [12,13,14,15,16,17,18,19,20,21,22,23,24,25,26,27,28,29,30,31,32,33], some of them are using commercially available ABBs [13, 15,16,17,18,19,20,21,22,23, 30, 33]. The different ABBs used for the realizations are: operational amplifier (OA) [13, 15], operational transconductance amplifier (OTA) [17, 18, 22, 28], current feedback operational amplifier (CFOA) [16, 19, 21], differential difference current conveyor (DDCC) [12, 14], second-generation current conveyor (CCII) [20, 23], current backward transconductance amplifier (CBTA) [24], current conveyor transconductance amplifier (CCTA) [25, 29], differential voltage current conveyor transconductance amplifier (DVCCTA) [26], voltage differential current conveyor (VDCC) [32], and voltage differencing transconductance amplifier (VDTA) [27, 30, 31, 33]. The critical review reveals that the reported circuits suffer from one or more of the following weaknesses: excessive use of the active components [12, 13, 15,16,17,18,19,20,21, 23, 28, 33], excessive use of passive components [12,13,14,15,16,17,18,19,20,21, 23,24,25,26,27, 29, 31, 33], use of multiplier which needs precise adjustment with high accuracy [13,14,15, 17, 18, 20, 22,23,24, 27, 33], use of passive floating components [13,14,15,16,17,18, 20, 21, 23,24,25,26, 29] which are not suitable for IC fabrication, use of passive resistor [12,13,14,15,16,17,18,19,20,21,22,23,24,25,26,27, 29, 31, 33], and use of MOS resistor [12, 31, 32]. Moreover, the memristor circuits [13, 15,16,17,18,19,20,21, 23] have been realized using bipolar technology. Due to the use of bipolar technology, the memristor emulators are strictly temperature dependent. Moreover, the internal structures of [14, 22, 24,25,26, 29] memristor emulators suffer from the excessive number of transistors and the complexity, which results in a high-silicon area in the case of on-chip fabrication. Furthermore, topologies [19, 29] used two different types of ABBs, which is not encouraged from an IC point of view.

The authors in this paper proposed a single-OTA-based memristor emulator that overcomes all the aforementioned drawbacks. The proposed memristor emulator uses only one OTA and one capacitor. The used capacitor is grounded and hence is suitable for IC fabrication. The design is simulated using Cadence Virtuoso software with 180-nm Generic Process Design Kit (GPDK) CMOS technology parameters. To check the functionality of the proposed memristor emulator, an application as first-order high-pass filter is also included. Simulation results show that the proposed circuit agrees well with the theory. The pre-layout and post-layout results are also included.

This article is organized as follows. In Sect. 2, the design of the proposed memristor emulator is described. The performance simulation of the proposed memristor emulator is discussed in Sect. 3. In Sect. 4, the application of the proposed circuit is discussed, followed by comparison in Sect. 5. The conclusion is given in Sect. 6.

2 Proposed grounded memristor emulator circuits

A memristor is a two-terminal electrical component. It limits or controls the flow of electrical current in a circuit and also remembers or recollects the amount of charge that has previously flowed through it. Memristors are important because they retain memory without power, and are non-volatile. A memristor is a semiconductor that joins a capacitor, resistor, and inductor to make a fourth new kind of element whose resistance is called memristance that varies as a function of current and flux. Memristors, a combination of “memory resistors,” are a kind of passive circuit element that maintains a relationship between the time integrals of current and voltage across a two-terminal element. When the current flows in one direction, the resistance increases; in contrast, when the current flows in the opposite direction, the resistance decreases. However, resistance cannot go below zero. When the current is stopped, the resistance remains in the value that it had previously [1,2,3,4].

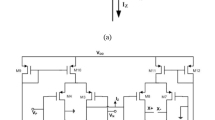

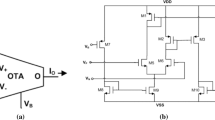

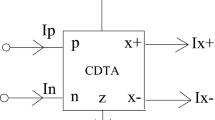

The operational transconductance amplifier (OTA) has a voltage input and a current output device. The symbol of double output OTA (DO-OTA) is shown in Fig. 1 [34], where Vin, IO+, IO−, VB are the differential input voltage, output current at positive terminal, output current at the negative terminal, and bias voltage, respectively.

The ideal transfer characteristics of an OTA for input Vin are expressed as

where \(g_{m}\), IO± and \(V_{{{\text{in}}}} = V_{{{\text{in}} + }} - V_{{{\text{in}} - }}\) are the transconductance, output current, and differential input voltage, respectively. Moreover, the \(V_{{{\text{in}} + }}\) and \(V_{{{\text{in}} - }}\) are the applied input voltages at the positive (p) and negative (n) terminals of the OTA, respectively.

The routine analysis results in the expression of \(g_{m}\) as

where \(k = \mu_{n} C_{{{\text{ox}}}} \frac{W}{L}\) is MOS device parameter and \(\mu_{n}\), \(C_{{{\text{ox}}}}\), W, L, and Vth are mobility, oxide capacitance, width, length, and the threshold voltage of the MOS transistor, respectively.

The proposed grounded memristor emulator is shown in Fig. 2. By interchanging the switch, it can perform the operation of an incremental- and decremental-type memristor emulator. If cross-coupled connected the terminal pins of the switch, i.e., pins P, Q, and R, S are interconnected (P–S and R–Q), an incremental-type memristor emulator is obtained shown in Table 1.

The input current (Iin), capacitor current (Ic), and bias voltage (VB) are obtained as

where \(\phi_{{{\text{in}}}} = \int {V_{{{\text{in}}}} \left( t \right){\text{d}}t}\) is the total flux obtained by the memristor. Putting the value of VB into (2), we get

Substituting (6) into (3), we get the input current expression as

Hence, the memconductance \(W\left( {\phi_{{\text{m}}} } \right)\) of the proposed incremental memristor is obtained as

Similarly, if we change the switch connections, i.e., pins P–Q and R–S changing the polarity of time-variant part of memconductance of (8), a decremental-type memristor emulator is obtained as

where gm is controllable by bias voltage VB, which makes the proposed emulator electronically tunable.

Equations (8) and (9) show that the proposed circuit works as incremental and decremental memristor emulators, respectively, where \(\frac{k}{\sqrt 2 }\left( {V_{{{\text{ss}}}} + 2V_{{{\text{th}}}} } \right)\) is the constant term and \(\frac{k}{\sqrt 2 }\left( {\frac{{g_{m} \phi_{{{\text{in}}}} }}{C}} \right)\) being the time-varying term as \(\phi_{{{\text{in}}}}\) is the function of time-varying input signals. For \(\phi_{{{\text{in}}}} = 0\), memconductance provides a constant value in both types of incremental and decremental emulators.

3 Simulation results

In this section, the proposed grounded memristor emulator of Fig. 2 using the CMOS structure of the DO-OTA [34] shown in Fig. 3 has been simulated. The aspect ratios of the transistors for Fig. 3 are given in Table 2. All transistors are in the saturation region. The supply voltages \(V_{{{\text{DD}}}} = - V_{{{\text{SS}}}} = 1.2\;{\text{V}}\) and bias voltage VB = 0.45 V are used for simulations, where VDD, VSS, and VB are positive supply voltage, negative supply voltage, and bias voltage, respectively. The DC transfer characteristics of Fig. 3 are shown in Fig. 4.

DC transfer characteristics of Fig. 3

Figure 5 shows the transient response of the grounded memristor emulator of Fig. 2. For transient analysis, a sinusoidal voltage signal of amplitude 1 V and frequency 1 MHz has been applied to the input terminal of the proposed emulator. Figure 6 shows the ac response in 20 dB of Fig. 2 with 0.5 V ac magnitude of the input DC voltage and VB = 0.45 V is applied.

Figure 7 is obtained when unit pulse voltage is applied for both incremental and decremental memristor emulators. The applied unit pulse voltage source value is taken as V1 = 0 V and V2 = 1 V. For a decremental graph, we select positive nodes of applied input unit pulse voltage and for an incremental graph, we select negative nodes of applied input unit pulse voltage. From Fig. 7, it can be observed that the current vs. time plot is increasing and decreasing with respect to the time interval for incremental and decremental topologies, respectively.

The various plot between current vs. time for unit pulse voltage for grounded memristor emulator at: a incremental topology with C = 100 nF, time period (tp) = 6 µs, pulse width (td) = 2 µs, b decremental topology with C = 100 nF, time period (tp) = 6 µs, pulse width (td) = 2 µs, c incremental topology with C = 20 nF, time period (tp) = 6 µs, pulse width (td) = 2 µs, d decremental topology with C = 20 nF, time period (tp) = 6 µs, pulse width (td) = 2 µs, e incremental topology with C = 5 nF, time period (tp) = 4 µs, pulse width (td) = 1.5 µs, f decremental topology with C = 5 nF, time period (tp) = 4 µs, pulse width (td) = 1.5 µs

The relation between the voltage–current of the proposed grounded memristor emulator is shown in Fig. 8. The input sinusoidal voltage is applied with 1 V amplitude and different frequencies such as 200 kHz, 300 kHz, 400 kHz, 500 kHz, and 1 MHz. The hysteresis loop is shown in Fig. 8a, b by the varying capacitor at a fixed value of frequency 400 kHz, the amplitude of input signal = 1 V. It is noted that by increasing of capacitor value the current through the memristor will be decreased. From Eq. (9), it is observed that current through the memristor is inversely proportional to the capacitance and its effect is observed on the V–I curve as expected. The hysteresis loop is shown in Fig. 8c by varying the frequency at a fixed value of capacitor is 250 pF and input sinusoidal voltage is applied with 1 V amplitude and different frequencies. The simulated results clearly show that the voltage–current relationship is very sensitive to the applied frequency of the input sinusoidal signal. Figure 8d shows the effect on hysteresis loop with temperature varying [− 40°, − 32°, 56°, 80°] at fixed value of frequency 1 MHz, capacitor value of C1 = 50 pF and amplitude of input signal = 1 V. The simulated results clearly show that the voltage–current relationship is very sensitive to the applied frequency of the input sinusoidal signal.

The important aspect when design moves toward the IC implementation is the process variation. The proposed grounded memristor is examined for the different processes like SS (slow N and slow P transistors), FS (fast N and slow P transistors), FF (fast N and fast P transistors), SF (slow N and fast P transistors), and NN (nominal N and nominal P transistors). Figure 9 shows the process variation at C = 300 pF and ƒ = 250 kHz with 1 V amplitude. It reveals that the current flow in the case of FF is greater than other processes.

The layout of the proposed memristor emulator is given in Fig. 10. The layout occupies (76.94 µm)·(33.75 µm) area excluding the capacitor. The average power consumption in the NN (normal n and normal p transistor) process of the proposed emulator is found to be 411.2 µW. The applied input signal is sinusoidal with an amplitude of 1 V, at a 1 MHz frequency. The capacitor value is chosen for 250 pF. The pre-layout and post-layout simulation results of the proposed memristor are shown in Fig. 11. The post-simulation is done after extracting the parasitic capacitance and resistance.

The layout of the proposed memristor emulator circuit in Fig. 2

4 Applications of proposed memristor emulator

In this section, two application examples are included to verify the functionality of the proposed memristor emulator: first, as a single and parallel configuration, and second as a first-order high-pass filter (HPF).

4.1 Different combinations of memristor emulator

To check the performance of the proposed OTA-based memristor emulator, it is connected in a parallel configuration and compares the obtained result with a single memristor. In a parallel configuration, the memristor value is half by the single memristor, then we said, the proposed circuit is working correctly. The single and parallel combination of the memristor is shown in Fig. 12. To check, through simulation applied a sinusoidal signal with an amplitude of 1 V with 250 kHz frequency. It can see that the proposed memristor emulator works properly as shown in Fig. 13. According to that parallel memristor emulator, the value of the memristor is halved by the single memristor.

4.2 First-order high-pass filter

In this section, the first-order passive high-pass filter (HPF) is compared with memristor emulator-based first-order HPF. Figure 14 shows the resistor–capacitor (RC) and proposed memristor–capacitor (MC)-based first-order high-pass filter (HPF), respectively. The values chosen for simulation are C = 10 pF, R = 13 MΩ for the cut of the frequency of 1.224 kHz. The frequency response of both the RC and MC-based filters is shown in Fig. 15. This shows that the proposed emulator works very well.

5 Comparison of proposed memristor emulator with other available in the literature

The detailed comparative analysis of the proposed circuit with existing memristor emulators available in the literature is given in Table 3.

It is concluded from Table 3 that

-

1.

The topologies [12,13,14,15,16,17,18,19,20,21,22,23,24, 27,28,29, 33] use two or more analog building blocks, whereas the proposed emulator uses only one OTA.

-

2.

The topologies [13,14,15, 17, 18, 20, 22,23,24, 27, 33] use the analog multiplier to obtain the nonlinear characteristics of the memristor emulator, and hence, circuits become complex and required precise adjustment with high accuracy. However, the proposed topology is designed without using multipliers.

-

3.

The topologies [13,14,15,16,17,18, 20, 21, 23,24,25,26, 29] use passive floating components, whereas the proposed emulator topology uses only grounded components that are suitable for the IC fabrication point of view.

-

4.

The reported memristor emulators in [12,13,14,15,16,17,18,19,20,21,22,23,24,25,26,27, 29, 32, 33] use resistors in the design, while the proposed topology is resistorless.

-

5.

The maximum operating frequency achieved by the topologies [12, 13, 15,16,17,18,19,20,21,22,23,24, 30, 33] is in the range of kHz, while the proposed design can operate up to 1 MHz.

-

6.

The topologies [13, 15,16,17,18,19,20,21, 23] have been realized using bipolar technology which is strictly temperature dependent, whereas the proposed emulator is MOS based.

-

7.

The topologies [19, 29] use two different types of ABBs, which is not encouraged from an IC point of view, whereas the proposed emulator uses only a single ABB.

-

8.

The topology [32] required more number of MOS transistors to implement ABB as compared to the proposed design that uses less transistors.

Therefore, based on the above discussion, it is concluded that the performance of the proposed memristor emulator is better than most of the designs available in the literature.

6 Conclusion

In this paper, we have proposed a new memristor emulator circuit using only one OTA as an active element and one grounded capacitor. The simple switching connection can be used to realize both the decremental and incremental types of memristor emulators. The proposed memristor emulator is simple and suitable for integrated circuit implementation. It provides the following advantageous features: (1) only one active component: OTA, (2) only one passive component: capacitor, (3) capacitor is grounded, which is suitable for monolithic integration, and (4) low power consumption. The pre-layout and post-layout simulation results of the proposed circuit are also included. All the theoretical concepts are verified using Cadence Virtuoso Analog Design Environment software with 180-nm generic process design kit (GPDK) technology parameters.

Data availability

All the data related to the research are included in the article. Any additional data required by any reader will be provided on request to the corresponding author.

References

Chua, L.: Memristor-the missing circuit element. IEEE Trans. Circuit Theory 18(5), 507–519 (1971)

Wey, T.A., Jemison, W.D.: Variable gain amplifier circuit using titanium dioxide memristors. IET Circuits Devices Syst. 5(1), 59–65 (2011)

Amirsoleimani, A., Ahmadi, M., Ahmadi, A.: Logic design on mirrored memristive crossbars. IEEE Trans. Circuits Syst. II Express Briefs 65(11), 1688–1692 (2017)

Pal, S., Gupta, V., Ki, W.H., Islam, A.: Design and development of memristor based RRAM. IET Circuits Devices Syst. 13(4), 548–557 (2019)

Jeong, Y., Lu, W.: Neuromorphic computing using memristor crossbar networks: a focus on bio-inspired approaches. IEEE Nanatechnol. Mag. 12(3), 6–18 (2018)

Zhang, Y., Wang, X., Friedman, E.G.: Memristor-based circuit design for multilayer neural networks. IEEE Trans. Circuits Syst. I Regul. Pap. 65(2), 677–686 (2017)

Dong, Z., Lai, C.S., He, Y., Qi, D., Duan, S.: Hybrid dual-complementary metal-oxide semiconductor/memristor synapse-based neural network with its applications in image super-resolution. IET Circuits Devices Syst. 13(8), 1241–1248 (2019)

Luo, L., Hu, X., Duan, S., Dong, Z., Wang, L.: Multiple memristor series-parallel connections with use in synaptic circuit design. IET Circuits Devices Syst. 11(2), 123–134 (2017)

Muthuswamy, B.: Implementing memristor based chaotic circuits. Int. J. Bifurc. Chaos 20(5), 1335–1350 (2010)

Zidan, M.A., Omran, H., Radwan, A.G., Salama, K.N.: Memristor-based reactance-less oscillator. Electron. Lett. 47(22), 1220–1221 (2011)

Strukov, D.B., Snider, G.S., Stewart, D.R., Williams, R.S.: The missing memristor found. Nature 453, 80–83 (2008)

Yener, S., Kuntman, H.: A new CMOS based memristor implementation. In: 2012 International Conference on Applied Electronics (IEEE-ICAE), pp. 345–348 (2012)

Kim, H., Sah, M.P., Yang, C., Cho, S., Chua, L.O.: Memristor emulator for memristor circuit applications. IEEE Trans. Circuits Syst. I Regul. Pap. 59(10), 2422–2431 (2012)

Yesil, A., Babacan, Y., Kaçar, F.: A new ddcc based memristor emulator circuit and its applications. Microelectron. J. 45(3), 282–287 (2014)

Sánchez López, C., Mendoza Lopez, J., Carrasco Aguilar, M., Muñiz Montero, C.: A floating analog memristor emulator circuit. IEEE Trans. Circuits Syst. II Express Briefs 61(5), 309–313 (2014)

Abuelma’atti, M.T., Khalifa, Z.J.: A new memristor emulator and its application in digital modulation. Analog Integr. Circuits Signal Process. 80(3), 577–584 (2014)

Kumngern, M., Moungnoul, P.: A memristor emulator circuit based on operational transconductance amplifiers. In: 2015 12th International Conference on Electrical Engineering/Electronics, Computer, Telecommunications and Information Technology (ECTI-CON) (IEEE), pp. 1–5 (2015)

Kumngern, M.: A floating memristor emulator circuit using operational transconductance amplifiers. In: 2015 IEEE International Conference on Electron Devices and Solid-State Circuits (EDSSC), (IEEE), pp. 679–682 (2015)

Abuelma’atti, M.T., Khalifa, Z.J.: A continuous-level memristor emulator and its application in a multivibrator circuit. AEU-Int. J. Electron. Commun. 69(4), 771–775 (2015)

Sánchez López, C., Carrasco Aguilar, M., Muñiz Montero, C.: A 16 Hz–160 kHz memristor emulator circuit. AEU-Int. J. Electron. Commun. 69(9), 1208–1219 (2015)

Abuelma’atti, M.T., Khalifa, Z.J.: A new floating memristor emulator and its application in frequency-to-voltage conversion. Analog Integr. Circuits Signal Process. 86(1), 141–147 (2016)

Babacan, Y., Yesil, A., Kacar, F.: Memristor emulator with tunable characteristic and its experimental results. AEU-Int. J. Electron. Commun. 81, 99–104 (2017)

Cam, Z.G., Sedef, H.: A new floating memristance simulator circuit based on second generation current conveyor. J. Circuits Syst. Comput. 26(02), 1750029 (2017)

Ayten, U.E., Minaei, S., Sagbas, M.: Memristor emulator circuits using single CBTA. AEU-Int. J. Electron. Commun. 82, 109–118 (2017)

Ranjan, R.K., Rani, N., Pal, R., Paul, S.K., Kanyal, G.: Single CCTA based high frequency floating and grounded type of incremental/decremental memristor emulator and its application. Microelectron. J. 60, 119–128 (2017)

Ranjan, R.K., Raj, N., Bhuwal, N., Khateb, F.: Single DVCCTA based high frequency incremental/decremental memristor emulator and its application. AEU-Int. J. Electron. Commun. 82, 177–190 (2017)

Petrovic, P.B.: Floating incremental/decremental flux-controlled memristor emulator circuit based on single VDTA. Analog Integr. Circuits Signal Process. 96(3), 417–433 (2018)

Kanyal, G., Kumar, P., Paul, S.K., Kumar, A.: Ota based high frequency tunable resistorless grounded and floating memristor emulators. AEU-Int. J. Electron. Commun. 92, 124–145 (2018)

Ranjan, R.K., Sagar, S., Roushan, S., Kumari, B., Rani, N., Khateb, F.: High- frequency floating memristor emulator and its experimental results. IET Circuits Devices Syst. 13(3), 292–302 (2018)

Yesil, A., Babacan, Y., Kaçar, F.: Design and experimental evolution of memristor with only one VDTA and one capacitor. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 38(6), 1123–1132 (2019)

Petrovic, P.B.: Tunable flux-controlled floating memristor emulator circuits. IET Circuits Devices Syst. 13(4), 479–486 (2019)

Yesil, A., Babacan, Y., Kacar, F.: Electronically tunable memristor based on VDCC. AEU-Int. J. Electron. Commun. 107, 282–290 (2019)

Pal, I., Kumar, V., Aishwarya, N., Nayak, A., Islam, A.: A VDTA-based robust electronically tunable memristor emulator circuit. Analog Integr. Circ. Sig. Process 104, 47–59 (2020)

Kumar, K., Nagar, B.C.: New tunable resistorless grounded meminductor emulator. J. Comput. Electron. 20(3), 1452–1460 (2021). https://doi.org/10.1007/s10825-021-01697-5

Acknowledgements

This work was performed at Integrated Circuits and System Design Lab of the Department of Electronics and Communication Engineering, National Institute of Technology Patna under the SMDP-C2SD program and is supported by the Ministry of Electronics and Information Technology (MeitY), Government of India.

Funding

No funding was received to assist with the preparation of this manuscript.

Author information

Authors and Affiliations

Contributions

All authors contributed to the study conception and design. Analysis, simulation, and post-layout were performed by KK. The draft and final version of the manuscript was written by BCN, and all authors read and approved the final manuscript.

Corresponding author

Ethics declarations

Conflict of interest

The authors have no conflict of interest to declare that are relevant to the content of this article.

Consent to participate

We agree to the terms and policies for the publication of the articles.

Consent for publication

We agree to the terms and policies for the publication of the articles.

Human and animal rights

Accepted principles of ethical and professional conduct have been followed. No human or animals participation is involved in the research.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Kumar, K., Nagar, B.C. & Pradhan, G. Single OTA-based tunable resistorless grounded memristor emulator and its application. J Comput Electron 22, 549–559 (2023). https://doi.org/10.1007/s10825-022-01955-0

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-022-01955-0