Abstract

The variability of switching parameters in redox-based resistive switching RAM (ReRAM) devices is investigated by a 3D kinetic Monte Carlo approach. This physics-based model can simulate the filamentary resistive switching in the electroforming, SET and RESET processes and captures their key features. It allows to predict the impact of the forming and switching conditions on the fluctuations of key parameters like the current and resistance levels of the cell in on and off states. The origin of the variability of the switching parameters was investigated in terms of the involved physical processes. The simulations also confirm the multilevel cell operation capabilities of ReRAM devices.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

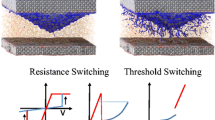

Among the current types of nonvolatile memories (NVM), ReRAM possesses unique features like CMOS compatibility, low-power consumption, promising scalability and a simple structure [1, 2]. These features make ReRAM a potential candidate for main memory applications of future computer systems, which also has the capability of performing logic and arithmetic operations beyond data storage and can accelerate neural network applications [3, 4].

Usually, a one-time process called electroforming is required for a virgin cell to create an oxygen-deficient conductive filament (CF) through the oxide sandwiched between two electrodes. The rupture and reconstruction of this filament later during the RESET and SET processes can modulate the cell resistance and switches the cell on and off. The on and off states are referred to here as low-resistance state (LRS) and high-resistance state (HRS) [5]. The switching between HRS and LRS causes fluctuations, because it is the result of stochastic processes happening during the switching cycles like oxygen vacancy (V\(_{\text {O}}^{\bullet \bullet }\)) generation, recombination and diffusion. This randomness causes a poor switching uniformity, which is one of the main obstacles for ReRAM to be mass produced and has been reported commonly in the literature [6,7,8]. The origin of these fluctuations is not fully understood yet, and further studies are needed to avoid the undesired fluctuations in future device designs.

The switching characteristics of ReRAM can be affected by different parameters related to the forming, SET and RESET processes like the current compliance or the applied SET and RESET voltages. This work studies the effect of some of these parameters on the device behaviour during the SET and RESET processes and the cycle-to-cycle variability of the switching characteristics. We have used a 3D KMC model that contains enough physical details and is yet computationally efficient to be able to compare our results to experimental data in the literature. All KMC models published so far on this topic [9,10,11,12] are based on the formation/annihilation of V\(_{\text {O}}^{\bullet \bullet }\)s in the bulk [13]. In our model, in contrast, the formation/annihilation of V\(_{\text {O}}^{\bullet \bullet }\)s can solely occur due to an oxygen exchange reaction at one of the electrodes [14]. The model applies to all filamentary switching VCM cells with one interface allowing for an oxygen exchange reaction and the other one blocking any oxygen exchange reaction. The activation barriers for the oxygen exchange reaction depend on the specific material stack. For a HfO\(_2\)/Hf interface, for example, it was shown by DFT simulation that the extraction of oxygen from the oxide to the Hf metal requires a lower barrier than the reverse operation [15]. This study does not investigate the extraction at grain boundaries or defects of the Hf metal. In this situation, the barriers might be different. The main goal of this work is to put this KMC model in practice to study the switching kinetics and the cycle to cycle variability. With our KMC code that tracks the movement of individual V\(_{\text {O}}^{\bullet \bullet }\) inside the oxide, we can precisely explain the origin of fluctuations and some abnormal behaviour in the switching processes.

2 Model description and simulation results

We have developed a robust KMC-based model to simulate the behaviour of ReRAM devices. The creation and recombination of V\(_{\text {O}}^{\bullet \bullet }\) in this model can solely happen along the electrode–oxide interface. During the forming and SET processes, V\(_{\text {O}}^{\bullet \bullet }\)s migrate in the direction of the applied electric field from the anode towards the cathode creating the CF. Other details of this physics-based model can be found in [14]. The simulations were run on a computer with the following features: model name: Intel(R) Xeon(R) CPU E5-2690 v3 @ 2.60GHz, cpu cores: 12. The simulation time of a forming process followed by a RESET and a SET in a cell with size of \(5\times 5\times 5\) nm\(^3\) takes in average 1 h. The choice of cell size is based on having a reasonable computational time for studying the switching variability. The number of treated particles, depending on the process, can change from 4 V\(_{\text {O}}^{\bullet \bullet }\)s, which are the initial number of V\(_{\text {O}}^{\bullet \bullet }\) distributed at the beginning of the forming process, to more than 150 V\(_{\text {O}}^{\bullet \bullet }\)s. The characteristic vibration frequency of V\(_{\text {O}}^{\bullet \bullet }\) which determine the order of time steps in the KMC method is considered \(7\times 10^{13}\)Hz. The spacing between adjacent V\(_{\text {O}}^{\bullet \bullet }\) sites is 0.5 nm. This lattice spacing is refined by factor two to solve the physical equations numerically. Similar to [14] the parameters used to model the resistive switching fit to a structure with electrodes showing the same metal work function, e.g. TiN/HfO\(_2\)/Ti.

The model presented in [14] was reused in this work by a small modification in electron hopping rates to affect the conduction mechanism change. The smooth transition between trap-assisted tunnelling (TAT) and Drift model is achieved by choosing higher electron hopping rates between traps in TAT models than the rates between traps and electrodes [16].

Figure 1 shows the simulated \(I-V\) characteristics for one forming process and a couple of switching cycles under an applied ramped voltage. The voltages in the forming, SET and RESET processes are ramped with sweep rates of 0.25 V/s, 1.5 V/s and − 1.5 V/s, respectively. The simulated \(I-V\) curve shows great stability and almost follows the normal expected features of resistive switching in ReRAM cells including an abrupt SET process and a gradual RESET process [17]. The abrupt changes in some RESET cycles are due to the conduction mechanism change between Drift and TAT. The criteria for this transition are the number of V\(_{\text {O}}^{\bullet \bullet }\)s. The small size of the simulated cell can also lead to an abrupt current change even during a single conduction mechanism, since the dissolution of even one layer of the CF can alter the tunnelling gap significantly. In this simulation, a current compliance (\(I_{\text {C}}\)) of 100 \(\upmu\)A is applied during the forming and SET processes. \(I_{\text {C}}\) is the maximum current allowed during the filament formation to avoid irreversible physical damage to the dielectric. In practice, a current limiter is used to force the cell current to the value of \(I_{\text {C}}\) [18]. Depending on the response speed of the current limiter to the rapid increase of leakage current at the end of the filament formation and transition from HRS to LRS, a current overshoot might happen [18,19,20]. Figure 2 shows the \(I-V\) characteristics of the first RESET after the forming process with the same initial conditions for three cases: with no overshoot and overshoot with two different RC time constants, \(t_{\text {OS}} = 100\) ns and \(t_{\text {OS}} = 1000\) ns. The comparison of the V\(_{\text {O}}^{\bullet \bullet }\) distribution at the end of the forming process for no overshoot and the overshoot with \(t_{\text {OS}} = 100\) ns shows that during the overshoot due to the high current and temperature, a considerable number of V\(_{\text {O}}^{\bullet \bullet }\) are generated and the filament continues to grow, which causes a higher maximum current during the RESET process.

Simulated \(I-V\) characteristics including the first RESET process after the forming step with the same initial conditions for \(t_{\text {OS}} = 0\), \(t_{\text {OS}} = 100\) ns and \(t_{\text {OS}} = 1000\) ns. The shape of the filament at the end of the forming process is shown for \(t_{\text {OS}} = 0\), \(t_{\text {OS}} = 100\) ns (Color figure online)

For the values considered for the generation barrier of V\(_{\text {O}}^{\bullet \bullet }\) at the electrode–oxide interface and V\(_{\text {O}}^{\bullet \bullet }\) diffusion barrier inside the oxide (i.e. \(E_{\text {diffusion}} = 0.9\) eV and \(E_{\text {generation}} = 1.6\) eV), the evolution of the CF proceeds from the top electrode (in this work a positive voltage is applied to the top electrode during the forming and SET processes and a negative voltage during the RESET process) to the bottom electrode (always grounded) as shown in Fig. 3 consistent with simulation results [14, 21] and experimental observations [22, 23].

Evolution of the CF during the forming process at different stages of the applied voltage, \(V_A = 0.5\) V, \(V_B = 1.85\) V, \(V_C = 1.95\) V and \(V_D = 2.0\) V. Stage D corresponds to the completion of the forming process, where the CF connects the top and bottom electrodes and the leakage current reaches to the current compliance level

3 Variability of the switching parameters

Figure 4 shows the simulated dependency of the SET time on the sweep rate. The definition of the SET time in this study is the time, at which \(I = I_{\text {C}}\). The simulation was carried out for 50 switching cycles for every sweep rate. For all sweep rates, the initial conditions of the forming process are the same and the applied voltages during forming and RESET are ramped with rates of 0.25 V/s and − 1.5 V/s, respectively. The probability distributions of the SET times for different values of the voltage sweep rate are shown in Fig. 4a. The mean value of the SET time as a function of the sweep rate is also shown in Fig. 4b. The average value of the SET time decreases with increasing sweep rate, while the variance in the SET time distribution increases.

The SET time variability was also studied in the pulse voltage mode. The distribution of the SET time for different values of the SET pulse amplitude, which was simulated for 50 switching cycles, and the average value of the SET time are shown in Fig. 5a, b. A fixed SET pulse amplitude, \(V_{\text {SET}} = -\,1\) V with a pulse duration of 0.5 s and the same forming conditions are applied in all cases. The results show that the SET time decreases about five orders of magnitude when doubling the applied SET voltage amplitude [24]. This high nonlinearity comes from the reduction of V\(_{\text {O}}^{\bullet \bullet }\) diffusion barrier in the oxide during the SET process. The V\(_{\text {O}}^{\bullet \bullet }\) diffusion barrier reduction is affected by the external applied voltage, the potential induced by the space charge inside the oxide and the local temperature.

The high leakage current during the RESET process can be an obstacle for the practical usage of ReRAMs. Therefore, it is important to pay attention to the factors affecting the maximum current, \(I_{\text {RESET}}\), during the RESET process. A well-known parameter that allows to control \(I_{\text {RESET}}\) is the current compliance, \(I_{\text {C}}\), the maximum allowed current during the forming and SET processes [1, 25]. Figure 6a demonstrates the switching \(I-V\) characteristics for different values of \(I_{\text {C}}\). The dependency of \(I_{\text {RESET}}\) on \(I_{\text {C}}\) can be seen from this graph, where by increasing \(I_{\text {C}}\) from 10 to \(100 \upmu\)A, \(I_{\text {RESET}}\) also scales up. The higher \(I_{\text {C}}\) results in a conductive filament (CF) with higher V\(_{\text {O}}^{\bullet \bullet }\) density at the end of the forming and SET processes as shown in Fig. 6b. The smaller \(I_{\text {C}}\) corresponds to a lower V\(_{\text {O}}^{\bullet \bullet }\) concentration and higher resistance, resulting in a less stable CF, where the generation or rearrangement of a few V\(_{\text {O}}^{\bullet \bullet }\)s can result in a considerable current change; hence, higher variability from one cycle to another is expected (Fig. 7). A denser CF during the RESET process before switching to HRS causes a better electron conduction and a higher \(I_{\text {RESET}}\). The probability distribution of \(I_{\text {RESET}}\) for different values of \(I_{\text {C}}\) during 50 switching cycles is shown in Fig. 8a. It shows more variance in the \(I_{\text {RESET}}\) distribution for higher \(I_{\text {C}}\). The value of \(I_{\text {RESET}}\) strongly depends on the shape of the CF after the forming and SET processes. Higher \(I_{\text {C}}\) results in a CF with higher number of V\(_{\text {O}}^{\bullet \bullet }\)s, which during the RESET process can fluctuate more in and out of the filament and consequently cause higher variance in the RESET current. Figure 8b shows the evolution of the average value of \(I_{\text {RESET}}\) as a function of \(I_{\text {C}}\) confirming the idea of scaling down \(I_{\text {RESET}}\) by limiting the \(I_{\text {C}}\). The measured LRS resistance and \(I_{\text {RESET}}\) as a function of \(I_{\text {C}}\) for various ReRAM materials in [26, 27] confirm the trends shown in Figs. 7 and 8.

The RESET process ends when a predefined RESET stop voltage is reached. The choice of this value has a great effect on the switching properties of ReRAM devices. Figure 9 shows the \(I-V\) characteristics for different RESET stop voltages applied in ramped mode. Every switching loop in this figure started with the same CF. Changing the RESET stop voltage (\(V_{\text {RESET}}\)) from \(-\,1.1\) to \(-\,1.5\) V results in a stronger dissolution of the CF as shown in Fig. 10 and consequently a reduction of the current. Figure 10 shows a 2D view along the filament at the end of the forming process (\(V_{\text {applied}} = V_{\text {form}} = 2\) V), where a CF connects the top and the bottom electrode. The 2D view along the filament is also shown at two different values of the \(V_{\text {RESET}}\) (\(V_{\text {applied}} = V_{\text {RESET}} = -\,1.1\) V and \(-\,1.5\) V). Clearly, the higher absolute value of the \(V_{\text {RESET}}\) causes a larger tunnelling gap between the tip of the filament and the electrode, which reduces the tunnelling current [28]. The distributions of the RESET currents (the current at the applied voltage equal to \(V_{\text {RESET}}\)) for 50 switching cycles are shown in Fig. 11a. The average value and the relative standard deviation of current for each voltage as a function of \(V_{\text {RESET}}\) are shown in Fig. 11b for better analysis. The average value and the relative deviation of the RESET current decrease with increasing \(V_{\text {RESET}}\). This trend was also observed in experiments [7, 27]. The reduction of the average RESET current with increasing \(V_{\text {RESET}}\) is expected because of the growing tunnelling gap. With increasing \(V_{\text {RESET}}\), the RESET current level reaches a stable plateau with only a little of fluctuation. For lower \(V_{\text {RESET}}\) the gap between the tip of the CF and the electrode, which can be quite different from cycle to cycle, is smaller. Therefore, any V\(_{\text {O}}^{\bullet \bullet }\) fluctuation in this area can cause a huge current fluctuation. Figure 11c shows the distribution of the LRS and HRS resistances for different values of \(V_{\text {RESET}}\). In contrary to the HRS resistance, the LRS resistance shows almost no dependency on \(V_{\text {RESET}}\). Application of a larger \(V_{\text {RESET}}\) creates a wider gap with higher resistivity within the CF, resulting in a larger HRS resistance. The variation of the HRS resistance is slightly higher for smaller values of \(V_{\text {RESET}}\). Generally, as shown in Fig. 11c, the resistance fluctuation in the HRS is higher than in the LRS and the resistance window between the LRS and HRS increases with increasing \(V_{\text {RESET}}\).

The shape of the filament at different applied voltages, \(V = V_{\text {form}} = 2\) V, where the creation of the filament is completed and the ReRAM has switched to LRS, \(V = V_{\text {RESET}} = -\,1.1\) V, shows the partially dissolved filament at the end of the RESET process. Filament has been dissolved even more at higher \(V_{\text {RESET}} = -\,1.5\) V. \(V_{\text {form}}\) and \(V_{\text {RESET}}\) were applied to the bottom electrode

a Cumulative distribution of the leakage current at the end of the RESET process, where \(V_{\mathrm{applied}} = V_{\mathrm{RESET}}\) for different values of \(V_{\mathrm{RESET}}\) for 50 switching cycles; b mean value and relative standard deviation of the RESET current; c cumulative distribution of the LRS and HRS resistance for different values of \(V_{\mathrm{RESET}}\) (Color figure online)

MLC operation of ReRAM necessary for high density memory application is achieved by controlling the LRS and HRS resistance states. Modulating the LRS resistance by the SET current compliance and the HRS resistance by the RESET stop voltage is a common property of ReRAM devices and is reported for many materials [29, 30]. This multilevel resistance state distributions are captured by the simulations presented in Figs. 7, 11c.

4 Conclusion

In this work, a physical model, which can successfully simulate the forming process and a large number of switching cycles in a ReRAM, was used to study the switching kinetics and fluctuations of key parameters, such as the LRS and HRS resistance and the maximum RESET current. The effect of different forming and switching conditions on the switching kinetics and variability was investigated using KMC model to validate the observations made in experiments. This paper provides insight into the physical source of the high nonlinearity in the switching kinetics and switching parameter variation phenomenon. MLC operation of ReRAM was reproduced by the introduced simulator. The efficient and stable KMC simulator can be used to study other performance metrics like switching endurance and retention and also the size effect on the variability, which are topics of our future work.

References

Nardi, F., Ielmini, D., Cagli, C., Spiga, S., Fanciulli, M., Goux, L., Wouters, D.J.: Control of filament size and reduction of reset current below 10 µA in NiO resistance switching memories. Solid-State Electron. 58(1), 42–47 (2011)

Celano, U., Fantini, A., Degraeve, R., Jurczak, M., Goux, L., Vandervorst, W.: Scalability of valence change memory: from devices to tip-induced filaments. AIP Adv. 6(1), 085009 (2016)

Chi, P., Li, S., Xu, C., Zhang, T., Zhao, J., Liu, Y., Wang, Y., Xie, Y.: PRIME: a novel processing-in-memory architecture for neural network computation in ReRAM-based main memory. In: 2016 ACM/IEEE 43rd Annual International Symposium on Computer Architecture (ISCA), pp. 27–39 (2016)

Long, Y., Na, T., Mukhopadhyay, S.: ReRAM-based processing-in-memory architecture for recurrent neural network acceleration. IEEE Trans. Very Large Scale Integr. VLSI Syst. 26(12), 2781–2794 (2018)

Waser, R., Dittmann, R., Staikov, G., Szot, K.: Redox-based resistive switching memories - nanoionic mechanisms, prospects, and challenges. Adv. Mater. 21(25–26), 2632–2663 (2009)

Yu, S., Guan, X., Wong, H.-P.: On the switching parameter variation of metal oxide RRAM-part II: model corroboration and device design strategy. IEEE Trans. Electron Devices 59(4), 1183–1188 (2012)

Balatti, S., Ambrogio, S., Wang, Z., Sills, S., Calderoni, A., Ramaswamy, N., Ielmini, D.: Pulsed cycling operation and endurance failure of metal–oxide resistive (RRAM). In: 2014 IEEE International Electron Devices Meeting, pp. 14.3.1–14.3.4 (2014)

Ielmini, D.: Resistive switching memories based on metal oxides: mechanisms, reliability and scaling. Semicond. Sci. Technol. 31(6), 063002 (2016)

Guan, X., Yu, S., Wong, H.-S.P.: On the switching parameter variation of metal-oxide RRAM: part I: physical modeling and simulation methodology. IEEE Trans. Electron Devices 59(4), 1172–1182 (2012)

Padovani, A., Larcher, L., Pirrotta, O., Vandelli, L., Bersuker, G.: Microscopic modeling of HfO\(_x\) RRAM operations: from forming to switching. IEEE Trans. Electron Devices 62(6), 1998–2006 (2015)

Larcher, L., Padovani, A., Pirrotta, O., Vandelli, L., Bersuker, G.: Microscopic understanding and modeling of HfO\(_2\) RRAM device physics. In: 2012 International Electron Devices Meeting, pp. 20.1.1–20.1.4 (2012)

Makarov, A., Sverdlov, V., Selberherr, S.: Stochastic modeling of bipolar resistive switching in metal-oxide based memory by Monte Carlo technique. J. Comput. Electron. 9(3), 146–152 (2010)

Bradley, S.R., Shluger, A.L., Bersuker, G.: Electron-injection-assisted generation of oxygen vacancies in monoclinic HfO\(_{2}\). Phys. Rev. Appl. 4, 064008 (2015)

Abbaspour, E., Menzel, S., Hardtdegen, A., Hoffmann-Eifert, S., Jungemann, C.: KMC simulation of the electroforming, set and reset processes in redox-based resistive switching devices. IEEE Trans. Nanotechnol. 17(6), 1181–1188 (2018)

O’Hara, A., Bersuker, G., Demkov, A.A.: Assessing hafnium on hafnia as an oxygen getter. J. Appl. Phys. 115(18), 183703 (2014)

Gao, B., Sun, B., Zhang, H., Liu, L., Liu, X., Han, R., Kang, J., Yu, B.: Unified physical model of bipolar oxide-based resistive switching memory. IEEE Electron Device Lett. 30(12), 1326–1328 (2009)

Lee, M.-J., Lee, C.B., Lee, D., Lee, S.R., Chang, M., Hur, J.H., Kim, Y.-B., Kim, C.-J., Seo, D.H., Seo, S., Chung, U.-I., Yoo, I.-K., Kim, K.: A fast, high-endurance and scalable non-volatile memory device made from asymmetric Ta\(_2\)O\(_{5-x}\)/TaO\(_{2-x}\) bilayer structures. Nat. Mater. 10, 625–630 (2011)

Kinoshita, K., Tsunoda, K., Sato, Y., Noshiro, H., Yagaki, S., Aoki, M., Sugiyama, Y.: Reduction in the reset current in a resistive random access memory consisting of NiOx brought about by reducing a parasitic capacitance. Appl. Phys. Lett. 93, 033506 (2008)

Song, J., Lee, D., Woo, J., Koo, Y., Cha, E., Lee, S., Park, J., Moon, K., Misha, S.H., Prakash, A., Hwang, H.: Effects of RESET current overshoot and resistance state on reliability of RRAM. IEEE Electron Device Lett. 35(6), 636–638 (2014)

Yu, S., Guan, X., Wong, H.-P.: Understanding metal oxide RRAM current overshoot and reliability using Kinetic Monte Carlo simulation. In: 2012 International Electron Devices Meeting, pp. 26.1.1–26.1.4 (2012)

Marchewka, A., Waser, R., Menzel, S.: Physical modeling of the electroforming process in resistive-switching devices (talk). In: 2017 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD) (2017)

Yalon, E., Karpov, I., Karpov, V., Riess, I., Kalaev, D., Ritter, D.: Detection of the insulating gap and conductive filament growth direction in resistive memories. Nanoscale 7(37), 15434–15441 (2015)

Yang, Y., Gao, P., Li, L., Pan, X., Tappertzhofen, S., Choi, S., Waser, R., Valov, T., Lu, W.D.: Electrochemical dynamics of nanoscale metallic inclusions in dielectrics. Nat. Commun. 5, 4232 (2014)

Menzel, S., Böttger, U., Wimmer, M., Salinga, M.: Physics of the switching kinetics in resistive memories. Adv. Funct. Mater. 25(40), 6306–6325 (2015)

Seo, S., Lee, M.J., Seo, D.H., Jeoung, E.J., Suh, D.-S., Joung, Y.S., Yoo, I.K., Hwang, I.R., Kim, S.H., Byun, I.S., Kim, J.-S., Choi, J.S., Park, B.H.: Reproducible resistance switching in polycrystalline NiO films. Appl. Phys. Lett. 85(23), 5655–5657 (2004)

Ielmini, D.: Modeling the universal set/reset characteristics of bipolar RRAM by field- and temperature-driven filament growth. IEEE Trans. Electron Devices 58(12), 4309–4317 (2011)

Balatti, S., Ambrogio, S., Wang, Z.-Q., Sills, S., Calderoni, A., Ramaswamy N., Ielmini, D.: Understanding pulsed-cycling variability and endurance in HfOx RRAM. In: 2015 IEEE International Reliability Physics Symposium, Monterey, CA, pp. 5B.3.1–5B.3.6 (2015)

Kim, W., Menzel, S., Wouters, D.J., Guo, Y., Robertson, J., Roesgen, B., Waser, R., Rana, V.: Impact of oxygen exchange reaction at the ohmic interface in Ta2O5-based ReRAM devices. Nanoscale 8(41), 17774–17781 (2016)

Yu, S., Wu, Y., Wong, H.-S.P.: Investigating the switching dynamics and multilevel capability of bipolar metal oxide resistive switching memory. Appl. Phys. Lett. 98(10), 103514 (2011)

Goux, L., Chen, Y.-Y., Pantisano, L., Wang, X.-P., Groeseneken, G., Jurczak, M., Wouters, D.J.: On the gradual unipolar and bipolar resistive switching of TiN/HfO\(_2\)/Pt memory systems. Electrochem. Solid-State Lett. 13(6), G54–G56 (2010)

Acknowledgements

This work was supported by the Deutsche Forschungsgemeinschaft under Grant SFB 917.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Abbaspour, E., Menzel, S. & Jungemann, C. Studying the switching variability in redox-based resistive switching devices. J Comput Electron 19, 1426–1432 (2020). https://doi.org/10.1007/s10825-020-01537-y

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-020-01537-y