Abstract

One of the emerging technology that can be used for replacing CMOS technology is Quantum-dot Cellular Automata (QCA) technology. Counter circuits are widely used circuits in the design of digital circuits. This paper presents and evaluates circuits for 2-, 3-, 4-, and 5-bit coplanar counter in the QCA technology. The designed QCA coplanar counter circuits are based on the modified D-Flip-Flop (D-FF) circuit that is designed in this paper. The designed QCA circuits are implemented and verified by using QCADesigner tool version 2.0.3. The results show that the designed circuits for 2-, 3-, 4-, and 5-bit coplanar counter contain 44 (0.03 μm2), 93 (0.07 μm2), 160 (0.13 μm2), and 245 (0.2 μm2) quantum cells (area). The comparison results indicate that the designed circuits have advantages compared to other QCA circuits in terms of cost, area, and cell count.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

The typical technologies such as CMOS technology are faced with serious challenges such as short cannel effect [1, 2] and high fault tolerance at nano-scale [3]. Carbon-Nano-Tube Field Effect Transistors (CNTFETs), Spintronics, Silicon On Insulator (SOI) MOSFET and Quantum-dot Cellular Automata (QCA) are considered as replaced technologies [3,4,5,6,7,8,9,10,11,12,13,14]. The QCA technology is an emerging technology designed as an appropriate alternative to CMOS technology [7].

In the QCA technology, data is transmitted through polarization based on binary information encoding in quantum dot cells [9]. In recent years, many arithmetic circuits such as counter circuits [15,16,17,18,19,20,21,22,23], flip-flop circuits [15, 17,18,19, 22, 23], shift register circuits [24], full-adder circuits [25,26,27,28,29,30,31], multiplexer circuits [32, 33], switched network circuits [34], number generator circuits [35] and Cellular comparator circuits [36, 37] have been designed in the QCA technology.

One of the most used circuits in arithmetic circuits is the counter circuit. Kong et al. [15] have developed a 5-bit QCA counter circuit. This designed QCA counter circuit consists of 490 cells and 0.7992 μm2area.The authors of [16] have designed a 3-bit QCA counter circuit. This designed QCA counter circuit consists of 238 cells and 0.36 μm2 area. Aghababa et al. [17] have designed a 4-bit QCA counter circuit that consists of 232 cells and 0.20 μm2 area. Sarmadi et al. [18] have developed a 4-bit QCA counter circuit. This designed QCA counter circuit consists of 183 cells and 0.24 μm2 area. Angizi et al. [19] have presented a 4-bit QCA counter circuit, which consists of 422 cells and 0.46 μm2 area. Sheikhfaal et al. [20] have designed a 3-bit QCA counter circuit. This designed QCA counter circuit consists of 428 cells and 0.48 μm2 area. Sangsefidi et al. [21] have proposed a 4-bit QCA counter circuit. This designed QCA counter circuit consists of 273 cells and 0.26 μm2 area. Abutaleb [22] has designed a 3-bit QCA counter circuit. This designed QCA counter circuit consists of 196 cells and 0.22 μm2 area. Yang et al. [23] have designed a 3-bit QCA counter circuit. This designed QCA counter circuit consists of 616 cells and 1.2 μm2 area.

A common method to design a QCA counter circuit is mapping the circuits from CMOS technology to the QCA technology. Developing a building block circuit based on the QCA Flip-Flops (FFs) plays an important role in this method [19].

In this paper, new circuits are designed for implementation of 2-, 3-, 4- and 5-bit QCA counter circuits. First, an efficient modified D-FF circuit is designed and then the 2-, 3-, 4- and 5-bit QCA counter circuits are designed using this modified D-FF circuit as building block. The designed counters are implemented in one layer. The functionality of the designed circuits are verified using QCADesigner tool version 2.0.3.The simulation results indicate that the designed modified D-FF circuit consists of 13 quantum cells and 0.01 μm2 area. The 2-, 3-, 4-, and 5-bit QCA counter circuits contain 44 (0.03 μm2), 93 (0.07 μm2), 160 (0.13 μm2), and 245 (0.2 μm2) quantum cells (area). The comparison indicate that the designed circuits for the QCA counter have better performance compared to other QCA counter circuits in terms of cell count and area.

The rest of the paper is as follows: Section 2 provides a background of the QCA technology. Section 3 provides a general overview of the D-FF circuits and counter circuits in the QCA technology. In section 4, the designed circuits are presented. In section 5, the implementation results of the designed circuits are presented and evaluated. Finally, the paper is concluded in section 6.

2 Background

2.1 Cells in the QCA Technology

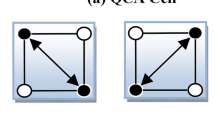

Cells in the QCA technology include four cavities located in the square corners. These cells have two electrons, which can freely move in the cavities and create two stable states [38]. These electrons are arranged in the diagonal manner. As a result, two poles of +1 (logic “1”) and − 1 (logic “0”) are created. Figure 1 shows these two stable states [24, 38].

Polarization of the cells is calculated as follows [16, 38]:

Where Pi denotes the electric charge at ith point. Binary information is displayed using these electrons position in logical cells [9].

2.2 Gates in the QCA Technology

The basic QCA logic gates include the inverter gate and majority gate. Several types of inverter and majority gates are shown in Fig. 2 [9, 39, 40].

The output of the inverter gate is the inverse of the input [9, 24]. In addition, the three-input majority gate consists of at least five QCA cells [9, 39,40,41]. The output of the three-input majority gate is computed as follows [24]:

3 Flip-Flop and Counter

3.1 Flip-Flop

The sequential circuits, which have two stable states output and can store at least one bit, are called flip-flops. Flip-flops can be categorized in 4 groups: T-FF, JK-FF, RS-FF and D-FF [35]. The D-FF is used as a register cell. It is because the D-FF can save its input data and shows this data in output after each clock cycle. The truth table for the D-FF is illustrated in Table 1 [42].

It should be noted that if the inverse of the D-FF output is used as the D-FF input, it can be used as a semi-oscillator circuit [17].

3.2 Counter

The counters are a class of sequential logics that are implemented using register-type circuits such as Flip-Flops. Counters can be categorized in several groups such as: asynchronous (ripple) counters, synchronous counters, cascaded counters and modulus counters [17]. The counter circuit plays an important role in the arithmetic circuits. As a result, several attempts have been done to implement efficient counter circuits especially in the QCA technology, which will be considered in the next section.

3.3 Previous QCA Counter Circuits

Figure 3 shows the previous designed counter [15,16,17,18,19, 21,22,23].

Yang et al. [23] have proposed a 3-bit synchronous counter that is illustrated in Fig. 3a. This designed counter consists of 616 cells and 1.2 μm2 area. The authors of [16] have designed 3-bit synchronous counter, which is illustrated in Fig. 3b. This design consists of 238 cells and 0.36 μm2 area. Aghababa et al. [17] have developed a 4-bit counter that is illustrated in Fig. 3c. This designed counter consists of 232 cells and 0.20 μm2 area. Sarmadi et al. [18] have presented a 4-bit QCA counter, which is shown in Fig. 3d. This designed counter consists of 183 cells and 0.24 μm2 area. Angizi et al. [19] have presented a 4-bit counter that is illustrated in Fig. 3e. This designed counter consists of 422 cells and 0.46 μm2 area. Sangsefidi et al. [21] have developed 4-bit QCA synchronous counter, which is illustrated in Fig. 3f. This counter consists of 273 cells and 0.26 μm2 area. The author of [22] have designed a 3-bit cascading three level-sensitive D-FFs, which is illustrated in Fig. 3g. This design consists of 196 cells and 0.22 μm2 area. Kong et al. [15] have developed a 5-bit QCA counter that is illustrated in Fig. 3h. This designed counter consists of 490 cells and 0.7992 μm2 area.

4 The Designed Circuits

In this section, we propose novel QCA circuits for the counter. The designed QCA counter circuits are based on the modified D-FF circuit that is developed in this paper.

4.1 The Modified D-FF Circuit

Figure 4 shows the designed modified D-FF circuit.

The designed modified D-FF circuit has an input and an output, which are shown by clock and out1, respectively. The designed circuit is composed of a new D-FF in which the inverse of the D-FF output is utilized as D-FF input. It contains 13 quantum cells and 0.01 μm2 area. This modified D-FF circuit is used as the building block for design of QCA counter circuits.

4.2 The Designed Counter Circuit

Figure 5 shows the designed circuit for 2-bit QCA counter.

The designed 2-bit QCA counter circuit has clock input and two outputs, out1 and out2. The designed circuit for the 2-bit QCA counter has 44 quantum cells and 0.03 μm2 area.

It should be noted that this counter can be easily extended to n-bit QCA counter. Figures 6, 7 and 8 shows the designed circuits for 3-, 4-, and 5-bit QCA counter based on designed modified D-FF circuit, respectively. These designed circuits have clock input and n outputs, out1, out2, out3, …, and outn corresponding to the n-bit counter circuits.

The designed circuits for the 3-, 4-, and 5-bit QCA counter have 93 (0.07 μm2), 160 (0.13 μm2) and 245 (0.20 μm2) quantum cells (area), respectively.

5 The Simulation Results and Comparison

The QCADesigner tool version 2.0.3 is used to verify the functionality of the designed QCA circuits. The utilized parameters for the simulation is shown in Table 2.

5.1 The Modified D-FF Circuit

Figure 9 shows the simulation results of the modified D-FF circuit.

Figures 10, 11, 12 and 13 show the simulation results of the designed 2-, 3-, 4-, and 5-bit QCA counter circuits.

The simulation results indicate that the outputs of the designed QCA counter circuits are correctly obtained. Table 3 shows the simulation results of the designed QCA counter circuits compared with other counter circuits in [15,16,17,18,19,20,21,22,23]. The cost is computed using Eq. (3) [30]:

Based on the simulation results that are summarized in Table 3, the cell count, area and cost of the designed 2-bit QCA counter circuit are considerably improved compared to 2-bit QCA counter circuits in [15, 16, 19,20,21,22,23]. The only 2-bit QCA counter circuit that has the same cost compared to the developed 2-bit QCA counter circuit is the 2-bit QCA counter circuit in [21]. However, the area and cell count in this circuit are about 2 and 1.7 times bigger than the designed 2-bit QCA counter circuit.

Moreover, the cost, cell count, and area of the designed 3-bit QCA counter circuit are considerably improved compared to 3-bit QCA counter circuits in [15, 16, 19,20,21,22,23].

In addition, the cell count, area and cost of the designed 4-bit QCA counter circuit are considerably improved compared to 4-bit QCA counter circuits in [15,16,17,18,19,20,21, 23]. The only 4-bit QCA counter circuit that has a slightly better cost than the designed 4-bit QCA counter circuit is the 4-bit QCA counter circuit of [19]. However, the area and cell count in this circuit are about 3.5 and 2.6 times bigger than the designed 4-bit QCA counter circuit. In addition, the only 4-bit QCA counter circuit that has the same cost compared to the designed 4-bit QCA counter circuit is the 4-bit QCA counter circuit in [21]. However, the area and cell count in this circuit are about 2 and 1.7 times bigger than the designed 4-bit QCA counter circuit.

For 5-bit QCA counter circuit, the cell count, area and cost of the designed QCA counter circuit are considerably improved compared to QCA counter circuit in [15].

6 Conclusion

In the QCA circuits design, counters are the most used circuits. In this paper, 2-, 3-, 4- and 5-bit coplanar counter circuits were designed based on the modified QCA D-FF circuit designed in this paper. In the modified D-FF circuit, the inverse of the D-FF output was used as D-FF input. The designed circuits were simulated and verified by using the QCADesigner tool version 2.0.3. The developed coplanar counter circuits for the 2-, 3-, 4-, and 5-bit QCA counter have 44 (0.03 μm2), 93 (0.07 μm2), 160 (0.13 μm2), and 245 (0.20 μm2) quantum cells (area), respectively. The comparison results demonstrate that the designed QCA counter circuits have improvements compared with other counter circuits in [15,16,17,18,19,20,21,22,23] in terms of cell count, and area.

References

Sharma, V.K., Pattanaik, M., Raj, B.: INDEP approach for leakage reduction in nano scale CMOS circuits. Int. J. Electronics. 102(2), 200–215 (2015)

Chaudhry, A., Kumar, M.J.: Controlling short-channel effects in deep-submicron SOI MOSFETs for improved reliability. IEEE Trans. Device Mater. Reliab. 4(1), 99–109 (2004)

Anvarifard, M.K.: An accurate compact model to extract the important physical parameters of an experimental nano scale short-channel SOI MOSFET. J. Comput. Electron. 1–7 (2019)

Karimi, A., Rezai, A.: Improved device performance in CNTFET using genetic algorithm. ECS J. Solid State Science and Technology. 6(1), 9–12 (2017)

Bakshi, U. and A. Godse.: The Depletion Mode MOSFET. Electronic Circuits (2007)

Sen, B., Mukherjee, R., Mohit, K., Sikdar, B.K.: Design of reliable universal QCA logic in the presence of cell deposition defect. Int. J. Electron. 104(8), 1285–1297 (2017)

Lent, C.S., Tougaw, P.D., Porod, W., Bernstein, G.H.: Quantum cellular automata. Nanotechnology. 4(1), 49–57 (1993)

Anvarifard, M.K.: Modeling a double-halo-doping carbon nanotube FET in DC and AC operations. ECS J. Solid State Sci. Technol. 7(12), 209–216 (2018)

Liu W. W., O’Neill, M., Earl, E.: Quantum-dot Cellular Automata. 11–44 (2013)

Seminario, J.M., Derosa, P.A., Cordova, L.E., Bozard, B.H.: A molecular device operating at terahertz frequencies: theoretical simulations. IEEE Trans. Nanotechnol. 3(1), 215–218 (2004)

Mehrad, M., Zareiee, M., Orouji, A.A.: Controlled kink effect in a novel high-voltage LDMOS transistor by creating local minimum in energy band diagram. IEEE Trans. Electron Devices. 64(10), 4213–4218 (2017)

Zareiee, M.: High performance nano device with reduced short channel effects in high temperature applications. ECS J. Solid State Science and Technology. 6(7), 75–78 (2017)

Mortaza Shafizadeh, M., Rezai, A.: Improved device performance in a CNTFET using La22O33high-κκ dielectrics. J. Comput. Electron. 16(2), 221–227 (2017)

Karimi, A., Rezai, A.: A design methodology to optimize the device performance in CNTFET. ECS J. Solid State Science and Technology. 6(8), 97–102 (2017)

Kong, K., Shang, Y., Lu, R.: Counter designs in quantum-dot cellular automata. IEEE International Conference on Nanotechnology (IEEE-NANO), pp. 1130–1134. (2010)

Angizi, S., Moaiyeri, M.H., Farrokhi, S., Navi, K., Bagherzadeh, N.: Designing quantum-dot cellular automata counters with energy consumption analysis. Microprocess. Microsyst. 39(7), 512–520 (2015)

Aghababa, H., Yazdinejad, M. H., Afzali, A., Forouzandeh, B.: Simplified quantum-dot cellular automata implementation of counters. IEEE International Caribbean Conference Devices, Circuits and Systems (ICCDCS), pp. 1–4. (2008)

Sarmadi, S., Azimi, S., Sheikhfaal, S., Angizi, S.: Designing counter using inherent capability of quantum-dot cellular automata loops. Int. J. Modern Education and Computer Science. 7(9), 22–28 (2015)

Angizi, S., Sayedsalehi, S., Roohi, A., Bagherzadeh, N., Navi, K.: Design and verification of new n-bit quantum-dot synchronous counters using majority function-based JK flip-flops. J. Circuits, Systems and Computers. 24(10), 15501531–15501517 (2015)

Sheikhfaal, S., Navi, K., Angizi, S., Navin, A.H.: Designing high speed sequential circuits by quantum-dot cellular automata: memory cell and counter study. Quantum Matter. 4(2), 190–197 (2015)

Sangsefidi, M., Abedi, D., Yoosefi, E., Karimpour, M.: High speed and low cost synchronous counter design in quantum-dot cellular automata. Microelectron. J. 73, 1–11 (2018)

Abutaleb, M.: Robust and efficient quantum-dot cellular automata synchronous counters. Microelectron. J. 61, 6–14 (2017)

Yang, X., Cai, L., Zhao, X., Zhang, N.: Design and simulation of sequential circuits in quantum-dot cellular automata: falling edge-triggered flip-flop and counter study. Microelectron. J. 41(1), 56–63 (2010)

Divshali, M.N., Rezai, A., Karimi, A.: Towards multilayer QCA SISO shift register based on efficient D-FF. Int. J. Theor. Phys. 57(11), 1–14 (2018)

Adelnia, Y., Rezai, A.: A novel adder circuit design in quantum-dot cellular automata technology. Int. J. Theor. Phys. 58(1), 184–200 (2019)

Roshany, H.R., Rezai, A.: Novel efficient circuit design for multilayer QCA RCA. Int. J. Theor. Phys. 58(6), 1745–1757 (2019)

Mokhtari, D., Rezai, A., Rashidi, H., Rabiei, F., Karimi, A.: Design of novel efficient full adder circuit for quantum-dot cellular automata technology. Electron.Energ. 31(2), 279–285 (2018)

Arani, I.E., Rezai, A.: Novel circuit design of serial–parallel multiplier in quantum-dot cellular automata technology. J. Comput. Electron. 17(4), 1771–1779 (2018)

Balali, M., Rezai, A., Balali, H., Rabiei, F., Emadi, S.: Towards coplanar quantum-dot cellular automata adders based on efficient three-input XOR gate. Results phys. 7, 1389–1395 (2017)

Rashidi, H., Rezai, A.: High-performance full adder architecture in quantum-dot cellular automata. J. Engineering. 1(1), 394–402 (2017)

Balali, M., Rezai, A.: Design of low-Complexity and High-Speed Coplanar Four-bit Ripple Carry Adder in QCA technology. Int. J. Theor. Phys. 57(7), 1948–1960 (2018)

Rashidi, H., Rezai, A., Soltany, S.: High-performance multiplexer architecture for quantum-dot cellular automata. J. Comput. Electron. 15(3), 968–981 (2016)

Rashidi, H., Rezai, A.: Design of novel efficient multiplexer architecture for quantum-dot cellular automata. J. Nano- Electron. Phys. 9(1), 1012–1011 (2017)

Das, J.C., De, D.: Circuit switching with quantum-dot cellular automata. Nano Commun. Networks. 14, 16–28 (2017)

Abutaleb, M.: A novel true random number generator based on QCA nano computing. Nano Commun. Networks. 17, 14–20 (2018)

Shiri, A., Rezai, A., Mahmoodian, H.: Design of efficient coplanar 1-bit comparator circuit in QCA technology. FACTA UNIVERSITATIS Series: Electron. Energ. 32(1), 119–128 (2019)

Mokhtarii, R., Rezai, A.: Investigation and Design of Novel Comparator in quantum-dot cellular automata technology. J. Nano, Electr, Phys. 10(5), 05014–1 - 05014-4 (2018)

Sridharan, K., Pudi, V.: Design of arithmetic circuits in quantum dot cellular automata nanotechnology. (2015)

Balali, M., Rezai, A., Balali, H., Rabiei, F., Emadi, S.: A novel design of 5-input majority gate in quantum-dot cellular automata technology. In: IEEE Symposium on Computer Applications & Industrial Electronics (ISCAIE), pp. 13–16 (2017)

Kassa, S.R., Nagaria, R.K., Karthik, R.: Energy efficient neoteric design of a 3-input majority gate with its implementation and physical proof in quantum dot cellular automata. Nano Communication Networks. 15, 28–40 (2018)

Bahar, A., Waheed S., Habib, M.: A novel presentation of reversible logic gate in quantum-dot cellular automata (QCA). In: IEEE International Conference on Electrical Engineering and Information & Communication Technology (ICEEICT), pp. 1–6, (2014)

Mano, M., Kime C. R., Martin, T.: Logic and Computer Design Fundamentals, USA: Pearson Education International. (2004)

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Niknezhad Divshali, M., Rezai, A. & Falahieh Hamidpour, S.S. Design of Novel Coplanar Counter Circuit in Quantum Dot Cellular Automata Technology. Int J Theor Phys 58, 2677–2691 (2019). https://doi.org/10.1007/s10773-019-04158-9

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10773-019-04158-9