Abstract

Quantum-dot Cell Automata (QCA) technology is a promising alternative technology for CMOS technology. In this technology, the ultra-dense and low-latency digital circuits are designed. One of the important digital circuits is Full Adder (FA). In this paper, a new and efficient multilayer QCA full adder circuit is designed and evaluated. In the designed full adder circuit, sum and carry output are designed in separated layers. Then, a novel and efficient 4-bit Ripple Carry Adder (RCA) circuit is designed based on this new FA circuit. The proposed QCA circuits are simulated using QCADesigner tool version 2.0.3. The simulation results show that the proposed 4-bit QCA RCA requires 135 QCA cells, 0.06 μm2 area and 5 clock phases. The comparison shows that the proposed QCA circuits have advantages compared to other QCA circuits in terms of area, latency, and cost.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

The CMOS technology as the dominant technology for VLSI has faced with limitations at nano-scale such as short channel effects [1]. So, alternative technologies such as Silicon On Insulator (SOI) [2,3,4,5,6,7,8], Carbon NanoTube Field Effect Transistors (CNTFETs) [9,10,11,12,13], molecular devices [14], single electron transistors [15], Spintronics [16] and Quantum-dot Cellular Automata (QCA) [17,18,19] are proposed for circuits design at nano-scale.

The QCA technology could be one of the alternatives for the CMOS technology [20]. Recently, the QCA arithmetic and logical circuits design are in the focal point of the researcher interests. Many logical gates and circuits such as Full Adder (FA) circuits [21, 22], multiplier circuits [23, 24], shift register circuits [25, 26], comparator circuits [27, 28] and multiplexer circuits [29, 30] have been designed in the QCA technology. Full adder circuit is one of the important elements in digital circuits. It plays a vital role in computing and arithmetic circuits such as ALUs and microprocessors [23].

Many of QCA full adders have designed using three 3-input majority gates and two inverter gates in one layer [31,32,33,34,35,36,37,38]. Some of these designs have been implemented without the use of wire crossing [39]. A few numbers of designs have used one lesser inverter gate for implementing QCA FAs in single layer [40] and multilayer [41, 42] wire-crossing layouts. The 5-input majority gate (MG5) has also been utilized for designing QCA FAs [22, 31, 43,44,45,46,47,48,49,50,51,52,53,54,55]: coplanar [43,44,45,46,47,48,49,50] and multilayer [22, 31, 51,52,53,54,55] QCA FAs. Some designers have realized QCA FAs using 3-input XOR gate. They have implemented their circuits in QCA coplanar [17, 56,57,58] and QCA multilayer [59, 60].

In this paper, we propose a novel and efficient QCA full adder circuit in multilayer. The sum output is designed by using one efficient QCA XOR gate. The carry output is also designed by using one efficient 3-input majority gate. Then, we propose an efficient 4-bit Ripple Carry Adder (RCA) circuit using the proposed full adder circuit. The proposed circuits are simulated using QCADesigner tool version 2.0.3 [61]. The simulation results demonstrate that the proposed circuits work correctly. The comparison shows that the proposed QCA circuits have advantages compared to other QCA circuits in term of area, latency, and cost.

The rest of this paper is organized as follows. In Section 2, an overview of the QCA technology is presented. In Section 3, previously reported designs are presented. In Section 4, the proposed new efficient 1-bit full adder and 4-bit QCA RCA are presented. Section 5 shows simulation results and compares proposed circuits to other QCA circuits. Finally, Section 6 concludes the paper.

2 Background

2.1 Quantum Cells

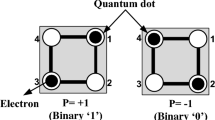

The normal QCA cell is usually constructed in a square form that has four quantum-dots in its corners. Generally, two electrons are injected in each cell, which are placed diagonally because of columbic repulsion [62, 63]. So, there are two stable states for replacing the electrons in dots that result in equalization to a binary system that are shown in Fig. 1 [63].

Normal QCA cell [63]

Unlike traditional structures, the position of electrons in the dots is based of binary logic instead of the voltage level in the QCA cells. It should be noted that two diagonal stable states of electrons in the QCA cell give two polarization states P = −1 and P = +1 which are equivalent to logic “0” and “1”, respectively [64]. The polarization P is computed from Eq. (1).

Where pi denotes the polarization of ith dot. At the time of applying clock signal, electrons can move between dots by tunneling because of lowering level of potential barriers. The cells are constructed in such a way that they are isolated from each other and tunneling between dots of adjacent cells cannot be happened [20].

2.2 QCA Clocking

QCA clocking is different to CMOS clocking. The QCA clock is utilized to control and synchronize signals. Furthermore, there aren’t power lines in the QCA technology. The QCA cells set to four clock phases named switch, hold, release, and relax phases. Actually, clock signals change potential barrier of tunneling between dots and control electron mobility in the tunnel. Therefore, the cell polarizations will be controllable. As a result, the cell gets four states: polarization, fixed polarization, depolarization and keep depolarized in mentioned clock phases, respectively. Clock phases and signal propagation direction are illustrated in Fig. 2.

Clock phases of cells and signal propagation in a wire [65]

2.3 QCA Gates

Three primitive and important gates in the QCA technology are Inverter Gate (IG), Majority Vote Gate (MVG or MG) and XOR gate. In Fig. 3, the layouts of some IGs are illustrated [66].

Various types of IG gates [66]

The MG is an important gate to digital circuits design in the QCA technology. The MG works according to the superposition of inputs. In Fig. 4, two common layouts of 3-input MGs are depicted [67].

Two types of 3-input majority gates; (a) original, (b) rotated [67]

The logical function of 3-input majority gate is defined by Eq. (2).

The 2-input AND (AND2) and OR (OR2) gates are obtained by fixing polarization of one input of MG3 to −1 and + 1, respectively [67].

Another important QCA gate is 3-input XOR gate (XOR3). Figure 5 shows the layout of the QCA 3-input XOR gate [56].

The utilized 3-input XOR gate in [56]

3 QCA Full Adder

3.1 Circuit Theory

The outputs of the QCA full adder can be computed as follows [31,32,33,34,35,36,37,38,39]:

Figure 6 shows the QCA block diagram for the implementation of this full adder circuit.

In addition, the output of the full adder can be computed as follows [40,41,42]:

Figure 7 shows the QCA block diagram for the implementation of this full adder circuit.

Moreover, the sum output can be computed as follows [22, 43,44,45,46,47,48,49,50, 52,53,54,55]:

Figure 8 shows the QCA block diagram for the implementation of this full adder circuit [22, 43,44,45,46,47,48,49,50,51,52,53,54,55].

Recently, by using the advantage of 3-input QCA XOR gate, designing of QCA FAs has become more optimum and has facilitated by using only two gates (i.e. XOR3 and MG3) [21, 56,57,58,59,60, 68]. In this method, despite using a minimum number of gates, the main issue is how to interconnect inputs of two gates to each other in coplanar approach. It is because accessing to inputs become more restricted for using the FA in the larger QCA circuits.

3.2 Previous QCA Full Adder Layouts Design

In this section, the previous multilayer QCA full adders are reviewed.

Figure 9 shows the utilized FA in [51] that is based on block diagram that is shown in Fig. 8. It constructed of 51 cells in 0.03 μm2 effective area on three layers. It has 3 clock phases delay.

The layout of the QCA FA in [51]

Figure 10 shows the layout of the designed full adder in [53]. This design uses 52 QCA cells, 3 clock phases and 0.04 μm2 area in three layers.

The layout of the FA in [53]

Figure 11 illustrates the layout of the QCA FA design in [54]. The cell count, area and delay of this design are 31 cells, 0.01 μm2, and 2 clock phases, respectively.

The layout of the FA in [54]

Figure 12 shows two layouts of the designed full adders by Navi et al. in [22, 52]. The first layout that is illustrated in Fig. 12a has 73 cells, 0.04 μm2 area, and 3 clock phases delay. The second layout that is illustrated in Fig. 12b has 61 QCA cells, 3 clock phases, and 0.03 μm2 area.

Another design has realized in [55] that is shown in Fig. 13. This designed FA has 22 QCA cells, 3 clock phases, and 0.01 μm2 area. In this layout, accessing to output cells is impossible unless using extra layers.

Three layers of the designed FA in [55]

It is noticeable that the reviewed designs in Figs. 10, 11, 12 and 13 are designed according to block diagram that is shown in Fig. 8.

Figure 14 shows the three-dimensional view of the utilized QCA FA circuit in [67]. This design consists of 23 cells, 3 clock phases, and 0.01 μm2 area in three layers.

The layout of the designed FA in [67]

In addition, it is feasible to place XOR3 and MG3 gates on two separated layers using the multilayer approach. In these designed circuits, accessing to the inputs and outputs for using the FA in larger circuits become more facilitated.

In this way, Safoev et al. [59, 60] has proposed efficient FA in three layers that uses only 31 cells as shown in Fig. 15. The latency of this design is 2 clock phases, and the required area is 0.02μm2.

4 The Proposed Circuits

4.1 The Proposed QCA Full Adder

As described in [18], where two beside input signals of MG3 (i.e. B and Cin inputs) in Fig. 15 with same polarization reach sooner than another input signal (i.e. A input), the B (or Cin) value temporarily dominates to A input value. Accordingly, MG3 acts like an inverter gate in this case. Thus, lengthening output paths can lead to noise amplification due to synergic effect. It can be tested that lengthening input paths in [59] can lead to wrong response where B = Cin.

Hence, drawing the mid-input (i.e. A input) closer to device cell of two gates (i.e. XOR3 and MG3) gives more reliable output response. In this paper, we use this property to design an efficient QCA full adder circuit.

The logical block diagram of the proposed FA circuit is presented in Fig. 16. In addition, Fig. 17 shows the three layers of the proposed efficient FA.

Figure 18 shows three layers of the proposed FA separately. As illustrated in Fig. 18, the XOR3 gate is placed on the main layer (i.e. layer 0) and MG3 gate is placed in layer 2. Layer 1 consists of 3 cells for interconnecting two layers.

The presented work consists of 28 QCA cells. It has 2 clock phases delay. The occupation area of the proposed full adder is 0.01μm2.

4.2 The Proposed 4-Bit RCA

The accessibility to the inputs and outputs of the proposed FA is feasible and it is simple for using the proposed FA in larger designs. Therefore, we use the proposed FA for designing an efficient 4-bit ripple carry adder. Figures 19 and 20 show the logical diagram and the layout of the proposed 4-bit QCA RCA, respectively.

The layout of the proposed RCA contains only 135 cells, and 0.06μm2 area. This design could be easily extended to n-bit RCA circuit.

5 Simulation Results and Comparison

The proposed 1-bit QCA full adder and 4-bit QCA RCA are simulated by using QCADesigner tool version 2.0.3. In this section, for determining the cost parameter value, the following equation is used:

5.1 The Proposed QCA Full Adder

Figure 21 shows simulation results using the bistable approximation engine by default settings. The simulation results illustrate that the designed FA performs correctly. The latency is 0.5 clock cycles.

Table 1 compares our proposed 1-bit QCA FA with other existing designs. This comparison shows that our proposed QCA FA is most cost and delay efficient compared to other QCA FA circuits in [21, 22, 31,32,33,34,35,36,37,38,39,40,41,42,43,44,45,46,47,48,49,50,51,52,53,54,55,56,57,58,59, 67, 68].

Based on our simulation results that are shown in Table 1, our proposed QCA FA circuit has a minimum number of cell count, area, delay and cost in comparisons with previous designs in [21, 31,32,33,34,35,36,37,38,39,40,41,42,43,44,45,46,47,48,49,50,51, 53, 54, 56,57,58,59]. For example, the proposed QCA FA circuit provides an improvement by about 26, 50, 33 and 66% in terms of cell count, area, latency, and cost, respectively compared to [42].

Despite less cell count in [55, 67], the designed FA circuit in this paper has a better delay and cost term features and has improved by about 33% in these two terms. Moreover, despite the presented FA circuit in [55], our design has accessibility to output cells.

Although the designed FA circuits in [21, 36, 44, 54, 56, 58, 59, 68] have the same delay time with our proposed QCA FA circuit, our proposed FA circuit has supremacy in cell count, area and cost parameters. In comparison with the designed FA in [21], our design has one cell lesser and improvement by about 50% in area and cost. In addition, our design has improvements in cell count, area and cost parameters by about 31, 75 and 75% in comparison with [56], 9, 50 and 50% in comparison with [54, 59], 15, 50 and 50% in comparison with [36], 37, 74 and 74% in comparison with [44], 31, 75 and 75% in comparison with [58], and 9, 66 and 66% in comparison with [68], respectively.

Practically, it could be tested that lengthening the input and output lines of the proposed FA circuit leads to more reliable output response and the proposed FA circuit is more relaxed about changing the input and outputs lines than previous design in [59].

The results show that we propose an efficient QCA full adder in terms of cell count, area, delay, and cost. Moreover, compatibility with other designs, accessibility to the inputs and outputs and flexibility for changing the length of the input and output lines are other advantages of the proposed FA circuit. Hence, the proposed QCA FA is applicable to use in designing larger QCA circuits such as RCA circuits.

5.2 The Proposed 4-Bit RCA

Figure 22 illustrates simulation results of the proposed 4-bit RCA that is simulated by bistable approximation engine using 220,000 samples. Other setting remained by default. The proposed RCA has 5 clock phases or 1.25 clock cycles latency.

The comparison between the proposed 4-bit ripple carry adder circuit and previous circuits are demonstrated in Table 2.

According to results in Table 2, the proposed 4-bit QCA RCA circuit has best results in terms of cell count, area and cost in comparison to all mentioned designs in Table 2. So, our design provides improvement at least by about 22, 40 and 40% in terms of cell count, occupation area and cost, respectively in comparison to other QCA RCA circuits in this table. For example, despite the more delay of one clock phase in comparison to [36], the provided improvement in terms of cell count, area and cost are 22, 57, and 46%, respectively.

Despite similar delay time to those of the designs proposed in [58, 60], our proposed design provides considerable improvement from the point of view of cell count, occupation area, and final cost. So, the cell count, area, and cost terms have been reduced by about 26, 39, and 40%, respectively compared to [60].

6 Conclusion

The QCA technology as a promising and developing alternative technology for CMOS technology is in the focal point of the researcher interests for designing the ultra-dense and ultra-speed digital circuits. In this paper, we designed a new and efficient QCA full adder circuit by designing an efficient circuit for sum and carry output in separated layers. Then, we designed a novel and efficient 4-bit QCA RCA using 135 QCA cells in 0.06 μm2 with 5 clock phases delay. The proposed designs are simulated using QCADesigner tool version 2.0.3 that demonstrated correctness work of the proposed designs. Besides, the comparisons showed that the proposed QCA circuits have advantages compared to other QCA circuits in term of area, latency and cost.

References

Karimi, A., Rezai, A.: A design methodology to optimize the device performance in CNTFET. ECS J. Solid State Sci. Technol. 6(8), M97–M102 (2017)

Zareiee, M.: A novel high performance nano-scale MOSFET by inserting Si3N4 layer in the channel. Superlattice. Microst. 88, 254–261 (2015)

Zareiee, M.: Modifying buried layers in nano-MOSFET for achieving reliable electrical characteristics. ECS J. Solid State Sci. Technol. 5(10), M113–M117 (2016)

Zareiee, M.: High performance Nano device with reduced Short Channel effects in high temperature applications. ECS J. Solid State Sci. Technol. 6(7), M75–M78 (2017)

Zareiee, M., Mehrad, M.: A reliable Nano device with appropriate performance in high temperatures. ECS J. Solid State Sci. Technol. 6(4), M50–M54 (2017)

Zareiee, M., Orouji, A.A.: Superior electrical characteristics of novel nanoscale MOSFET with embedded tunnel diode. Superlattice. Microst. 101, 57–67 (2017)

Mehrad, M.: Reducing floating body and Short Channel effects in Nano scale transistor: inserted P+ region SOI-MOSFET. ECS J. Solid State Sci. Technol. 5(9), M88–M92 (2016)

Mehrad, M.: Application of N+ buried layer in reducing lattice temperature of Nano-scale MOSFET. ECS J. Solid State Sci. Technol. 5(12), M158–M162 (2016)

Cho, G., Kim, Y.-B., Lombardi, F.: Assessment of CNTFET based circuit performance and robustness to PVT variations. In: Circuits and Systems, 2009. MWSCAS'09. 52nd IEEE International Midwest Symposium on 2009, pp. 1106–1109. IEEE (2009)

Shafizadeh, M., Rezai, A.: Improved device performance in a CNTFET using La2O3 high-κ dielectrics. J. Comput. Electron. 16(2), 221–227 (2017)

Karimi, A., Rezai, A.: Improved device performance in CNTFET using genetic algorithm. ECS J. Solid State Sci. Technol. 6(1), M9–M12 (2017)

Naderi, A., Tahne, B.A.: T-CNTFET with gate-drain overlap and two different gate metals: a novel structure with increased saturation current. ECS J. Solid State Sci. Technol. 5(8), M3032–M3036 (2016)

Naderi, A., Ahmadmiri, S.A.: Attributes in the performance and design considerations of asymmetric drain and source regions in carbon Nanotube field effect transistors: quantum simulation study. ECS J. Solid State Sci. Technol. 5(7), M63–M68 (2016)

Seminario, J.M., Derosa, P.A., Cordova, L.E., Bozard, B.H.: A molecular device operating at terahertz frequencies: theoretical simulations. IEEE Trans. Nanotechnol. 3(1), 215–218 (2004)

Abu El-Seoud, A., El-Banna, M., Hakim, M.: On modelling and characterization of single electron transistor. Int. J. Electron. 94(6), 573–585 (2007)

Meng, H., Wang, J., Wang, J.-P.: A spintronics full adder for magnetic CPU. IEEE electr. Dev. lett. 26(6), 360–362 (2005)

Balali, M., Rezai, A., Balali, H., Rabiei, F., Emadi, S.: A novel design of 5-input majority gate in quantum-dot cellular automata technology. In: Computer Applications & Industrial Electronics (ISCAIE), 2017 IEEE Symposium on 2017, pp. 13–16. IEEE

Kim, K., Wu, K., Karri, R.: Towards designing robust QCA architectures in the presence of sneak noise paths. In: Proceedings of the conference on Design, Automation and Test in Europe-Volume 2 2005, pp. 1214–1219. IEEE Computer Society (2005)

Kim, K., Wu, K., Karri, R.: Quantum-dot cellular automata design guideline. IEICE Trans. Fundam. Electron. Commun. Comput. Sci. 89(6), 1607–1614 (2006)

Niemier, M.T.: Designing digital systems in quantum cellular automata. University of Notre Dame (2000)

Balali, M., Rezai, A., Balali, H., Rabiei, F., Emadi, S.: Towards coplanar quantum-dot cellular automata adders based on efficient three-input XOR gate. Results Phys. 7, 1389–1395 (2017)

Navi, K., Farazkish, R., Sayedsalehi, S., Azghadi, M.R.: A new quantum-dot cellular automata full-adder. Microelectron. J. 41(12), 820–826 (2010)

Swartzlander, E.E., Cho, H., Kong, I., Kim, S.-W.: Computer arithmetic implemented with QCA: A progress report. In: Signals, Systems and Computers (ASILOMAR), 2010 Conference Record of the Forty Fourth Asilomar Conference on 2010, pp. 1392–1398. IEEE (2010)

Liu, W., Lu, L., O'Neill, M., Swartzlander, E.E.: Design rules for quantum-dot cellular automata. In: Circuits and Systems (ISCAS), 2011 IEEE International Symposium on 2011, pp. 2361–2364. IEEE (2011)

Sabbaghi-Nadooshan, R., Kianpour, M.: A novel QCA implementation of MUX-based universal shift register. J. Comput. Electron. 13(1), 198–210 (2014)

Mustafa, M., Beigh, M.: Novel Linear Feedback Shift Register Design in Quantum-Dot Cellular Automata. (2014)

Perri, S., Corsonello, P., Cocorullo, G.: Design of efficient binary comparators in quantum-dot cellular automata. IEEE Trans. Nanotechnol. 13(2), 192–202 (2014)

Hayati, M., Rezaei, A.: Design and optimization of full comparator based on quantum-dot cellular automata. ETRI J. 34(2), 284–287 (2012)

Rashidi, H., Rezai, A., Soltany, S.: High-performance multiplexer architecture for quantum-dot cellular automata. J. Comput. Electron. 15(3), 968–981 (2016)

Rashidi, H., Rezai, A.: Design of Novel Efficient Multiplexer Architecture for quantum-dot cellular automata. J. Nano Electron. Phys. 9(1), 1012–1011 (2017)

Waje, M.G., Dakhole, P.: Analysis of various approaches used for the implementation of QCA based full adder circuit. In: Electrical, Electronics, and Optimization Techniques (ICEEOT), International Conference on 2016, pp. 2424–2428. IEEE (2016)

Singh, G.: Design and performance analysis of a new efficient coplanar quantum-dot cellular automata adder. Indian Journal of Pure & Applied Physics (IJPAP). 55(2), 97–103 (2017)

Abedi, D., Jaberipur, G., Sangsefidi, M.: Coplanar full adder in quantum-dot cellular automata via clock-zone-based crossover. IEEE Trans. Nanotechnol. 14(3), 497–504 (2015)

Ramesh, B., Rani, M.A.: Design of an Optimal Decimal Adder in quantum dot cellular automata. Int. J. Nanotechnol. Appl. 11(2), 197–211 (2017)

Mokhtari, D., Rezai, A., Rashidi, H., Rabiei, F., Emadi, S., Karimi, A.: Design of novel efficient full adder architecture for quantum-dot cellular automata technology. Facta Univ. Ser. Electron. Energ. 31(2), 279–285 (2018)

Rashidi, H., Rezai, A.: High-performance full adder architecture in quantum-dot cellular automata. J. Eng. 2017(7), 394–402 (2017)

Sen, B., Sahu, Y., Mukherjee, R., Nath, R.K., Sikdar, B.K.: On the reliability of majority logic structure in quantum-dot cellular automata. Microelectron. J. 47, 7–18 (2016)

Kianpour, M., Sabbaghi-Nadooshan, R., Navi, K.: A novel design of 8-bit adder/subtractor by quantum-dot cellular automata. J. Comput. Syst. Sci. 80(7), 1404–1414 (2014)

Mostafaee, A., Rezaei, A., Karkhanehchi, M.M., Jamshidi, S.M.: Design of QCA full adders without wire crossing. Boson J. Modern Phys. 2(2), 90–96 (2015)

Sonare, N., Meena, S.: A robust design of coplanar full adder and 4-bit Ripple Carry adder using qunatum-dot cellular automata. In: Recent Trends in Electronics, Information & Communication Technology (RTEICT), IEEE International Conference on 2016, pp. 1860–1863. IEEE (2016)

Pudi, V., Sridharan, K.: Low complexity design of ripple carry and Brent–kung adders in QCA. IEEE Trans. Nanotechnol. 11(1), 105–119 (2012)

Mohammadi, M., Mohammadi, M., Gorgin, S.: An efficient design of full adder in quantum-dot cellular automata (QCA) technology. Microelectron. J. 50, 35–43 (2016)

Bishnoi, B., Giridhar, M., Ghosh, B., Nagaraju, M.: Ripple carry adder using five input majority gates. In: Electron Devices and Solid State Circuit (EDSSC), 2012 IEEE International Conference on 2012, pp. 1–4. IEEE (2012)

De, D., Das, J.C.: Design of novel carry save adder using quantum dot-cellular automata. J. Comput. Sci. 22, 54–68 (2017)

Hashemi, S., Navi, K.: A novel robust QCA full-adder. Proc. Mater. Sci. 11, 376–380 (2015)

Jaiswal, R., Sasamal, T.N.: Efficient design of full adder and subtractor using 5-input majority gate in QCA. In: Contemporary Computing (IC3), 2017 Tenth International Conference on 2017, pp. 1–6. IEEE (2017)

Kassa, S.R., Nagaria, R.: A novel design of quantum dot cellular automata 5-input majority gate with some physical proofs. J. Comput. Electron. 15(1), 324–334 (2016)

Labrado, C., Thapliyal, H.: Design of adder and subtractor circuits in majority logic-based field-coupled QCA nanocomputing. Electron. Lett. 52(6), 464–466 (2016)

Sasamal, T.N., Singh, A.K., Mohan, A.: An optimal design of full adder based on 5-input majority gate in coplanar quantum-dot cellular automata. Optik-Int. J. Light Electron Opt. 127(20), 8576–8591 (2016)

Sasamal, T.N., Singh, A.K., Mohan, A.: An efficient design of quantum-dot cellular automata based 5-input majority gate with power analysis. Microprocess. Microsyst. (2018)

Hashemi, S., Tehrani, M., Navi, K.: An efficient quantum-dot cellular automata full-adder. Sci. Res. Essays. 7(2), 177–189 (2012)

Navi, K., Sayedsalehi, S., Farazkish, R., Azghadi, M.R.: Five-input majority gate, a new device for quantum-dot cellular automata. J. Comput. Theor. Nanosci. 7(8), 1546–1553 (2010)

Roohi, A., Khademolhosseini, H., Sayedsalehi, S., Navi, K.: A symmetric quantum-dot cellular automata design for 5-input majority gate. J. Comput. Electron. 13(3), 701–708 (2014)

Sen, B., Rajoria, A., Sikdar, B.K.: Design of efficient full adder in quantum-dot cellular automata. Sci. World J. 2013, 250802 (2013)

Seyedi, S., Navimipour, N.J.: An optimized design of full adder based on nanoscale quantum-dot cellular automata. Optik-Int. J. Light Electron Opt. 158, 243–256 (2018)

Ahmad, F., Bhat, G.M., Khademolhosseini, H., Azimi, S., Angizi, S., Navi, K.: Towards single layer quantum-dot cellular automata adders based on explicit interaction of cells. J. Comput. Sci. 16, 8–15 (2016)

Goswami, M., Mohit, K., Sen, B.: Cost effective realization of XOR logic in QCA. In: Embedded Computing and System Design (ISED), 2017 7th International Symposium on 2017, pp. 1–5. IEEE (2017)

Balali, M., Rezai, A.: Design of low-complexity and high-speed coplanar four-bit ripple carry adder in QCA technology. Int. J. Theor. Phys. 57(7), 1948–1960 (2018)

Safoev, N., Jeon, J.-C.: Full adder based on quantum-dot cellular automata. In proc. Manila Int. Conf. Trends Eng. Technol. (MTET-17), 83–86 (2017)

Safoev, N., Jeon, J.-C.: Compact RCA based on multilayer quantum-dot cellular automata. In: Information Systems Design and Intelligent Applications. pp. 515–524. Springer (2018)

Walus, K., Dysart, T.J., Jullien, G.A., Budiman, R.A.: QCADesigner: a rapid design and simulation tool for quantum-dot cellular automata. IEEE Trans. Nanotechnol. 3(1), 26–31 (2004)

Lent, C.S., Tougaw, P.D., Porod, W., Bernstein, G.H.: Quantum cellular automata. Nanotechnology. 4(1), 49 (1993)

Niknezhad Divshali, M., Rezai, A., Karimi, A.: Towards multilayer QCA SISO shift register based on efficient D-FF circuits. Int. J. Theor. Phys. 57(11), 3326–3339 (2018)

Lent, C.S., Tougaw, P.D.: A device architecture for computing with quantum dots. Proc. IEEE. 85(4), 541–557 (1997)

Pudi, V., Sridharan, K.: Efficient design of a hybrid adder in quantum-dot cellular automata. IEEE trans. Very Large Scale Integ. (VLSI) Syst. 19(9), 1535–1548 (2011)

Hanninen, I., Takala, J.: Robust adders based on quantum-dot cellular automata. In: Application-specific Systems, Architectures and Processors, 2007. ASAP. IEEE International Conf. on 2007, pp. 391–396. IEEE (2017)

Roohi, A., DeMara, R.F., Khoshavi, N.: Design and evaluation of an ultra-area-efficient fault-tolerant QCA full adder. Microelectron. J. 46(6), 531–542 (2015)

Arani, I.E., Rezai, A.: Novel circuit design of serial–parallel multiplier in quantum-dot cellular automata technology. J. Comput. Electron. 1–9 (2018)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Adelnia, Y., Rezai, A. A Novel Adder Circuit Design in Quantum-Dot Cellular Automata Technology. Int J Theor Phys 58, 184–200 (2019). https://doi.org/10.1007/s10773-018-3922-0

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10773-018-3922-0