Abstract

This paper describes a wide-harvesting-range, wide band, and high-efficiency complementary metal-oxide-semiconductor (CMOS) rectifier for low-power application in internet of things systems. Through maximum power point tracking, the proposed rectifier can dynamically detect the output voltage to enable switching between various circuit modes in order to achieve higher power conversion efficiency (PCE), even during sub-1-V operation. The experimental results for a \(0.18\hbox {-}\upmu \hbox {m}\) standard CMOS process with a 1.8-V power supply voltage demonstrate that the proposed rectifier can operate from a low voltage (0.7 V) to a high voltage (1.8 V) while maintaining high PCE. The proposed rectifier achieves a PCE improvement of 16% from the rectifier with a bootstrapping circuit under a peak alternating current (AC) input voltage of 0.85 V, and of 47.5% from the fully cross-coupled rectifier under a 1.8-V peak AC input voltage. Moreover, because its structure is insensitivity to the frequency response, the proposed rectifier provides a wide operating frequency range of 10–960 MHz.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

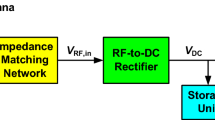

With the continuing development of wireless technology and commercial electronic devices, the internet of things (IoT) has become a technological trend that enables ordinary objects capable of exercising independent functions to implement interoperable networks. Cisco is expected to have an IoT market worth US$ 19 trillion within the next decade [14], and analysts have predicted that IoT applications will connect 36 billion devices by 2020 [32]. Energy harvesting plays a key role in IoT applications. Compared with thermal, photovoltaic (PV) [2], and piezoelectric energy harvesting technologies [22, 33], radio frequency (RF) energy harvesting is more suitable for use in low-power, low-cost IoT systems such as wireless sensor platforms [1, 5, 13, 19, 24, 27,28,29]. As shown in Fig. 1, the working principle of an energy harvester for low-power IoT system applications entails the transmission of an RF alternating current (AC) signal to a near-field coupling coil using a power transmitter and its conversion using a rectifier. The AC signal received by the coupling coil is converted to direct current (DC) power supply and used in a load system that is input to a low-dropout regulator (LDO) to produce a stable DC supply.

In the standard CMOS process, the diodes are generally easily replaced by the diode-connected MOS. However, this architecture is affected by the threshold voltage \((V_{\mathrm{TH}})\), and the instantaneous voltage change through transistor-based switches caused by channel resistance results in the reduction in the output voltage, which in turn affects the overall power conversion efficiency (PCE) [15]. Therefore, many rectifier architectures, such as the gate cross-coupled rectifier (GCCR) [31], fully cross-coupled rectifier (FCCR) [3, 6, 9], rectifier with unbalanced-biased comparators (RUBC) [8], and rectifier with bootstrapping circuit (RBC) [11, 26], have been proposed.

The remainder of this paper is organized as follows: Sect. 2 discusses the architecture and characteristics of conventional rectifier topologies. Section 3 presents the proposed rectifier topology based on maximum power point tracking (MPPT) and describes its circuit. Section 4 presents the experimental results of the proposed rectifier and compares it with those of other topologies. Concluding remarks are provided in Sect. 5.

2 Analyses and Comparisons of Conventional Rectifiers

The full-wave bridge rectifier (FWBR) is one of the most common rectifier structures and the most widely implemented full-wave rectifier structure, as shown in Fig. 2. Compared with half-wave rectifiers, it exhibits higher power conversion and lower ripple voltages [31]. The FWBR consists of four diodes and does not require a center-tapped transformer. Because diodes connected to the load are used, a difference is generated between the output voltage \((V_{\mathrm{OUT}})\) and AC input voltage \((V_{\mathrm{AC}})\) for the \(V_{\mathrm{TH}}\) values of these two diodes.

The GCCR [31] implements the full-wave rectifier with all MOS transistors, as shown in Fig. 3. The GCCR and FWBR differ in that two diodes in the GCCR are replaced by N-type MOS (NMOS)-based switches \(M_{3}\) and \(M_{4}\), and the NMOS gate is connected directly to the signal source to obtain a greater voltage swing, thereby enabling the transistor to instantaneously switch between the cutoff and linear regions. Therefore, the favorable transmission characteristics of the low voltage potential in the NMOS-based switch can effectively reduce the output voltage loss caused by the threshold voltage, resulting in higher PCE. However, the GCCR uses diode-connected p-channel MOS (PMOS) switches \(M_{1}\) and \(M_{2}\) connected to the load, resulting in a variation in the output voltage and AC input voltage for the \(V_{\mathrm{TH}}\) of one diode. In low-voltage operation, the voltage conversion efficiency (VCE) degrades considerably because of the \(V_{\mathrm{TH}}\), thereby directly affecting the PCE. The \(V_{\mathrm{OUT}}\), VCE, and PCE are defined as:

where \(P_{\mathrm{RL}}\) is the power consumed by the load, \(P_{\mathrm{IN}}\) is the total power input, and \(I_{\mathrm{RL}}\) is the current flowing through the load.

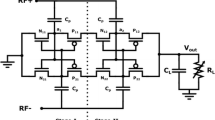

The FCCR [6] differs from the GCCR in that it contains four MOS-based switches (\(M_{1}-M_{4})\) in the two main branches, and each gate is cross-connected to the other input signal, as shown in Fig. 4a. In contrast to the GCCR, the FCCR circuit solves the problem caused by the output drop by using a full-switch form. However, it cannot achieve high PCE in an operation over a wide voltage range because it experiences reverse current on PMOS transistors \(M_{1}\) and \(M_{2}\) [9], as shown in Fig. 4b. To reduce the difference between the input and output instantaneous voltages in order to suppress the occurrence of reverse current, relative coupling capacitances \(C_{\mathrm{C1}}\) and \(C_{\mathrm{C2}}\) are required during high-voltage operation for achieving high conversion efficiency. Therefore, using reverse current to charge the coupling capacitance improves the input DC level.

Notably, on adjusting the size and the corresponding coupling capacitance, the FCCR yields different peaks in the PCE characteristic curve, as shown in Fig. 5. The simulation results all have shunt loads of \(C_{\mathrm{L}}= 400\, \hbox {pF}\) and \(R_{\mathrm{L}}= 70\,\Omega \) under various AC input voltages. Consequently, increasing the size of all transistors to enhance the current drive capability, which in turn increases the output load voltage, is essential for achieving the ideal PCE peak in low-voltage operation. Because the input signal is small and the output voltage is relatively low in the FCCR, the problem of reverse current is not too concerning and thus no coupling capacitance aid is required. By contrast, obtaining the ideal PCE peak in high-voltage operation does not require an extremely large transistor size to enhance drive capability, but does require auxiliary coupling capacitance to avoid excessive reverse current.

As shown in Fig. 6, the RUBC [8] is based on the FCCR, with the only difference being that the RUBC contains two PMOS transistors controlled by two unbalanced-biased comparators that enable the circuit to more precisely control the switching behavior. Power PMOS transistors \(M_{1}\) and \(M_{2}\) are switched on only when the moment input voltage is higher than the output voltage, thereby effectively preventing reverse current without coupling capacitance. Therefore, the RUBC occupies a smaller area but achieves higher PCE performance than does the FCCR when the operation voltage is high. The RUBC exhibits good PCE character curves in high-voltage operation; however, as a trade-off for the high conversion efficiency, the two unbalanced-biased comparators require a certain degree of input voltage drive to operate normally; thus, achieving high efficiency in low-voltage operation is a substantial challenge for the RUBC.

In most rectifier topologies, the \(V_{\mathrm{TH}}\) of components decreases the conversion efficiency in low-voltage operation. Only the FCCR can achieve optimal conversion; however, it cannot maintain high PCE over a wide input voltage range because of reverse current. As shown in Fig. 7, the RBC [11, 26] uses bootstrapping diodes \(M_{1}\), \(M_{5}\), \(M_{7}\), and \(C_{1}\) and \(M_{2}\), \(M_{6}\), \(M_{8}\), and \(C_{2}\) with \(V_{\mathrm{TH}}\) values lower than those of the diode-connected MOS connected to the load in order to obtain higher VCE and more favorable PCE curves. Therefore, the RBC has the potential to mitigate the problems of low voltage input and a wide input voltage range.

In Eq. (4), in contrast to the conventional diode-connected PMOS structure, the effective \(V_{\mathrm{TH}} (V^{\prime }_{\mathrm{TH}})\) of the circuit is reduced. Thus, reducing the \(V^{\prime }_{\mathrm{TH}}\) of a standard MOS transistor can increase the output voltage range for an input source voltage:

where the \(V_{\mathrm{TH}}\) values of MOS transistors \(M_{1} (V_{\mathrm{TH1}})\) and \(M_{5}(V_{\mathrm{TH5}})\) are equal to those of MOS transistors \(M_{2} (V_{\mathrm{TH2}})\) and \(M_{6}\) \((V_{\mathrm{TH6}})\), respectively.

Figure 8 shows the PCE characteristic curves for the GCCR, FCCR, RUBC, and RBC at the same power transistor size and under a shunt load of \(C_{\mathrm{L}} = 400\, \hbox {pF}\) and \(\hbox {R}_{\mathrm{L}} = 70\,\Omega \). Evidently, the RBC is an evolved version of the GCCR, but it is not as efficient as the FCCR is in low-voltage operation or the RUBC is in high-voltage operation.

Table 1 and the aforementioned description and figures illustrate the advantages and disadvantages of various rectifier topologies and their appropriate operating conditions. In recent years, more and more MPPT techniques are used in the energy harvesting circuits to enhance efficiency [4, 23, 25, 33]. Therefore, this study combines the advantages of the FCCR [6] and RBC [11] with the concept of MPPT technique. Through dynamic sensing, the various output voltage conditions required to switch to the most suitable circuit operation mode at any time were obtained to effectively enhance the input voltage range and operating bandwidth and upgrade the overall PCE under different input conditions in correlation with the many system specifications, thereby achieving the goals of low input voltage, wide harvesting range, wide band, and high efficiency.

3 Design of the Proposed Rectifier

As shown in Fig. 8, among the analyzed topology rectifiers, the FCCR exhibits the best PCE performance for low-voltage operation, and it does not require coupling capacitances (Ver. 3 of Fig. 5), thereby greatly reducing the required chip area. In addition, because the FCCR directly controls the MOS switches from the signal input, the PCE characteristic is almost completely unaffected by the different frequency. Therefore, the FCCR is the preferred circuit for low-voltage and wide-frequency operation. For high-voltage operation, the PCE characteristic of the RUBC is the best. However, the use of comparators results in significant degradation of the PCE curve of the RUBC in high-frequency operation. Therefore, the RUBC exhibits lower performance than does the RBC in relatively high-frequency operation.

To achieve maximum PCE under various operating voltages and frequencies, this paper proposes an MPPT-based structure with a wide harvesting range, wide band, and high efficiency. Figure 9 shows the basic concepts used in this work. The proposed rectifier is controlled by a dynamic output voltage detector (DOVD) that combines the advantages of the FCCR in low-voltage operation as shown in Fig. 9a and the RBC in high-voltage operation as shown in Fig. 9b. Figure 9c shows the proposed rectifier is extended by combining both curves in Fig. 9a, b. Because of its compact architecture, the proposed rectifier can reduce the parasitic effects of internal and external nodes and remain unaffected by the variation in input frequency. Therefore, the proposed rectifier can maintain high PCE in both low-voltage operation and high-voltage operation.

Figure 10a shows a concept diagram of the wide-input-voltage-range CMOS rectifier with DOVD, where the power transistor MOS \(M_{1}-M_{4}\) is the main path transistor, and all the power transistor MOS operate at linear region as switches with low on-resistance as Eq. 5. As a result, it can reduce voltage drops to achieve higher voltage conversion ratio. When the AC input signal is insufficiently high, \(V_{\mathrm{OUT}}\) is relatively low. Consequently, the DOVD provides diode-connected PMOS \(M_{6}\) with a path to ground to send output power transistor PMOS \(M_{5}\) into the linear region as a switch (Fig. 10b), resulting in the FCCR circuit mode for low-voltage operation achieving a high PCE without coupling capacitance. Thus, the \(V_{\mathrm{OUT}}\) of FCCR mode is given by Eq. 6. By contrast, when the \(V_{\mathrm{OUT}}\) is relatively high, the DOVD \(V_{\mathrm{OUT}}\, (V_{\mathrm{DO}})\) follows the rectifier \(V_{\mathrm{OUT}}\) (Fig. 10c), resulting in the RBC circuit mode, and the \(V_{\mathrm{OUT}}\) can be rewritten as Eq. 7. In high-voltage operation, the circuit output connects to a bootstrapping diode that can effectively block reverse current with only a tiny voltage dropout due to the \(V_{\mathrm{TH}}\) of the bootstrapping diode in Eq. (4). Therefore, this circuit can achieve a higher VCE and thus a higher PCE.

The proposed rectifier based on an MPPT with DOVD design to dynamically detect \(V_{\mathrm{OUT}}\) values to enable switching to different circuit modes, thereby achieving high PCE. Figure 11 shows the flowchart of the proposed rectifier based on MPPT technique. The output voltage \((V_{\mathrm{OUT}})\) is the function of AC input voltage \((V_{\mathrm{AC}})\). Once the \(V_{\mathrm{OUT}}\) is greater than \(V_{\mathrm{T}}\), the circuit enters the RBC mode; otherwise, it enters the FCCR mode. Then, the \(V_{\mathrm{OUT}}\) of RBC mode and FCCR mode is given by Eqs. (6) and (7), respectively. As a result, a higher VCE is achieved by reducing voltage drop, thereby achieving higher PCE.

The complete timing diagram of the proposed rectifier with DOVD is illustrated in Fig. 12. A conceptual diagram of the proposed DOVD is depicted in Fig. 13. The DOVD \(V_{\mathrm{OUT}} (V_{\mathrm{DO}})\) is 0 when the DOVD input voltage \((V_{\mathrm{DIN}})\) is lower than the DOVD transition voltage \((V_{\mathrm{T}})\) (line A), and the \(V_{\mathrm{DO}}\) follows the \(V_{\mathrm{DIN}}\) when the \(V_{\mathrm{DIN}}\) is higher than the \(V_{\mathrm{T}}\) (line B).

Figure 14a illustrates the proposed high-efficiency CMOS rectifier, and its operating principle of the different input voltage cycles under high-voltage operation is shown in Fig. 14b, c. In the positive half cycle of AC input voltage, the power transistor MOS \(M_{2}\) and \(M_{3 }\)are turned OFF and the power transistor MOS \(M_{1}\) and \(M_{4}\) are turned ON in the linear region to form the main path. The output voltage \((V_{\mathrm{OUT}})\) connects to a bootstrapping diode formed by PMOS \(M_{5}\) and \(M_{6}\) which can effectively block reverse current with only a tiny voltage dropout. By contrast, the power transistor MOS \(M_{1}\) and \(M_{4 }\) are turned OFF and the power transistor MOS \(M_{2}\) and \(M_{3}\) are turned ON in the linear region to form the main path during the negative half cycle of AC input voltage. The proposed DOVD is combined with the FCCR characteristic of high PCE in low-voltage operation without coupling capacitors and the RBC characteristic of effectively preventing reverse current in high-voltage operation with low-voltage dropout, thereby maintaining high voltage and PCE. When the voltage division of the \(V_{\mathrm{DIN}}\) on resistor \(\hbox {R}_{1}\) is higher than the \(V_{\mathrm{TH}}\) of PMOS transistor \(M_{7}\, (V_{\mathrm{T7}})\), PMOS transistor \(M_{7}\) is sent to the linear region, thereby enabling adjustment of the ratio of resistors \(\hbox {R}_{1}\) and \(\hbox {R}_{2}\) the determination of the \(V_{\mathrm{T}}\) in Fig. 13:

To enable PMOS transistor \(M_{7}\) to quickly enter the linear region to obtain a low-dropout \(V_{\mathrm{DO}}\), the ratio size of PMOS transistor \(M_{7}\) and resistor \(\hbox {R}_{3}\) must be controlled; a larger transistor size for \(M_{7}\) or larger resistor value for \(\hbox {R}_{3}\) enables PMOS transistor \(M_{7}\) to more quickly and easily enter the linear region.

The main path PMOS transistors \(M_{1}\) and \(M_{2}\) and output power PMOS transistor \(M_{5}\) contribute to a relatively large parasitic capacitance as a smoothing capacitance at node \(V_{\mathrm{X}}\), which causes the DC voltage at the node \(V_{\mathrm{X}}\) to rise. However, different DC and AC voltage at \(V_{\mathrm{AC}}\), \(V_{\mathrm{X}}\), and \(V_{\mathrm{OUT}}\) will cause floating source and drain on PMOS transistors \(M_{1}\), \(M_{2}\), and \(M_{5}\). Because of the floating source and drain, the transistor base in the case of conduction cannot receive the highest potential in the circuit, resulting in the body effect, leakage current, and latch-up effect. To mitigate these problems, the dynamic base bias (DBB) circuit [7] is connected to the base terminal of PMOS transistors \(M_{1}\), \(M_{2}\) and \(M_{5}\) to ensure that the body bias of PMOS transistors \(M_{1}\), \(M_{2}\) and \(M_{5}\) can be maintained at high potential, as shown in Fig. 15.

Compared with the FCCR, the proposed rectifier can effectively prevent reverse current to achieve a higher PCE without coupling capacitance. Compared with the RBC, PMOS transistors \(M_{1}\)–\(M_{5}\) in the proposed rectifier operate in the linear area in low-voltage operation to effectively reduce the source–drain voltage and improve the VCE and PCE. In addition, the reduced use of capacitance results in the proposed rectifier requiring less chip area than does the RBC.

4 Experimental Results

The proposed rectifier was developed through \(0.18\hbox {-}\upmu \hbox {m}\) standard CMOS process with a 1.8-V supply voltage. The layout diagram is shown in Fig. 16. The entire system, including the I/O pad, required an area of \(645 \times 790\, \upmu \hbox {m}\). In Fig. 16, region A represents bootstrapped capacitance \(C_{1}\), region B represents the main path PMOS transistors \(M_{1}\) and \(M_{2}\) with DBB circuits and NMOS transistors \(M_{3}\) and \(M_{4}\), region C represents the output power PMOS transistor \(M_{5}\) with DBB circuit, and region D represents the DOVD with PMOS transistor \(M_{6}\).

Figure 17 presents the simulation results of the DOVD under various \(V_{\mathrm{AC}}\) values. In this design, the \(V_{\mathrm{T}}\) is set at 1.1 V to serve as the circuit mode transition point to maintain the highest possible PCE under various \(V_{\mathrm{AC}}\) conditions. The \(V_{\mathrm{DO}}\) is 0 when the \(V_{\mathrm{AC}}\) is less than 1.1 V; otherwise, the \(V_{\mathrm{DO}}\) follows the \(V_{\mathrm{OUT}}\). The \(V_{\mathrm{T}}\) of this circuit can be adjusted according to the load conditions. Appropriate to set the \(V_{\mathrm{T}}\) in the cross-point of PCE of the two adopted circuit architectures (FCCR and RBC) can achieve the overall best PCE output.

PCE is often used to compare the characteristics of various rectifier structures. In this section, we compare the previously discussed FCCR and RBC simulation results with those of the proposed rectifier. Figure 18 shows the PCE characteristic curves and peak input amplitudes of three rectifiers with identical main path power MOS \((M_{1}-M_{4})\) and shunt loads of \(C_{\mathrm{L}}= 400\, \hbox {pF}\) and \(R_{\mathrm{L}}= 70\, \Omega \). Compared with the RBC, the proposed rectifier achieves a 16% PCE upgrade in the case of a 0.85-V peak \(V_{\mathrm{AC}}\); moreover, because of the use of less capacitance than does the RBC, the proposed rectifier requires a relatively small area to achieve higher performance. Because of the lack of reverse current in high-voltage operation, PCE does not degrade as it does in the FCCR structure. The proposed rectifier achieves a PCE upgrade of 47.5% from that of the FCCR in the case of a 1.8-V peak \(V_{\mathrm{AC}}\).

Figure 19a and b shows the simulation waveforms of the proposed rectifier with \(V_{\mathrm{OUT}}\) values of 0.61 and 1.3 V at 0.85 and 1.8 V \(V_{\mathrm{AC}}\), respectively, under 13.56 MHz in steady state. Figure 20 shows the simulation results of the VCE characteristic curves for the load under a source frequency of 13.56 MHz. The voltage conversion efficiencies were 52.51, 72.3, and 71.35%, and the overall power efficiencies were simulated to be 55.1, 73.03, and 73.66% at peak input source amplitudes of 0.7, 0.85, and 1.8 V, respectively. Figure 21a and b shows the simulation waveforms of the proposed rectifier with \(V_{\mathrm{OUT}}\) of 1.2 and 1.25 V at 1.8-V \(V_{\mathrm{AC}}\) and 10 and 960 MHz, respectively, in steady state. Figure 22 presents the PCE simulation results for the proposed rectifier under various frequency operating points with a 1-V peak amplitude \(V_{\mathrm{AC}}\). No significant changes in PCE were observed from 10 to 960 MHz, and the overall power efficiencies were simulated to be approximately 70%.

The proposed CMOS rectifier has the features of a wide harvesting range, wide band, and high efficiency and is based on the FCCR and RBC according to different input voltages for the appropriate switch. The proposed rectifier is designed to adjust the most suitable circuit mode through the DOVD sensing circuit to obtain the highest possible PCE at each operating point. Because of the insensitivity of the FCCR and RBC to the frequency response, the operating frequency range can include the biomedical (low frequency) and IoT (high frequency) bandwidths, thus achieving wide band operation.

Table 2 compares the performance of recently developed state-of-the-art rectifiers. As evident from the table, the proposed rectifier circuit can be applied to biomedical systems operating at a relatively low frequency (13.56 MHz) [16,17,18, 20, 30] and achieves high PCE performance. In addition, the proposed rectifier has been used in an IoT system at relatively high frequencies of 400–950 MHz [10, 12, 21, 28, 34]. Because of the high-frequency operation and parasitic effects engendering low PCE, the input voltage range is often affected by the efficiency of the lifting mechanism. Therefore, enhancing the performance, bandwidth, and input voltage range of the proposed rectifier in high-frequency operation is crucial problem associated with rectifier application in all systems. The proposed rectifier exhibits high PCE performance under low input voltage, wide input range, and wide band.

5 Conclusion

Energy harvesting technologies, which have grown rapidly in recent years, have been applied in various devices. However, varying degrees of RF decay occur because of various environmental factors. Therefore, many conditions of real applications for energy harvesting circuits must be considered to prevent the possibility of heavily affecting the output characteristics and subsequent operation of the entire system.

This study proposed a wide-harvesting-range, wide band, high-efficiency CMOS rectifier based on an MPPT with DOVD design to dynamically detect \(V_{\mathrm{OUT}}\) values to enable switching to different circuit modes, thereby achieving high PCE. The VCE was 52.51, 72.3, and 71.35% and the overall PCE was 55.1, 73.03, and 73.66% at peak input source amplitudes of 0.7, 0.85, and 1.8 V, respectively. Moreover, the overall PCE in the 10–960 MHz range was approximately 70% at peak input source amplitudes of 1 V. The main feature of the proposed rectifier is its ability to maintain high PCE in both low-voltage operation (approximately 0.7 V) and high-voltage operation (approximately 1.8 V) and under wide band operation (10–960 MHz), rendering it suitable for low-power IoT applications and RF energy harvesting systems.

References

M.A. Abouzied, K. Ravichandran, E. Sánchez-Sinencio, A fully integrated reconfigurable self-startup RF energy-harvesting system with storage capability. IEEE J. Solid State Circuits 52(3), 704–719 (2017)

P.H. Chen, C.S. Wu, K.C. Lin, A 50 nW-to-10 mW output power tri-mode digital buck converter with self-tracking zero current detection for photovoltaic energy harvesting. IEEE J. Solid State Circuits 51(2), 523–532 (2016)

S. Chatterjee, M. Tarique, A 100-nW sensitive RF-to-DC CMOS rectifier for energy harvesting applications, in International Conference on VLSI Design, (2016), pp. 557–558

S.H. Chen, T.C. Huang, S.S. Ng, K.L. Lin, M.J. Du, Y.C. Kang, K.H. Chen, C.L. Wey, Y.H. Lin, C.C. Lee, J.R. Lin, T.Y. Tsai, A direct AC-DC and DC-DC cross-source energy harvesting circuit with analog iterating-based MPPT technique with 72.5% conversion efficiency and 94.6% tracking efficiency. IEEE Trans. Power Electron. 31(8), 5885–5899 (2016)

O. Elsayed, M. Abouzied, E. Sánchez-Sinencio, A 540 \(\upmu \)W RF wireless receiver assisted by RF blocker energy harvesting for IoT applications with +18 dBm OB-IIP3, in IEEE Radio Frequency Integrated Circuits Symposium, (2016), pp. 230–233

A. Facenetal, A. Boni, Power supply generation in CMOS passive UHF RFID tags, in Ph.D. Research in Microelectronics and Electronics, (2006), pp. 33–36

M. Ghovanloo, K. Najafi, Fully integrated wideband high-current rectifiers for inductively powered devices. IEEE J. Solid State Circuits 39(11), 1976–1984 (2004)

S. Guo, H. Lee, An efficiency-enhanced CMOS rectifier with unbalanced-biased comparators for transcutaneous-powered high-current implants. IEEE J. Solid State Circuits 44(6), 1796–1784 (2009)

J. Hu, H. Min, A low power and high performance analog front end for passive RFID transponder, inIEEE Workshop on Automatic Identification Advanced Technologies, (2005), pp. 199–204

P.H. Hsieh, C.H. Chou, T. Chiang, An RF energy harvester with 44.1% PCE at input available power of -12 dBm. IEEE Trans. Circuits Syst. I Regul. Pap. 62(6), 1528–1537 (2015)

S.S. Hashemi, M. Sawan, Y. Savaria, A high-efficiency low-voltage CMOS rectifier for harvesting energy in implantable devices. IEEE Trans. Biomed. Circuits Syst. 6(4), 326–335 (2012)

Z. Hameed, K. Moez, A 3.2 V -15 dBm adaptive threshold-voltage compensated RF energy harvester in 130 nm CMOS. IEEE Trans. Circuits Syst. I Regul. Pap. 62(4), 948–956 (2015)

N. Jose, N. John, P. Jain, P. Raja, T. V. Prabhakar, K. J. Vinoy, RF powered integrated system for IoT applications, inIEEE International New Circuits and Systems Conference, (2015), pp. 1–4

O.U. Khan, D.D. Wentzloff, 8.1nJ/b 2.4 GHz short-range communication receiver in 65 nm CMOS. IEEE Trans. Circuits Syst. I Regul. Pap. 62(7), 1854–1862 (2015)

U. Karthaus, M. Fischer, Fully integrated passive UHF RFID transponder IC with 16.7-mW minimum RF input power. IEEE J. Solid State Circuits 38(10), 1602–1608 (2003)

H.M. Lee, M. Ghovanloo, An integrated power-efficient active rectifier with offset-controlled high speed comparators for inductively powered applications. IEEE Trans. Circuits Syst. I Regul. Pap. 58(8), 1749–1760 (2011)

H. M. Lee, M. Ghovanloo, Fully integrated power-efficient AC-to-DC converter design in inductively-powered biomedical applications, in IEEE Custom Integrated Circuits Conference, (2011), pp. 1–8

H. M. Lee, M. Ghovanloo, An adaptive reconfigurable active voltage doubler/rectifier for extended-range inductive power transmission, in IEEE International Solid State Circuits Conference, (2012), pp. 286–288

L.X. Liu, J.C. Mu, N. Ma, W. Tu, Z.M. Zhu, Y.T. Yang, An ultra-low-power integrated RF energy harvesting system in 65-nm CMOS process. Circuits Syst. Signal Process. 35(2), 421–441 (2016)

S.Y. Lee, J.H. Hong, C.H. Hsieh, M.C. Liang, J.Y. Kung, A low-power 13.56 MHz RF front-end circuit for implantable biomedical devices. IEEE Trans. Biomed. Circuits Syst. 7(3), 256–265 (2013)

T. Le, K. Mayaram, T. Fiez, Efficient far-field radio frequency energy harvesting for passively powered sensor networks. IEEE J. Solid State Circuits 43(5), 1287–1302 (2008)

X. Liu, L. Huang, K. Ravichandran, E. Sánchez-Sinencio, A highly efficient reconfigurable charge pump energy harvester with wide harvesting range and two-dimensional MPPT for Internet of Things. IEEE J. Solid State Circuits 51(5), 1302–1312 (2016)

X. Liu, E. Sánchez-Sinencio, An 86% efficiency 12 \(\upmu \)W self-sustaining PV energy harvesting system with hysteresis regulation and time-domain MPPT for IOT smart nodes. IEEE J. Solid State Circuits 50(6), 1424–1437 (2015)

Y. Lu, H. Dai, M. Huang, M.K. Law, S.W. Sin, S.P.U, R.P. Martins, A wide input range dual-path CMOS rectifier for RF energy harvesting. IEEE Trans. Circuits Syst. II, Express Briefs 64(4), 166–170 (2017)

Y. Li, Z. Zhu, Y. Yang, Y. Sun, X. Wang, A novel interface circuit with 99.2% MPPT accuracy and 1.3% THD for energy harvesting. J. Circuits Syst. Comput. 26(11), 1750176 (2017)

W. W. Y. Lau, L. Siek, A 2.45GHz CMOS rectifier for RF energy harvesting, in IEEE Wireless Power Transfer Conference, (2016), pp. 1–3

A.K. Moghaddam, J.H. Chuah, H. Ramiah, J. Ahmadian, P.I. Mak, R.P. Martins, A 73.9% efficiency CMOS rectifier using a lower DC feeding (LDCF) self-body-biasing technique for far-field RF energy-harvesting systems. IEEE Trans. Circuits Syst. I Regul. Pap. 64(4), 992–1002 (2017)

D. Michelon, E. Bergeret, A. D. Giacomo, P. Pannier, RF energy harvester with sub-threshold step-up converter, in IEEE International Conference on RFID, (2016), pp. 1–8

M. Mahmoud, A. B. Abdel-Rahman, G. A. Fahmy, A. Aliam, H. Jia, R. K. Pokharel, Dynamic threshold compensated, low voltage CMOS energy harvesting rectifier for UHF applications, inIEEE International Midwest Symposium on Circuits and Systems, (2016), pp. 1–4

X.H. Qian, M.S. Cheng, C.Y. Wu, A CMOS 13.56-MHz high-efficiency low-dropout-voltage 40-mW inductive link power supply utilizing on-chip delay-compensated voltage doubler rectifier and multiple LDOs for implantable medical devices. IEEE J. Solid State Circuits 49(11), 2397–2407 (2014)

P. Rakers, L. Connell, T. Collins, D. Russell, Secure contactless smartcard ASIC with DPA protection. IEEE J. Solid State Circuits 36(3), 559–565 (2001)

ST. Wireless connectivity for IoT applications. http://www.st.com/content/ccc/resource/sales_and_marketing/promotional_material/brochure/d7/74/dc/eb/b4/f5/40/d5/brwireless_web.pdf/files/brwireless_web.pdf/jcr:content/translations/en.brwireless_web.pdf

J. Wang, Z. Yang, Z. Zhu, Y. Yang, A high efficiency self-powered rectifier for piezoelectric energy harvesting systems. J. Circuits Syst. Comput. 25(12), 1650164 (2016)

J. Yi, W.H. Ki, C.Y. Tsui, Analysis and design strategy of UHF micro-power CMOS rectifiers for micro-sensor and RFID applications. IEEE Trans. Circuits Syst. I Regul. Pap. 54(1), 153–166 (2007)

Acknowledgements

This work was supported by the Ministry of Science and Technology (MOST), Taiwan, under Grant MOST 106-2221-E-017-012. The authors thank the National Chip Implementation Center (CIC) of Taiwan for chip fabrication.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Lo, YL., Chuang, YH. A High-Efficiency CMOS Rectifier with Wide Harvesting Range and Wide Band Based on MPPT Technique for Low-Power IoT System Applications. Circuits Syst Signal Process 36, 5019–5040 (2017). https://doi.org/10.1007/s00034-017-0643-1

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-017-0643-1