Abstract

In this paper, a radio frequency energy harvesting system with a wide dynamic range rectifier is presented. This rectifier has two feedback and feedforward structures. These paths keep the rectifier’s power conversion efficiency (PCE) high at different input powers and thus create a high dynamic range (DR). This rectifier also has better sensitivity. Advances in the rectifier contribute to more satisfactory results for the final system. The circuit is simulated with 180 nm TSMC CMOS technology at a frequency of 900 MHz. Also, a π-type input impedance matching network circuit is used. This circuit is matched at Pin = − 19.5 dBm and f = 900 MHz. In addition, an off-chip balun is utilized to convert the received single-ended signal to the differential one. The achieved PCE and DR are 86.03% and 9.76 dB, respectively, with a sensitivity of − 19.32 at 1 V output voltage. Furthermore, the overall circuit results indicate a PCE of 76.13%, a DR of 6.3 dB, and a sensitivity of − 18.75 dBm.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Today, one of the challenges facing electronics engineers is the power supply of devices that are impractical to connect directly to wiring or batteries. Although the same methods (especially battery usage) are still used to supply power, researchers are looking for new ways to make it easier. Batteries have a limited lifetime, which raises the problem of replacing them after a certain time. For example, in the medical field [4], replacing the batteries of implants in the body can be very dangerous and expensive at the same time. In the case of the radio-frequency identification (RFID) [13], Internet of Things (IoT) or wireless sensor networks [10, 23, 26], the replacement of the battery is extremely tedious due to the large number of sensors, which may be located in dangerous areas. An alternative solution to this predicament is the utilization of environmental energies that are typically overlooked. Energy harvesting is a method that uses energy from the environment, such as radio-frequency signals [16, 17], solar [5], piezoelectric [28], heat [3], etc. to convert it into energy that can be used by sensors and electrical devices. The energy obtained from this method has very low power, but it is enough to operate low-power devices. Energy harvesting systems are usually classified according to their energy source. The most commonly used systems are vibration energy, thermal energy, light energy, and electromagnetic energy. In this paper, we intend to investigate the conversion of radio-frequency signals’ energy into DC energy that can be used by sensors.

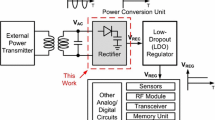

The task of the radio-frequency energy harvesting (RFEH) system is to receive the input energy and convert it to DC energy for an electric load or store it in a storage unit. A general block diagram of an RFEH system is illustrated in Fig. 1. The system includes an antenna, an impedance matching network, an RF rectifier, and a storage capacitor. These systems have three important parameters. Sensitivity is the lowest input power needed to produce the minimum usable DC voltage for a load. The power conversion efficiency (PCE) is the ratio of the output power delivered to the load to the power at the circuit’s input. Dynamic range (DR) is also a range of input power whose PCE is greater than a specific ratio of its maximum. In this paper, we consider the range above 80% of the maximum PCE as the DR [15].

Today, Dickson and differential rectifiers are widely used. The Dickson rectifier [9] operates with ordinary diodes or Schottky diodes. As depicted in Fig. 2a, the Dickson model can be implemented in standard CMOS technology using diode-connected transistors. But we will face a high voltage drop (at least one threshold voltage) resulting in reduced PCE especially at low input powers. Because of the diode-connected structure, this scheme exhibits low return current at both high and low input powers, offering an advantage in terms of low current leakage. To solve the problem of this type of rectifiers, auxiliary circuits are usually used to supply part of the threshold voltage of the transistors and the so-called threshold voltage compensation is done in [25]. The structure of this system is such that it compensates for the threshold voltage using four-stage combinations. These compounds consist of transistors that are in the sub-threshold region. Using this structure, Dickson’s low-sensitivity problem is partially solved, and the circuit has a high-power conversion efficiency over a wide range of input powers. Compensation is also done in such a way that the level of compensating voltages is limited and varies according to the input power. In this work, a kind of intelligent compensation has been done.

A differential rectifier is shown in Fig. 2b [13]. In the steady-state and when this circuit operates in its positive cycle, the gate of transistor MN1 is tied to the positive voltage, and its source is tied to the negative voltage, so in this state, this transistor is on. Simultaneously, the source of transistor MP2 is linked to the positive voltage, and its gate to a negative voltage, making it also on. In this case, we will have a loop that transmits the input power to the circuit, rectifies the signal, and charges the output capacitor. Likewise, transistors MN2 and MP1 will be on when the circuit is in its negative cycle, forming another charge loop. This rectifier can work at low power with high PCE. Transistors in this structure operate in the linear region, so these transistors will have a lower voltage drop resulting in less power being lost in the rectifier itself. The disadvantage of this rectifier type is the high reverse current of these transistors at higher input powers.

Auxiliary feedback circuits are used to solve this problem. In Fig. 3, a structure is introduced by utilizing transistors to generate a feedback network from the output to the gate of P-type transistors. This feedback network turns off the P-type transistors at high input power levels to prevent the discharge of the output energy. Unfortunately, this structure reduces the output resistance. Also, this configuration does not offer a path to improve efficiency at low capacities [21]. In [22], instead of using the large feedback circuit, only resistors RFB1 and RFB2 are used. As illustrated in Fig. 4, these two resistors have a very large value. Although this method increases the dynamic range in the rectifier, it limits the input current and reduces the efficiency at high input powers.

Differential rectifier using transistor feedback network presented in [21]

Proposed differential rectifier using resistors as a feedback system in [22]

The circuit illustrated in Fig. 5 presents a less defective structure compared to others [2]. As can be seen, in this configuration, the auxiliary circuit endeavors not to disturb the input current. This reference suggests the usage of diode-connected transistors. Specifically, transistors D1 and D2 remain off at low input powers. However, at higher input powers, when the output voltage exceeds the input voltages, these diodes activate to turn off the main P-type transistors. Consequently, the return current from these transistors is significantly reduced. Unfortunately, the return current of N-type transistors is not considered in this structure. On the left side of the circuit, diode-connected transistors are employed. These transistors are introduced to boost the input current, but due to their high threshold voltage, they typically remain off and do not contribute positively to the circuit.

Differential rectifier using diode-connected transistors, presented in [2]

In [19], a novel high dynamic range rectifier has been suggested, which reduces reverse current, increases forward current, and ultimately, improves the rectifier’s PCE, sensitivity, and DR. This paper provides detailed circuit operation and analysis, along with extensive post-layout simulation results. Additionally, the design of the input impedance matching network and the entire energy harvesting system is reported.

The remainder of the paper is organized as follows: Sect. 2 presents the structure of the proposed RF energy harvesting system with a detailed description and analysis of the proposed CMOS rectifier. Post-layout simulation results are provided in Sect. 3. The conclusion is presented in Sect. 4.

2 Proposed RF Energy Harvesting System

In this section, the proposed RF energy harvesting system is described, with the rectifier at its core being initially expounded upon. The second part covers the rest of the circuit, including the matching network, balun, and antenna.

2.1 Proposed Differential Rectifier

As shown in Fig. 6a, the proposed rectifier consists of a conventional differential rectifier and 8 diode-connected PMOS transistors. These diode-connected transistors, which we call diodes in this article, give the feed-forward and feedback routes for this circuit. The D1-D4 diodes provide a feedback path and reduce the return current at high input power levels. Also, the D5-D8 diodes provide a feed-forward path, enhancing the power reception of the rectifier at low or medium input power levels.

In the conventional differential rectifier, when the input power is high, the absolute values of VDC+ and VDC− exceed VRF+ and VRF−. In this scenario, the drain and source of MP1, MP2, MN1, and MN2 transistors are swapped, transforming the sources into drains and vice versa. When this happens, the rectifier begins to discharge the output capacitor, and drain its energy to reach equilibrium. This significantly reduces PCE at high input powers, consequently diminishing the DR. To counteract this situation, as illustrated in Fig. 6a, D1–D4 diodes are employed. In this case, because the absolute value of VDC+ and VDC- are larger than VRF+ and VRF−, the anode voltage of these diodes is greater than their cathode and high threshold voltage. So, D1 and D4 (in negative cycle), and D2 and D3 (in positive cycle) become ON and turn off MP1, MN2, MP2, and MN1 transistors, respectively. Whit these switches (MP1, MP2, MN1, and MN2 transistors) turned off, there is no pathway to discharge the output capacitor. Consequently, PCE remains unaffected, and the DR stays wide. It’s essential to note that the mentioned circuit utilizes transistors MN1, MN2, MP1, and MP2 as switches, functioning in either an “on” or “off” state. These transistors undergo changes in their states as time progresses, ultimately reaching a stable state. As a result, the circuit and its transistors lack a fixed bias point. The steady-state process of the rectifying system at high input power levels for MP2 transistor is shown in Fig. 6c.

To reduce the PCE loss, the current passing into the diodes should be low. When a PMOS diode-connected transistor operates in the saturation region, its drain-source current is given by:

and in the sub-threshold region, it is described as:

where n is dependent on the process, W/L is the transistor’s aspect ratio, VTH is the threshold voltage, VT is the thermal voltage, and Ids0 is dependent on the aspect ratio and the process. As explained in [2], and according to the relations (1) and (2), the current passing through these diodes is directly proportional to their aspect ratio and inversely proportional to their threshold voltage. As a result, we have opted for a smaller aspect ratio, achieved by utilizing a longer channel length for these diodes. Also, we use high threshold voltage (HVT) PMOS transistors to realize D1–D4 diodes.

Similarly, D5–D8 diodes provide feed-forward paths in the circuit. These diodes are added to the rectifier to increase forward input current. When the circuit operates at low or medium input power levels, the output voltage is still lower than VRF+ and VRF−. As a result, these diodes can turn on, creating an additional path for charging the output capacitor. All these explanations are presented in Fig. 6b and c.

A better understanding of the functions of self body biasing (SBB) and HVT diodes in a circuit can be achieved by comparing the PCE in various situations. This encompasses a standard circuit without diodes, a circuit containing solely SBB diodes, and a circuit employing only HVT diodes. It is clear that SBB diodes enhance PCE at lower input powers, while HVT diodes enable higher peak PCE and increased efficiency levels at higher input powers. This description is illustrated in Fig. 7.

According to relations (1) and (2), it is obvious that if the threshold voltage of D5–D8 diodes becomes lower, these diodes turn on sooner and can have a better effect on the circuit. It is also crucial that the reverse current in these diodes be smaller. By utilizing the SBB technique, beneficial in low-power systems, we can achieve both advantages. As shown in Fig. 8, in this technique, the transistor’s bulk is connected to its drain instead of connecting to the source. In this case, when the diode is ON (VS > VG), according to relation (3), the absolute value of threshold voltage is less than |VTH0|. Whereas when the bulk is connected to its source, its |VTH| becomes larger than or equal to |VTH0|.

In this context, VTH0 represents the threshold voltage without body effect, γ denotes the body effect coefficient, VBS is the voltage difference between the bulk and source terminals, and the formula for the Fermi level (ϕF) is given by ϕF = (kT/q) ln (Nsub/ni), where k represents Boltzmann’s constant, q symbolizes the elementary charge of an electron, Nsub stands for the doping density of the substrate, and ni denotes the electron density in undoped silicon [24]. The typical value of 2ϕF is about 0.7 V [24].

Also, when the diode is OFF (VS < VG), the positions of the source and drain terminals change with each other. In this situation, the new source-bulk voltage equals zero, while these diodes still exhibit a reverse current. We know that the higher the threshold voltage, the lower the leakage current. Under these conditions, according to (3), the absolute value of the new threshold voltage is larger than |VTH0|, reducing the return current. In simple terms, this technique improves the performance of the proposed circuit when D5–D8 diodes are either ON or OFF by providing large feed-forward and small reverse currents in ON and OFF states, respectively. Additionally, proper transistor sizing helps achieve balanced operation, minimize distortion, and improve efficiency in converting RF to DC signals. Proper transistor sizing is paramount in achieving balanced operation, minimizing distortion, and improving the efficiency of RF to DC signal conversion. Our approach to selecting transistor sizes revolves around ensuring symmetry between NMOS and PMOS transistors, a critical factor in maintaining balanced signal paths. Notably, we aim for consistent behavior from both transistor types. Due to the inherent difference in charge carrier mobility, with PMOS transistors exhibiting lower mobility compared to NMOS transistors, a deliberate decision was made to size the PMOS transistors five times larger than their NMOS counterparts. This intentional disproportionality is designed to counterbalance the impact of the mobility difference and attain the desired equilibrium in circuit behavior.

Alternating currents and charges of MP2’s drain are shown in Figs. 9 and 10 for the conventional and proposed rectifiers. These currents and charges are in steady state mode and represent the required amounts for generating a 1.5 V DC output. As expected, both circuits need an equal net charge to produce the same output voltage for the same loads. However, the range of forward and reverse charges in the conventional rectifier is several times larger than that of the proposed rectifier. This shows that the proposed circuit can provide the same voltage and charge at lower input power levels.

2.2 Matching Network

As shown in Fig. 11, we modeled the antenna with an RF voltage source and a 50 Ω resistor. Additionally, an off-chip balun is used to convert the single-ended input signal to a differential one. The circuit needs an input impedance matching network to transfer the maximum power from the antenna and balun to the rectifier. Moreover, because the input signal has a low voltage at the start-up of the circuit, this matching circuit serves as a passive voltage amplifier according to relation (4).

where VRec is the voltage at the input of the rectifier, VRF is the voltage of the source, and Q is the quality factor of the circuit. In this case, due to the increase of the rectifier’s input voltage, the dead zone decreases, the sensitivity increases, and the circuit starts working sooner.

In this paper, a π-type input impedance matching circuit is used. Because the circuit operates in large-signal mode and lacks direct bias, it is very difficult to design an impedance matching circuit. The input impedance of the rectifier varies with frequency, the amount of input power, and the amount of input voltage. We use the iteration technique in this situation. In the first step, the matching operation is performed for the amount of rectifier impedance observed in the non-matching mode. The mentioned matching circuit is designed and added to the rectifier circuit. Then, after doing this, the rectifier is optimized again with new values. After this step, the input impedance of the rectifier is revaluated, and a new matching circuit is designed for this new impedance. This will take several iterations and then converge to a constant value. The condition for the convergence of this value is the selection of the appropriate initial value. The loop in Fig. 12 will be rotating and repeating until the observed impedance from the rectifier head converges to a certain amount. It should be noted that naturally, after performing the necessary iterations, the impedance seen from the matching circuit should correspond to the impedance observed from the antenna and the balun. At the end, this circuit is matched at Pin = − 19.5 dBm and f = 900 MHz.

3 Post-layout Simulation Results

The structure introduced in this paper is crafted utilizing the 180 nm RF-CMOS process through cadence design systems. This choice of design and fabrication platform allows us to demonstrate the circuit’s performance. Also, the ADTL2-18 + is employed as an off-chip balun due to its suitable parameters for this application. These parameters are low S11, creating low phase differences between the two sides of the differential signal. Layouts of the proposed and conventional rectifier and on-chip matching capacitor (Cm2) are shown in Fig. 13. Cm2 is sized at 365 fF, a value suited for on-chip dimensions. Nonetheless, larger inductors and capacitor are needed for Lm1, Lm2, and Cm1, making it more pragmatic to place them outside the chip. As illustrated in Figs. 11 and 13, Cm2 occupies the initial position on the left side of the IC. Hence, it is viable to establish a direct connection between Cm2 and the rest of the components within the matching network situated externally to the chip. Metal–insulator–metal (MIM) capacitors are used for capacitors, NMOS2V transistors are used for N-type transistors, PMOS2V transistors are used for P-type transistors and feedforward diodes, and PMOS3V transistors are used for high-threshold diodes. It is noteworthy to mention that the transistors are not shielded in this layout. Additionally, it is important to highlight that in the case of the rectifier-only design, the calculation of the net RF input power supplied to the rectifier can be ascertained using the subsequent equation.

where PRF signifies the net RF input power for the rectifier, PSig represents the RF power source from the signal generator, and S11 corresponds to the rectifier’s input reflection coefficient [7]. Also, as a summary, Table 1 encapsulates the value of designed device components.

It is important to note that in evaluating differential rectifiers, only the results of the matching and rectifier circuit sections are taken into account, and the impact of the antenna and balun is excluded from consideration. This approach ensures fair comparisons, eliminating the influence of the balun and antenna (particularly the balun) on the results. In this paper, we present the results in both scenarios.

Figure 14a illustrates the S11 results versus the input frequency at − 19.5 dBm input power, and Fig. 14b demonstrates this result in terms of input power at 900 MHz input frequency. As shown in Fig. 14, this circuit exhibits an S11 = − 38 dB at the desired frequency and input power. As explained in Sect. 2.2, the input impedance of the rectifier is influenced by factors such as frequency and input power. Considering that the rectifier exhibited its highest power conversion efficiency (PCE) around − 20 dBm input power, we developed a dedicated matching system aimed at achieving optimal alignment at this power level and a frequency of 900 MHz. Leveraging the proposed wide dynamic range CMOS differential rectifier and having a grasp of the expected input power, it becomes possible to fine-tune the matching circuit accordingly. This adjustment enables the realization of the highest attainable output power. It is important to note that this study focuses on an IoT application, where the input power typically is around − 20 dBm.

Figure 15 shows the PCE and output voltage for the rectifier and total system in conventional and proposed structures. As depicted in Fig. 15a and b, the input power is changing from Pin = − 30 dBm to Pin = − 10 dBm. This leads to a corresponding output voltage range, varying from VDC = 0.2 V to VDC = 1.79 V. The PCE for the proposed rectifier is 86.03%, which offers an improvement of 5.03% compared to the conventional rectifier. According to Fig. 15a, the dynamic range of the proposed structure is 9.76 dB, which is 3.5 dB more than the conventional circuit. According to Fig. 15b, the rectifier sensitivity used in this paper equals − 19.3 dB, which shows an improvement of 5.01 dB compared to the conventional circuit. These improvements directly translate to increased energy extraction from the available input, enabling more efficient energy conversion and utilization. With higher PCE, a greater portion of the harvested energy can be effectively converted into usable power, enhancing the overall performance of energy harvesting devices. Additionally, the improved DR allows for better signal reception and adaptability to varying input conditions, ensuring reliable operation even in challenging scenarios. Therefore, these advancements contribute to the viability and effectiveness of energy harvesting technologies, particularly in applications where low input power is the norm.

To examine the robustness of the designed circuits, the sensitivity and PCE of both proposed rectifier and total system over process corners and temperature variations have been done and the results are illustrated in Fig. 16 and summarized in Table 2. According to Fig. 16 and Table 2, the results are very well matched and meet expectations. Therefore, the circuit is less sensitive to temperature changes and technology corner cases.

The main load of the circuit has a value of 100 kΩ. The reason for selecting this load is its suitability for IoT applications and radio wave identification systems. However, to demonstrate the versatility and superior performance of the proposed rectifier circuit across various loads (different applications), we also analyze it with loads of 30 kΩ and 80 kΩ. The results of these simulations are observed in Fig. 17.

Tables 3 and 4 are provided to compare both the proposed rectifier and total RF energy harvesting system, including antenna and balun with several other previous works. The proposed structure has higher sensitivity, better PCE, and a wider dynamic range than previous works. Reference [13] has the maximum efficiency between the references, but with low sensitivity and dynamic range. Reference [6] shows high efficiency, and has good sensitivity, but the proposed structure has better parameters and has created a wider dynamic range. Diode (diode-connected transistors) network techniques have been used in [2] and [6]. Due to balun and antenna losses, the results of the entire system are slightly lower than the results of the rectifier and the matching network. Usually, systems with differential rectifiers are not systematically compared to other energy harvesting systems. However, in this paper, in addition to comparing the designed rectifier with similar works, we compare the total system with other systems. As shown in Table 4, in terms of PCE, it has achieved better results than all previous works. The sensitivity of the proposed circuit is less than [20, 25], and [11]. The reason is the high load of these references when calculating the sensitivity.

4 Conclusion

This paper introduces a rectifier structure that decreases the return current at high input power levels and enhances the forward current at low input power levels. The performance of diode-connected transistors, acting as feedback and feedforward paths, enhances the rectifier’s PCE and DR. According to the detailed post-layout simulations in a 180 nm CMOS process, the proposed rectifier’s PCE and DR are 86.03% and 9.76 dB, respectively, with a sensitivity of − 19.3 dBm at 900 MHz at 1 V output voltage across a 100 kΩ resistive load. Also, because of this improvement at the rectifier, the total system’s results are 76.13% and 6.3 dB for PCE and DR with a sensitivity of − 18.75 dBm for the same condition with the rectifier.

Data availability

Data sharing is not applicable to this article as no datasets were generated or analyzed during the current study.

References

M.A. Abouzied, K. Ravichandran, E. Sánchez-Sinencio, A fully integrated reconfigurable self-startup RF energy-harvesting system with storage capability. IEEE J. Solid-State Circuits 52(3), 704–719 (2017)

A.S. Almansouri, M.H. Ouda, K.N. Salama, A CMOS RF-to-DC power converter with 86% efficiency and − 19.2-dBm sensitivity. IEEE Tran. Micro. Theory Tech. 66(5), 2409–2415 (2018)

M. Ashraf, A maximum power-point tracking multiple-input thermal energy harvesting module. AEU Int. J. Electron. Commun. 121, 153231 (2020)

M. Barati, M. Yavari, A power conversion chain with an internally-set voltage reference and reusing the power receiver coil for wireless bio-implants. Microelectron. J. 74(4), 69–78 (2018)

S.C. Chandrarathna, J.-W. Lee, A self-resonant boost converter for photovoltaic energy harvesting with a tracking efficiency >90% Over an ultra-wide source range. IEEE J. Solid-State Circuits 57(6), 1865–1876 (2022)

G. Chong, H. Ramiah, J. Yin, J. Rajendran, P. Mak, R.P. Martins, A wide-PCE-dynamic-range CMOS cross-coupled differential- drive rectifier for ambient RF energy harvesting. IEEE Trans. Circuits Syst. II Express Briefs 68(6), 1743–1747 (2021)

A. Choo, Y.C. Lee, H. Ramiah, Y. Chen, P.-I. Mak, R.P. Martins, A high-PCE range-extension CMOS rectifier employing advanced topology amalgamation technique for ambient RF energy harvesting. IEEE Trans. Circuits Syst. II Express Briefs 70(10), 3747–3751 (2023)

K.K.P. Churchill, H. Ramiah, G. Chong, Y. Chen, P.-I. Mak, R.P. Martins, A fully-integrated ambient RF energy harvesting system with 423-µW output power. Sensors 22(12), 4415 (2022)

J.F. Dickson, On-chip high-voltage generation in MNOS integrated circuits using an improved voltage multiplier technique. IEEE J. Solid-State Circuits SC-11(3), 374–378 (1976)

U. Guler, Y. Jia, M. Ghovanloo, A reconfigurable passive RF-to-DC converter for wireless IoT applications. IEEE Trans. Circuits Syst. II Express Briefs 66(11), 1800–1804 (2019)

D. Khan, S.J. Oh, K. Shehzad, M. Basim, D. Verma, Y.G. Pu, M. Lee, K.C. Hwang, Y. Yang, K.-Y. Lee, An efficient reconfigurable RFDC converter with wide input power range for RF energy harvesting. IEEE Access 8, 79310–79318 (2020)

H. Kim, I. Kwon, Design of high-efficiency CMOS rectifier with low reverse leakage for RF energy harvesting. Electron. Lett. 55(8), 446–448 (2019)

K. Kotani, A. Sasaki, T. Ito, High-efficiency differential-drive CMOS rectifier for UHF RFIDs. IEEE J. Solid-State Circuits 44(11), 3011–3018 (2009)

W.W.Y. Lau, L. Siek, 2.45 GHz wide input range CMOS rectifier for RF energy harvesting, in 2017 IEEE Wireless Power Transfer Conference (WPTC) (2017), pp. 1–4

C.-J. Li, T.-C. Lee, 2.4-GHz High-efficiency adaptive power harvester. IEEE Trans. VLSI Syst. 22(2), 434–438 (2014)

L.-X. Liu et al., An ultra-low-power integrated RF energy harvesting system in 65-nm CMOS process. Circuits Syst. Signal Process. 35(2), 421–441 (2016)

Y.-L. Lo, W.-H. Chuang, A high-efficiency CMOS rectifier with wide harvesting range and wide band based on MPPT technique for low-power IoT system applications. Circuits Syst. Signal Process. 36(12), 5019–5040 (2017)

Y. Lu, H. Dai, M. Huang, M.-K. Law, S.-W. Sin, U. Seng-Pan, R.P. Martins, A wide input range dual-path CMOS rectifier for RF energy harvesting. IEEE Trans. Circuits Syst. II Express Briefs 64(2), 166–170 (2017)

A. Mahsafar, M. Yavari, A high dynamic range differential rectifier for RF energy harvesting, in 29th Iranian Conference on Electrical Engineering (ICEE) (2021), pp. 124–128

S.M. Noghabaei, R.L. Radin, Y. Savaria, M. Sawan, A high-efficiency ultra-low-power CMOS rectifier for RF energy harvesting applications, in 2018 IEEE International Symposium on Circuits and Systems (ISCAS) (2018), pp. 1–4

M.H. Ouda, W. Khalil, K.N. Salama, Wide-range adaptive RF-to-DC power converter for UHF RFIDs. IEEE Microw. Wirel. Compon. Lett. 26(8), 634–636 (2016)

M.H. Ouda, W. Khalil, K.N. Salama, Self-biased differential rectifier with enhanced dynamic range for wireless powering. IEEE Trans. Circuits Syst. II Express Briefs 64(5), 515–519 (2017)

P. Prakasam, T.R. Suresh Kumar, T. Velmurugan, S. Nandakumar, Efficient power distribution model for IoT nodes driven by energy harvested from low power ambient RF signal. Microelectron. J. 98, 104665 (2020)

B. Razavi, Design of Analog CMOS Integrated Circuits, 2nd edn. (McGraw-Hill, New York, 2016)

P. Saffari, A. Basaligheh, K. Moez, An RF-to-DC rectifier with high efficiency over wide input power range for RF energy harvesting applications. IEEE Trans. Circuits Syst. I Regul. Pap. 66(12), 4862–4875 (2019)

N. Shafiee, S. Tewari, B. Calhoun, A. Shrivastava, Infrastructure circuits for lifetime improvement of ultra-low power IoT devices. IEEE Trans. Circuits Syst. I Regul. Pap. 64(9), 2598–2610 (2017)

J.K. Yong, et al., A fully integrated CMOS tri-band ambient RF energy harvesting system for IoT devices, in IEEE Transactions on Circuits and Systems I: Regular Papers (2023)

P.W. Yuen, G. Chong, R. Harikrishnan, A high efficient dual-output rectifier for piezoelectric energy harvesting. AEU Int. J. Electron. Commun. 111, 152922 (2019)

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interests

The authors declare that they have no known competing financial interests or personal relationships that could have appeared to influence the work reported in this paper.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Mahsafar, A., Yavari, M. A Wide Dynamic Range CMOS Differential Rectifier for Radio Frequency Energy Harvesting Systems. Circuits Syst Signal Process 43, 2658–2674 (2024). https://doi.org/10.1007/s00034-024-02607-3

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-024-02607-3