Abstract

In current work, the microstructure and optical and electrical properties of sol–gel-derived Gd-doped ZrO2 gate dielectric thin films as functions of annealing temperatures were systemically investigated. Analyzes by x-ray diffraction have indicated that the 240 °C-baked sample as well as those samples annealed at lower temperatures keep amorphous state. In the sample annealed at 500 °C, however, the amorphous phase disappears and tetragonal ZrO2 is formed. Measurements from ultraviolet-visible spectroscopy (UV/Vis) have demonstrated that transmittance of all samples in the visible region is approximately 80% and the increase in band gap energy has been found with increasing the annealing temperature. Electrical properties of all samples based on Al/Si/ZrGdOx/Al MOS capacitor have been investigated by using semiconductor device analyzer. Through the analysis and calculation of the electrical characteristic curves, solution-processed Al/ZrGdOx/Si/Al capacitor shows improved performances at a annealing temperature of 400 °C, such as high dielectric constant (k) of 16.56, lowest oxidation charge density (Q ox) of −0.74 × 1012 cm−2, and boundary trap oxidation charge density (N bt) of 3.17 × 1012 cm−2. In addition, the leakage current mechanism for 400 °C-annealed sample has been discussed in detail.

Graphical Abstract

solution-processed Gd-doped ZrO2 gate dielectric films were realized. Al/ZrGdOx/Si/Al capacitor shows optimized and improved performances at a annealing temperature of 400 °C.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

With the development of the semiconductor industry, the feature size of complementary metal-oxide-semiconductor field effect transistors (CMOSFETs) is becoming smaller and smaller. As a result, the thickness of traditional SiO2 gate dielectrics has reached its physical limits due to high leakage current from channel to gate. By far, many high-k gate dielectrics have been paid more attention to replace conventional SiO2 gate dielectrics due to its relatively large dielectric constant, suitable band gap, and excellent thermal stability in contact with Si [1,2,3,4]. Among these high-k gate dielectrics, ZrO2 has been investigated extensively for its excellent performance, including large dielectric constant of 25, large band gap of about 5.8 eV, and outstanding physical and chemical stability [5,6,7]. However, for ZrO2-based high-k gate dielectrics, there still exist some challenges, including the lower crystallization temperature and the oxygen vacancies existed in films, which lead to the formation of uncontrollably increased leakage current and degrade the performance of MOSFET devices. It has been reported that Gd incorporation into high-k ZrO2 gate dielectrics can reduce oxygen vacancies, enlarge the band gap, increase the crystallization temperature, and optimize the electrical properties. By far, much works have been committed to investigate the effect of Gd incorporation on the thermal stability, interfacial and electrical properties of sputtering-derived ZrO2 high-k gate dielectric thin films [8,9,10,11]. However, few work has been carried out to study the effect of annealing temperature on the structural and optical and electrical properties of the solution-processed Gd-doped ZrO2 high-k gate dielectric thin films. Compared with physical vapor deposition, chemical vapor deposition, and atomic layer deposition (ALD) [12,13,14,15], solution-based method is gradually attracting more attention due to its simple operation, controllable molar ratio of elements, low cost and large-scale production [16,17,18].

In current work, solution-processed Gd-doped ZrO2 high-k gate dielectric thin films were spin-coated on Si and quartz substrate, respectively. By means of characterizations from x-ray diffraction (XRD), spectroscopy ellipsometry (SE), ultraviolet-visible spectroscopy (UV/Vis), and semiconductor device analyzer, the effect of rapid thermal annealing temperature on the structural and optical and electrical properties of solution-derived Gd-doped ZrO2 high-k gate dielectric thin films were investigated systematically.

2 Experimental details

2.1 Preparation of the precursor solutions

The Gd-doped ZrO2 precursor solution was synthesized through dissolving a mixture of Zirconium oxychloride octahydrate (ZrOCl2•8H2O) and Gadolinium nitrate hexahydrate (Gd2(NO3)3) in 2-methoxyethanol (C3H8O2) solution (AR) with Zr/Gd molar ratio of 9:1. The precursor solution was stirred at room temperature for 360 min by a magnetic stirrer. Then, to get a more pure sol solution, the solutions were filtered through a 0.22 μm injection filter before spin coating.

2.2 Film deposition

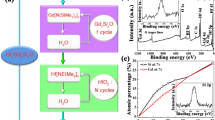

First of all, all substrates such as n-type Si (100) wafers and quartz wafers were cleaned by a modified RCA (Radio Corporation of American) to remove surface impurities, and then all the wafers were immersed in a solution of 1% hydrofluoric acid for about 15 s to remove native SiO2. Finally, all Si wafers and glass substrates dried by N2 gun were placed in a plasma cleaner to enhance the hydrophilicity of the substrate surface. All the samples were prepared initially by a sol–gel machine at 5000 r.p.m. for 25 s, and then the thin films were placed on the roaster and baked at 240 °C for 5 min to remove the residual solvent and cooled to room temperature. To obtain the desired thickness, the procedure was repeated several times. For XRD characterization, the procedure was repeated five times. For electrical measurements, only one time was done. Finally, all thin films were annealed in vacuum environment (4.6 × 10−5 mbar) with annealing temperatures ranging from 400 to 600 °C for 5 min. The details of the preparation of the ZrGdOx thin films are shown in Fig. 1. The microstructure of Gd-doped ZrO2 gate dielectric thin films related with annealing temperature were investigated by XRD. The thickness of Gd-doped ZrO2 thin films was obtained by spectroscopy ellipsometry (SE) (SC630, SANCO Co, Shanghai). The ultraviolet-visible spectroscopy (UV/Vis) was carried out to investigate the annealing temperature-dependent band gap and transmittance spectra of the Gd-doped ZrO2 gate dielectric thin films.

2.3 Electrical performance measurements

In order to measure the electrical properties of the Gd-doped ZrO2 thin films, MOS capacitors based on ZrGdOx/Si gate stack were fabricated. The aluminum electrode with an area of 3.14 × 10−8 m2 was sputtered to deposit on the top surface of samples. In order to keep ohmic contact, the back electrode was deposited by sputtering Al disk. The capacitance-voltage (C-V) and the leakage current density-voltage (J-V) of Al/ ZrGdOx/Si/Al MOS capacitors as a function of annealing temperature were measured by using an Agilent B1500A semiconductor device analyzer. All electrical measurements were performed at room temperature in a dark shelter.

3 Results and discussion

3.1 Microstructure investigation

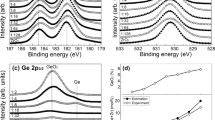

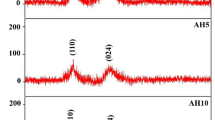

Figure 2 shows the XRD patterns of Gd-doped ZrO2 gate dielectric thin films annealed at various temperatures. Based on Fig. 2, it can be noted that the 240 °C-baked Gd-doped ZrO2 gate dielectric thin films are in an amorphous state. Annealing the samples in 400 °C, amorphous state still keeps and no crystallization has been detected. It is well known that microstructure is an important factor to affect the electrical properties of high-k gate dielectric thin films. For application in CMOS device, the amorphous states for high-k gate dielectrics are desirable due to their lower surface roughness and lower leakage current density [19, 20]. However, with rising the annealing temperature to 500 °C, the amorphous ZrO2 disappears and new diffraction peaks have been observed, indicating that the crystallization for amorphous Gd-doped ZrO2 thin films takes place at 500 °C, which is higher than previous results investigated by Chang [18]. Those four peaks located at 30.4, 35.1, 50.6, and 60.1°, corresponding to T(011), T(110), T(020), T(121), are attributed to the tetragonal phase of ZrO2, which is in good agreement with the observations reported by Park [21]. Continuing increasing the annealing temperature to 600 °C, it can be seen that the intensity of the strong peak (011) of tetragonal ZrO2 increases obviously, indicating that higher annealing temperature leads to the full crystallization of Gd-doped ZrO2 gate dielectric thin films. Based on previous analyzes, it can be concluded that the crystallization of Gd-doped ZrO2 gate dielectric thin films can be controlled by the annealing temperature.

3.2 Optical properties analysis

For high-k gate dielectrics, the investigation of optical constants, such as optical band gap, transmittance spectra and the absorption spectra, will offer the criterion for choosing the suitable gate dielectrics for CMOS devices. Therefore, in current work, the evolution of the optical properties of solution-derived ZrGdOx thin films deposited on quartz glass was determined by UV/Vis measurements. Figure 3 shows the transmittance spectra as a function of annealing temperature with the range of wavelength from 190 to 900 nm. As demonstrated in Fig. 3, the average transmittance spectra of all samples at different annealing temperatures are about 80% in the visible region. To obtain the band gap of Gd-doped ZrO2 gate dielectric thin films, UV/Vis absorption spectra of the ZrGdOx gate dielectric thin films annealed at various temperatures has been illustrated in Fig. 4.

The band gap of the ZrGdOx films can be obtained by the following formula [22, 23]:

in which hν is the photon energy, α is absorption coefficient and A is a semiconductor constant characteristic. The transition type of photoelectron between valence band and conduction band determines the value of the index n. Based on the different values of n, it can be determined whether this band gap is a direct band gap or an indirect band gap [24]. In current work, the optical direct band gaps of the ZrGdOx films were obtained through the linear tangent part of the curve relating (αhν)2 and (hν) to (αhν)2=0. As demonstrated in Fig. 4, the optical direct band gaps have been determined to be 5.60, 5.78, 5.89, and 5.94 eV, respectively, with the increase of the annealing temperature. It is reported that the localized states is an important factor to affect the band gap. The localized states in the band structure attributed to the presence of defects and disorders in the films leads to the low energy gap. And high temperature annealing helps to reduce the oxygen vacancy and disorders in the film, so the density of the local state also decreases. Therefore the band gap increases while the annealing temperature increases [25].

3.3 Electrical properties observations

Figure 5 shows the C-V curves of Al/ZrGdOx/n-Si MOS capacitors measured at 1 MHz. As demonstrated in Fig. 5, all the C-V curves show smooth characteristics in the scan region from −1.5 to 1 V and the 400 °C-annealed sample demonstrates the highest accumulation capacitance C ox of 531 pF. Based on the following equations and the accumulated capacitance in the C-V curves, the equivalent oxide thickness (E ot) and the relative dielectric constants (k hk) of the ZrGdOx gate dielectric thin films have been determined [26]:

in which kSiO2 is the relative dielectric constant of the SiO2, ε o is the vacuum capacitance, C ox is the accumulated capacitor, A is the surface area of the aluminum electrode, t hk and t SiO2 are the thicknesses of ZrGdOx films and SiO2 layer, respectively. As shown in Table 1, the smallest equivalent oxide thickness of 2.04 nm and the highest dielectric constant of 16.56 have been obtained for the 400 °C-annealed sample. It can be seen that with the annealing temperature increasing from 400 to 600 °C, the dielectric constants of ZrGdOx films show a decreased trend, which can be attributed to the high temperature-induced formation of the low-k interfacial layer [27]. The flat band capacitance C fb is calculated by the following formula [28]:

where ε ro is the dielectric constant of ZrGdOx thin film, N A is the doping concentration of substrate, εrs is the dielectric constant of the Si substrate, N A is the carrier concentration and t hk is the thickness of the film, respectively. The value of flat band voltage V fb and hysteresis ΔV fb can be determined based on the C fb values from C—V curve respectively. According to Table 1, it can be noted that ZrGdOx gate dielectric thin film annealed at 400 °C has the lowest flat band voltage. As we know, the flat band voltage has been determined by the traps and defects located at interface layer. Therefore, it can be concluded that the samples annealed at 400 °C have less defects and traps and contributes to the lowest flat band voltage [29,30,31,32,33]. The oxidation charge density Qox can be expressed by the following equation [28]:

where ϕ ms is the work function difference between metal electrode and silicon substrate, A is the area of Al electrode and q is electricity of charge. From Table 1, the Q ox of the 240 °C-baked, 400, 500, and 600 °C-annealed samples were calculated to be 1.67 × 1012 cm−2, −0.74 × 1012 cm−2, 1.50 × 1012 cm−2, and 4.94 × 1012 cm−2, respectively. Based on previous reports, it can be concluded that the large negative V fb shift and the negative Q ox can be due to the presence of oxygen vacancies, the interface state and defects [34].

The boundary trap oxidation charge density (N bt) was calculated by using following expression [35, 36]:

As demonstrated in Table 1, the Q ox and N bt are lower than other samples when the annealing temperature is fixed at 400 °C, indicating that 400 °C-annealed sample has demonstrated the improved interfacial quality.

Figure 6 shows the J-V curves for Al/ZrGdOx/n-Si MOS capacitors with different annealing temperatures. Based on Fig. 6, it can be seen that the leakage current density for the 240 °C-baked and the annealed samples at 400, 500, and 600 °C is 5.15 × 10−4 A/cm2, 2.28 × 10−5 A/cm2, 7.36 × 10−5 A/cm2, 1.90 × 10−4 A/cm2, respectively, when the gate voltage is fixed at 2 V. Indrek [10] has reported that the leakage current density of 6-nm-thick ZrxGdyOz gate dielectrics prepared by ALD is 10−6A/cm2 at 1 V, and reaches to about 10−5 A/cm2 at 2 V, which is similar to our result. As we know, ALD can prepare highly uniform and dense film and has an excellent prospect in the manufacture of microelectronic device. In our current work, solution-based method was selected and the electrical properties of gate dielectrics was very close to ALD method. Compared to other samples, 400 °C-annealed sample demonstrate the lowest leakage current density, which can be attributed to the lower interface states density at ZrGdOx/Si interface [37]. With the increase of annealing temperature, the leakage current densities increase, which is probably due to the reduced conduction band offset caused by the high oxide charge and trap charge with the increase of annealing temperature based on previous C-V results [38]. In addition, the high annealing temperature leads to the crystallization of ZrGdOx gate dielectric thin films and attributes to the increased leakage current.

According to previous analyzes, it can be concluded that ZrGdOx gate dielectric thin film annealed at 400 °C demonstrates the improved electrical performance and optimized electrical parameters, suggesting that 400 °C-annealed sample has potential application in CMOSFET devices.

3.4 Leakage current mechanism analysis

In order to investigate the leakage current conduction mechanisms of the ZrGdOx gate dielectric thin films, the Schottky emission (SE), Ohmic conduction and direct tunneling were analyzed for samples annealed in 400 °C by linear curve fitting method. Schottky emission is a field-assisted thermionic emission of an electron over a surface barrier, which is the most likely current conduction mechanism in gate dielectrics [39]. The leakage current density determined by SE is given by [40]:

in which A is the effective Richardson constant, φ B is the Schottky barrier height, T, qϕ B , E, ε o , ε r , and k B , are the absolute temperature, the trap barrier height between semiconductor and oxide, the electric field in oxide, the vacuum permittivity, the dynamic dielectric constant and the Boltzmann constant, respectively. Figure 7a presents the plot of \({\rm{ln}}\left( {J/{T^2}} \right)\) vs. E (1)/(2) for the ZrGdOx gate dielectrics thin films at low electric field (0.07 < E < 0.44 MV/cm), indicating that the J-E curve measured in low electric fields fits well with the schottky emission. In addition, Ohmic conduction is caused by the movement of mobile electrons in the conduction band and holes in the valence band. Figure 7b shows the plot of J vs. E and the good and linear fitting at low electric field indicates the existence of Ohmic conduction mechanism. When the electric field has been increased to higher than 0.50 MV/cm, leakage conduction mechanism has been replaced by other mode. The plot of Eln(J/E 2)vs. E 3/2at different annealing temperatures is presented in Fig. 7c, indicating the existence of direct tunneling when the electric field is higher than 1.64 MV/cm.

Leakage current conduction mechanism of Al/ZrGdOx/Si MOS capacitors annealed at 400 °C under substrate injection. a The curve of ln(J/T 2) vs E (1)/(2) in low electric field; b the curve of J vs E in low electric field; c the curve of \(E\,{\rm{ln}}\,\left( {J/{E^2}} \right)\)vs E (3)/(2) in high electric field

4 Conclusion

In summary, the microstructure, optical and electrical properties of ZrGdOx gate dielectric thin films deposited by sol–gel method as functions of annealing temperatures have been systematically investigated. XRD measurements show that the ZrGdOx gate dielectric thin films change from amorphous state to stable tetragonal phase with the increase of annealing temperature. Based on the optical properties analysis, it can be noted that annealing leads to the increase in band gap energy, which can be attributed to the reduction in localized states in the band structure. Electrical investigation demonstrates that 400 °C-annealed ZrGdOx gate dielectric thin film has the improved electrical performance and optimized electrical parameters, such as the highest dielectric constant, smallest flat band voltage hysteresis, border trapped oxide charge density and low leakage current density. Based on the analysis of leakage current conduction mechanism, it can be noted that Schottky emission and Ohmic conduction are main conduction mechanisms in low electric fields. The main conduction mechanism in the high electric field is the direct tunneling mechanism. Therefore, it can be concluded that the ZrGdOx gate dielectric thin film annealed at 400 °C shows potential application for future MOS devices.

References

He G, Zhu LQ, Liu M, Fang Q, Zhang LD (2007) Appl Surf Sci 253:3413–3418

He G, Fang Q, Liu M, Zhu LQ, Zhang LD (2004) J Cryst Growth 268:155–162

He G, Deng B, Liu M, Ma YQ, Chen XS, Lv JG, Shi SW, Song XP, Sun ZQ (2013) Sci Adv Mater 5:709–712

Jones AC, Aspinall HC, Chalker PR, Potter RJ, Kukli K, Rahtu A, Ritala M, LeskeläM (2004) J Mater Chem 14:3101–3112

Wilk GD, Wallace RM, Anthony JM (2001) J Appl Phys 89:5243–5275

Liao L, Bai JW, Lin YC, Qu YQ, Huang Y, Duan XF (2010) Adv Mater 22:1941–1945

Zhang W, Cui Y, Hu ZG, Yu WL, Sun J, Xu N, Ying ZF, Wu JD (2012) Thin Solid Films 520:6361–6367

Xiong Y, Tu H, Du J, Ji M, Zhang X, Wang L, (2010) Appl Phys Lett 97:012901

Xiao DQ, He G, Lv JG, Wang PH, Liu M, Gao J, Jin P, Jiang SS, Li WD, Sun ZQ (2017) J Alloys Compd 699:415–420

Jõgi Indrek, Tamm A, Kukli K, Kemell M, Lu J, Sajavaara T, Ritala M, Leskeläb M (2010) J Electrochem Soc 157:G202–G210

Cho MH, Moon DW, Park SA, RhoYS, Kim YK, Jeong K, Chang CH, Gu JH, Lee JH, Choi SY (2004) Appl Phys Lett 84:678–680

Venkatachalam DK, Bradby JE, Saleh MN, Ruffell S, Elliman RG (2011) J Appl Phys 110:043527

Iizuka H, Yokoo K, Ono S (1992) Appl Phys Lett 61:2978–2980

Ritala M, Kukli K, Rahtu A (2000) Science 288:319–321

Zhu SL, Wang FH, Lou HY, Wu WT (1995) Surf Coat Technol 71:9–15

Liu A, Liu G, Zhu H, Shin B, Fortunato E, Martions R, Shan F, (2016) Appl Phys Lett 108:233506

Jin P, He G, Fang ZB, Liu M, Xiao DQ, Gao J, Jiang SS, Li WD, Sun ZQ, Zhang M (2017) Ceram Int 43:3101–3106

Chang SM, Doong RA (2005) Chem Mater 17:4837–4844

Chaneliere C, Four S, Autran JL, Devine RAB, Sandler NP (1998) J Appl Phys 83:4823–4829

Jo SJ, Ha JS, Park NK, Kang DK, Kim BH (2006) Thin Solid Films 513:253–257

Park JH, Yoo YB, Lee KH, Jang WS, Oh JY, Chae SS, Baik HK (2013) ACS Appl Mater Interfaces 5:410–417

Tan TT, Liu ZT, Lu HC, Liu WT, Yan F, Zhang WH (2009) Appl Phys A 97:475–479

Ananthakumar R, Sang JK (2012) J Alloy Compd 544:115–119

Liang LP, Sheng YG, Xu Y, Wu D, Sun YH (2007) Thin Solid Films 515:7765–7771

Liu M, Fang Q, He G, Li L, Zhu LQ, Li GH, Zhang LD (2006) Appl Phys Lett 88:192904-192904-3

Fan JB, Liu HX, Kuang QW, Gao B, Ma F, Hao Y (2012) Microelectron Reliab 52:1043–1049

Das PS, Biswas A (2011) Microelectron Eng 88:282–286

Lai PT, Chakraborty S, Chan CL, Cheng YC (2000) Appl Phys Lett 76:3744–3746

Zhang JQ, Li ZX, Zhou H, Ye C, Wang H (2014) Appl Surf Sci 294:58–65

Liu JW, Liao MY, Imura M, Tanaka A, Iwai H, Koide Y (2014) Sci Rep 4:6395

Liu JW, Liao MY, Imura M, Oosato H, Watanabe E, Koide Y, (2013) Appl Phys Lett 102:112910

Zhang JW, He G, Zhou L, Chen HS, Chen XS, Chen XF, Deng B, Lv JG, Sun ZQ (2014) J Alloy Comp 611:253–259

Chen F, Bin X, Hella C, Shi X, Gladfelter WL, Campbell SA (2004) Microelectron Eng 72:263–266

Quah HJ, Cheong KY (2012) J Alloys Compd 529:73–83

Quah HJ, Cheong KY, Hassan Z, Lockman Z (2011) J Mater Sci Mater Electron 22:583–591

Quah HJ, Lim WF, Cheong KY, Hassan Z, Lockman Z (2011) J Cryst Growth 326:2–8

Gao F, Lee SJ, Chi DZ, Balakumar SK, Wong DL, (2007) Appl Phys Lett 90:252904

Gao J, He G, Deng B, Xiao DX, Liu M, Jin P, Zheng CY, Sun ZQ (2016) J Alloy Compd 622:339–347

Chiu FC (2006) J Appl Phys 100:114102

Ding SJ, Zhang DW, Wang LK (2007) J Phys D 40:1072–1076

Acknowledgements

The authors acknowledge the support from National Natural Science Foundation of China (51572002,11474284), Technology Foundation for Selected Overseas Chinese Scholar, Ministry of Personnel of China (J05015131), Anhui Provincial Natural Science Foundation (1608085MA06).

Author information

Authors and Affiliations

Corresponding authors

Ethics declarations

Conflict of interest

The authors declare that they have no competing interests.

Rights and permissions

About this article

Cite this article

Zhu, L., He, G., Sun, Z.Q. et al. Annealing temperature-dependent microstructure and optical and electrical properties of solution-derived Gd-doped ZrO2 high-k gate dielectrics. J Sol-Gel Sci Technol 83, 675–682 (2017). https://doi.org/10.1007/s10971-017-4468-y

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10971-017-4468-y