Abstract

The electrical properties of Au/Ti/HfO2/n-GaAs metal/insulating layer/semiconductor (MIS) contact structures were analyzed in detail by the help of capacitance–voltage (C–V) and conductance–voltage (G–V) measurements in the temperature range of 60–320 K. The HfO2 thin-film layer was obtained by atomic layer deposition technique (ALD). The main electrical parameters such as ideality factor (n) and barrier height (ΦB0) were determined for Au/Ti/n-GaAs and Au/Ti/HfO2/n-GaAs diodes using current–voltage (I–V) measurement at 300 K. The values of these parameters are 1.07 and 0.77 eV for the reference (Au/Ti/n-GaAs) diode and 1.30 and 0.94 eV for the Au/Ti/HfO2/n-GaAs MIS diode, respectively. An interfacial charge density value of \({Q}_{ss}\)= 4.14 × 1012 Ccm−2 for the MIS diode was calculated from the barrier height difference of \(\Delta\Phi =0.94-0.77=0.17 \mathrm{V}\). Depending on these results, the temperature-dependent C–V and G–V plots of the device were also investigated. The series resistance (Rs), phase angle, the interface state density (Dit), the real impedance (Z′) and imaginary impedance (Z″) were evaluated using admittance measurements. The C and G values increased, whereas (Z″) and Z decreased with increasing voltage at each temperature. An intersection point being independent of temperature in the G–V curves appeared at forward-bias side (≈1.4 V); after this intersection point of the G–V plot, the G values decreased with increasing temperature at a given voltage. The intersection points in total \(Z\) versus V curves appeared at forward-bias side (≈1.7 V). The Nyquist spectra were recorded for the MIS structure showing single semicircular arcs with different diameters depending on temperature.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Thin-film technology has been widely used in the production of electronic devices from past to present and characterization of variety of them derived from traditional metal–semiconductor (MS) junction with Schottky barrier formation between metal and semiconductor [1, 2]. Schottky contacts based on group III–V semiconductors have been appeared especially in high-speed optoelectronic and electronic structures such as solar cells, field-effect transistors, high-electron mobility transistors and diodes [3,4,5,6,7]. Schottky diodes (SDs) are the simplest MS contact devices [8,9,10,11,12,13] the understanding of which has great technological importance in the electronics. At this point, since gallium arsenide (GaAs) is one of the most important materials for low-power and high-speed devices, a full understanding of the nature of the electrical characteristics of GaAs-based SDs is essential for its application. In general, in the literature, we find that mainly two parameters of a Schottky diode, ideality factor (n) and barrier height (BH), were evaluated and their dependence on temperature and voltage was discussed [14,15,16,17,18]. Biber et al. [12], Kahveci et al. [11] and Karabulut [13] have obtained an approximate value of zero-bias barrier height (ΦB0) as around 0.76 eV at 300 K for Au/Ti/n-GaAs MS diode.

Recently, MS diodes have stayed popular in determining the electrical properties of interfacial thin-film layers produced by different methods [19, 20]. In fact, the performance of metal–insulator–semiconductor (MIS) diodes depends on formation of an insulator layer, active metal/semiconductor interface, the interface states distribution at semiconductor, insulator interface, series resistance and inhomogeneous barrier heights [21,22,23,24,25,26,27,28]. Therefore, the production of thin-film surfaces with different methods has gained importance for MIS diodes in recent years. In the literature, MIS diodes were formed by adding an interfacial layer to the MS contact interface by different deposition methods such as metal–organic chemical vapor deposition (MOCVD), sputtering, molecular beam epitaxy (MBE) and atomic layer deposition (ALD) technique [29,30,31,32]. Electrical behavior and capacitive characteristics of MS diode change with the presence of the interfacial thin-film layer.

Self-generated oxide layer or layer intentionally formed on semiconductor sample takes effect BH formation between metal and semiconductor. Reliability and performance of MIS diodes depend on this barrier formation and its effects on ideality of the diode behavior such as inhomogeneous barrier heights together with parasitic resistances and interface states distribution at an interfacial thin layer and semiconductor interface [31, 32]. The SiO2 thin layer is generally used as the interfacial layer at the MS contact interface by different methods. Many studies have shown that the SiO2 interface layer causes high leakage current. That is why the researchers started working on different interface layers to reduce leakage current of MIS diodes [33,34,35]. Due to the high leakage current problem of SiO2 layer, high-dielectric materials have been a point of interest in Schottky-type and MIS diodes.

At this point, the high-dielectric materials such as HfO2, ZrO2 and TiO2 attracted great interest in which the leakage current of metal/HfO2/, metal/TiO2/ and metal/Si3N4/ contacts on the semiconductor substrate is lower than the leakage current of metal/SiO2/semiconductor diode, and high-dielectric layers dropping influence in leakage current of devices increased rectification rate (RR = IF/IR) or shunt resistance [36,37,38,39,40,41,42,43,44,45]. Recently, hafnium oxide (HfO2) thin films have been received much attention because it can suppress the leakage current in insulating gate materials [46,47,48,49,50,51]. This film also shows high resistivity and dielectric constant at diode interface [46,47,48,49]. In addition, HfO2 insulator layer has positive fixed charges; therefore, it is good suitable for n-Si sample. There is currently limited research focusing on the passivation of HfO2 on n-Si sample for Si-based solar cells [52,53,54].

Active dangling bonds at Si semiconductor surface had still problems on passivation processes [32, 34]. Therefore, new materials alternative to SiO2 and different deposition methods have been also point of interest. The quality of HfO2 thin films depends on deposition method. In the literature, several deposition techniques have been used to grow this insulator layer on semiconductor. Among many possible deposition techniques for preparing ultrathin metal oxide films, ALD is very promising one because it can produce high-quality films with precise thickness control and near-perfect conformality owing to its adsorption-controlled deposition mechanism [32, 55,56,57,58,59]. One of the biggest advantages of ALD technique is ability to obtain highly reproducible, homogenous coatings, while deposition process does not depend on source of substrates [60, 61]. Ritala et al. reported that HfO2 gate dielectric is compatible with conventional poly-Si without needing a barrier layer [62].

MS and MIS diodes are crucial to indicate the electrical properties in wide range frequency and temperature to detail the interface homogeneity and nature transport mechanism [32,33,34]. The basic electrical properties of these diodes are extracted according to thermionic emission (TE) theory. Applying this theory, n and BH can be determined. There are some literature works on HfO2/Si or HfO2/GaAs diodes [13, 63,64,65,66]. Gullu et al. fabricated the In/HfO2/Si diode, and ΦB0 and n for this type of diode were determined 0.79 eV and 4.22 at room temperature, respectively [63]. In addition, Turut et al. fabricated the diode with HfO2 thin interlayer, and the values of these parameters for this diode were determined 0.91 eV and 1.11 at 280 K, respectively [67]. In this work, the electrical properties of the Al/Ti/HfO2/GaAs Schottky diodes were analyzed by the admittance measurements in the temperature range of 60–320 K. The HfO2 film layer of 10 nm was deposited on n-GaAs semiconducting sample by ALD method, and the Schottky contact (Au/Ti) was obtained using thermal evaporation method. The basic electrical parameters as ΦB0 and n were determined from TE theory implemented to the I–V measurements (300 K) of the Al/Ti/HfO2/GaAs and Al/Ti/GaAs Schottky diodes. In addition, the diode parameters such as the phase angle, the capacitance C, conductance G, series resistance Rs, density of interface states Dit, real impedance \({Z}^{^{\prime}}\) and imaginary impedance Z″ of Al/Ti/HfO2/GaAs diode were investigated using admittance–voltage measurements with the change in temperature (60–320 K).

It has been investigated the effect of atomic-layer-deposited HfO2 thin-film interfacial layer on the electrical properties of Au/Ti/n-GaAs Schottky diode. The HfO2 thin-film layer at MS interface causes the barrier modification and semiconductor surface passivation. The barrier modification is an important process in the rectifying MS contacts. The MS Schottky contacts (SCs) play an important role in integrated device fabrication. The purpose of the BH modification can be both to increase the BH and to improve the rectification properties in MS SCs. The reduced BH decreases the voltage drop in forward bias while maintaining the rectification properties in reverse bias. Some authors [1, 2, 11,12,13, 66,67,68] reported that the low-barrier diodes allow as small signal zero-biased MS SCs and microwave mixers. In the microwave MS SC applications, the larger-barrier SCs must be used with a dc offset voltage. Furthermore, the increased barrier structures can be used for the gates of MESFETs, and the small-barrier SCs normally cause very large gate leakage currents. Moreover, the increased barrier devices and diodes are also useful in surface recombination studies and optical detectors such as solar cells and photodiodes. Moreover, the SCs and bipolar p–n junctions with high BH can be used in determination of minority-carrier lifetimes and carrier diffusion constants. The semiconductor surface passivation or the use of the HfO2 thin film before Schottky metallization offers a number of potential advantages such as improvement in the impedance characteristics of the device or to protect the semiconductor surface from defective interfacial compounds. The surface passivation by the HfO2 thin film can be designed to control the defective states originated from the deposition of Schottky metal and interfacial reaction during metallization. That is, the MIS diodes may be a sensitive probe useful to increase the quality of devices fabricated using the interfacial thin layer in establishing processes for minimizing surface states, surface damage and contamination, and actively tunable barrier heights [1, 2, 11,12,13, 66,67,68].

2 Experimental Procedure

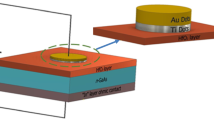

The Au/Ti/HfO2/n-GaAs MIS structure was fabricated by the process order of indium (In) back contact evaporation on the n-GaAs sample (2 Ω.cm resistivity and 7.43 × 1015 cm−3 carrier concentration), HfO2 thin-film deposition on the n-GaAs sample. For the front contacts, the n-GaAs wafer was placed on a rotating table to get homogeneity. Ti (10 nm) Schottky contacts were made using the magnetron DC sputter system, and Au (90 nm) was evaporated as a top layer on the Ti/HfO2/n-GaAs structure to protect the Ti metallic layer in high-vacuum system of about 10−6 Torr. [13, 67,68,69]. Before the deposition process, n-GaAs sample was chemically cleaned. For the ohmic contact, one side of the GaAs sample was deposited by elemental In evaporation process and post-annealing treatment was applied at 385 °C. The contact resistivity of the In/n-GaAs structure was determined as 2.5 × 10–4 Ω cm [66, 70,71,72]. Then, 10-nm HfO2 layer was deposited using a Savannah S300 ALD system [73,74,75].

The surface topography and roughness characterization for the deposited HfO2 film and n-GaAs sample surface were performed using PARK system XE 100E atomic force microscopy (AFM). In Fig. 1a and b, the topography of the n-GaAs sample is presented as 3D and 2D AFM images, respectively. These images indicate the presence of smooth surface profile with root-mean-square (RMS) surface roughness value as 895 pm. Similarly, in Fig. 2a and b, topography of the HfO2 layer is presented as 3D and 2D AFM images, respectively. As a result, 10-nm HfO2 film was found in a uniform and homogenous surface profile where its RMS surface roughness value was observed as 1.19 nm. Finally, Au (90 nm)/Ti (10 nm) Schottky contacts were formed on HfO2/n-GaAs structure by the DC sputtering method [13, 66, 67]. Au/Ti contact was preferred to obtain low-barrier formation, since work function of Au/Ti is smaller than Au. At this point, there are some works to analyze barrier height of Ti and Au/Ti Schottky contacts on n-InAlAs and these values were reported as 0.64 and 0.55 eV, respectively [76, 77]. In the current MIS structure, the Au thin film was used as a top layer to protect the Ti metallic layer on the GaAs substrate. In other words, Au was selected as the second layer to prevent oxidation and to promote current spreading, and to provide good smoothness to the contact [67, 75]. It is a common technique that Au over layer is deposited on top to enhance conductivity and prevents resistance problems [78]. Therefore, Au/Ti layer was preferred instead of one type metal contact such as Au or Ti.

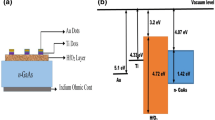

The energy band diagram and schematic design structure for the Au/Ti/HfO2/n-GaAs diodes are shown in Fig. 3a and b, respectively. In addition, the energy level of Au/Ti metal Schottky contact is shown in Fig. 3a, b shows energy-band diagram for Au/Ti/HfO2/n-GaAs diode at under applied and zero-bias condition, where Efm is the Fermi energy level, M is the work function of metal, Vn is the potential difference between Fermi energy level (Efs) and the conduction band bottom (Ec), bo = VDo + Vn is the effective barrier height at the zero bias, VDo is the value at the zero bias of the surface potential, VD is the value under the applied reverse bias of the surface potential and VR is the voltage drop across the depletion region in the reverse-bias case. As shown in Fig. 3b, the electron affinity (χs) of n-GaAs is ~ 4.07 eV, the thickness (δ) of the HfO2 is 10 nm and the energy band gap of n-GaAs is ~ 1.42 eV.

After the fabrication process, the current values were collected by a Keithley 487 Picoammeter voltage source. For the temperature-dependent measurements between 60 and 320 K, a Leybold–Heraeus closed-cycle helium cryostat was used and the temperature on the Au/Ti/HfO2/n-GaAs MIS diode was adjusted using a Lake-Shore DCR-91C controller. In addition, the admittance measurements were carried out by a HP model 4192A LF impedance analyzer under dark conditions.

3 Results and discussion

As an initial step to determine basic electrical properties from I–V plots for a diode with and without interfacial layer (MIS diode), thermionic emission (TE) equation was used. For this type of diodes, it can be expressed as [13, 28, 34, 79]

where Is is the saturation current and it is defined as

where qΦB0 is the measured zero-bias barrier height from Eq. (2), which can be expressed as

where T is the absolute temperature, S is the Schottky diode area and A* is the effective Richardson constant and it is 8.16 Acm−2 K−2 for n-type GaAs. The equation of n can be written from Eq. (1) for (V < 3kT/q)

From Fig. 4 (a), ΦB0 and n values of the reference and MIS diodes were calculated as 0.77 eV and 1.07 and 0.94 eV and 1.30 using the intercept and slope of the linear part of the I–V curves at 300 K using Eqs. (3) and (4), respectively. Therefore, these results indicate that the MIS structure with HfO2 film can be used for the barrier height modification. This interfacial film is a gate insulator for capacitor applications [79, 80]. The HfO2 gate has a considerably high-barrier height for holes and electrons in the semiconductor, which can require relatively large band offsets at interfaces of MIS diode [81, 82]. Figure 4b shows the linear I–V plot of diode with and without interfacial HfO2 thin film. As presented in this figure, the rectification ratio, turn-on voltage and leakage current values of Au/Ti/n-GaAs diode were determined as 1 × 106 (RR = VF/VR, at VR = − 0.5 V and VF = 0.5 V), ~ 0.3 V and 8.8 × 10–10 A at − 0.5 V, respectively. On the other hand, these values were found as 3 × 106 (at VR = − 1.0 V and VF = 1.0 V), ~ 0.68 V and 1.3 × 10–10 at − 1.0 V for Au/Ti/HfO2/n-GaAs diode, respectively. Currently, the leakage current of Au/Ti/HfO2/n-GaAs diode was 3.5 × 10–11 A at − 0.5 V. Depending on these results, 10-nm HfO2 increases RR and turn-on voltage of Au/Ti/n-GaAs diode while leakage current decreases. Similar results were shown in the literature [13, 66, 67].

As shown in Fig. 4, the ΦB0 value of the reference diode is lower than the value of Au/Ti/HfO2/n-GaAs diodes. Kahveci et al. [11], Biber et al. [12] and Karabulut [13] have obtained an approximate ΦB0 value of 0.76 eV at 300 K for Au/Ti/n-GaAs MS diode. In addition, Biber et al. reported that n of Au/Ti/n-GaAs MS diode is 1.074 at 300 K [12]. The barrier height value in the literature (~ 0.76) is very close to the value (~ 0.77) that was found for the reference diode in this work. The higher than unity value of n is the indication of lateral inhomogeneity in the MIS diode [32, 45]. At room temperature, Au/Ti/HfO2/n-GaAs MIS diode gives higher ΦB0 values than Au/Ti/n-GaAs MS diode. Thus, it is an obvious fact that HfO2 interfacial layer causes the modification and increase in the ΦB0 that can be related to the free carriers having enough energy to pass over the barriers [32, 79]. In addition, the experimental result where the ΦB0 value of Au/Ti/HfO2/n-GaAs diodes is higher than the value of the reference diode may be evaluated by the presence of the HfO2 oxide layer and interface state charge \({Q}_{ss}\) at the thin oxide layer/n-GaAs semiconductor interface. The negatively charged acceptor-type interface state charge \({Q}_{ss}\) also increases the positive space charge in the depletion region or the presence of a net negative \({Q}_{ss}\) may be caused increase in the barrier height [79,80,81,82,83,84,85,86]. The negative \({Q}_{ss}\) charge is defined as [82,83,84]:

where \({\varepsilon }_{i}\) is the dielectric constant of HfO2 layer (22 \({\varepsilon }_{0}\)), \(\updelta \) thickness of HfO2 (10 nm) and the increase in the barrier height \(\Delta\Phi =0.94-0.77=0.17 \mathrm{V}\). Thus, an interface charge density value of \({Q}_{ss}\)= 4.14 × 1012 Ccm−2 is obtained from Eq. (5).

The increase in the ideality factor much larger than one for MIS diode shows that the transport properties of the device cannot be well described by only TE model. Therefore, the barrier height and ideality factor are merely a curve fitting parameters for these samples and should not be interpreted as representing the true barrier height and current mechanism. That is, the determination processes of the diode parameters by means of eqns. (3) and (4) are to learn about whether the current mechanism through the device fits the standard TE theory [87]. Figure 4c shows the Fowler–Nordheim (FN) tunneling model plotted for Au/Ti/HfO2/n-GaAs/In MIS diode from the I–V characteristics given in Fig. 4a. The FN equation can be applied to the tunneling mechanism of carriers through thin oxide layers (i.e., tunneling through triangular barrier). The FN expression for the carriers is given as [88,89,90]

The \(\mathrm{ln}\left(\frac{{I}_{F}}{{V}_{F}^{2}}\right) vs {V}_{F}^{-1}\) plot in Fig. 4b consists of two linear regions. The linear behavior of the plot indicates that the FN tunneling current dominates through the interfacial thin-layer HfO2. The straight lines in the low- and high-bias voltage regions in this figure are found in the exponential functions as \(y=0.064exp(-4.27x)\) and \(y=0.0057exp(-2.83x)\), respectively.

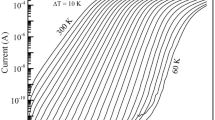

Figure 5a and b shows the temperature-dependent capacitance–voltage (C–V) and voltage-dependent capacitance–temperature (C–T) measurements for the Au/Ti/HfO2/n-GaAs diodes at 1000 kHz, respectively. As shown in Fig. 5a, the values of capacitance increase with increasing temperature in the temperature range of 60–320 K. The values of capacitance give a peak in the temperature range of 160–320, shifting to forward-bias region with decreasing temperature. It is shown in Fig. 5a that the C values of Au/Ti/HfO2/n-GaAs diode increase rapidly in the interval of − 3 and 3 V. In addition, the capacitance values decrease with decreasing voltage in the voltage range of − 3 –2.4 V at each temperature, whereas there is a slow increase in behavior between 150 and 320 K. The observed non-ideality behaviors in the admittance spectra can be due to inhomogeneities in the interfacial layer and barrier height in the diode. The interfacial passivation layer thickness, frequency and temperature can influence the G–V and C–V behavior of these diodes [91,92,93,94,95,96,97,98,99]. The C–V plot of these structures is influenced by various non-idealities such as the interfacial insulator layer, series resistance and interface states [1, 2, 99, 100]. Figure 6b shows the G–V plots of the Au/Ti/HfO2/n-GaAs MIS structure. As shown in Fig. 6a, the G values of Au/Ti/HfO2/n-GaAs MIS structure increase rapidly in the interval of 0.6 and 1.4 V, whereas there is a slow increase in behavior between − 3 and 0.6 V. Turut et al. reported similar G–V characteristics for the Au/Ti/Al2O3/n-GaAs structure at 300 K [86]. It was observed that unlike ideal Schottky diodes, G–V plots intersect at ~ 1.4 V. This behavior appears in the case of inhomogeneous Schottky diodes, and the presence of series resistance (\({R}_{s}\)) keeps this intersection unobservable and hidden in homogeneous Schottky diodes [66, 83]. Then, this crossing of the G–V, the G values of Au/Ti/HfO2/n-GaAs diodes decrease with increasing temperature in the temperature range of 60–320 K. As shown in Fig. 6b, the conductance value increases with increasing voltage for each temperature.

The \({R}_{s}\) profile was determined in the strong accumulation region from the \(C-V\) and \(G-V\) measurements [49, 101, 102],

and the corresponding values are calculated according to Eq. (7) and demonstrated in Fig. 7 for each temperature at 1000 kHz. As shown in this figure, in the voltage range of − 3.0–0.4 V, the Rs is the constant for each temperature and the Rs value of the Au/Ti/HfO2/n-GaAs MIS diode increases rapidly in the interval of 0.4 and 0.95 V. In the voltage range of 0.95–2.2 V, the Rs gives a peak depending on temperature. The two crossings of the Rs–V curves appear at forward bias (≈0.95 V and 2.2 V), and this observation can be concluded as being a non-ideal Schottky diode behavior [66, 83].

The total impedance (Z) can be expressed as [12, 103]

where ZIm and ZRe are the imaginary and real part of the total impedance Z, respectively. Then, Eqn. (8) can be decomposed by

As shown in Eqs. (8) and (9), Y is the admittance and \({G}_{m}\) and \({C}_{m}\) are the measured conductance and capacitance, respectively. The Rs is the reel part of impedance given in Eq. (7).

Figure 8a exhibits the voltage-dependent plots of the imaginary impedance (Z″) of the Au/Ti/HfO2/n-GaAs MIS structure in the temperature range of 60-320 K. As shown in Fig. 8a, the Z″ value of the MIS diode decreases with increasing voltage at each temperature and decreases with increasing temperature in the voltage range of − 3–0.4 V. A crossing of the \({Z}^{^{\prime}}\)–V curves appears at forward bias (≈1.4 V). After this crossing of the \({Z}^{^{\prime}}\)–V curves, the \({Z}^{^{\prime}}\) value of diode increases with increasing temperature in the voltage range of 1.4–3 V. Figure 8b exhibits the voltage-dependent plots of the impedance real part of the Au/Ti/HfO2/n-GaAs diode in the temperature range of 60-320 K. The real part of impedance corresponds to Rs. This figure also shows that the \({Z}^{^{\prime}}\) value of the diode is constant in the voltage range of − 3.0–0.4 V for each temperature. In addition, the \({Z}^{^{\prime}}\)–V curves have two crossings at forward bias (≈0.95 V and 2.2 V). As shown in Fig. 8b and Fig. 7, the \({Z}^{^{\prime}}\)–V plots exhibit the same behavior as Rs–V plots. Figure 8c exhibits the total impedance of the MIS diode. It is obvious from Fig. 8b that the total impedance decreases with increasing voltage at each temperature and the crossing of the \(Z\)–V curves appears at forward bias (≈1.7 V). As shown in Fig. 8c, the total impedance value increases with increasing temperature in the voltage range of 1.7–3 V. Figure 9 exhibits the impedance imaginary part versus the real impedance part of the MIS diode in the temperature range of 60-320 K. The complex impedance Z consists of an imaginary part Z″ and a real part Z′ which can be estimated from measured values of C and G [104, 105]. It is well-known fact that the Z′−Z″ plot is called a Nyquist diagram. This plot can provide further electrical information about the diode [106]. The Nyquist spectra recorded for the Au/Ti/HfO2/n-GaAs diode at different temperatures show the single semicircular arcs with different diameters. These semicircles indicate the homogeneity of the HfO2layer. The semicircle radius increases with decreasing the temperature. As shown in Fig. 9, the maximum points of the semicircular arcs are shifted toward the origin on increasing temperature [106,107,108,109,110].

Figure 10 exhibits the phase angle versus voltage plots for the Au/Ti/HfO2/n-GaAs diode. As given in this figure, the phase angle is constant (same value) in the voltage range of (−3)-0.6 V as temperature independent. Then, the phase angle increases with decreasing temperature in the voltage range of 0.6 V–1.2 V. In addition, an intersection point at phase angle curves is observed at about 1.20 V as independent of temperature. Turut et al. reported the phase angle for the Au/Ti/Al2O3/n-GaAs structure is always 90° from − 10 V to 0.0 V in the reverse-bias branch, and it suddenly decreases at 0.0 V and then approaches 0° from 0.0 V to 4.0 V in the forward branch [86]. This behavior is similar to the phase angle–voltage plot of the Au/Ti/HfO2/n-GaAs diode. The case clearly indicates that the diode behaves more capacitively at the reverse-bias region rather than the forward-bias region [111].

Figure 11 exhibits the conductivity (σ) versus voltage of the Au/Ti/HfO2/n-GaAs diode in the temperature range of 60-320 K. The σ of the Au/Ti/HfO2/n-GaAs diodes increases with increasing temperature between − 3 and 1.4 V. In addition, the crossing of the σ–V curves appears at forward bias (≈1.4 V).

The interface traps are defects located at the semiconductor–oxide layer interface. At frequency of AC voltage, the loss depends both on the interface trap level density near the Fermi level and on the speed of response of interface traps, determined by their capture probability. Thus, interface trap level density for energy levels and capture probability within the semiconductor band gap can be determined using the loss [80].

Figure 12 represents the experimental conductance of the interface states versus voltage plots for the Au/Ti/HfO2/n-GaAs MIS structure with about 10-nm HfO2 layer thickness at 1000 kHz frequency. (a) Lin–Lin plots in 60–200 K range, (b) Lin–Lin plots in 200–320 K range and (c) semi-log plots in 60–320 K range with steps of 20 K. The interface state conductance \({G}_{is}\) for the \({G}_{is}\) versus voltage curve ateach temperature was calculated from the following expression [111]

where \({C}_{ox}\) is the interfacial layer capacitance and the \({G}_{m}\) and \({C}_{m}\) are the measurement experimental conductance and capacitance, respectively. Figure 13 displays the density distribution of the interface states on sample temperature for the Au/Ti/HfO2/n-GaAs MIS diode. The interface state density value \({D}_{it}\) at each temperature was calculated using the peak value in the interface state conductance versus voltage curve in \({D}_{it}={G}_{max}/qwA\) expression. All interface states have the same time constant (relaxation time) because the measurements have made at 1.0 MHz; however, they have different energy positions in the semiconductor band gap at MS interface at each temperature. The interface state density value remains almost unchanged from 60 to 200 K, but it has an exponential rise with the temperature from about 200 K to 260 K, and it again remains almost unchanged from 260 to 320 K.

4 Conclusion

The main electrical parameters such as ΦBo and n for the Au/Ti/HfO2/n-GaAs MIS structure fabricated by the ALD method and reference Au/Ti/n-GaAs diode were determined 0.94 eV and 1.30 and 0.77 eV and 1.07 from I–V curves at room temperature, respectively. As seen from results, the interfacial HfO2 thin layer increased these values for the MIS structure and lowered leakage current. Finally, the C–V and G–V characteristics of Au/Ti/HfO2/n-GaAs MIS structure were analyzed at 1000 kHz. The temperature- and voltage-dependent Dit, Rs, Z, Z′, Z″ and phase angle of the MIS structure were examined in the temperature range of 60–320 K. It was observed that the G, C and Rs values displayed a behavior increasing with increasing temperature. The Dit, Z and Z′ increased with decreasing temperature in the temperature range of 60–320 K.

References

S.M. Sze, Physics of Semiconductor Devices, 2nd edn. (John Wiley & Sons, New York, 1981).

E.H. Rhoderick, R.H. Williams, Metal-Semiconductor Contacts, 2nd edn. (Clarendon Press, Oxford, 1988).

J.C. Huang, P. Saledas, J. Wendler, A. Platzker, W. Boulais, S. Shanfield, W. Hoke, P. Lyman, L. Aucoin, A. Miquelarena, C. Bedard, D. Atwood, IEEE Electron Device Lett. 14, 456 (1993)

A.G. Baca, V.M. Hietala, D. Greenway, J.C. Zolper, D.F. Dubbert, I.R. Sloan, R.J. Shul, I.E.E.E. Electron, Device Lett. 35, 308 (1999)

C. Nguyen, N. Micovic, IEEE Trans. Electron Devices 48, 472 (2001)

G. Eftekhari, Semicond. Sci. Technol. 8, 409 (1993)

M.A. Green, Appl. Phys. Lett. 27, 287 (1975)

N.L. Dmitruk, O. Borkovskaya, I.N. Dmitruk, S.V. Mamykin, Z. Horvath, I.B. Mamontova, Appl. Surf. Sci. 190, 455 (2002)

T. Hadjersi, H. Cheraga, W. Chergui, Appl. Surf. Sci. 235, 197 (2004)

S.H. Huang, Y. Tian, F. Lu, Appl. Surf. Sci. 234, 362 (2004)

O. Kahveci, A. Akkaya, E. Ayyildiz, A. Turut, Surf. Rev. Lett. 24, 1750047 (2017)

M. Biber, C. Temirci, A. Türüt, J. Vac. Technol. B 20(1), 10 (2002)

A. Karabulut, Bull. Mater. Sci. 42(5), 1 (2019)

R. Singh, S.K. Arora, R. Tayagi, S.K. Agarwal, D. Kanjilal, Bull. Mater. Sci. 23, 471 (2000)

H. Doğan, H. Korkut, N. Yıldırım, A. Turut, Appl. Surf. Sci. 253, 7467 (2007)

S. Hardikar, M.K. Hudait, P. Modak, S.B. Krupanidhi, N. Padha, Appl. Phys. A 68, 49 (1999)

M.K. Hudait, P. Venkateswarlu, S.B. Krupanidhi, Solid-State Electron. 45, 133 (2001)

B.L. Sharma, Metal-Semiconductor Schottky Barrier Junctions and Their Applications (Springer, Boston, 1984).

Y. Jiao, A. Heliman, Y. Fang, S. Gao, M. Kall, Sci. Rep. 5, 11374 (2015)

H.C. Card, E.H. Rhoderick, J Phys D: Appl Phys 4, 1589 (1971)

P. Cova, A. Singh, R.A. Masut, J. Appl. Phys. 82, 5217 (1997)

M. Ozer, D.E. Yildiz, S. Altındal, M.M. Bulbul, Solid-State Electron. 51, 941 (2007)

D.E. Yildiz, S. Altındal, H. Kanbur, J. Appl. Phys. 103(12), 124502 (2008)

S. Chand, J. Kumar, Appl Phys A 63, 171 (1996)

J.H. Werner, H.H. Guttler, J. Appl. Phys 69(3), 1522 (1991)

P.G. McCafferty, A. SellaI, P. Dawson, H. Elabd, Solid State Electron 39, 583 (1996)

H. Durmus, S. Karatas, Int. J. Electron. 106(4), 507 (2019)

F. Hirose, Y. Kinoshita, K. Kanomata, K. Momiyama, S. Kubota, K. Hirahara, Y. Kimura, M. Niwano, Appl. Surf. Sci. 258, 7726 (2012)

K.Y. Lee, W.C. Lee, M.L. Huang, C.H. Chang, Y.J. Lee, Y.K. Chiu, T.B. Wu, M. Hong, R. Kwo, J. Cryst. Growth 301–302, 378 (2007)

H.H. Gullu, D.E. Yildiz, A. Kocyigit, M. Yıldırım, J. Alloys Compd. 827, 154279 (2020)

D.E. Yildiz, H.H. Gullu, A. Sarilmaz, F. Ozel, A. Kocyigit, M. Yildirim, J. Mater. Sci: Mater. Electron. 31(2), 935 (2020)

D.A. Muller, T. Sorsch, S. Moccio, F.H. Baumann, K. Evans-Lutterodt, G. Timp, Nature 399, 758 (1999)

F. Yigiterol, H.H. Gullu, O. Bayrakli, D.E. Yildiz, J. Mater. Sci: Mater. Electron. 47, 2979 (2018)

A. Ashery, M.M.M. Elnasharty, SILICON 11, 1875 (2019)

J.H. Kim, V.A. Ignatova, P. Kucher et al., Curr. Appl. Phys. 9, 104 (2009)

J.H. Choi, Y. Mao, J.P. Chang, Mater. Sci. Eng. R 72, 97 (2011)

S. Rudenja, A. Minko, D.A. Buchanan, Appl. Surf. Sci. 257, 17 (2010)

J.B. Park, W.S. Lim, B.J. Park, I.H. Park, Y.W. Kim, G.Y. Yeom, J. Phys. D Appl. Phys. 42, 055202 (2009)

Yu. Tao, C. Jin, X. Yang, Y. Dong, H. Zhang, L. Zhuge, Wu. Xumei, Wu. Zhaofeng, Appl. Surf. Sci. 258, 2953 (2012)

M.H. Cho, Y.S. Roh, C.N. Whang, K. Jeong, S.W. Nahm, D.H. Ko, J.H. Lee, N.I. Lee, K. Fujihara, Appl. Phys. Lett. 81, 472 (2002)

B.K. Park, J. Park, M. Cho, C.S. Hwang, K. Oh, Y. Han, D.Y. Yang, Appl. Phys. Lett. 80, 2368 (2002)

S. Sayan, S. Aravamudhan, B.W. Busch, W.H. Schulte, F. Cosandey, G.D. Wilk, T. Gustafsson, E. Garfunkel, J. Vac. Sci. Technol. A 20, 507 (2002)

Y. Wang, J. Zhang, G. Liang, Y. Shi, Y. Zhang, Z.R. Kudrynski, Z.D. Kovalyuk, A. Patane, Q. Xin, A. Song, Appl. Phys. Lett. 115, 033502 (2019)

S. Alialy, D.E. Yildiz, Ş Altindal, J. Nanoelectron. Optoelectron. 11, 626 (2016)

B.H. Lee, L. Kang, R. Nieh, W.J. Qi, J.C. Lee, Appl. Phys. Lett. 76, 1926 (2000)

L. Kang, B.H. Lee, W.J. Qi, Y. Jeon, R. Nieh, S. Gopalan, K. Onishi, J.C. Lee, IEEE ElectronDevice Lett. 21, 181 (2000)

S.Y. Lee, S. Chang, J.S. Lee, Thin Solid Films 518, 3030 (2010)

G. He, L.Q. Zhu, M. Liu, Q. Fang, L.D. Zhang, Appl. Surf. Sci. 253, 3413 (2007)

K.P. Bastos, J. Morais, L. Miotti, R.P. Pezzi, G. Soares, I.J.R. Baumvol, R.I. Hegde, H.H. Tseng, P.J. Tobin, Appl. Phys. Lett. 81, 1669 (2002)

S. Sayan, E. Garfunkel, S. Suzer, Appl. Phys. Lett. 80, 2135 (2002)

X.Y. Zhang, C.H. Hsu, S.Y. Lien, W.Z. Zhu, S.Y. Chen, W. Huang, L.G. Xie, L.D. Chen, X.Y. Zou, S.X. Huang, App. Sci. 7, 1244 (2017)

J. Cui, Y. Wan, Y. Cui, Y. Chen, P. Verlinden, A. Cuevas, Appl. Phys. Lett. 110, 021602 (2017)

J. Wang, S. SadeghMottsghian, M. ForrokhBaroughi, IEEE Trans. Electron. Devices 59, 342 (2012)

L. Zhang, H.C. Jiang, C. Liu, J.W. Dong, P. Chow, J. Phys. D: Appl. Phys. 40, 3707 (2007)

Y. Jang, S. Shin, S. Yi, M. Hong, Thin Solid Films 674, 52 (2019)

J.A. García-Valenzuela, R. Rivera, A.B. Morales-Vilches, L.G. Gerling, J.M. Asensia, C. Voz, J. Bertomeu, J. Andreu, Thin Solid Films 619, 288 (2016)

M. Ritala, K. Kukli, P.I. Raisanen, M. Leskela, T. Sajavaara, J. Keinonen, Science 288, 319 (2000)

H. Kim, P.C. McIntyrei, Appl. Phys. Lett. 82, 106–108 (2003)

M. Knez, K. Nielsch, L. Niinistö, Adv. Mater. 19(21), 3425 (2007)

A. Seweryn, M. Alicka, A. Fal, K. Kornicka-Garbowska, K. Lawniczak-Jablonska, M. Ozga, P. Kuzmiuk, M. Godlewski, K. Marycz, J. Nanobiotechnol. 18, 132 (2020)

L. Kang, Y. Jeon, K. Onishi, B. H. Lee, W-J Qi, R. Nieh, S. Gopalan, J. C. Lee, Technical Digest of VLSI Symposium, p. 44. (2000 )

H.H. Gullu, D.E. Yildiz, O. Surucu, M. Parlak, J. Mater. Sci: Mater. Electron. 31, 9394 (2020)

N. Miyata, T. Yasuda, Y. Abe, J. Appl. Phys. 110, 074115 (2011)

W.B. Bouiadjra, A. Saidane, A. Mostefa, M. Henini, M. Shaf 71, 225 (2014)

A. Turut, D.E. Yıldız, A. Karabulut, İ Orak, J. Mater. Sci: Mater. Electron. 31, 7839 (2020)

N. Biyikli, A. Karabulut, H. Efeoglu, B. Guzeldir, A. Turut, Phys. Scr. 89, 095804 (2014)

D.E. Yildiz, J. Mater. Sci. Mater. Electron. 29, 17802 (2018)

Ö. Bayrakli, H.H. Sürücü, M. Güllü, D.E. Terlemezoglu, M. Yildiz, M. Parlak, Phys. B 570, 246 (2019)

Y. Wang, Y. Wang, L. Li, Y. Zhao, G. Feng, X. Wang , Research on rapid thermal annealing of ohmic contact to GaAs, International Conference on Optoelectronics and Microelectronics (ICOM), 23–25 (2012)

S.Y. Moon, J.H. Son, K.J. Choi, J.L. Lee, Appl. Phys. Lett. 99, 202106 (2011)

D.W. Davies, D.V. Morgan, H. Thomas, Semicond. Sci. Technol. 14, 615 (1999)

K. Kolanek, M. Tallarida, M. Michling, D. Schmeisser, J. Vac. Sci. Technol. A 30(1), 01A143 (2011)

S.-J. Jeong, Y. Gu, J. Heo, J. Yang, C.S. Lee, M.H. Lee, Y. Lee, H. Kim, S. Park, S. Hwang Sci. Reports 6, 20907 (2016)

A. Christou, W.M. Webb, Reliability of Compound Analogue Semiconductor Integrated Circuits (Reliability Information Analysis Center (RIAC), New York, 2006).

W. Gao, P.R. Berger, R.G. Hunsperger, G. Zydzik, W.W. Rhodes, H.M. O’Bryan, D. Sivco, A.Y. Cho, Appl. Phys. Lett. 66, 3471 (1995)

I.B. Chistokhin, M.S. Aksenov, N.A. Valisheva, D.V. Cmitriev, A.P. Konchavtsev, A.K. Gutakovskii, I.P. Prosvirin, K.S. Zhuravlev, Mater. Sci. Semicond. Process. 74, 193 (2018)

V.R. Reddy, Y.M. Reddy, R. Padmasuvarna, T. L. Narasappa Procedia. Mater. Sci. 10, 666 (2015)

W. Mönch, Semiconductor Surfaces And, interfaces2nd edn. (Springer, Berlin, 1995).

S.K. Gupta, B. Shankar, W.R. Taube, J. Singh, J. Akhtar, Phys. B 434, 44 (2014)

VV Afanas’ev, A Stesmans, G Brammertz, A Delabie, S Sionke, A O’Mahony, IM Povey, ME Pemble, E O’Connor, PK Hurley, SB Newcomb (2009) Appl. Phys. Lett. 94: 202110

S. Ashok, J.M. Borrego, R.J. Gudmann, Solid-Stale Electron. 22, 621 (1979)

M.S.P. Reddy, P. Puneetha, V.R. Reddy, J.H. Lee, S.H. Jeong, C. Park, J. Electron. Mater. 45, 5655 (2016)

R.H. Williams, G.Y. Robinson, Physics and Chemistry of III-V Compound Semiconductor Interfaces (Plenum, New York, 1985).

S. Dimitrijev, Principles of Semiconductor Devices, 2nd edn. (Oxford University, New York, 2012).

A. Türüt, A. Karabulut, K. Ejderha, N. Bıyıklı, Mater. Res. Express 2, 046301 (2015)

E. Ayyildiz, A. Turut, Solid-State Electron. 43, 521 (1999)

F.C. Chiu, Adv.Mater.Sci. Eng., ID78168, 18 (2014)

A. Paskaleva, D. Spassov, D. Dankovic, Facta Universitatis - Series: Electronics and Energetics. 30, 511 (2017)

O. Polat, M. Coskun, H. Efeoglu, M. Caglar, F.M. Coskun, Y. Caglar, A. Turut, J. Phys. Condensed. Matter. 33, 35704 (2021)

H.K. Ha, M. Yoshimoto, B.K. Moon, H. Ishiwara, Appl. Phys. Lett. 66, 2965 (1996)

O. Pakma, N. Serin, T. Serin, S. Altındal, J. Phys. D: Appl. Phys. 41, 215103 (2008)

B.H. Park, S.J. Hyun, C.R. Moon, B.D. Choe, J. Lee, C.Y. Kim, W. Jo, T.W. Noh, J. Appl. Phys. 84, 4428 (1998)

W. Huang, T. Khan, T.P. Chow, J. Electron. Mater. 35, 726 (2006)

Z.H. Feng, Y.G. Zhou, S.J. Cai, K.M. Lau, Appl. Phys. Lett. 85, 5248 (2004)

J. Derluyn, S. Boeykens, K. Cheng, R. Vandersmissen, J. Das, W. Ruythooren, S. Degroote, M.R. Leys, M. Gremain, G. Borghs, J. Appl. Phys. 98, 054501 (2005)

M.J. Wang, B. Shen, F.J. Xu, Y. Wang, J. Xu, S. Huang, Z.J. Yang, Z.X. Qin, G.Y. Zhang, Phys. Lett. A 369, 249 (2007)

L. Aballe, L. Gregoratti, A. Barinov, M. Kiskinova, T. Clausen, S. Gangopadhyay, J. Falta, Appl. Phys. Lett. 84, 5031 (2004)

M. Ilhan, J. Mater. Electron. Device. 1, 1–6 (2015)

C.R. Crowell, S.M. Sze, J. Appl. Phys. 36, 3212 (1965)

A. Karabulut, A. Türüt, S. Karatas, J. Mol. Struct 1157, 513 (2018)

M.C. Ozdemir, O. Sevgili, I. Orak, A. Turut, Mater. Sci. Semiconductor. 125, 105629 (2021)

V. Budhraja, D. Misra, ECS Transaction 16(5), 455 (2008)

A.M. Nawar, M.M. Makhlouf, J. Alloys Compd. 767, 1271 (2018)

T.M. Nahir, Impedance spectroscopy: theory, experiment, and applications, 2nd ed. Edited by Evgenij Barsoukov (Texas Instruments Inc.) and J. Ross Macdonald (University of North Carolina, Chapel Hill) (John Wiley & Sons, Hoboken, 2005)

A.M. Nawar, H.M. Abd El-Khalek, M.M. El-Nahass, Org. Opto Electron. 1, 25 (2015).

P. Yadav, K. Pandey, V. Bhatt, M. Kumar, J. Kim, Renew. Sustain. Energy Rev. 76, 1562 (2017)

D.C. Sinclair, Bol. Soc. Esp. Ceram. Vidrio 34, 55 (1995)

I. Trabelsi, A. Harizi, M. Kanzari, Thin Solid Films 631, 161 (2017)

A.M. Nawar, M.M. Makhlof, J. Electron. Mater. 48(9), 5771 (2019)

C.H. Kim, O. Yaghmazadeh, D. Tondelier, Y.B. Jeong, Y. Bonnassieux, G. Horowitz, J. Appl. Phys. 109, 083710 (2011)

E.H. Nicollian, A. Goetzberger, Bell. Syst. Technol. J. 46, 1055 (1967)

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Yıldız, D.E., Karabulut, A., Orak, İ. et al. Effect of atomic-layer-deposited HfO2 thin-film interfacial layer on the electrical properties of Au/Ti/n-GaAs Schottky diode. J Mater Sci: Mater Electron 32, 10209–10223 (2021). https://doi.org/10.1007/s10854-021-05676-1

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10854-021-05676-1