Abstract

In this paper, the effect of crosstalk noise in a mutually coupled multiwalled carbon nanotube (MWCNT) interconnect were investigated. The multiresolution time-domain method (MRTD) is used to analyze the crosstalk noise model. On the victim line of MWCNT interconnects, the worst-case propagation delay and peak voltage have been measured and compared to those obtained using the conventional finite difference time domain (FDTD) method, and HSPICE simulations for the 22 nm technology node have been validated. The results of the proposed method shows that the crosstalk induced propagation delays in both dynamic in-phase, out-phase, and peak voltage timing and peak voltage in functional crosstalk of the MWCNT interconnects are an average error less than 2% for the proposed model and conventional FDTD model with HSPICE simulations. It has been observed that the simulation results of the proposed model match accurately with HSPICE and dominate the conventional FDTD model. For various cases of input switching, the proposed numerical model is extremely time efficient and effective in evaluating crosstalk mediated propagation delay and peak voltages. The suggested approach could also be used to fix problems including electromagnetic interference and on-chip interconnect reliability.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Interconnections are becoming more critical with technology scaling, particularly in the nano-scale range for very large integration circuits (VLSI). the latest Copper on-chip interconnects fail to comply with the specifications. The speed and reliability of high-density copper wires on-chip is reduced due to the surface, grain boundary scatterings, and Joule heating (Meindl 2003). Carbon nanotubes (CNTs) and graphene nanotubes are being investigated as alternate material for interconnects solutions, the CNTs properties have made them potential materials, with applications to VLSI circuits (Wong 2011).

Carbon nanotubes (CNTs) are graphene sheets which are rolled up to form hollow cylinder. They can typically be labelled as multi-walled CNTs (MWCNTs) and single-walled CNTs (SWCNTs). Since all of the shells are connected correctly with metal contact, MWCNTs have a higher current carrying capacity. Since MWCNTs are often metallic in design, they are very promising for VLSI on-chip interconnect applications (Li et al. 2009). Multiconductor transmission line circuits are also used to model MWCNTs. When using the complete multiconductor transmission line circuit model to simulate and evaluate a large-scale MWCNT interconnect network, however, it will be difficult and time consuming. In order to prevent the problem, a simple single-driver equivalent model for the MWCNT is proposed in Sarto and Tamburrano (2009), which can be used to rapidly and precisely evaluate multi-wire MWCNT interconnects (D’Amore et al. 2010). MWCNTs were therefore viewed in this work as interconnected material.

In order to evaluate crosstalk noise, previous models interpreted the non-linear CMOS driver to be a Simply linear resistor (Agarwal et al. 2006; Cui et al. 2011) which appears to deviate from the effects. MOSFET operates approximately 50 percent of its operating in the saturation region during the transient period, and later in linear (or) cutoff regions. Several methods with different analytical solution, Finite Difference Time Domains (FDTD) approach and SPICE results have been documented in recent works for the DIL system in Kaushik and Sarkar (2008). In the current state, several researchers have researched the crosstalk results based on the algorithm of the traditional finite-difference time-domain (FDTD) as it is precise (Li et al. 2011) and Kumar et al. (2014a) applied the FDTD approach to a nonlinear driver of CMOS by using the model of alpha-power law and the model of nth-power law, respectively, and studied the effects of crosstalk in Cu interconnects. Process variation has become a major concern in the design of many nanometer circuits, including interconnect pipelines. The purpose of this research work is to provide a comprehensive overview of types and sources of all aspects of interconnect process variations. The impacts of these interconnect process variations on circuit delay and cross-talk noises along with the two major sources of delays, parametric delay variations and global interconnect delays have been discussed (Verma et al. 2009).

For CNT interconnects, the FDTD approach was used in Liang et al. (2011; Kumar et al. (2015b). Liang et al. (2011) used the FDTD approach to model MWCNT interconnects for crosstalk noise analysis compared with Cu interconnects, and the nonlinear CMOS driver is known to be a linear resistive driver. But there was no discussion about the validation of the model using HSPICE. Kumar et al. (2015a) studied the issues of inclusion crosstalk noise of FDTD, two-coupled MWCNT interconnects and also evaluated HSPICE as a linear resistive driver with the nonlinear CMOS driver. In order to study crosstalk noise in coupled MWCNT interconnects, Kumar et al. (2015b) continued the FDTD approach to a nonlinear CMOS driver using the modified alpha-power law model. Agrawal et al. (2016) enhanced MWCNT interconnect accuracy on the basis of the FDTD model over the Cu interconnects.

The FDTD approach is an important computational procedure used to solve problems of electromagnetic and partial differential equations. The FDTD approach is numerically distributive (Tentzeris et al. 1999) and is used for propagation along the discretization. Thus, there is an extreme need for a model with an edge in numerical distribution properties. Tentzeris et al. (1999) have suggested a multi-resolution time domain (MRTD) approach with an additional advantage of the numerical dispersion characteristics (Alighanbari and Sarris 2006; Krumpholz and Katehi 1996). Grivet-Talocia (Grivet-Talocia 2000) suggested the MRTD model in view of the Haar Scaling function as a basic function and gives the same precision with respect to the FDTD model. And MRTD technique used as a basic function based on Daubechies’ scaling function, is proposed by Fujii and Hoefer (2000) as three and four extinguished moments, which are more precise than the FDTD system. Transient analysis for two-conductors transmission lines with admirable numerical dispersion, Tong et al. (2016) proposed an MRTD model. Features and improved precision with SPICE, relative to the FDTD model.

Rebelli, Nistala in Rebelli and Nistala (2018a, 2018b) also suggested the MRTD approach to evaluate the signal integrity of coupled Copper interconnect driven by linear resistive and a nonlinear CMOS dependent on the Daubechies scaling function at four extinct moments. Rebelli and Nistala (2019) applied the MRTD approach driven to non-linear CMOS using the nth-power law model to evaluate crosstalk noises in coupled-MWCNT interconnects, resulting in increased accuracy relative to the FDTD method.

In this paper, the analyses of crosstalk effects of next generations graphene based MWCNTs interconnect were studied using the MTRD technique and considered the nonlinear CMOS driver model using modified Alpha-power law model. The most effective time domain analysis is presented for mutually coupled MRTD based MWCNT interconnect. The obtained results using the MRTD model is compared with the conventional FDTD method and HSPICE as well.

The rest of the paper is arranged as follows. In Sect. 2 involves the electrical modeling of the interconnects of the MWCNT. The transmission line-based MRTD model is discussed in Sect. 3 and the MRTD Model Comparisons and Evaluation is presented Sect. 4. Finally, Sect. 5 conclusions are given.

2 MWCNT interconnects ESC model

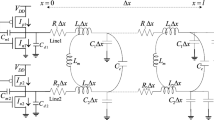

Figure 1 shows the structure of a MWCNT interconnect line for which the model was created (Das and Rahaman 2017). In this diagram the diameters of the outer and innermost CNT shells are represented by Dmax and Dmin. Furthermore, H is the distance above the ground plane, l represents the length of the interconnect, and d represent the van der Waals gaps, with d = 0.34 nm. MWCNT consists of several graphene sheet nesting shells and is represented by equivalent distributed transmissions lines model. In this analysis, the ESC (equivalent single conductor) model was used. Figure 2 shows the ESC model of two-coupled MWCNTs interconnect with driver and load. The parasitic capacitances of CMOS are expressed by \(C_{m}\), which stands for gate-to-drain coupled capacitance, and \(C_d\), which stands for drain/source diffusion capacitance. \(R_{ds}\) is the scatter resistance in per unit length (p.u.l.) and \(R_{fixed}\) is the average equivalent resistance value introduced by absolute imperfect contact resistance (\(R_{mc}\)) and quantum resistances (\(R_q\)), The MWCNT distributed capacitance p.u.l. \(C_q\) is calculated using shell-to-shell and quantum capacitance coupling capabilities. distributed inductance P.u.l. \(L_k\) is measured using shell-to-shell and kinetic inductances. Any of these parameters are from reference (Sarto and Tamburrano 2009; Maxwell 2D Student Version 2005). Similarly, the Ansoft Maxwell field solver (Maxwell 2D Student Version 2005) is used to extract the p.u.l. coupling capacitances between coupling interconnects lines (\(C_{12}\), \(C_{21}\)), electrostatic capacitance (\(C_e\)), mutual inductance between coupling interconnects lines (\(L_{12}\),\(L_{21}\)) and magnetic inductance (\(L_h\)).

3 MWCNT interconnects in MRTD model

The MRTD model for on-chip mutually two-coupled MWCNT interconnects is built in this section using basis function of Daubechies’ scaling function with four vanishing moments (D4).

3.1 Model formulations for two-coupled interconnects line

The Telegrapher’s equations can be used to describe the coupled interconnects mathematically. The coupled on-chip interconnects are defined as Paul (1994) using these equations.

where z and t are the positions and time, respectively. \(R_{ds}\), \(L_{ds}\), and \(C_{ds}\) are two-dimensional interconnect impedances that are measured using Paul (1994). The current and voltage variables for a two-coupled interconnect line are \(I=\left[ I_{1},I_{2} \right] ^{T}\) and \(V=\left[ V_{1},V_{2} \right] ^{T}\).

\(R=diag\left[ R _{ds},R_{ds} \right]\)

where subscript 1 corresponded to a line 1 and subscript 2 corresponded to a line 2. The voltage and current evaluations point on interconnect line 1 are shown in Fig. 4.

Alternatively, current and voltage points are considered in time and space to evaluate telegrapher equations. The currents and voltages are separated by \(\frac{\varDelta t}{2}\) in time and \(\frac{\varDelta z}{2}\) in space for better accuracy, as shown in Fig. 3, where\(\varDelta t\) is time and \(\varDelta z\) is space represent in discretization intervals.

The interconnects line l of length is resistive driver at \(z = 0\) and terminated at \(z = l\) is capacitive load. The line is divided consistently to NDZ segments of a length \(\varDelta z=\frac{l}{NDZ}\), indicating the discretization voltages(V) and currents(I) nodes, which are coefficients of unknown as seen in Fig. 4, where source current represents \(I_0\).

The voltages and currents terms can be extended using a known function (\(h_n(t)\) and \(\varPhi _{k}(z)\)). the coefficients of unknown in order to solve Eqs. (1) and (2) by following the method defined in Krumpholz and Katehi (1996) as:

where \(I_{k+\frac{1}{2}}^{n+\frac{1}{2}}\) is the coefficient of expansion current and \(V_{n}^{k}\) is the coefficients of the voltage expansion in terms of functions scaling, and the indices n and k are discrete time and space indices related to time and space organizes via \(t=n\varDelta t\), and \(z=k\varDelta z\). Functions \(h_n(t)\), and \(\varPhi _{k}(z)\) defined as:

where pulse function h(t) is defined as

where, \(\varPhi (z)\) signifies the scaling function of a

Daubechies, and h(t) represents the Haar scaling function The following integrals (Pan George 2003) are considered in order to derive the MRTD technique for a Eqs. (1) and (2):

where the Kronecker symbol is represented by ’\(\delta _{k,k'}\)’ and ’\(\delta _{n,n'}\)’ The effective support sizes of the basis functions is indicated by the Ls. By considering the scaling function of Daubechies as the basis functions with four vanishings moment (D4). The coefficients b(i) are called connections coefficients. Table 1 shows b(i) for \(1\le i\le L_{s}\),, whereas b(i) for \(i< 1\) it can be accomplished by symmetry condition b(-1-i) =-b(i), and zero for \(i> L_{s}\)

where the scaling function of Fourier transform f (z) is \({\hat{\varPhi }}(\lambda )\).

The follow iterative calculations for currents and voltages were carried out to employing the Galerkin technique (Krumpholz and Katehi 1996) in Eqs. (1) and (2) and by using the test functions \(\varPhi _{k}h_{n+\frac{1}{2}}(t)\) and \(\varPhi _{k+\frac{1}{2}}h_{n}(t)\):

where,

\(B_{1}=\left( 1+\frac{\varDelta t}{2}RL^{-1} \right) ^{-1}\left( 1-\frac{\varDelta t}{2}RL^{-1} \right)\)

\(B_{2}=\left( 1+\frac{\varDelta t}{2}RL^{-1} \right) ^{-1}\)

In the iterative equations (8a) and (8b), the near-end voltage \(V_{1}^{n+1}\) and the far-end voltage \(V_{NDZ+1}^{n+1}\)are obtained and the iterative equation of the currents and voltages near the boundary necessity to be modified. Near the boundary the currents are expressed by \(I_{j+\frac{1}{2}}^{n+\frac{1}{2}}\) and \(I_{NDZ+1-i+\frac{1}{2}}^{n+\frac{1}{2}}\) for \(i=1,2,3,\cdots ,L_{s}-1\) and voltages are \(V_{i}^{n+1}\) and \(V_{NDZ-i+1}^{n+1}\) for \(i=2,3,\cdots ,L_{s}\) Many of these currents and voltages have a number of terms that surpass the index ranges in iterative equations (8a) and (8b)

Equations (8a) and (8b) need to be decomposed using the relationship in Dogaru and Carin (2001) to update the iterative equations of currents and voltages, which satisfies the connection coefficients b(i) provided by the connection coefficients b(i) given by

By Substituting (9) into (8b), to get

To decompose (8b) considering a corresponding term with i as:

for at \(i=1,2,3,\cdots ,L_{s}-1\)

Equation (11) is further adapted by employ the at boundary conditions as proved in Sects. 3.3 and 3.4.

3.2 Modeling of CMOS driver

Figure 2 shows a two-coupled MWCNT interconnect line equivalent electrical circuit model. The input voltage (Vs) is a two-dimensional vector with the formula \(V_{s}=\left[ V_{s1},V_{s2} \right] ^{T}\). The interconnects line is driven by a CMOS driver (International Technology Roadmap for Semiconductors (ITRS) 2012) that follows a modified Alpha power law model. The velocity saturation effects, as well as the finite drain conductance parameters, are included

The latest equations for PMOS and NMOS are signified by \(m\times 1\) vectors, i.e. \(I_{p}=\left[ I_{p1},I_{p2} \right] ^{T}\) and \(In = \left[ I_{n1},I_{n2} \right] ^{T}\). The linear region transconductance parameters, threshold voltages, saturation region transconductance parameters, drain conductance parameters and velocity saturation index of NMOS(PMOS) are \(K_{ln}\left( K_{lp} \right)\), \(V_{tn}\left( V_{tp} \right) , and K_{sn}\left( K_{sp} \right)\) respectively. The NMOS/PMOS model parameter values for the 22nm technology node as seen in Table 2 are used for this analysis.

3.3 Modeling at near-end boundary condition

The DIL system’s modeling is used under boundary conditions. The current and voltage node points are at the near-end terminals defined by \(I_0\) and \(V_1\), respectively. where the nodal analysis of the terminal equation is given

Applying discretization and Galerkin technique to (14a) and (14b) respectively, then

then

the near end terminal a voltage is carry out at k=1 from (8b)

By following the steps from the Eqs. (9) to (11) to decomposed Eqs. (16a) to (16c) as

\(\vdots\)

Iterative equations (16a)–16c) to be considered as CAD, i.e., central difference equations. in the particular calculations, the subscript to the terms

\(I_{-\frac{1}{2}}^{n+\frac{1}{2}},I_{-\frac{3}{2}}^{n+\frac{1}{2}},\cdots , I_{-L_{s}+\frac{3}{2}}^{n+\frac{1}{2}}\) have surpassed the index range. To solve this, substitute the central difference scheme by using the forward difference scheme. By leaving the weight coefficient in each equations unchanged, iterative equations can also be obtained.

\(\vdots\)

From the above Eqs. (17a)–(17c), the iterative equation at the near-end boundary node voltage of \(V_{1}^{n+1}\) is obtained through the following:

In Eq. (18b), substituting by \(I_0^{n+\frac{1}{2}}=\frac{I_0^n+I_0^{n+1}}{2}\) and equation (15a), (15c) we obtained the equation as

where,

3.4 Modeling at far-end boundary condition

Similarly, the nodal analysis equation at load current \(I_{NDZ+1}\) is given by the far-end terminal (k = NDZ+1) is:

Applying discretization and Galerkin technique to (20a) and (20b) respectively, then

The final iterative equations given at the far end of the terminal is

where Some of the term indices surpass the index ranges for all the nodes between the terminals in the algorithm extension to obtain and update the iterative equations, so a truncation method is applied by taking \(V_{k}^{n+1}\)as an examples for \(k = 2, 3,\ldots , L_{s}\) and by subsequent the steps of Eqs. (10) and (11), it can be decomposed (8b) as an example for \(k = 2, 3,\ldots , L_{s}\)

\(\vdots\)

\(\vdots\)

From the Eqs. (22a) to 22(f) stated above, it is also observed that the indices of the equation do not surpass the index ranges for the first k terms. In addition, all calculations for which the index terms surpass the index spectrum appear in the remaining \(L_{s}-k\) term. As \(L_{s}-k\)terms are out-of-bound these equations are not available for iterative equations in MRTD model. To prevent problem, a truncations is built in calculations where the index range is surpassed. first k terms by summing up the in Eqs. (22a)–22(f), iterative equations can be updated for at \(k = 2, 3,\ldots , L_{s}\)

Using the same steps illustrated in Eqs. (22a)–(22f), a altered iterative equation of voltages at interiors point as presented in Eq. (23) and voltages near a load as presented in Eq. (24) is.

for at the \(k=L_{s}+1, L_{s}+2,NDZ-L_{s}, NDZ-L_{s}+1\)

for at the \(k=NDZ-L_{s}+2, NDZ-L_{s}+3, \ldots , NDZ\).

Iterative current equations can also be modified by subsequent the same voltages iterative equations with minor modifications. As seen in Fig. 5, it is observed that at the half-integer points the current nodes appear. It implies that at the interiors points of the terminals, all the currents are located. Therefore, the current near the terminals need alteration. For iterative current equations near to the terminals, it is necessary to decompose (8a) using the steps of iterative voltage of the equations. The final updated iterative current equations are given as

for at the k =1, near at the source

for k=2, 3,......., \(L_s\)

for at the \(k=L_{s}+1, L_{s}+2, \cdots , NDZ-L_{s}, NDZ-L_{s}+1.\) at the Interior point iteratives equations

for at the \(k=NDZ-L_{s}+2, NDZ-L_{s}+3, \cdots , NDZ\), Near the load, iteratives equations are

In the context of this bootstrapping method, modified voltage and current iterative equations are tested. Firstly, in terms of historical Voltages and current values, voltages iterative equations are solved at a rigid time using Eqs. (19), (21), (23)–(25). Then, Eqs. (26)–(29) solve the iterative equations of currents in terms of voltages measured initially and past values of current. The courant stability condition (Tong et al. 2016; Dogaru and Carin 2001) is thus known as the stable output for MRTD iteratives equations.

Which states that for each cell, the time of propagation must be higher than the time step. Where q is the current numbers given by \(q=1/\sum _{i=1}^{L_{s}}\left| b(i) \right| =\vartheta \varDelta t/\varDelta z\) and \(\vartheta\) and v is the phase velocity of the line propagation. However, the boundary conditions will always gratify the stability requirement as these are explicitly derived out of a implicit expression.

4 The MRTD model is compared and validated

Performance analyses of two-lines coupled MWCNT interconnects structure is presented. The proposed model is validated by comparison it to conventional FDTD model and with HSPICE simulation. The interconnects load is driven by CMOS driver, the interconnects dimensions are taken from ITRS (International Technology Roadmap for Semiconductors (ITRS) 2012; Kumar et al. 2017). At 22 nm technology node, the interconnect is placed from a ground plane is 48 nm. the aspect ratio is taken 3. the ratio of diameters inner to outer is 0.35. the interconnect width is 32nm. Imperfect metal contacts resistance is \(3.2k\varOmega\). and the distance between shells to shells in MWCNT is 0. 34 nm. The length and load capacitance of the interconnects are 1 mm and 2fF. The voltage \(V_{dd}\) is 0.8V. The signal voltage swings from 0 to 0.8 V (Low\(\rightarrow\)High) or 0.8 to 0V (High\(\rightarrow\)Low). The input source voltages have a transition time is 20ps. The proposed MRTD model implemented by MATLAB using Intel(R) Xeon(R) CPU E3-1225v6 operating at 3.30GHz and HSPICE tool ( Synopsys for HSPICE tools 2008). The parasitic values of RLC for a two-coupled interconnect line structure are

\(R_{ds}=\begin{bmatrix} 2.2&{} 0\\ 0&{} 2.2 \end{bmatrix}_{2\times 2}\frac{M\varOmega }{ m}\), \(L_{ds}=\begin{bmatrix} 16.35 &{} 0.66\\ 0.66 &{} 16.35 \end{bmatrix}_{2\times 2}\frac{uH}{m}\)

\(C_{ds}=\begin{bmatrix} 83.68&{} -68.23\\ -68.23&{} 83.68 \end{bmatrix}_{2\times 2}\frac{pF}{m}\)

4.1 Analysis of transients and crosstalk in two coupled MWCNT interconnects

This section covers the transient and crosstalk studies of a two-line coupled interconnects system. Line 1 is the aggressor in the coupled two MWCNT interconnects system seen in Fig. 2, and line 2 is the victim line. On the other end of the victim spectrum, the effect for functional, dynamic in-phase, and dynamic out-phase switching has been found using the proposed model, HSPICE, and the conventional FDTD model. On the victim line, the transient reaction is investigated. The effect of functional crosstalk is explored by modifying line 1’s aggressor input from 0.8V to 0V while holding line 2’s victim in quiescent mode. When both aggressor and victim stimuli turn at the same time, the impact of in-phase or out-phase is also explored. At the far end of the victim line, the transient graph results based on the above conditions are compared. Figure 5a–c displays the functional, dynamic in-phase, and dynamic out-phase transient responses. Figure 5b, c demonstrate that the victim-line peak solution has higher dispersion errors than the conventional FDTD method. The proposed model, on the other hand, is superior to the conventional FDTD model in terms of precision due to its significant superiority in numerical dispersion properties. Figure 5c illustrates how miller coupled capability allows signal transitions to take longer during out-phase than during in-phase switching. The simulation results of proposed MRTD model match HSPICE correctly in all input switching situations and outperform the conventional FDTD method.

In comparison to HSPICE, Table 3 indicates the computational error associated with estimating functional crosstalk effects over victim line2 for conventional FDTD and then suggested MRTD models. Efficacy at multiple input transition times. The proposed model’s average error in predicting crosstalk peak voltages is found to be 0.57 percent, compared to 1.68 percent for the conventional FDTD method. Table 4 also indicates that the proposed model correctly predicts peak voltage timing, with an average error of 0.77 percent compared to 1.31 percent using the conventional FDTD method.

With respect to HSPICE, Table 5 indicates the computational error associated with estimating dynamic in-phase crosstalk effects over victim line2 for conventional FDTD and proposed MRTD models. sturdiness of input transitions at different times the proposed model is observed to have a 2.18 percent average error in propagation delay estimation, compared to 5.07 percent for the conventional FDTD method.

With respect to HSPICE, Table 6 indicates the computational error associated with estimating dynamic out-phase crosstalk effects over victim line2 for conventional FDTD and proposed MRTD models. sturdiness of input transitions at different times the proposed model has a 0.431 percent average error in propagation delay estimation, compared to 1.48 percent for the conventional FDTD method. The simulation results of proposed MRTD model match HSPICE correctly in all input switching situations and outperform the conventional FDTD method.

The graphs for peak voltage timing and peak voltage value on the victim line as a result in functional crosstalk generated by a varied in input transition time are seen in Figures 6 and 7. At different input transition times, Figures 8 and 9 illustrate dynamic in-phase and out-phase crosstalk propagation delays.The results for both functional and dynamic crosstalk are MRTD model validated with HSPICE and outperform the conventional FDTD model

Figures 10 and 11 demonstrate the peak voltage timing and peak voltage on victim line2 in functional switching with varying values of load capacitance \(C_L\). The comparison of the Dynamic propagation delay response of crosstalk switching on victim line for two-coupled interconnect lines between the proposed MRTD method, HSPICE and the conventional FDTD method with reference (Kumar et al. 2014b). It is observed that the proposed MRTD method is in good agreement with the HSPICE simulation results.It is observed from Fig. 12 that the proposed MRTD method dominates the existing conventional FDTD and is in good agreement with HSPICE. The power delay product (PDP) signifies energy dissipation in a system and is an important figure of merit. Thus, a low value of PDP is desirable for any high-performance integrated circuit design (Kumar et al. 2006). The PDP for MWCNT interconnects using MRTD and Conventional FDTD has been analyzed and presented in Fig. 13. Fig. 14 demonstrates the CPU computing time specifications for crosstalk study of coupled-MWCNT interconnect lines in various scenarios. The simulation results of the proposed MRTD model fit HSPICE adequately and outperform the conventional FDTD model, according to the results.

5 Conclusion

The modified alpha power law model is used in this paper to build an analytically dependent MRTD model for functional and dynamic crosstalks study of coupled two transmission lines driven by a CMOS driver. For coupled two MWCNT interconnects, in this work provided a detailed study of functional, dynamic in-phase, and out-phase induced effects on the victim line. The Courant condition is strictly followed by the suggested model’s stability. The influence of input transition time on crosstalk propagation delay under dynamic and peak voltage timing, as well as the peak voltage value for functional crosstalk, is studied. The proposed MRTD model’s effects are in comparison to the results of conventional FDTD and HSPICE simulations. With regard to HSPICE, the proposed MRTD model and the FDTD validate that the proposed MRTD model is in good agreement with HSPICE. The findings show that the average error of crosstalk-induced propagation delays in both dynamic in-phase and out-phase MWCNT interconnects is 2.18 percent and 0.431 percent, respectively, according to the proposed model. Functional crosstalk has a peak voltage timing of 0.57 percent and a peak voltage value of 0.77 percent. Furthermore, the suggested MRTD model and FDTD model are validated with HSPICE for peak voltage timing and peak voltage value on victim line for functional cases for various values of load capacitances with an average error is less than 1%. The proposed model time efficiency over the FDTD model and HSPICE is reported, suggesting that it has the ability to analyses crosstalk in on-chip interconnects quickly and accurately. The analysis was performed on two coupled interconnect, but it can also be generalised to M- mutually coupled MWCNT interconnects and it can be extended to Through Silicon Vias(TSVs).

Data availability

Data sharing is not applicable to this article as no datasets were generated or analyzed during the current study.

References

Agarwal K, Sylvester D, Blaauw D (2006) Modeling and analysis of crosstalk noise in coupled RLC interconnects. IEEE Trans Comput Aided Des Integr Circuits Syst 25(5):892–901

Agrawal Y, Kumar MG, Chandel R (2016) Comprehensive model for high-speed current-mode signaling in next generation MWCNT bundle interconnect using FDTD technique. IEEE Trans Nanotechnol 15(4):590–598

Alighanbari A, Sarris CD (2006) Dispersion properties and applications of the Coifman scaling function based S-MRTD. IEEE Trans Antennas Propag 54(8):2316–2325

Cui J-P, Zhao W-S, Yin W-Y, Jun H (2011) Signal transmission analysis of multilayer graphene nano-ribbon (MLGNR) interconnects. IEEE Trans Electromagn Compat 54(1):126–132

D’Amore M, Sarto MS, Tamburrano A (2010) Fast transient analysis of next-generation interconnects based on carbon nanotubes. IEEE Trans Electromagn Compat 52(2):496–503

Das D, Rahaman H (2017) Carbon nanotube and graphene nanoribbon interconnects. CRC Press

Dogaru T, Carin L (2001) Multiresolution time-domain algorithm using CDF biorthogonal wavelets. IEEE Trans Microw Theory Tech 49(5):902–912

Fujii M, Hoefer WJR (2000) Dispersion of time domain wavelet Galerkin method based on Daubechies’ compactly supported scaling functions with three and four vanishing moments. IEEE Microw Guided Wave Lett 10(4):125–127

Grivet-Talocia S (2000) On the accuracy of Haar-based multiresolution time-domain schemes. IEEE Microw Guided Wave Lett 10(10):397–399

International Technology Roadmap for Semiconductors (ITRS) (2012) [Online]. http://www.itrs.net/. Accessed 10 Aug 2018

Kaushik BK, Sarkar S (2008) Crosstalk analysis for a CMOS-gate-driven coupled interconnects. IEEE Trans Comput Aided Des Integr Circuits Syst 27(6):1150–1154

Krumpholz M, Katehi LPB (1996) MRTD: new time-domain schemes based on multiresolution analysis. IEEE Trans Microw Theory Tech 44(4):555–571

Kumar KB, Sankar S, Agarwal RP, Joshi RC (2006) Crosstalk analysis and repeater insertion in crosstalk aware coupled VLSI interconnects. Microelectron Int 23(3):55–63

Kumar VR, Kaushik BK, Patnaik A (2014a) An accurate FDTD model for crosstalk analysis of CMOS-gate-driven coupled RLC interconnects. IEEE Trans Electromagn Compat 56(5):1185–1193

Kumar VR, Kaushik BK, Patnaik A (2014b) An accurate model for dynamic crosstalk analysis of CMOS gate driven on-chip interconnects using FDTD method. Microelectron J 45(4):441–448

Kumar VR, Kaushik BK, Patnaik A (2015a) Crosstalk noise modeling of multiwall carbon nanotube (MWCNT) interconnects using finite-difference time-domain (FDTD) technique. Microelectron Reliab 55(1):155–163

Kumar VR, Kaushik BK, Patnaik A (2015b) Improved crosstalk noise modeling of MWCNT interconnects using FDTD technique. Microelectron J 46(12):1263–1268

Kumar MG, Chandel R, Agrawal Y (2017) An efficient crosstalk model for coupled multiwalled carbon nanotube interconnects. IEEE Trans Electromagn Compat 60(2):487–496

Li H, Chuan X, Srivastava N, Banerjee K (2009) Carbon nanomaterials for next-generation interconnects and passives: physics, status, and prospects. IEEE Trans Electron Devices 56(9):1799–1821

Li X-C, Mao J-F, Swaminathan M (2011) Transient analysis of CMOS-gate-driven \(RLGC\) interconnects based on FDTD. IEEE Trans Comput Aided Des Integr Circuits Syst 30(4):574–583

Liang F, Wang G, Lin H (2011) Modeling of crosstalk effects in multiwall carbon nanotube interconnects. IEEE Trans Electromagn Compat 54(1):133–139

Maxwell 2D Student Version (2005) Ansoft Corp., Pittsburgh, PA, USA

Meindl JD (2003) Beyond Moore’s law: the interconnect era. Comput Sci Eng 5(1):20–24

Pan George W (2003) Wavelets in electromagnetics and device modeling, vol 159. Wiley

Paul CR (1994) Incorporation of terminal constraints in the FDTD analysis of transmission lines. IEEE Trans Electromagn Compat 36(2):85–91

Rebelli S, Nistala BR (2018a) A novel MRTD model for signal integrity analysis of resistive driven coupled copper interconnects. COMPEL Int J Comput Math Electr Ectron Eng 37(1):189–207

Rebelli S, Nistala BR (2018b) An efficient MRTD model for the analysis of crosstalk in CMOS-driven coupled Cu interconnects. Radioengineering 27(2):532–540

Rebelli S, Nistala BR (2019) A Multiresolution Time Domain (MRTD) Method for Crosstalk Noise Modeling of CMOS-Gate-Driven Coupled MWCNT Interconnects. IEEE Trans Electromagn Compat 62(2):521–531

Sarto MS, Tamburrano A (2009) Single-conductor transmission-line model of multiwall carbon nanotubes. IEEE Trans Nanotechnol 9(1):82–92

Synopsys for HSPICE tools (2008) [Online]. http://www.synopsys.com. Accessed 15 Oct 2020

Tentzeris EM, Robertson RL, Harvey JF, Katehi LPB (1999) Stability and dispersion analysis of Battle-Lemarie-based MRTD schemes. IEEE Trans Microw Theory Tech 47(7):1004–1013

Tong Z, Sun L, Li Y, Luo J, (2016) Multiresolution Time-Domain Scheme for Terminal Response of Two-Conductor Transmission Lines. Math Probl Eng https://doi.org/10.1155/2016/8045749

Verma KG, Kaushik BK, Singh R (2009) Effects of process variation in VLSI interconnects-a technical review. Microelectron Int 26(3):49–55

Wong H-S, Philip, Akinwande D (2011) Carbon nanotube and graphene device physics. Cambridge University Press

Acknowledgements

The research has been sponsored by the University Grants Commission (UGC) fellowship (24261/(NET-DEC.2013)). Authors would like to thank the Principal, VBIT & UCE(A) Osmania University for all their support.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Gugulothu, B., Naik, B.R. Analysis of crosstalk noise in coupled MWCNT interconnects using MRTD technique. Microsyst Technol (2024). https://doi.org/10.1007/s00542-024-05666-3

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s00542-024-05666-3