Abstract

In this paper, crosstalk noise analysis of coupled on-chip interconnects is presented. The multiresolution time domain (MRTD) method is used to analyze the crosstalk noise model. The crosstalk-induced propagation time delay and crosstalk peak voltage on the victim line of interconnects are determined. The results obtained for the proposed MRTD model are compared with the conventional finite difference time domain (FDTD) method and validated with HSPICE simulations at the 22-nm technology node. The results show that crosstalk induced a propagation delay which is dynamic in-phase and dynamic out-of-phase, and peak voltage timing and the peak voltage value of functional crosstalk in the copper interconnects have an average error of less than 0.53% when compared with HSPICE simulations. The results for the proposed model are very similar to those of HSPICE simulations. Electromagnetic interference and electromagnetic compatibility of on-chip interconnects can also be addressed using the proposed method.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Advances in very large-scale integration (VLSI) technology offer gigascale integrated circuits in a system on a chip. The use of interconnects is particularly important in the integration of electronic devices. Because of these requirements, chip complexity and the number of sources of variations have increased, and tightly packed interconnects emit transient crosstalk at high operating frequencies [1, 2]. Accurate peak noise timing and peak crosstalk noise estimation in a driver-interconnect-load (DIL) system has long been a key architectural objective [3]. On the basis of lumped and distributed RC interconnects, various crosstalk and delay models have been proposed [4, 5]. Masoumi et al. [6] computed crosstalk noise effects in a capacitively coupled RC interconnect line using closed-form expressions. Ismail et al. [7] strengthened the model by integrating self-inductance effects and estimated the RLC line propagation delay. With the introduction of low-resistivity interconnect materials and fast operating switching frequencies, parasitic inductance has begun to play an important role in on-chip interconnect efficiency. To accurately estimate the output of on-chip interconnects, they must be viewed as scattered RLC lines or transmission lines [8].

For evaluation of crosstalk noise, previous models have interpreted the nonlinear complementary metal–oxide–semiconductor (CMOS) driver to be a simple linear resistor [9, 10], which appears to deviate from the effects. Approximately 50% of MOSFET operation is in the saturation region during the transient period and later in the linear (or) cutoff regions. Several methods with different analytical solutions have been proposed, including the finite difference time domain (FDTD) approach and SPICE [simulation program with an integrated circuit emphasis], the results of which have been documented in recent works for DIL systems [11]. In the current state of the art, several studies have investigated crosstalk results based on the algorithm of the traditional FDTD, as it offers high precision [12], and Vobulapuram et al. [13] applied the FDTD approach to a nonlinear CMOS driver using the alpha-power law and nth-power law models, respectively, and they studied the effects of crosstalk in Cu interconnects.

The FDTD approach is an important computational procedure used to solve problems of electromagnetic and partial differential equations. The FDTD method is numerically dispersive [14, 15] during the propagation along the discretization. As a result, there is a need for a novel method with advantageous numerical dispersion properties. Krumpholz and Katehi [16] proposed a multiresolution time domain (MRTD) approach with an additional advantage of numerical dispersion characteristics. Grivet-Talocia [17] proposed an MRTD model using the Haar scaling function as the basis function, and achieved the same precision as with the FDTD model. Fujii et al. [18] proposed a model using MRTD as a basis function based on the Daubechies scaling function as three and four vanishing moments, which was more precise than the FDTD system. For effective field computation, Massy and Ney [19] hybridized the Battle–Lemarié-based MRTD model and the FDTD model to take advantage of the characteristics of both models, including the low dispersion characteristics of the MRTD model and the faster computation of the FDTD model. Tong et al. [20, 21] proposed an MRTD model for transient analysis of two-conductor transmission lines which outperformed conventional FDTD in terms of numerical dispersion and accuracy when compared with SPICE. Rebelli et al. [22, 23] proposed an MRTD approach to evaluate the signal integrity of coupled copper interconnects driven by a linear resistive and nonlinear CMOS dependent on the Daubechies scaling function at four vanishing moments. Rebelli et al. [24] applied the MRTD approach to a nonlinear CMOS using the nth-power law model to evaluate crosstalk noise in mutually coupled multiwalled carbon nanotube (MWCNT) interconnects at 32-nm technology. In the current state of the art, the MRTD method has not been used to calculate crosstalk noise, and the delay of the CMOS driver is analyzed using a modified alpha-power law model for coupled on-chip interconnects.

In this paper, the crosstalk effects of on-chip interconnects are analyzed using a Daubechies scaling function-based MRTD technique and considering the nonlinear CMOS driver modeled using a modified alpha-power law model which includes a drain conductance parameter. The most effective time domain model is presented to analyze both functional and dynamic crosstalk issues of two mutually coupled on-chip interconnect lines at 22-nm technology. The results obtained by the present model are compared with those of the conventional FDTD model and validated using HSPICE simulations.

The remainder of the paper is organized as follows. The transmission line-based MRTD model is discussed in Sect. 2, and the MRTD model comparisons and evaluation are presented in Sect. 3. Finally, conclusions are given in Sect. 4.

2 MRTD model of on-chip interconnects

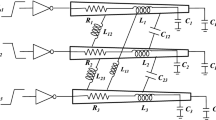

The model of two mutually coupled on-chip interconnects with driver and load is shown in Fig. 1. The parasitic capacitance of the CMOS is expressed by \(C_m\), which represents the gate-to-drain coupled capacitance, and \(C_d\), which represents the drain/source diffusion capacitance. \(R_1\) and \(R_2\) are the line resistance values, \(C_1\) and \(C_2\) are the line capacitance, \(L_1\) and \(L_2\) are the line inductance, and \(C_{L1}\) and \(C_{L2}\) are the load capacitance values of line 1and line 2, respectively. All these values are obtained per unit length (p.u.l.). Both capacitance and inductance are coupled to the interconnect lines. \(C_c\) and \(L_m\) are the p.u.l. coupling capacitance and mutual inductance of coupling interconnect lines, respectively. The position and time of the interconnect lines are denoted by x and t, respectively.

The MRTD model for two mutually coupled on-chip interconnects is built in this section using the basis function of Daubechies’ scaling function with four vanishing moments (\(D_4\)).

2.1 Model formulations for two mutually coupled on-chip interconnect lines

The telegrapher’s equations can be used to mathematically describe the coupled interconnects. The coupled on-chip interconnects are defined as in [24, 25] using the following equations.

where x and t are the positions and time, respectively; R, L, and C are two-dimensional interconnect impedance that is measured using [25]. The current and voltage variables for a the coupled interconnect lines are \(I=\left[ I_{1},I_{2} \right] ^{T}\) and \(V=\left[ V_{1},V_{2} \right] ^{T}\).

where subscript 1 corresponds to line 1 and subscript 2 corresponds to line 2. The voltage and current evaluation points on interconnect line 1 are shown in Fig. 3.

Alternatively, current and voltage points are considered in time and space to evaluate telegrapher equations. The current and voltage are separated by \(\frac{\varDelta t}{2}\) in time and \(\frac{\varDelta x}{2}\) in space for better accuracy, as shown in Fig. 2, where\(\varDelta t\) is time and \(\varDelta x\) is space represented in discretization intervals.

The interconnect line l of length is the resistive driver at \(x = 0\) and terminated at \(x = l\) is capacitive load. The line is divided consistently into Nx segments of length \(\varDelta x=\frac{l}{Nx}\) indicating the discretization voltage (V) and current (I) nodes, which are unknown coefficients, as seen in Fig. 3, where the source current is represented by \(I_0\).

The voltage and current terms can be extended using a known function (\(h_n(t)\) and \(\varPhi _{k}(x)\)). In order to solve Eqs. (1) and (2), the unknown coefficients can be found by following the method defined in [16] as:

where \(I_{k+\frac{1}{2}}^{n+\frac{1}{2}}\) is the coefficient of current expansion and \(V_{n}^{k}\) is the coefficient of voltage expansion in terms of function scaling, and the indices n and k are discrete time and space. Indices related to time and space are organized via \(t=n\varDelta t\) and \(x=k\varDelta x\). Functions \(h_n(t)\) and \(\varPhi _{k}(x)\) are defined as:

where pulse function h(t) is defined as

where \(\varPhi (x)\) signifies the Daubechies scaling function, and h(t) represents the Haar scaling function.

The following integrals [26] are considered in order to derive the MRTD technique for Eqs. (1) and (2):

where the Kronecker delta is represented by \(\delta _{k,k'}\)and \(\delta _{n,n'}\). The effective support sizes of the basis functions are indicated by \(L_s\) by considering the Daubechies scaling function as the basis function with four vanishing moments (D4). The coefficient b(i) is called the connection coefficient. Table 1 shows b(i) for \(1\le i\le L_{s}\), whereas b(i) for \(i< 1\) can be found by symmetry condition b(−1−i) =−b(i) and equals zero for \(i> L_{s}\)

where the scaling function of Fourier transform f(x) is \(\hat{\varPhi }(\lambda )\).

The following iterative calculations for current and voltage were carried out by employing the Galerkin technique [16] in Eqs. (1) and (2) and by using the test functions \(\varPhi _{k}h_{n+\frac{1}{2}}(t)\) and \(\varPhi _{k+\frac{1}{2}}h_{n}(t)\):

where

In the iterative Eqs. (8a) and (8b), the near-end voltage \(V_{1}^{n+1}\) and the far-end voltage \(V_{Nx+1}^{n+1}\) are obtained, and the iterative equations of the current and voltage near the boundary need to be modified. Near the boundary, the current is expressed by \(I_{j+\frac{1}{2}}^{n+\frac{1}{2}}\) and \(I_{Nx+1-i+\frac{1}{2}}^{n+\frac{1}{2}}\) for \(i=1,2,3,\cdots ,L_{s}-1\) and the voltage is \(V_{i}^{n+1}\) and \(V_{Nx-i+1}^{n+1}\) for \(i=2,3,\cdots ,L_{s}\) Many of these current and voltage values have a number of terms that surpass the index ranges in iterative Eqs. (8a) and (8b)

Equations (8a) and (8b) need to be decomposed using the relationship in [27] to update the iterative equations of current and voltage, which satisfies the connection coefficient b(i) given by

By substituting (9) into (8b), we get

We decompose (8b) considering a corresponding term with i as:

for at \(i=1,2,3,\cdots ,L_{s}-1\).

Equation (11) is further adapted by employing the boundary conditions as proved in Sects. 2.3 and 2.4.

2.2 Modeling of CMOS driver

The equivalent electrical circuit model for two mutually coupled on-chip interconnect lines is shown in Fig. 2. The input voltage (Vs) is a two-dimensional vector with the formula \(V_{s}=\left[ V_{s1},V_{s2} \right] ^{T}\). The interconnect lines are driven by a CMOS driver [28] that follows a modified alpha-power law model. The velocity saturation effects and the finite drain conductance parameters are included.

The latest equations for PMOS and NMOS are signified by \(m\times 1\) vectors, i.e. \(I_{p}=\left[ I_{p1},I_{p2} \right] ^{T}\) and \(In = \left[ I_{n1},I_{n2} \right] ^{T}\). The linear region transconductance parameter, threshold voltage, saturation region transconductance parameter, drain conductance parameter and velocity saturation index of NMOS (PMOS) are \(K_{ln}\left( K_{lp} \right)\), \(V_{tn}\left( V_{tp} \right) , K_{sn}\left( K_{sp} \right),\sigma _{n}(\sigma _{p}), {\text{ and }} {\alpha_{n}(\alpha _{p}}), \) respectively. The NMOS/PMOS model parameter values for the 22-nm technology node as shown in Table 2 are used for this analysis.

2.3 Modeling at the near-end boundary condition

The DIL system is modeled under boundary conditions. The current and voltage node points are at the near-end terminals defined by \(I_0\) and \(V_1\) , respectively, where the nodal analysis of the terminal equation is given by

Applying discretization and the Galerkin technique to (14), then

and

The near-end terminal voltage is carried out at k=1 from (8b)

By following the steps from Eqs. (9)–(11), Eq. (16) is decomposed as

\(\vdots\)

Iterative Eqs. (17a)–(17c) are considered computer-aided design (CAD), i.e., central difference equations. In the particular calculations, the subscript to the terms \(I_{-\frac{1}{2}}^{n+\frac{1}{2}},I_{-\frac{3}{2}}^{n+\frac{1}{2}},\cdots , I_{-L_{s}+\frac{3}{2}}^{n+\frac{1}{2}}\) has surpassed the index range. To solve this, we substitute the central difference scheme by using the forward difference scheme. By leaving the weight coefficient in each equation unchanged, iterative equations can also be obtained.

\(\vdots\)

From the above iterative Eqs. (18a)−(87c), at the near-end boundary node a voltage of \(V_{1}^{n+1}\) is obtained through the following:

In Eq. (19), substituting by \(I_0^{n+\frac{1}{2}}=\frac{I_0^n+I_0^{n+1}}{2}\) and Eq. (15a) we obtain the equation

where

2.4 Modeling at the far-end boundary condition

Similarly, the nodal analysis equation at load current \(I_{Nx+1}\) given by the far-end terminal \((k = N_x+1)\)is:

Then the final iterative equation given at the far end of the terminal is

where \(E=\left( 1+\frac{C_{L}}{\varDelta t}C^{-1}\sum _{i=1}^{L_{s}}a(i) \right)\)

where some of the term indices surpass the index ranges for all the nodes between the terminals in the algorithm extension to obtain and update the iterative equations, so a truncation method is applied by taking \(V_{k}^{n+1}\) as an example for \(k = 2, 3,\cdots , L_{s}\), and by subsequent steps of Eqs. (10) and (11) it can be decomposed (8b) as an example for \(k = 2, 3,\cdots , L_{s}\)

\(\vdots\)

\(\vdots\)

From Eqs. (23a)–(23f) stated above, it is also observed that the indices of the equation do not surpass the index ranges for the first k terms. In addition, all calculations for which the index terms surpass the index spectrum appear in the remaining \(L_{s}-k\) term. As \(L_{s}-k\) terms are out of bound, these equations are not available for iterative equations in the MRTD model. To prevent this problem, a truncation is built into the calculations where the index range is surpassed.

The first k terms can be found by summing Eqs. (23a)–(23f), and the iterative equations can be updated at \(k = 2, 3,\cdots , L_{s}\)

Using the same steps illustrated in Eqs. (23a)–(23f), an altered iterative equation of voltage at interior points, as presented in Eq. (25), and voltage near the load, as presented in Eq. (26), become \(k=L_{s}+1, L_{s}+2, \cdots ,Nx-L_{s}, Nx-L_{s}+1\)

for \(k=Nx-L_{s}+2, Nx-L_{s}+3, \cdots , N_{x}\).

Current iterative equations can also be modified by the same voltage iterative equations with minor modifications. As seen in Fig. 3, at the half-integer points, the current nodes appear, implying that all the current is located at the interior points of the terminals. Therefore, the current near the terminals needs alteration. For iterative current equations near the terminals, it is necessary to decompose (8a) using the steps of iterative voltage of the equations. The final updated iterative current equations are given as

for k =1, near at the source

for k=2, 3, ....\(\ldots\), \(L_s\)

for \(k=L_{s}+1, L_{s}+2, \cdots , Nx-L_{s}, Nx-L_{s}+1.\) at the interior point iterative equations

for \(k=Nx-L_{s}+2, Nx-L_{s}+3, \cdots , Nx\) Near the load, iterative equations are

In the context of this bootstrapping method, modified voltage and current iterative equations are tested. Firstly, in terms of historical voltage and current values, voltage iterative equations are solved at a rigid time using Eqs. (20), (22), (24)–(26). Then, Eqs. (27)–(30) solve the iterative equations of current in terms of voltage measured initially and past values of current. The Courant stability condition [20, 27] is thus known as the stable output for MRTD iterative equations.

which states that for each cell, the time of propagation must be higher than the time step, where q is the current number given by \(q=1/\sum _{i=1}^{L_{s}}\left| b(i) \right| =\vartheta \varDelta t/\varDelta x\) and \(\vartheta\), and v is the phase velocity of the line propagation. However, the boundary conditions will always satisfy the stability requirement, as these are explicitly derived from an implicit expression.

3 MRTD model validation and benchmark

The performance analyses of the structure of the two mutually coupled on-chip interconnect lines are presented in this section. The proposed model is validated in comparison to the conventional FDTD model and HSPICE simulations. The numerical computations are carried out using MATLAB. The interconnect load is driven by a CMOS driver; the interconnect dimensions are taken from the International Technology Roadmap for Semiconductors (ITRS) [29, 30]. At the 22-nm technology node, the interconnect is placed 99 nm from a ground plane. The thickness of the line is 66 nm. The width and space between the lines are equal, at 33 nm. The inter-level dielectric medium permittivity is 2.3. The length and load capacitance of the interconnects are 1 mm and 2 fF. The Vdd voltage is 0.8 V. The signal voltage swings from 0 to 0.8 V (low\(\rightarrow\)high) or 0.8 to 0 V (high\(\rightarrow\)low). The input source voltages have a transition time of 20 ps. The parasitic values of RLC for the coupled interconnect line structure are

3.1 Transient and crosstalk analysis in two mutually coupled on-chip interconnects

This section covers the transient and crosstalk analysis of the -coupled on-chip interconnect system. Line 1 is the aggressor and line 2 is the victim line, as shown in Fig. 1. On the other side of the victim line, the crosstalk effects for functional, dynamic in-phase, and dynamic out-of-phase switching are found using the proposed model, the conventional FDTD model and HSPICE simulations [31]. The transient response is investigated on the victim line. The effect of functional crosstalk is explored by modifying line 1 (aggressor) input from 0.8 V to 0 V while holding line 2 (victim) in quiescent mode. When both aggressor and victim line stimuli turn at the same time, the impact of in-phase or out-of-phase is also explored. At the far end of the victim line, the transient graph results based on the above conditions are compared. The functional, dynamic in-phase, and dynamic out-of-phase transient responses on the victim line are shown in Fig. 4a–c, respectively. Figure 4b and c demonstrate that the victim line peak solution has higher dispersion errors in the conventional FDTD method. The proposed model is superior to the conventional FDTD model in terms of precision due to its significant superiority in numerical dispersion properties. Figure 4c illustrates how the Miller effect increases the capacity, which allows signal transitions to take longer during out-of-phase than in-phase switching. The results of the proposed MRTD model correctly matched with HSPICE in all input switching situations and outperform the conventional FDTD method.

Table 3 shows the computational error associated with the estimation of functional crosstalk effects over the victim line for conventional FDTD and the proposed MRTD model in comparison to HSPICE. The efficiency of the proposed model at multiple input transition times shows an average error for crosstalk peak voltage timing of 0.42% versus 0.92% for the conventional FDTD method when compared with HSPICE. Table 4 also indicates that the proposed model correctly predicts the peak voltage, with an average error of 0.27% versus 1.05% using the conventional FDTD method when compared with HSPICE.

The computational error associated with estimating dynamic in-phase crosstalk effects over the victim line for the conventional FDTD and proposed MRTD models is shown in Table 5. The sturdiness of input transitions of the proposed model at different times has an average error of 0.53% versus 1.4% average error in the conventional FDTD method for propagation delay estimation when compared to HSPICE.

Table 6 shows the computational error associated with the estimation of dynamic out-of-phase crosstalk effects over the victim line for the conventional FDTD and proposed MRTD models. The sturdiness of input transitions at different times for the proposed model has an average error of 0.18% versus 0.38% average error in the conventional FDTD method for propagation delay estimation when compared with HSPICE. The simulation results for the proposed MRTD model match HSPICE correctly in all input switching situations and outperform the conventional FDTD model.

The graphs for peak voltage timing and peak voltage value on the victim line results in functional crosstalk generated by varying input transition time, which is shown in Figs. 5 and 6, respectively. Figures 7 and 8 illustrate the dynamic in-phase and out-of-phase crosstalk propagation delays at different input transition times. The results for both functional and dynamic crosstalk of the MRTD model are validated with HSPICE, and the proposed model outperforms the conventional FDTD model.

Figures 9 and 10 demonstrate the peak voltage timing and peak voltage on the victim line for functional switching with varying values of load capacitance \(C_L\). For instance, using an interconnect length of 1 mm with 20 space segments and 3500 time segments, the elapsed CPU time for the proposed MRTD model, the conventional FDTD model, and the HSPICE is measured using a PC Intel® Xeon® CPU operating at 3.30 GHz. The elapsed CPU times are shown in Fig. 11. The figure demonstrates the elapsed CPU times for crosstalk analysis of the coupled on-chip interconnect lines in various functional, dynamic in-phase, and dynamic out-of-phase switching. In terms of simulation time, HSPICE has a higher CPU runtime than both the MRTD and conventional FDTD models. However, the MRTD is slightly slower than the conventional FDTD due to the higher number of iterations required for better accuracy. As a result, there exists a trade-off between simulation time and accuracy.

4 Conclusion

The modified alpha-power law model is used in this paper to build an analytically dependent MRTD model for functional and dynamic crosstalk study of two mutually coupled transmission lines driven by a CMOS driver. This work provides a detailed study of a two-line coupled on-chip interconnects for functional, dynamic in-phase, and dynamic out-of-phase switching which induced crosstalk effects on the victim line. The Courant condition is strictly followed by the proposed model’s stability. The influence of input transition time on crosstalk propagation delay under dynamic and peak voltage timing is investigated, as well as the peak voltage value for functional crosstalk. With regard to HSPICE, the proposed MRTD model and the FDTD confirm that the proposed MRTD model is in good agreement with HSPICE. According to the proposed model, the results show average errors of crosstalk-induced propagation delays in dynamic in-phase and out-of-phase on-chip interconnects of 0.53% and 0.18%, respectively, and functional crosstalk has peak voltage timing of 0.42% and a peak voltage value of 0.27%. Furthermore, the proposed MRTD model and FDTD model are validated with HSPICE for peak voltage timing and peak voltage value on the victim line for functional cases of various values of load capacitance, with average error of less than 1%. When compared to HSPICE, the elapsed CPU runtime for the MRTD model is significantly less. The analysis was performed on two mutually coupled interconnect lines but it can also be extended to M mutually coupled on-chip interconnect lines.

Data availability

Data sharing is not applicable to this article as no datasets were generated or analyzed during the current study.

References

Moaiyeri, M.H., Hajmohammadi, Z., Khezeli, M.R., Jalali, A.: Effective reduction in crosstalk effects in quaternary integrated circuits using mixed carbon nanotube bundle interconnects. ECS J. Solid State Sci. Technol. 7(5), M69 (2018). https://doi.org/10.1149/2.0111805jss

Khezeli, M.R., Moaiyeri, M.H., Jalali, A.: Active shielding of MWCNT bundle interconnects: an efficient approach to cancellation of crosstalk-induced functional failures in ternary logic. IEEE Trans. Electromag. Compat. 61(1), 100–110 (2018). https://doi.org/10.1109/temc.2017.2788500

Rabaey, J.M., Chandrakasan, A.P., Nikolić, B.: Digital integrated circuits: a design perspective, vol. 7. Pearson education, Upper Saddle River, NJ (2003)

Alpert, C.J., Devgan, A., Kashyap, C.V.: RC delay metrics for performance optimization. IEEE Trans. Comput. Aid. Des. Integr. Circuits. Syst. 20(5), 571–582 (2001). https://doi.org/10.1109/43.920682

Rubinstein, Jorge, Penfield, Paul, Horowitz, Mark A.: Signal delay in RC tree networks. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2(3), 202–211 (1983). https://doi.org/10.1145/62882.62932

Masoumi, M., Masoumi, N., Javanpak, A.: A new and efficient approach for estimating the accurate time-domain response of single and capacitive coupled distributed RC interconnects. Microelectron. J. 40(8), 1212–1224 (2009). https://doi.org/10.1016/j.mejo.2009.04.004

Ismail, Yehea I., Friedman, Eby G., Neves, Jose L.: Equivalent Elmore delay for RLC trees. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 19(1), 83–97 (2000). https://doi.org/10.1109/43.822622

Ismail, Y.I., Friedman, E.G.: Effects of inductance on the propagation delay and repeater insertion in VLSI circuits. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 8(2), 195–206 (2000)

Agarwal, K.: Sylvester, Dennis, Blaauw, David: Modeling and analysis of crosstalk noise in coupled RLC interconnects. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 25(5), 892–901 (2006). https://doi.org/10.1109/TCAD.2005.855961

Cui, J.P., Zhao, W.S., Yin, W.Y., Jun, H.: Signal transmission analysis of multilayer graphene nano-ribbon (MLGNR) interconnects. IEEE Trans. Electromag. Compat. 54(1), 126–132 (2011). https://doi.org/10.1109/TEMC.2011.2172947

Li, X.C., Mao, J.F., Swaminathan, M.: Transient Analysis of CMOS-Gate-Driven \(RLGC\) Interconnects Based on FDTD. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 30(4), 574–583 (2011). https://doi.org/10.1109/TCAD.2010.2095650

Liang, F., Wang, G., Lin, H.: Modeling of crosstalk effects in multiwall carbon nanotube interconnects. IEEE Trans. Electromag. Compat. 54(1), 133–139 (2011). https://doi.org/10.1109/temc.2011.2172982

Kumar, V.R., Kaushik, B.K., Patnaik, A.: Crosstalk noise modeling of multiwall carbon nanotube (MWCNT) interconnects using finite-difference time-domain (FDTD) technique. Microelectr. Reliab. 55(1), 155–163 (2015). https://doi.org/10.1016/j.microrel.2014.09.001

Tentzeris, E.M., Robertson, R.L., Harvey, J.F., Katehi, L.P.B.: Stability and dispersion analysis of Battle-Lemarie-based MRTD schemes. IEEE Trans. Microwave Theory Tech. 47(7), 1004–1013 (1999). https://doi.org/10.1109/22.775432

Alighanbari, A., Sarris, C.D.: Dispersion properties and applications of the Coifman scaling function based S-MRTD. IEEE Trans. Antennas Propag. 54(8), 2316–2325 (2006). https://doi.org/10.1109/tap.2006.879194

Krumpholz, M., Katehi, L.P.B.: MRTD: new time-domain schemes based on multiresolution analysis. IEEE Trans. Microwave Theory Tech. 44(4), 555–571 (1996). https://doi.org/10.1109/22.491023

Grivet-Talocia, S.: On the accuracy of Haar-based multiresolution time-domain schemes. IEEE Microwave Guided Wave Lett. 10(10), 397–399 (2000). https://doi.org/10.1109/75.877224

Fujii, M., Hoefer, W.J.R.: Dispersion of time domain wavelet Galerkin method based on Daubechies’ compactly supported scaling functions with three and four vanishing moments. IEEE Microwave Guided Wave Lett. 10(4), 125–127 (2000). https://doi.org/10.1109/75.846920

Massy, I., Ney, M.M.: A hybrid MRTD-FDTD technique for efficient field computation. In: Ahmed, I., Chen, Z.D. (eds.) Computational electromagnetics-retrospective and outlook, pp. 245–278. Springer, Singapore (2015)

Tong, Z., Sun, L., Li, Y., Luo, J.: Multiresolution time-domain scheme for terminal response of two-conductor transmission lines. Math. Probl. Eng. (2016). https://doi.org/10.1155/2016/8045749

Tong, Z., Sun, L., Li, Y., Angulo, L.D., Gonzalez, G., Salvador, L.J.: Multiresolution time-domain analysis of multiconductor transmission lines terminated in linear loads. Math. Probl. Eng. (2017). https://doi.org/10.1155/2017/9845702

Rebelli, S., Rao, N.B.: A novel MRTD model for signal integrity analysis of resistive driven coupled copper interconnects. COMPEL-Int. J. Comput. Math. Electr. Electr. Eng. (2018). https://doi.org/10.1108/COMPEL-12-2016-0521

Rebelli, S., Nistala, B.R.: An efficient MRTD model for the analysis of crosstalk in CMOS-driven coupled Cu interconnects. Radioengineering 27(2), 532–540 (2018). https://doi.org/10.13164/re.2018.0532

Rebelli, S., Nistala, B.R.: A multiresolution time domain (MRTD) method for crosstalk noise modeling of CMOS-gate-driven coupled MWCNT interconnects. IEEE Transactions on Electromagnetic Compatibility 62(2), 521–531 (2019). https://doi.org/10.1109/temc.2019.2903728

Paul, C.R.: Incorporation of terminal constraints in the FDTD analysis of transmission lines. IEEE Trans. Electromag. Compat. 36(2), 85–91 (1994). https://doi.org/10.1109/15.293284

Pan, G.W.: Wavelets in electromagnetics and device modeling, vol. 159. Wiley, London (2003)

Dogaru, T., Carin, L.: Multiresolution time-domain algorithm using CDF biorthogonal wavelets. IEEE Trans. Microwave Theory Tech. 49(5), 902–912 (2001). https://doi.org/10.1109/22.920147

Kumar, M.G., Chandel, R., Agrawal, Y.: An efficient crosstalk model for coupled multiwalled carbon nanotube interconnects. IEEE Trans. Electromag. Compat. 60(2), 487–496 (2017). https://doi.org/10.1109/TEMC.2017.2719052

International Technology Roadmap for Semiconductors (ITRS) 2013.[Online]. Available:http://www.itrs.net/

Badugu, D., Madhuri, S.S.: Crosstalk noise analysis of on-chip interconnects for ternary logic applications using FDTD. Microelectr. J. 93, 104633 (2019). https://doi.org/10.1016/j.mejo.2019.104633

Synopsys for HSPICE tools, (2008). [Online]. Available:http://www.synopsys.com

Acknowledgements

This research was sponsored by the University Grants Commission (UGC) fellowship. The authors would like to thank the Principal, UCE(A) Osmania University for all their support.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Gugulothu, B., Bhukya, R.N. Crosstalk noise analysis of coupled on-chip interconnects using a multiresolution time domain (MRTD) technique. J Comput Electron 21, 348–359 (2022). https://doi.org/10.1007/s10825-021-01828-y

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-021-01828-y