Abstract

This research paper investigates the new multilevel connections with minimum number of components as a voltage source inverter (VSI) which is connected in parallel as shunt active power filter (SAPF) for the purpose of the improving power quality and reactive power compensation in power systems. The main contribution of this paper is the design & development of modular structure which is capable of producing a wide range of output levels (9,11,13,15,17,19,21,23,25,27,29 and 31) using Asymmetric PV sources. A comparative study is made with other (27-level) reduced multilevel connection (RMC) topologies suitable for asymmetric input sources from solar photovoltaics (SPV). In addition, the state space analysis and the loss calculations are performed in order to ensure that the inverter is superior to the conventional topologies. The switching angles are determined using Particle Swarm Optimization (PSO) method. The implementation part of RMC is carried out with the selective harmonic elimination (SHE) which mitigates harmonics in the system. MATLAB/Simulink software is used for modelling of the proposed system. An Experimental setup of the proposed multilevel connections is developed and then it is experimentally investigated. A capacity of 3 KWp Solar PV system which feeds the DC input to the developed prototype. On the basis of the research findings, it is possible to draw the conclusion that the proposed inverter topology minimizes the voltage harmonics by 2.56% and current harmonics by 2.33% which enhances power quality, compensates the reactive power, lessens the number of components used by 12 and more cost effective.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

The rising need for electricity has led to a widespread adoption of renewable energy sources(RESs). This means we need to do something to extend the usefulness of our most basic forms of energy. To extend the availability of fossil fuels, various distinct methods have been developed. Efficient use of existing power sources is one option, as is expanding the use of renewable energy technologies like solar panels, wind turbines, thermal energy conversion from the ocean, wave energy converters, and so on. As a matter of procedure, power electronic converters are liable for meeting those commitments by using an inverter (DC to-AC converter) that produces an asymmetrical square wave. Low-pass filters are employed to eliminate the high and low harmonics of a waveform, improving its overall quality. From the studies of [1,2,3,4], it can be seen that, two level inverters were firstly conceived to convert AC into DC. However, these converters had a number of drawbacks, including excessive switching losses, high switching losses, high THD, high voltage stress (dv/dt), low efficiency, and the requirement for filters, among others. This has led to the development of multilevel inverters (MLI), which are ideal for medium-voltage and high-power applications. MLI produces a frequency response with a better emission than two level inverters. [5, 6], find out by comparing multilevel inverters to two-level inverters, there are various advantages such as less voltage stress on switches, less harmonic distortion on voltage waveforms, and less dv/dt on switching devices. Its benefits are mostly concentrated on enhancing the output signal quality and increasing the nominal power of the inverters. [7,8,9,10,11,12,13,14], suggests that researchers and scholars may now concentrate exploring emerging innovations that must be linked to renewable power facilities due to the increasing attention on sustainable power resources, particularly solar photovoltaic (SPV) power. Multilevel inverters/converters (MLIS), particularly, the field which has drawn the interest of many scholars [15]. shows that the usage of renewable energy is now more advantageous from a political and financial standpoint. Due to contemporary technology, ambiently renewable energies, encompass energy from the sun panels along with energy from the wind turbines, there are plenty different categories in energy and have grown incredibly common and challenging. In reality, PV solar sources have a variety of uses, such as pollution-free sources. [16,17,18,19,20,21,22,23,24,25,26,27,28,29,30,31,32], through their analysis shows cascaded H Bridge Multilevel (CHB) Inverters are typically utilised in static var uses, like as battery-based and renewable energy applications. The wye form or the delta form can be used with CHB multilevel inverters. From [30] it can be seen that modules can also be used to create multilayer converters, giving rise to multi-modular converters (MMCs). A certain multilevel converter can produce a levels using a DC source and two switches, hence it may be regarded as a module. More levels can be attained if these modules are joined in succession. Through the study by [33] it is a common fact that problems for grid-tied users significant concern with voltage stability, that can be brought on by frequency inverters in photovoltaic systems and affects utility firms as well as power variance. From the analysis of [34] non-linear electric and electronic loads cause harmonics, which are multiples of the fundamental frequency. From studies of [35] multilevel converters with lower power switches & very few circuit components are necessary to construct in order to decrease the price, and inefficiencies in the multilevel inverter and satisfy the power needs. But at the other end, the symmetrical MLI has the ability to be a more effective PV converter because it can raise the inverter's voltage levels despite running at a lower switching frequency. [36,37,38,39,40,41,42,43,44,45,46,47,48,49,50,51,52,53,54,55,56,57,58], states the distortion of the harmonic components also with the resultant spectrum are also among the key benefits of using the SHE methodology over alternative methods. Since the total eradication of a specific set of harmonics, being the primary function of such filters, is guaranteed, it is essential to take into account this modulating technique in order to enhance the performance of passive active filters.

From Table 1 Based on the research findings the objectives to design the proposed topology has the following benefit.

-

Reduces the number of Power switch components usage.

-

Reduces the usage of DC sources, Capacitors & gate drive circuits.

-

Increases the number of output voltage level with lesser number of components.

-

Reduces the total harmonic distortion as per the IEEE519 standard.

-

Implementation of SHE based on soft-computing technique with PI controller improves voltage regulation.

-

Minimizes the losses which leads to the improvement of efficiency.

-

Better the reactive power compensation

The organisation of this article is as follows: The overview of reduced multilevel connections is covered in Sect. 2. The converter's operating modes are included in the design. The state space analysis of the converter is covered in Sect. 3. The modelling of solar PV Module is covered in Sect. 4. The Theory of SHE is covered in Sect.5. The switching process of the proposed converter is covered in Sect. 4. The loss analysis of the proposed RMC is shown in Sect. 5. The system's reactive power compensation is described in Sect. 6. The cost calculation is presented in Sect. 7. The result and discussion findings are presented in Sect. 8. The comparative analysis of an asymmetrical 27-level inverter is covered in Sect. 9 The ultimate conclusions are presented in Sect. 10.

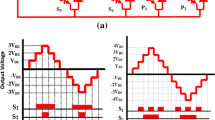

2 Proposed multilevel connections

The proposed approach only needs twelve switches to build the power circuit, while the conventional and trinary structures each need a different control circuit in order to reach level 27. Figs.1 and 2a depicts the structure of a simple, single-phase RMC. The switching sequence indicates in order to achieve 27 levels, Fig. 2b the polarity generation switches that generate positive half-cycles (T1,T2) and negative half-cycles (T3,T4) must be set to the ON position, while the switches responsible for producing level generation (S1–S4, B1–B4) as shown in Fig. 2c must be adjusted so that intermediate levels are produced. The PV system supplies the DC input voltages. Most likely, PV1, PV2, PV3& PV4 are the inputs. PV1 is the only source of energy for the first tier while the other PV sources are running. As with the previous levels, Level 27 is unlocked by toggling switches. According to the PV inputs, the RMC has the potential to produce 11 different levels. The range of possible output levels from the RMC given the PV inputs. The level 27 is generated by a combination of input DC sources fed by the PV array in the following ratio: 1:2:3:7.

Table 2 shows the elements of the proposed inverter based on number of levels and number of units on symmetric & Asymmetric Configuration.

When the developed structure is connected in cascaded mode Fig. 3 the amount of voltage levels obtained is 2NL i.e., it will be equal to 54-Voltage Levels for the above topology.

The proposed design has various modes of operation which are shown in Fig. 4a–n. During the positive half cycle the voltages + 1Vdc, + 2Vdc, + 3Vdc, + 4Vdc, + 5Vdc, + 6Vdc, + 7Vdc, + 8Vdc, + 9Vdc, + 10Vdc, + 11Vdc, + 12Vdc, + 13Vdc are obtained. For the negative obtained. e half cycle the output voltages obtained are– 1Vdc, – 2Vdc, – 3Vdc, – 4Vdc, – 5Vdc, – 6Vdc, 7Vdc, 8Vdc, – 9Vdc, – 10Vdc, – 11Vdc, – 12Vdc, – 13Vdc are. Table 3 shows the current path, number of switches in conduction and the developed voltage level corresponding to the switching strategy. The Positive voltage levels V0 = + 1Vdc, + 2Vdc, + 3Vdc, + 4Vdc, + 5Vdc, + 6Vdc, + 7Vdc, + 8Vdc, + 9Vdc, + 10Vdc, + 11Vdc, + 12Vdc, + 13Vdc are obtained by using the same switching strategies at positive half cycle. In the negative half cycle, the polarity generation switches T1 and T2 are switched on and Stages (I-XIV) are achieved. Tables 4 and 5 show the voltage & current stress of the switches at each level which is significantly reduced from the proposed topology which leads to the reduction of switching & conduction loss. By the reduction of switching & conduction loss the overall efficiency is improved. Figure 5a, b shows the switching and conduction loss of the proposed topology when compared to the existing topology.

3 State space modeling of proposed RMC

A system is represented in state space model by taking the systems input, output parameters and state variables.

General state space model is given by

Here X = State Variable, U = Input Variable, Y = Output Variable & \(\dot{X}\) = State Derivative The state space model of the RMC is shown in Fig. 6.

Let,

The variable Hb is denoted for the H-Bridge in the proposed topology. Hence, the net output VL for the inverter is given by:

where, Vdc is the sum of each dc source, and \(\vartheta 1\) to \(\vartheta 4\) is the comparator output signals.

By applying KVL to the circuit:

where, R0=Re+ Rinductor , and Re, Rinductor, Rswitch, and L are the total load resistance, internal resistance of inductor, Resistance of all conducting IGBTs in the ON state and load inductance in mH at each level. In this RMC the total conducting component in each level is same therefore in equation (15) substitute the value of VL from equation (14).

Assuming the state variable as \(X={i}_{L(t)}\) (current through the inductor) and the input variable \(U ={\mathrm{V}}_{\mathrm{dc}}\)

where,

\(A = - \left( {R_{{{\text{Switch}}}} + R_{O} } \right)\); \({\text{B}} = [1111]\left[ {\vartheta 1{\text{Hb}}\vartheta 2{\text{Hb}}\vartheta 3{\text{Hb}}\vartheta 4{\text{Hb}}} \right]^{{\text{T}}}\)

The output voltage across the load

where \(Y = V_{{{\text{out}}}}\); \(C = \left( {R_{0} + L\frac{{{\text{d}}i_{L} (t)}}{{{\text{d}}t}}} \right)\)

Therefore, the generalized (State space & Output) equation for proposed topology is given by:

where Vdc is the magnitude of each dc source fed from solar PV and iL(t) is the current through the inductor.

4 Modelling of solar PV module

Photo Voltaic system consist of.

-

Photo voltaic modules

-

Boost converter (DC/DC Converter).

-

Maximum Power Point Tracking (MPPT) controller.

Solar PV cells are contained in Solar PV modules (SPV), which are connected in series. By interconnecting the PV segments in parallel and series, a solar PV array is created. The voltage–current (V–I) characteristics of individual solar cells vary. In order to simulate the MPPT boost converter, various elements are used, including the PV model.The major purpose of the PV model is to generate the Current–Voltage I–V characteristic curve of PV module. A reverse biased diode that is shunted across a resistor Rsh is used in the equivalent circuit of a solar panel, as shown in Fig. 7.

4.1 Design of solar PV panel

Each solar cell has an open circuit voltage of 0.5 V and a short circuit current of 7 A. There are 24 solar cells in a single module. At typical test circumstances (1000 W/m2 and 25 °C), these cells are wired in series to provide 12 V, 7A. A 24 V, 7 A solar PV array is created by connecting two single modules in series. [54, 55],. The fixed interconnection design is put into place, and the ratio of DC sources is kept at 1: 2: 3: 7. The designed inverter produces 27 levels of output voltage from four DC sources.

4.2 DC–DC (BOOST) converter with MPPT control

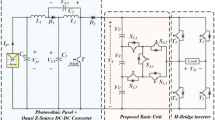

To deal with the issue of the PV module being partially shaded, DC-DC converters are used. The Converter used in the proposed system is a boost converter. [48, 49]. A boost converter is a most efficient type of converter module that has been incorporated into this system. The boost converter is essentially a DC–DC converter that generates an output voltage that is higher than the input voltage.

As shown in Fig. 8, where the inducer, diode, capacitor and switches are the components of the boost converter which provides there required voltage level with the MPPT controller, the MPPT technique provides the extracted voltage and current from the PV source to the boost converter.

4.2.1 Maximum power point tracking (MPPT) method

To achieve 27 Levels, the proposed inverter uses various DC Sources. So, a discrete boost converter integrated with MPPT is used to obtain the desired output voltage [48, 49],. The power output by PV panels can be increased by using the MPPT method as shown Fig. 9 which employs an Adaptive modified perturb and observe algorithm [59]

5 Theory on selective harmonic elimination (SHE)

Among the various modulation techniques (Sinusoidal PWM, Multi-Carrier PWM, SHE PWM & Space-Vector PWM) the most efficient way to eliminate specific lower order harmonics is done by SHE-PWM[55],.It is derived from the Fourier transform, which contains a variety of triggering states over its complete cycle. These degrees of freedom can be calculated to verify that it is possible to generate a fundamental voltage component without (S-1) harmonics. By developing a set of equations to indicate when the triggering of switches should occur, these degrees of freedom are employed. In this work it is mainly focused to cancel the odd order harmonics.

In order to lower the 'S ang-1' harmonics for an N-level inverter, 'S ang' triggering angles must be determined. Therefore, in order to get the triggering angles for the 27-level RMC, the following Equation must be utilized.

The switching angles must adhere to the following requirements:

Equations below presents the nonlinear equations required to obtain the triggering angles.

The resultant equations, however, must be solved using quantitative tools because they are nonlinear and transcendental in nature. Due of limitations in computing the optimal switching angles mathematically, optimization techniques like Newton Rampson (NR), Particle Swarm Optimization (PSO) and Genetic Algorithm (GA) are employed to compute the triggering angles. The PSO approach is superior among other methods [59]. in terms of switching angles prediction accuracy, fundamental output voltage generation and total harmonic distortion reduction in the case of different level CHB inverters. So, in this research work, the switching angles determined for the asymmetric 27-level RMC using the PSO approach is shown in Fig. 10.

By solving the preceding equations, we obtain 13 triggering angles from that the harmonics of orders 5, 7, 11, 13, 17, 19, 23, 25, 29, 31, 35, and 34 are cancels each other. The SHE approach was applied for the 27-level RMC.For RMC with Mi = 0.95, the corresponding switching angles are listed in Table 6 which is shown in Fig. 11.

6 Reactive power compensation in power system

Generally Reactive power can be compensated using solar power systems as per the IEEE1547a standard (Fig. 12). The designed controller injects reactive power into the photovoltaic inverter and smooths its apparent power transition. To reduce voltage, drop, reactive power is fed into the distribution line, when real power drops unexpectedly. However, frequent reactive power from the PV fed inverter generates reactive current, which increases power system losses. When the PV system's power reaches the proportional gain Kp maximum, the slope of the apparent power of inverter (Sin v) is fixed with a constant integral gain Ks value.

The MPPT controller receives PV panel voltage and current. The proposed system tracks solar panel power using the Adaptive Improved P and O method [58]. Cascaded control loops use the MPP block output signal as a voltage reference. A PLL determines grid phase and angle. The PI controller detects the DC error. The PLL angle and PI controller current signal form the reference active current component, \({{i}_{\mathrm{a}}}^{\mathrm{ref}}\). Q produces reactive current, \({{i}_{\mathrm{a}}}^{\mathrm{ref}}\). The inner current controller of the cascaded control system tracks the sum of the actual and reactive current references The PI controller receives the error from the inverter current and the reference currents (\({{i}_{\mathrm{a}}}^{\mathrm{ref}}\) + \({{i}_{\mathrm{r}}}^{\mathrm{ref}}\)). The SHE block receives the output from PI. The proposed inverter's switches are triggered by pulses from the SHE block, compensating reactive power.

The reactive power Q can be calculated by performing the steps.

Step 1: Sense the Grid voltage and Inverter current.

Step 2: Determine the active power, the active power's rate of change over time, and the apparent power.

Step 3: After determining \(\frac{\mathrm{d}{P}_{\mathrm{inv}}}{\mathrm{d}t}\) value, equate the obtained \(\frac{\mathrm{d}{P}_{\mathrm{inv}}}{\mathrm{d}t}\) value with the proportional gain \((-{K}_{\mathrm{p}})\).This stage decides the amount of reactive power needed for compensation by the proposed inverter.

Step 4: This stage helps to determine, At this point, we determine how much reactive power the proposed inverter needs to compensate for.

Step 5: The apparent power \({S}_{\mathrm{inv}}\) is updated by using \(\frac{\mathrm{d}{S}_{\mathrm{inv}}}{\mathrm{d}t}\).The updated \({S}_{\mathrm{inv}}\) and the \({P}_{\mathrm{inv}}\) values are used to determine reactive power \((Q)\). From this \(Q\) value, the reactive reference current is achieved. The Q value is updated from time to time to successfully fix the reactive power compensation (Fig. 13)

.

7 Cost calculation

The total cost of the RMC depends on the voltage and current rating of the switches. It also depends on the voltage blocking capacity of switces if it doubles it cost of RMC will be more.The cost of RMC depends on the number of IGBT’s, number of driver circuits, number of different DC sources and standing voltage rating of switches.The quantity of IGBTs NIGBT, the quantity of driver circuits (Ndriver), the variety of DC sources (Ndiff DC), and the standing voltage rating of the switches (VTSV) all affect the price of RMC.

The weight coefficient of total standing voltage on switches is ζ which is inverse to total power switches. Greater total standing voltage requires higher ζ. The proposed RMC uses fewer NIGBT, Ndriver, and lesser VTSV than the conventional configuration.

8 Results and discussion

8.1 Simulation results

Utilizing MATLAB/Simulink, the proposed PV fed RMC is simulated. A Diode rectifier in combination with R- L Load is used as Non-Linear Load. The simulation results is obtained for the duration 0.01–0.2 s for the proposed shunt active filter. To achieve a steady, constant DC voltage A series connection is made among 2,4,6,14 batteries of 12 V range. This RMC generates a peak voltage of 312 V. The DC inputs of 24 V, 48 V, 72 V and 168 V as in Fig. 14 The switching angles produced using PSO techniques are stored in the lookup table for switching sequences generation. The output waveform of the 27-level RMC is shown in Figs. 15 and 16 along with an analysis using the Fast Fourier Transform (FFT). The system's measured Total Harmonic Distortion (THD), which is does not include RMC-based APF, is shown in Fig. 16. The proposed active power filter is changed from 0.05 to 0.2 s in order to acquire the simulation results in the simulation model. Figure 16 displays the measured THD of the RMC-based APF.The measured voltage THD value for 0 ≤ t ≤ 0.05 s in Fig. 16c is non-sinusoidal in character and has a measured THD value of 30.43%.(not including APF). The measured voltage THD value drops to 3.11% when the APF is turned on for 0.05 ≤ t ≤ 0.2 s, and the current THD value is obtained as 0.81%, which is within IEEE -519 standards and suggests the waveform obtained is sinusoidal in nature. The measured current and voltage THDs after compensation are shown in Fig. 16a, b. After compensation, there is some short-term fluctuation in the source voltage, which has a harmonics of 3.11% The system's source voltage and source current are shown in Fig. 17. The system's load voltage and load current are shown in Fig. 18. The source current is initially not sinusoidal due to the nonlinear load, as shown in the Fig. 16 However, after the SAPF is switched from 0.05 to 0.2 s, it is discovered that the source current more closely resembles a sinusoidal waveform. When nonlinear loads are used in the load side of the SAPF, the RMC generates compensation currents that act as right angles to the harmonic currents generated by those nonlinear loads. Harmonic currents and compensation currents cancel each other at the Point of Common Coupling (PCC), which frees from the source current harmonics (Figs. 19, 20 and 21).

8.2 Experimental validation

The prototype of the proposed RMC-based SAPF is developed. The developed prototype's is shown in Fig. 22. Each leg of the voltage source inverter consists of 12 switches FGA25N120 with a gate driver HCPL316J running at a switching frequency of 1 kHz to test the performance of the proposed system. To reduce current harmonics and balance reactive power, coupled inductors (1.9mh) are connected in series with the RMC (Fig. 23). As the load, a diode rectifier is used in. The Components list with their respective rating are shown in Table 7. The voltage and current sensors connected to the Controller board's analogue to digital converters generate the reference currents for the SAPF. Harmonics are introduced into the system through the introduction of a nonlinear load on the DC side. The Solar PV Systems parameters for hardware design are shown in Table 8. The hardware output of the 27-level RMC is shown in Fig. 24. The hardware output of the three phases' source voltage is shown in Fig. 22. The compensating currents generated by the RMC-based SAPF to reduce the current harmonics in the source side are shown in Fig. 23. The hardware output of the load current is shown in Fig. 24. The hardware output of the source current is shown in Figs. 25 and 26. Due to the injection of compensating currents at PCC, it can be shown in Figs. 27 and 28 that the source current has a sinusoidal nature.

The active and reactive power of the system are represented in Fig. 21. The proposed PV fed RMC-based APF corrects the source side's power factor almost to unity by injecting harmonic currents. Only active power is provided from the source side, as can be shown in Fig. 21. The figure also shows that source-side reactive power delivered is almost negligible, resulting in a power factor of unity there. As a result, the RMC-based APF injects harmonic currents that are similar in size but in phase opposition at PCC to make the distorted source current approximately sinusoidal. Consequently, the proposed technology improves the quality of the power.

Figure 29 presents the change in output current when the resistive load is switched from 0 to 100 Ω. Figure 27 illustrates the change of output current when the RL load is changed from 50Ω + 100mh to 50Ω + 50mh (Fig. 30).

Figure 31 illustrates the switching reaction of the system with and without SAPF. From Fig. 26, it is clearly seen that the source current before switching on the ASAPF is non-sinusoidal in nature and after switching exhibits there is a sinusoidal current wave of the injection of the compensation current.

As a result, RMC topology improves power quality. The frequency spectrum of the proposed topology is acquired using a power quality analyzer and is shown in Fig. 32. The proposed topology, when used with SAPF, produces measured current THD of 2.33% and measured voltage THD of 2.61%, as can be shown in Fig. 32. The permitted IEEE standard limitations are not exceeded by this measured THD %. It has been demonstrated through simulation and experimentation that the suggested RMC decreases THD, raises voltage levels with fewer components, and compensates reactive power (Fig. 33).

9 Comparative analysis

Table 9 shows the comparison of the proposed work with other existing work, From the table, it is clear that the proposed 27 Level Multilevel inverter topology reduce the THD by 2.61 which is lower than 5%,satisfying the standard of IEEE519.

10 Conclusions

In this research paper, Novel multilevel connections have been Modelled & Developed, when compared with conventional topologies it is more superior in terms of number of components, number of levels, simple switching pattern, reduction in total losses with improved efficiency.Interms of switch count, proposed topology uses only 12 IGBT’s & only 4 DC sources with various configuration for achieving 27-Levels.And switch stress is reduced to nearly 50% which leads to the improvement of efficiency. Modelling of PV Panels is carried out with integrated Step-up Converter(Boost converter) which uses Adaptive Modified P&O (MPPT) method for voltage regulation. In terms of harmonic mitigation, the SHE method is implemented with Particle swam optimization technique for the generation of 13 switching angles apart for this, the cost calculation is also done for the proposed method. Simulation analysis is carried out with the help of MATLAB-SIMULINK (R2020A) which proves that the total harmonic distortion is reduced to 3.62% for voltage and 3.85% for current. The Proposed RMC is experimentally investigated & Votlage THD is around 3.11% & Current THD is around 0.81% which is less as per IEEE 519 standard. Further, the developed inverter acts as shunt active filter is for reactive power compensation in power system application.Finally, this paper is concluded with the comparative analysis with other recent work.

References

Ullah M, Shah SW, Ali F (2022) Multilevel inverter topology having reduced number of input DC sources and switches. Int J Eng Works 9(03):89–99

Babaei E, Kangarlu MF, Mazgar FN (2012) Symmetric and asymmetric multilevel inverter topologies with reduced switching devices. Electr Power Syst Res 86:122–130

Babaei E, Laali S, Bayat Z (2015) A single-phase cascaded multilevel inverter based on a new basic unit with reduced number of power switches. IEEE Trans Ind Electron 62(2):922–929

Harbi IA, Azazi HZ, Lashine AE, Elsabbe AE (2018) A higher levels multilevel inverter with reduced number of switches. Int J Electron 105(8):1286–1299

Alishah RS, Hosseini SH, Babaei E, Sabahi M, Gharehpetian GB (2016). New high step- up multilevel converter topology with self- voltage balancing ability and its optimization analysis. 1–11

Gautam SP, Kumar L, Gupta S (2018) Single-phase multilevel inverter topologies with self-voltage balancing capabilities. IET Power Electron 11(5):844–855

Arif MSB, Sarwer Z, Siddique MD, Ayob SM, Iqbal A, Mekhilef S (2021). Asymmetrical multilevel inverter topology with low total standing voltage and reduced switches count. Int J Circ Theor Appl. 1–19.

Varsha S (2013).New topology with re- duced number of switches in asymmetrical cascaded mul- tilevel inverter. In Fifth International Conference on Advances in Recent Technologies in Communication and Computing (ARTCom 2013)

Arunima S, Bindu S, Unni KP (2020) A flyback converter based asymmetrical cascaded h-bridge 27 level grid connected inverter from a single source using FPGA. In: 2020 International Conference for Emerging Technology, INCET 2020, 1–6

Periyaazhagar D, Irusapparajan G (2019) Design and completion of asymmetric single phase 27 level cascaded mli for various pwm scheme. Int J Innov Technol Explor Eng 8(6):792–797

Muñoz J, Gaisse P, Baier C, Rivera M, Gregor R, Zanchetta P (2016). Asymmetric multilevel topology for photovoltaic energy injection to microgrids. In: 2016 IEEE 17th Workshop on Control and Modeling for Power Electronics, COMPEL 2016.

Monicka JG (2016) A modified topology for three phase asymmetric multilevel inverter. World Appl Sci J 34(10):1343–1350. https://doi.org/10.5829/idosi.wasj.2016.1343.1350

Vijayaraja L, Kumar SG, Rivera M (2021) An investigation and design of symmetric and asymmetric inverter for various applications. Electr Electron Dev Circuits Mater Technol Chall Solut. https://doi.org/10.1002/9781119755104.ch25

Shunmugham Vanaja D, Stonier AA (2020) A novel PV fed asymmetric multilevel inverter with reduced THD for a grid-connected system. Int Trans Electr Energy Syst 30(4):e12267

Vivek P, Muthuselvan NB (2021). Investigation on photovoltaic system based asymmetrical multilevel inverter for harmonic mitigation. In: Proceedings of the 7th International Conference on Electrical Energy Systems, ICEES 2021, 334–339

Azli NA, Choong YC (2006). Analysis on the perfomance of a three-phase cascaded h-bridge multilevel inverter. In: First International Power and Energy Conference.

Ajami A, Oskuee MRJ, Mokhberdoran A, van den Bossche, (2014) A developed cascaded multilevel inverter topology to minimise the number of circuit devices and voltage stresses of switches. IET Power Electron 7(2):459–466

Samanbaksh R, Ibanez FM, Koohi P, Martin F (2021) A new asymmetric cascaded multilevel converter topology with reduced voltage stress and number of switches. IEEE 9:92276

Hosseinpour M, Seifi A, Feyez E (2020) A new symmetric/asymmetric multilevel inverter based on cascaded connection of sub-multilevel units aiming less switching components and total blocked voltage. J Telecommun 12:53

Babaei E, Laali S, Alilu S (2014) Cascaded multilevel inverter with series connection of novel H-bridge basic units. IEEE Trans Industr Electron 61(12):6664–6671

Kangarlu MF, Babaei E (2012) A generalized cascaded multilevel inverter using series connection of submultilevel inverters. IEEE Trans Power Electron 28(2):625–636

Massoud AM, Finney SJ, Cruden AJ, Williams BW (2007) Three-phase, three-wire, five-level cascaded shunt active filter for power conditioning, using two different space vector modulation techniques. IEEE Trans Power Deliv 22(4):2349–2361

Ranjith Kumar G, Zhu GR, Lu J, Chen W, Li B (2017) Thermal analysis and reliability evaluation of cascaded H-bridge MLPVI for grid-connected applications. J Eng 2017(13):1595–1599

Sonti V, Jain S, Bhattacharya S (2017) Analysis of the modulation strategy for the minimization of the leakage current in the PV grid-connected cascaded multilevel inverter. IEEE Trans Power Electron 32(2):1156–1169

Uthirasamy R, Kumar Chinnaiyan V, Ragupathy US, Karpagam J (2018) Investigation on three-phase seven-level cascaded DC-link converter using carrier level shifted modulation schemes for solar PV system applications. IET Renew Power Gener 12(4):439–449

Villanueva E, Correa P, Rodriguez J, Pacas M (2009) Control of a single-phase cascaded H-bridge multilevel inverter for grid-connected photovoltaic systems. IEEE Trans Ind Electron 56(11):4399–4406

Wu F, Li X, Feng F, Gooi HB (2015) Modified cascaded multilevel grid-connected inverter to enhance european efficiency and several extended topologies. IEEE Trans Ind Inf 11(6):1358–1365

Xiao B, Hang L, Mei J, Riley C, Tolbert LM, Ozpineci B (2015) Modular cascaded H-bridge multilevel PV inverter with distributed MPPT for grid-connected applications. IEEE Trans Ind Appl 51(2):1722–1731

Coppola M, Di Napoli F, Guerriero P, Iannuzzi D, Daliento S, Del Pizzo A (2016) An FPGA-based advanced control strategy of a GridTied PV CHB inverter. IEEE Trans Power Electron 31(1):806–816

Samanbakhsh R, Ibanez FM, Koohi P, Martin F (2021) A new asymmetric cascaded multilevel converter topology with reduced voltage stress and number of switches. IEEE Access 9:92276–92287

Nikouei B, Tan NML, Taghizadeh SF, Younis MAA, Tan NML, Taghizadeh SF, Design MAAY (2015) Design of a 27-level cascaded converter as FACTS device for voltage sag mitigation. Austr J Electr Electron Eng 12(3):232–241. https://doi.org/10.1080/1448837X.2015.1092994

Hasan MM, Abu-Siada A, Islam SM, Dahidah MSA (2018) A new cascaded multilevel inverter topology with galvanic isolation. IEEE Trans Ind Appl 54(4):3463–3472. https://doi.org/10.1109/TIA.2018.2818061

Aliaga R, Rojas D, Muñoz J, Villalón A (2020) 27 - Level asymmetric multilevel inverter for photovoltaic energy conversion. J Power Electron 20:904–915

Reddy AKVK, Narayana KVL (2020). Optimal total harmonic distortion minimization in multilevel inverter using improved whale optimization algoritham, 21(3).

Kumar DG, Ganesh A, Sireesha NV, Kshatri SS, Mishra S, Sharma NK, Bajaj M, Kotb H, Milyani AH, Azhari AA (2022) Performance analysis of an optimized asymmetric multilevel inverter on grid connected SPV system. Energies 15(20):1–25

Torres I, Muñoz J, Rojas D, Espinosa EE (2022) Selective harmonic elimination technique for a 27-level asymmetric multilevel converter. Energies 15(10):1–17

Raj MD, Thiyagarajan V, Selvan NBM, Vanaja DS (2022) Amelioration of power quality in a solar PV fed grid-connected system using optimization-based selective harmonic elimination. Electr Eng 104:2775

Deng E, Borucki L, Lutz J (2021) Correction of delay-time-induced maximum junction temperature offset during electrothermal characterization of IGBT devices. IEEE Trans Power Electron 36(3):2564–2573

Franquelo L, Rodriguez J, Leon J, Kouro S, Portillo R, Prats M (2008) The age of multilevel converters arrives. IEEE Ind Electron Mag 2(2):28–39

Gupta KK, Jain S (2013) Multilevel inverter topology based on series connected switched sources. IET Power Electron 6(1):164–174

Hoon Y, Radzi MAM, Hassan MK, Mailah NF (2018) Operation of three-level inverter-based shunt active power filter under nonideal grid voltage conditions with dual fundamental component extraction. IEEE Trans Power Electron 33(9):7558–7570

Hu H, Shi Q, He Z, He J, Gao S (2015) Potential harmonic resonance impacts of PV inverter filters on distribution systems. IEEE Trans Sustain Energy 6(1):151–161

Jana J, Saha H, Das Bhattacharya K (2017) A review of inverter topologies for single-phase grid-connected photovoltaic systems. Renew Sustain Energy Rev 72:1256–1270

Nabae A, Takahashi I, Akagi H (1981) A new neutral point clamped PWM inverter. IEEE Trans Ind Electron 7(2):518–523

Najafi E, Yatim AHM (2012) Design and implementation of a new multilevel inverter topology. IEEE Trans Ind Electron 59(11):4148–4154

Selvaraj J, Rahim NA (2009) Multilevel inverter for grid-connected PV system employing digital PI controller. IEEE Trans Industr Electron 56(1):149–158

Jagabar Sathik MA, Abdel Aleem SHE, Kannan R, Zobaa AF (2017) A new switched DC-link capacitor-based multi-level converter (SDC2MLC). Electr Power Compon Syst 45(9):1001–1015

Shunmugham Vanaja D, Stonier AA (2021) Grid integration of modular multilevel inverter with improved performance parameters. Int Trans Electr Energy Syst 31(1):e12667

Shunmugham Vanaja D, Albert JR, Stonier AA (2021) An experimental investigation on solar PV fed modular STATCOM in WECS using intelligent controller. Int Trans Electr Energy Syst 31(5):e12845

Wu F, Sun B, Duan J, Zhao K (2015) Online variable topology-type photovoltaic grid-connected inverter. IEEE Trans Ind Electron 62(8):4814–4822

“IEEE Standard for Interconnecting Distributed Resources with Electric Power Systems - Amendment 1,”IEEE Std 1547a-2014 (Amendment to IEEE Std 1547–2003) , vol., no., pp.1–16, May 21 2014.

E. Troester, “New German Grid codes for connecting PV systems to the medium voltage power grid,” 2nd International Workshop on Concentrating Phtovoltaic Power Plants : Optical Design, Production, Grid connection

Bihari SP, Sadhu PK (2020) Design analysis of high level inverter with EANFIS controller for grid connected PV system. Analog Integr Circ Sig Process 103(3):411–424

Vivek P, Vignesh V, Vigneshwaran T (2016). A novel approach on power quality improvement by multi-carrier multilevel inverter topology. In: 2016 3rd International Conference on Electrical Energy Systems, ICEES 2016, 13–17.

Vivek P, Ayshwarya R, Amali SJ, Sree ASN (2016). A novel approach on MPPT algorithm for solar panel using buck boost converter. In: 2016 International Conference on Energy Efficient Technologies for Sustainability, ICEETS 2016, 396–399.

Kannan C, Kishore CK (2014) A comparision of three phase 27 level inverter scheme under no load and multiple load conditions. Bull Electr Eng Inform 3(4):245–250. https://doi.org/10.11591/eei.v3i4.302

Roposed IIP, Opology BAT (2021). Novel switched-capacitor-based multilevel inverter topology for renewable energy. 5–9.

Manoharan P, Subramaniam U, Babu TS, Padmanaban S, Holm-Nielsen JB, Mitolo M, Ravichandran S (2021) Improved perturb and observation maximum power point tracking technique for solar photovoltaic power generation systems. IEEE Syst J 15(2):3024–3035. https://doi.org/10.1109/JSYST.2020.3003255

Marín-Reyes M, Aguayo-Alquicira J, De León-Aldaco SE (2020) Calculation of optimal switching angles for a multilevel inverter using NR, PSO and GA- a Comparison. Eur J Electr Eng 22(45):349–355. https://doi.org/10.18280/ejee.224-506

Funding

No government, private, or non-profit organization provided direct funding for this research.

Author information

Authors and Affiliations

Contributions

Each author participated actively in conducting analyses, drafting sections of the manuscript, editing and approving the final, submitted version. None of the authors has a financial or other conflict of interest.

Corresponding author

Ethics declarations

Conflict of interest

The authors declared no potential conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Vivek, P., Muthu Selvan, N.B. Experimental investigation on a Solar Photovoltaic system using reduced multilevel connections for power quality improvement. Electr Eng 105, 2889–2908 (2023). https://doi.org/10.1007/s00202-023-01829-z

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00202-023-01829-z