Abstract

In this paper, novel symmetric and hybrid topologies have been proposed for single phase multilevel inverter structures based on a new basic unit. The proposed topologies can be employed in solar energy systems. The main focus of this paper is to reduce the overall cost as well as to increase the efficiency of the multilevel inverters. To generate greater number of voltage levels, the basic units have been cascaded with each other to make extended topology. Different comparisons such as the number of power switches and percentage of THD against the number of voltage levels have been drawn to illustrate the advantages of the proposed topologies. To validate the performance of the proposed topologies, a 20 kW PV arrays based on fifteen-level hybrid inverter has been simulated through MATLAB/Simulink software.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Multilevel DC–AC power conversion systems were first introduced in 1975 by Baker [1]. Multilevel inverters have several advantages over two-level inverters: the former exhibit high efficiency, high power quality, low voltage distortion, less common mode noise generation, less dv/dt lower harmonic components, better electromagnetic compatibility and the ability to operate under low switching frequency [2,3,4,5,6,7,8]. Multilevel inverters have been widely used in various industrial applications as PV systems [9, 10], flexible AC transmission line systems [11,12,13] and electrical drives [14,15,16]. The primary purpose of designing a multilevel inverter is to generate a large number of desired output voltage levels using fewer power electronic components. There are mainly three conventional multilevel inverters: The CHB-MLI [1], the NPC multilevel inverter [17] and the FC multilevel inverter [2, 18, 19]. Although the introduced conventional multilevel inverters are able to provide large number of voltage levels with best quality, each of them exhibit certain drawbacks, which restrict their applications. The main drawbacks of these topologies are as follows:

-

a.

CHB-MLI: it requires a large number of power switches and gate drivers as well as isolated DC voltage sources.

-

b.

NPC inverter: it uses a large number of clamping diodes and voltage unbalancing in DC-link capacitors in high voltage levels.

-

c.

FC multilevel inverter: complex control mechanism for balancing the floating capacitors; they also use large number of flying capacitors.

In this paper, new symmetric and hybrid multilevel inverter configurations have been introduced with a new basic unit topology. Use of fewer IGBTs, diodes and gate driver circuits are the main advantages of the proposed topology in comparison with other topologies. The proposed multilevel inverter topology has been extended for application in PV systems. Moreover, the simulation tests have been done for a 20 kW PV system based on proposed fifteen-level inverter to demonstrate the validity of the proposed topology.

Section 2 explains the proposed basic and hybrid structures. Detailed comparisons between topologies are discussed in Sect. 3. Section 4 illustrates the simulation results.

2 Proposed Topologies

2.1 First Proposed Topology

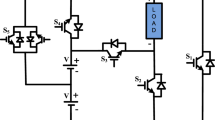

Figure 1 illustrates the proposed multilevel inverter topology with a new basic unit. The proposed structure consists of three stages. The first stage includes a PV panel and a qZSDCc. The qZSDCc is employed to increase the output voltage and maximum power tracking of the PV panel [20, 21]. The second stage is the structure of the proposed basic unit. The third stage includes an H-bridge inverter which is used to produce positive and negative voltage levels. The proposed basic unit inverter consists of five power switches and three DC-link capacitors to generate different voltage levels.

To analyze the proposed configuration, in the first stage, the output voltage of qZSDCc is increased to Vb according to the following equation [20, 21]:

where D is the duty cycle of the converter. The increased voltage Vbis then divided into three equal parts as \(V_{c} = \frac{{V_{b} }}{3}\) which then is used to generate different voltage levels in the proposed inverter.

In the second and third stage, to generate different voltage levels, different combinations of power switches states exist. Figure 2d–g indicates one of these combinations. In these figures, the pale gray paths indicate the current flow to generate seven different voltage levels. The output voltage levels of multilevel inverter are 0, − VC, + VC, + 2VC, − 2VC, + 3VC and − 3VC. For example, to generate + VC, one of the switching combinations is turning on the power switches S2,1, S3,1, S4,1, and T2. In this mode, when the switches turn on, the antiparallel diodes of power switches S1,1 and S5,1 get reverse biased. In this mode, the current flows through Vc, S2,1, S3,1, S4,1, load, and T2 and the voltage of load becomes Vo = Vc. It is important to note that to generate other voltage levels, the same analysis exists.

One of the most important targets in multilevel inverter topologies is to design a structure that decreases the overall cost and volume of the converter. The overall cost and volume of the converter have a near relevance to the number of power electronic elements such as power switches and gate diver circuits. To generate more number of voltage levels, the proposed basic unit can be extended by cascading the basic units. Figure 3 shows the developed proposed topology. In the proposed developed topology, if n indicates the number of basic units, then the number of voltage levels is determined by the following equation:

Moreover, considering the developed topology in Fig. 3, the number of power IGBTs is calculated by the following equation:

By substituting n from (2) in (3), the number of power IGBTs is calculated as:

2.2 Second Proposed Topology

Hybrid topology can be employed to generate greater number of voltage levels with fewer power electronic elements. In order to achieve hybrid topology, a three-level inverter is cascaded with the proposed developed topology, which increases the number of voltage levels. Figure 4 shows the proposed hybrid multilevel inverter.

In the proposed hybrid structure, we choose the magnitude of \(E\) equal with \(\frac{{V_{C} }}{2}\). Therefore, we can calculate the number of voltage levels as in the following equation:

According to the previous subsection 2.1, the number of power IGBTs is also calculated by:

By combining (5) and (6), the number of power IGBTs versus the number of voltage levels is determined as follows:

3 Comparisons

To illustrate the advantages of the proposed topology, we compared it with the other traditional topologies. Figure 5 illustrates the number of power IGBTs against the number of voltage levels. As can be seen, the first and second proposed topologies use fewer power IGBTs as compared to NPC, FC and CHB inverters.

One of the other important factors in multilevel inverter topologies is the percentage of THD against the number of used power switches. Figure 6 shows the percentage of THD against the used power IGBTs. It is clear that the first and second proposed topologies have fewer power switches in comparison to conventional topologies in the same THD. It is important to note that the low THD with fewer power electronic components reduces the total cost of the converter.

4 Simulation Results

To verify the operation of the proposed multilevel inverter, a 20 kW PV system based on the proposed hybrid fifteen-level inverter has been simulated through MATLAB/Simulink software. The fifteen-level inverter includes 19 power IGBTs and 7 DC-link capacitors. The parameters of the simulated system are listed in Table 1. In this simulation, a prototype of KC200GT PV panel with 10 identical modules connected in parallel and 10 in series has been selected and its parameters are listed in [21, 22]. Also, the insolation and environment temperature have been chosen as 1000 w/M2 and 25 °C, respectively.

Figure 7 shows the output voltage, output current and output power of the PV panels with modules connected in series and in parallel. As PV panels operate in standard environmental conditions and each PV panel has 200.143 W output power, 10 number of serried PV panels can produce 20 kW output power. Further, at maximum power point tracking, each PV panel has the maximum voltage and maximum current equal to 26.3 V and 7.61 A, respectively. Further, PV panels with 10 modules connected in series and 10 in parallel can produce 263 V output voltage and 76.1 A output current. According to the simulation consequences, these values have been shown in Fig. 7.

Figure 8 shows the simulation results for the output voltage of the qZSDCc. The increased amount of increased output voltage of the converter is almost 1200 V. This value divided into three and therefore, each input capacitor of the inverter becomes 400 V.

The active and reactive power of the load has been shown in Fig. 9. In this simulation, the converter operates in nominal conditions. Therefore, the amount of active and reactive power of the load which supplied by PV arrays and battery are 18 kW and 0.8 kVAr, respectively.

Figures 10 and 11 show the simulation results for the load voltage. As can be seen from Fig. 10, the rms value of the output voltage is almost 1100 V. Moreover, the FFT analysis shows that the THD of the load voltage is 8.93%.

Figures 12 and 13 illustrate the simulation results for the load current. According to these figures, the rms value of the output current is almost 20 A and the THD of the load is 1.48%. The load current is similar to the sinusoidal waveform because the load is inductive and acts as a low pass filter for the current.

5 Conclusion

In this article, novel basic and hybrid multilevel inverter structures have been presented, which can be used in photovoltaic applications. The proposed topology used fewer power electronic components in comparison to the other conventional topologies. Evidently, the proposed topology has clear advantages over conventional topologies. Finally, simulation results using MATLAB/Simulink software validated our conclusions.

Abbreviations

- kW:

-

Kilowatt

- kVAr:

-

Kilovar

- PV:

-

Photovoltaic

- CHB-MLI:

-

Cascade H-bridge inverter

- IGBT:

-

Insulated gate bipolar transistor

- NPC:

-

Neutral point clamped

- FC:

-

Flying capacitor

- CHB:

-

Cascaded H-bridge

- qZSDCc:

-

Quasi Z-source DC–DC converter

- THD:

-

Total harmonic distortion

- Rms:

-

Root mean square

- FFT:

-

Fast Fourier transform

References

“Electric power converter” ed: Google Patents (1975)

J. Rodriguez, J.-S. Lai, F.Z. Peng, Multilevel inverters: a survey of topologies, controls, and applications. IEEE Trans. Ind. Electron. 49(4), 724–738 (2002)

K. Corzine, Y. Familiant, A new cascaded multilevel H-bridge drive. IEEE Trans. Power Electron. 17(1), 125–131 (2002)

Y. Zhang, Z. Zhao, J. Zhu, A hybrid PWM applied to high-power three-level inverter-fed induction-motor drives. IEEE Trans. Ind. Electron. 58(8), 3409–3420 (2011)

G. Mondal, K. Sivakumar, R. Ramchand, K. Gopakumar, E. Levi, A dual seven-level inverter supply for an open-end winding induction motor drive. IEEE Trans. Ind. Electron. 56(5), 1665–1673 (2009)

J.-H. Kim, S.-K. Sul, P.N. Enjeti, A carrier-based PWM method with optimal switching sequence for a multilevel four-leg voltage-source inverter. IEEE Trans. Ind. Appl. 44(4), 1239–1248 (2008)

M.R. Banaei, E. Salary, Single-source cascaded transformers multilevel inverter with reduced number of switches. IET Power Electron. 5(9), 1748–1753 (2012)

Z. Pan, F.Z. Peng, Harmonics optimization of the voltage balancing control for multilevel converter/inverter systems. In Industry Applications Conference, 2004. 39th IAS Annual Meeting. Conference Record of the 2004 IEEE, 2004, vol. 4, pp. 2194–2201: IEEE

I. Abdalla, J. Corda, L. Zhang, Multilevel DC-link inverter and control algorithm to overcome the PV partial shading. IEEE Trans. Power Electron. 28(1), 14–18 (2013)

G. Buticchi, D. Barater, E. Lorenzani, C. Concari, G. Franceschini, A nine-level grid-connected converter topology for single-phase transformerless PV systems. IEEE Trans. Ind. Electron. 61(8), 3951–3960 (2014)

Y. Liu, F. Luo, Trinary hybrid multilevel inverter used in STATCOM with unbalanced voltages. In Electric Power Applications, IEE Proceedings-, 2005, vol. 152, no. 5, pp. 1203–1222: IET

M. Saradarzadeh, S. Farhangi, J.-L. Schanen, P.-O. Jeannin, D. Frey, Application of cascaded H-bridge distribution-static synchronous series compensator in electrical distribution system power flow control. IET Power Electron. 5(9), 1660–1675 (2012)

C. Hochgraf, R.H. Lasseter, A transformer-less static synchronous compensator employing a multi-level inverter. IEEE Trans. Power Deliv. 12(2), 881–887 (1997)

G. Waltrich, I. Barbi, Three-phase cascaded multilevel inverter using power cells with two inverter legs in series. IEEE Trans. Ind. Electron. 8(57), 2605–2612 (2010)

M.F.M. Elias, N.A. Rahim, H.W. Ping, M.N. Uddin, Asymmetrical cascaded multilevel inverter based on transistor-clamped h-bridge power cell. IEEE Trans. Ind. Appl. 50(6), 4281–4288 (2014)

X. Zha, L. Xiong, J. Gong, F. Liu, Cascaded multilevel converter for medium-voltage motor drive capable of regenerating with part of cells. IET Power Electron. 7(5), 1313–1320 (2014)

A. Nabae, I. Takahashi, H. Akagi, A new neutral-point-clamped PWM inverter. IEEE Trans. Ind. Appl. 5, 518–523 (1981)

X. Yuan, I. Barbi, Fundamentals of a new diode clamping multilevel inverter. IEEE Trans. Power Electron. 15(4), 711–718 (2000)

S. Choi, M. Saeedifard, Capacitor voltage balancing of flying capacitor multilevel converters by space vector PWM. IEEE Trans. Power Deliv. 27(3), 1154–1161 (2012)

D. Sun, B. Ge, D. Bi, F.Z. Peng, Analysis and control of quasi-Z source inverter with battery for grid-connected PV system. Int. J. Electr. Power Energy Syst. 46, 234–240 (2013)

M.B. Kalashani, M. Farsadi, New Structure for Photovoltaic Systems with Maximum Power Point Tracking Ability. Int. J. Power Electron. Drive Syst. 4(4), 489 (2014)

M.G. Villalva, J.R. Gazoli, E. Ruppert Filho, Comprehensive approach to modeling and simulation of photovoltaic arrays. IEEE Trans. Power Electron. 24(5), 1198–1208 (2009)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Barzegar Kalashani, M., Nazarpour, D. New Symmetric and Hybrid Multilevel Inverter Topology Employed in Solar Energy Systems. Trans. Electr. Electron. Mater. 19, 304–310 (2018). https://doi.org/10.1007/s42341-018-0031-y

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s42341-018-0031-y