Abstract

An ultra-low power consumption two-stage mixed switching scheme for successive approximation register (SAR) analog-to-digital converter (ADC) is presented. Using two simple switches, the novel switching scheme divides the capacitor arrays into two sub-arrays: stage-one and stage-two arrays. The two sub-arrays convert high and low bits cycles, respectively. Once the high bits conversion cycles are completed, the corresponding sub-arrays are split off from the capacitor arrays. This decreases the number of capacitors used in the rest conversion procedure. Thus, the proposed method improves the energy efficiency of SAR ADC. Thanks to C–2C dummy capacitors and two-stage capacitor arrays, the novel architecture achieves 86% reduction in capacitor area than conventional SAR ADC. Furthermore, based on the charge sharing technique and monotonic switching method, the proposed switching scheme does not consume reset energy and achieves 99.8% less switching energy than the conventional switching method. In addition, the proposed scheme is less sensitive to capacitor mismatch because of its great performance in linearity.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Successive approximation register (SAR) analog-to-digital converter (ADC) is widely used in low-power areas such as sensor networks [1, 12] and biomedical devices [6, 19, 30] owing to its suitability for nanometer CMOS processes. SAR ADC mainly consists of DAC capacitor arrays, bootstrapped switches, a comparator, SAR logic units and voltage reference circuits. These are the dominant power-limiting factors [7, 20, 24, 33]. As DAC switching energy is one of the major consumption sources [2, 5, 15, 23, 34], numerous studies have been conducted to improve the power efficiency of DAC capacitor arrays.

Compared with conventional switching scheme for SAR ADC, the monotonic [10] and the VCM-based [31] schemes require a large number of capacitors, causing extra area consumption. Some schemes introduced in Refs. [14, 27, 29, 32] decrease the switching energy effectively, which save energy without taking the parasitic capacitance into consideration. The methods reported in Refs. [16, 18, 22, 26] reduce switching energy by 98.83%, 98.83%, 98.4% and 98.4%, respectively, which ignore the reset energy between two sampling periods. Recently, there have been some mixed switching schemes which combine several techniques to make the scheme more energy efficient, such as Wang [21] and Liang [9]. The method reported in Ref. [21] requires 26.54 CV 2REF switching energy by splitting the MSB capacitor and applying the one-side two-level switching scheme. Unfortunately, the method reported in Ref. [21] has no advantage in power consumption after taking the parasitic capacitance into consideration and requires more switches because of split capacitors. The scheme reported in Ref. [9] consumes 7.94 CV 2REF switching energy by combining two energy-saving methods. The two methods do not require power consumption in the second comparison cycle and decrease the negative switching energy. However, the scheme reported in Ref. [9] ignores the reset energy, making the scheme energy-inefficient.

To overcome the above disadvantages, an ultra-low power consumption two-stage mixed switching scheme is presented for SAR ADC. In the proposed SAR ADC, two-stage capacitor arrays are used. The two sub-arrays (stage-one and stage-two arrays) which convert high and low bits cycles separately are connected using two simple switches. Once the high bits conversion cycles are completed, the corresponding sub-arrays are split off from the capacitor arrays, reducing the number of capacitors used in the rest conversion procedure. Thanks to C–2C dummy capacitors and two-stage capacitor arrays, the novel architecture achieves 43% reduction in capacitor area over the methods reported in Refs. [9, 21]. The number of switches used in the proposed scheme is only 62.5% of that reported in Ref. [21]. Top-plate sampling is utilized in the generation of MSB to reduce energy in the first comparison. To further reduce the power, the switching scheme combines the charge sharing technique and monotonic switching method from the third comparison. The two-step method is also applied to avoid the reset energy in the proposed scheme, while the reset energy is 128 CV 2REF in [9]. Thus, the proposed switching scheme achieves 99.8% less switching energy compared with the conventional method. Even by considering parasitic capacitance, the switching energy of the proposed method is reduced by 86.8% compared with the method reported in Ref. [21].

The rest of this paper is organized as follows: the structure of proposed SAR ADC is described in Sect. 2. Section 3 illustrates the proposed switching scheme. The simulation and comparison of energy consumption based on the analysis of reset energy and parasitic capacitance are discussed in Sect. 4. Section 5 provides an explanation on non-ideal factors, including the analysis of parasitic capacitance and mismatch of capacitor. Section 6 analyzes the choice of factor M. Section 7 introduces the simulation results. Section 8 reports the conclusion of entire switching scheme.

2 Structure of Proposed SAR ADC

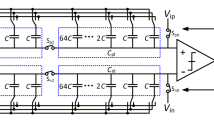

An ultra-low power consumption two-stage mixed switching scheme is proposed for SAR ADC benefitting from the charge sharing and C–2C dummy capacitor techniques in this letter. To suppress supply voltage noise and achieve good common-mode noise rejection, a fully differential architecture is used. The N-bit structure of the proposed SAR ADC consists of stage-one and stage-two arrays which determine high M bits and low N–M bits, respectively. Cb is the bridge capacitor which connects the two-stage capacitor arrays. The integral structure of the proposed switching scheme for 10-bit SAR ADC is shown in Fig. 1 with M = 6 (C is the unit capacitance).

The proposed SAR ADC consists of DAC capacitor arrays, bootstrapped switches S1 and S2, a comparator and SAR logic units. Switches S3 and S4 connect stage-one arrays and stage-two arrays. Through switches S3 and S4, the stage-one arrays are split off from the capacitor arrays after high 6 bits conversion cycles are completed, which reduces the energy consumed by DAC capacitor arrays in the following conversion cycles. The dummy capacitors of the stage-two arrays are replaced by C–2C capacitors to add one-bit accuracy. For the binary matching of the whole voltage, the stage-two arrays need a redundant capacitor Cr. The value of redundant capacitor is (2N−3–2N−M−1) C. In a 10-bit SAR ADC, the redundant capacitor is required to be 120C when M = 6. For a 10-bit SAR ADC, the proposed structure only needs 292 unit capacitors.

3 The Analysis of Switching Scheme

3.1 The Charge Sharing Technique

An equivalent model of DAC capacitor arrays is shown in Fig. 2 to illustrate the principle of the charge sharing technique. The differential DAC capacitor arrays consist of two parts DACP and DACN as shown in Fig. 2. Before charge sharing, the initial voltages of top plate of DACP and DACN are VP and VN, respectively. The voltages of bottom plate of MSB capacitor are Vn and Vn′. After charge sharing, the voltages of bottom plate of MSB capacitor are set to the same voltage Va. As a result, the voltage of top plate of DACP and DACN is changed to VP′ and VN′, respectively. During the procedure, the voltages of bottom plate of the rest capacitors remain unchanged. The charge sharing technique follows the principle of charge conservation.

Charge conservation of top plate on DACP capacitor array:

Charge conservation of top plate on DACN capacitor array:

Charge conservation of bottom plate of MSB capacitors:

Equations (1)–(3) explain the principle of charge sharing technique. After charge sharing, the voltage of bottom plate of MSB capacitor can be expressed as follows:

For example, a 6-bit proposed SAR ADC is explained in detail in Fig. 3. Figure 3 shows the second bit cycle of the proposed scheme when MSB = 1 and second MSB = 0. The initial voltages of Vn and Vn′ are VCM (VCM = 1/2VREF) and VREF, respectively. After charge sharing, the voltage Va of bottom plate is changed to 3/4VREF. As shown in Fig. 3, the charge sharing technique consumes less energy than the monotonic switching mode, thus significantly reducing overall power consumption.

3.2 Proposed Switching Scheme

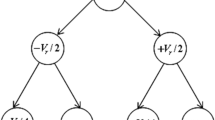

The flowchart of the proposed switching scheme is shown in Fig. 4. VP and VN are the voltages of top plates of differential capacitor arrays. SP and SN represent the switches between the bottom plates of capacitors and reference voltages. A 6-bit differential SAR ADC with M = 4 is used to illustrate the proposed scheme shown in Fig. 5. Because the switching scheme is symmetrical, for simplicity, Fig. 5 shows the switching scheme when MSB = 1. At the sampling phase, switches S1, S2, S3 and S4 close. The differential input signals are sampled to the top plates of both capacitor arrays at the same time, and the bottom plates of all the capacitors are connected with VCM (VCM = 1/2VREF). After the sampling phase, bootstrapped switches S1 and S2 open and the DAC arrays start working. At the conversion phase, the MSB is directly determined without any switching energy because of the top-plate sampling. After the first comparison, the bottom plates of capacitor array which samples the lower input voltage are connected to VREF and the other capacitor array remains unchanged. After the switching activity, the voltage level of capacitors on the lower voltage side is increased by 1/2VREF. Then, the comparator begins the second comparison and the second MSB is achieved. To further reduce the power, the combined monotonic and charge sharing switching method obtained from the third comparison is utilized. In this switching procedure, as soon as the potential of capacitor array which samples the lower input voltage is higher, the positive array and negative array capacitors are merged by charge sharing. In other cases, the DAC capacitor arrays perform by using the monotonic switching method. The ADC finishes the conversion of stage-one arrays until the fourth comparison is done. Before the fifth comparison, switches S3 and S4 are turned off, and the stage-one arrays are split off from the DAC capacitor arrays. Hence, the switching energy of the stage-one arrays in the remaining comparisons is reduced to improve the performance of SAR ADC. Then, stage-two arrays are operated to generate the rest bits. Stage-two arrays operate similarly as stage-one arrays by using the switching scheme shown in Fig. 5. Besides, the least significant bit (LSB) in stage-two is performed by reusing the unit capacitor.

The common-mode voltage variation of comparator inputs leads to input-dependent dynamic offset that deteriorates the performance of ADC. Reducing the output common-mode variation of capacitor array is important for decreasing the input-dependent offset of comparator. The waveform of the 6-bit SAR ADC is illustrated in Fig. 6. As shown in Fig. 6, the common-mode voltage variation of the proposed method is 1/4VREF. Therefore, the proposed method can ease the effect of common-mode voltage variation on the performance of comparator. A comparison of common-mode voltage variation between the proposed scheme and existing schemes is shown in Table 2.

The generation of MSB is independent of VCM because of top-plate sampling. Only one-side capacitor array switches when the second bit is generated. This makes the SAR ADC operation sensitive to the accuracy of VCM from the second bit. As a result, the accuracy of VCM should be ensured in the proposed method. A comparison of sensitivity to the accuracy of VCM between the proposed scheme and existing schemes is shown in Table 2.

3.3 Bridge Capacitor

The proposed DAC capacitor arrays are divided into two sub-arrays through the bridge capacitor Cb. To make the total weight of stage-two array equal to the weight of the lowest bit in the whole array, a bridge capacitor that is non-integer times relative to the unit capacitor is inserted. The value of bridge capacitor Cb should be calculated using the following equations:

Cu is the unit capacitor, and Cstage-two is the value of the capacitance in the stage-two array. Besides, in the proposed structure, the accuracy of capacitance value of Cb has no influence on the conversion of the low bits cycle. A 6-bit SAR ADC is shown in Fig. 7 to illustrate the effect of bridge capacitor on low bits cycle. As shown in Fig. 7, V1 and V2 are the initial voltages of nodes 1 and 2, whereas V1′ and V2′ are the voltages after the conversion. Nodes 1 and 2 follow the principle of charge conservation.

Charge conservation of node 1:

Charge conservation of node 2:

ΔV1 is the voltage variation of top plates of stage-two capacitor array in the low bits cycle, whereas ΔV2 is the voltage variation of input port of comparator. From above analysis, it can be concluded that ΔV2 follows ΔV1, which is not affected by Cb. Hence, the size of Cb does not affect the function of SAR ADC during the low bits cycle.

3.4 DAC Control Logic Analysis

A 6-bit SAR ADC introduced above is used to analyze the DAC control logic. Ni and Pi are the control signals of the ith bit (i = 1–6). DAC control logic of the proposed circuit is shown in Fig. 8. The control logics of the ith (i = 1–5) capacitor and the redundant capacitor are different. These logics have acceptable complexity. As the process technology improves, the total area and energy consumption in SAR logic are small enough compared to the switching capacitor array. A comparison of logic complexity between the proposed scheme and existing schemes is shown in Table 2.

4 Switching Energy

4.1 Switching Energy Analysis and Comparison

The behavior simulations of a differential 10-bit SAR ADC based on the switching schemes mentioned in Refs. [10, 18, 29, 31, 32] and the proposed switching scheme with M = 6 were performed in MATLAB. Figure 9 shows a comparison of switching energy for several switching schemes. The average switching energy for the proposed scheme is 2.9 CV 2REF and achieves 99.8% energy saving. Moreover, the proposed switching scheme achieves an area reduction of 86% with respect to conventional switching scheme.

4.2 Reset Energy Analysis and Comparison

The DAC capacitor arrays need to preload the corresponding capacitor sequences before a conversion cycle. The reset energy is needed in the procedure. A complete setting process for the DAC capacitor arrays consists of the switching and reset of capacitor arrays. However, all the schemes mentioned in [16, 18, 22, 26] ignored the reset energy between two sampling periods. Thus, the reset energy must be considered for an overall energy evaluation [17, 25]. According to the two-step reset method in [13], the reset process of the proposed switching scheme is shown in Fig. 10. Figure 10 shows an equivalent model of the proposed DAC arrays.

We suppose the final state as [V1, V2,…Vn]. When the final state is converted to [Gnd…Gnd…Gnd], the reset energy Ereset(step1) can be obtained as follows:

When all the capacitor states are set from [Gnd…Gnd…Gnd] to [VCM…VCM…VCM], the reset energy Ereset(step2) can be obtained as follows:

By substituting (12) into (11):

Through the above equations, the proposed method consumes zero reset energy thanks to the two-step reset method. It should be noted that the reset power is zero and independent of the final state because the initial state of the capacitor array is the same. In other words, the voltages connected to the bottom plates of all the capacitors are identical.

4.3 Effect of Parasitic Capacitance on Switching Energy

Because parasitic capacitance exists between the capacitor plates and substrate in reality, the effect of these parasitic capacitors should be considered for analyzing the switching energy consumption of SAR ADCs. Figure 11 shows a simple model for analyzing the effect of parasitic capacitors. As shown in Fig. 11, Cpt represents the equivalent parasitic capacitance of two stages between top plates and substrate. Cpcomp represents the parasitic capacitance between the input of comparator and substrate. The parasitic capacitance of a unit capacitor between bottom plates and substrate is represented as Cpb. Clearly, the parasitic capacitance should also be charged during the conversion cycle, thus increasing the power consumption of switching method.

After considering the parasitic capacitance, the behavior simulations of a differential 10-bit SAR ADC were performed in MATLAB. The parasitic capacitance is assumed to be Cpt + Cpcomp = 10%Ct and Cpb = 15%C. Ct is the total capacitance, and C is the unit capacitor in the capacitor array. The average switching energy of this proposed scheme is 8.3 CV 2REF , achieving energy saving by 99.5% compared with the conventional switching scheme. As discussed above, the proposed switching scheme is still energy efficient after taking the parasitic capacitance into consideration. In other words, the proposed method has low sensitivity to parasitic capacitance. A comparison of sensitivity to parasitic capacitance between the proposed scheme and existing schemes is shown in Table 1.

Tables 1 and 2 summarize the main features of the proposed switching scheme and the switching schemes mentioned in Refs. [3, 4, 8,9,10, 14, 16, 18, 21, 22, 26,27,28,29, 31, 32].

5 Analysis of Non-ideal Factors

5.1 Analysis of Effect of Parasitic Capacitance on Gain Error

In the proposed switching scheme, stage-one array connects stage-two array through the bridge capacitor Cb. In the high bits cycle, the capacitor array is equivalent to the full binary structure of capacitor array structure. In the low bits cycle, the bridge capacitor couples the voltage at node A to the input of comparator. Figures 12 and 13 illustrate the parasitic capacitance [11] of positive input port of the comparator in the high bits cycle and the low bits cycle, respectively. Cp1 and Cp4 are the parasitic capacitance on the top plates of stage-one array and stage-two array, respectively. Cp2 and Cp3 are equivalent to the parasitic capacitance on the top plate and bottom plate of the bridge capacitor, respectively. Cp5 represents the parasitic capacitance on the top plate of the C–2C capacitor.

For example, in high bits cycle, setting C1 from VCM to Gnd, the voltage change at the input port of the comparator can be obtained as follows:

Therefore, the gain error in high bits is

In low bits cycle, when C3 is set from VCM to Gnd, the voltage change at node A should be:

The voltage change at the input port of the comparator should be:

Therefore, the gain error in low bits is

If the value of parasitic capacitance on top plates is linear to the total value of DAC arrays, defaulting the ratio as \( \eta \), the value of parasitic capacitance can be defined as follows:

From the above analysis, it can be found that the bridge capacitor slightly affects the gain error of parasitic capacitance. Besides, the high bits comparison and low bits comparison have different gain errors.

5.2 Analysis of Effect of Capacitor Mismatch on Linearity

Due to process variation, the practical capacitance of each unit capacitor deviates from the nominal value. Capacitor mismatch is very important, and it determines the linearity of the SAR ADC [3, 8]. Some existing methods pursue the reduction of power dissipation but neglect the decrease in linearity, which require large unit capacitor and consume more energy. After taking the capacitor mismatch into account, simulation building with the unit capacitor obeys a Gaussian distribution, modeled with a nominal value of Cu and a standard deviation of σu.

For a given digital input, the analog output of N-bit capacitive DAC for the proposed switching scheme can be expressed as follows:

where d(p,n),i is equal to 0, 1/2 or 1 representing the DAC connecting to Gnd, VCM, VREF for bit i, respectively. M is the bits that the stage-one determines.

INL can be expressed as:

DNL can be expressed as:

5.3 Linearity Simulation

A 500-runs Monte–Carlo simulation of a 10-bit SAR ADC was performed in MATLAB for the effect of capacitor mismatch on linearity, with the mismatch of unit capacitor satisfying 3σu = 0.01C [4, 28]. Figures 14 and 15 show the simulation results of DNL and INL for the conventional switching scheme and the proposed switching scheme. The root-mean-square (RMS) values of maximum DNL and INL for the proposed switching scheme are 0.269LSB and 0.381LSB, respectively. The simulation results indicate that the proposed switching scheme has good performance in linearity.

6 Choose of Factor M

For a 10-bit SAR ADC, the value of M can be different. The switching energy and area reduction were simulated in MATLAB at different values of M for proposed 10-bit SAR ADC, and the result is shown in Fig. 16. The effects of different M on the linearity, switching energy and number of capacitors are shown in Table 3. Table 3 indicates that with the increase in M value, the number of capacitors increases, reducing the mismatch of capacitor arrays and improving the linearity of the proposed scheme. When M is 6, the number of capacitors, switching energy and linearity achieve a balance.

7 Simulation Results

A 40 MS/s 10-bit 1 V SAR ADC used in the proposed switching scheme was implemented in MATLAB. The simulation was implemented after taking VCM variations and capacitance mismatch into account. The deviation in VCM value and mismatch of capacitor are set as 10 mV and σ = 1%, respectively. A 16384-point fast Fourier transform (FFT) of the 40 MS/s SAR ADC when the input frequency is 12.47 MHz is shown in Fig. 17. The signal-to-noise and distortion ratio (SNDR) and the spurious-free dynamic range (SFDR) can reach 61.40 and 82.52 dB, respectively. Figure 18 exhibits the dynamic performance as the input frequency is swept at 40 MS/s. The ADC achieved a peak SNDR of 61.62 dB.

8 Conclusion

This paper proposes an ultra-low power consumption two-stage mixed switching scheme which applies to SAR ADC. The proposed switching scheme adopts two-stage capacitor arrays with a novel mixed method. Thanks to C–2C dummy capacitors and two-stage capacitor arrays, the novel architecture achieves 86% reduction in capacitor area over the conventional SAR ADC. Furthermore, based on the charge sharing technique and monotonic switching method, the proposed switching scheme does not consume reset energy and achieves 99.8% less switching energy compared with the conventional switching method. In addition, the proposed scheme is less sensitive to capacitor mismatch because of its great performance in linearity. Therefore, the proposed switching scheme is suitable for the ultra-low power consumption SAR ADC, which is more energy efficient and area efficient among the reported switching schemes.

References

S.-U. Baek, K.-Y. Lee, M. Lee, Energy-efficient switching scheme for SAR ADC using zero-energy dual capacitor switching. Analog Integr. Circuits Signal Process. 94, 317–322 (2018)

F. Chen, A.P. Chandrakasan, V. Stojanovic, A low-power area-efficient switching scheme for charge-sharing DACs in SAR ADCs, in IEEE Custom Integrated Circuits Conference (CICC) (2010), pp. 1–4

Z. Ding, W. Bai, Z. Zhu, Trade-off between energy and linearity switching scheme for SAR ADC. Analog Integr. Circuits Signal Process. 86, 121–125 (2016)

B. Ghanavati, E. Abiri, M.R. Salehi, A. Keyhani, A. Sanyal, LSB split capacitor SAR ADC with 99.2% switching energy reduction. Analog Integr. Circuits Signal Process. 93, 375–382 (2017)

A.R. Ghasemi, M. Saberi, R. Lotfi, A low-power capacitor switching scheme with low common-mode voltage variation for successive approximation ADC. Microelectron. J. 61, 15–20 (2017)

W. Guo, Z. Zhu, A 0.3 V 8-bit 8.9 fJ/con.-step SAR ADC with sub-DAC merged switching for bio-sensors. Microelectron. J. 68, 44–54 (2017)

Y.F. Hu, Z.C. Yi, Z.H. He, B. Li, Energy-efficient, area-efficient, high-accuracy and low-complexity switching scheme for SAR ADC. IEICE Electron. Express 14, 1–7 (2017)

H. Liang, R. Ding, S. Liu, Z. Zhu, Energy-efficient and area-efficient asymmetric capacitor switching scheme for SAR ADCs. J. Circuits Systems and Computers 27, 1850109 (2017)

Y.H. Liang, Z. Zhu, An energy-efficient switching scheme for low-power SAR ADC design. J. Circuits Syst. Comput. 27, 1850015 (2018)

C.C. Liu, S.J. Chang, G.Y. Huang, Y.Z. Lin, A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure. IEEE J. Solid-State Circuits 45, 731–740 (2010)

J. Liu, R. Ding, S. Liu, Z. Zhu, A highly energy-efficient, highly area-efficient capacitance multiplexing switching scheme for SAR ADC. Analog Integr. Circuits Signal. Process. 96, 207–215 (2018)

S.A. Mahmoud, H.A. Salem, H.M. Albalooshi, An 8-bit, 10KS/s, 1.87 µW successive approximation analog to digital converter in 0.25 µm CMOS technology for ECG detection systems. Circuits Syst. Signal Process. 34, 2419–2439 (2015)

D. Osipov, S. Paul, Two-step reset method for energy-efficient SAR ADC switching schemes. Electron. Lett. 52, 816–817 (2016)

A. Sanyal, N. Sun, SAR ADC architecture with 98% reduction in switching energy over conventional scheme. Electron. Lett. 49, 248–250 (2013)

S. Sarafi, A.K.B. Aain, J. Abbaszadeh, High-linear, energy-efficient and area-efficient switching algorithm for high-speed SAR ADCs. Microelectron. J. 45, 288–296 (2014)

X. Tong, M. Ghovanloo, Energy-efficient switching scheme in SAR ADC for biomedical electronics. Electron. Lett. 51, 676–678 (2015)

X. Tong, Y. Zhang, 98.8% switching energy reduction in SAR ADC for bioelectronics application. Electron. Lett. 51, 1052–1054 (2015)

X. Tong, Y. Chen, Low-power high-linearity switching procedure for charge-redistribution SAR ADC. Circuits Systems and Signal Processing 36, 3825–3834 (2017)

S. Ur Rehman, A.M. Kamboh, A CMOS micro-power and area efficient neural recording and stimulation front-end for biomedical applications. Circuits Syst. Signal Process. 34, 1725–1746 (2015)

H. Wang, C.Y. Liu, W.M. Xie, Q.D. Zhang, Tri-level capacitor-splitting switching scheme with high energy-efficiency for SAR ADCs. IEICE Electron. Express 13, 1–5 (2016)

H. Wang, W.M. Xie, Z.X. Chen, S.J. Cai, A capacitor-splitting switching scheme with low total power consumption for SAR ADCs. J. Circuits Syst. Comput. 28(04), 1920002 (2018)

A. Wu, J. Wu, Energy-efficient switching scheme for ultra-low voltage SAR ADC. Analog Integr. Circuits Signal Process. 90, 507–511 (2017)

Y. Wu, X. Cheng, X. Zeng, A 960 μW 10-bit 70-MS/s SAR ADC with an energy-efficient capacitor-switching scheme. Microelectron. J. 44, 1260–1267 (2013)

L.B. Xie, G.J. Wen, J.X. Liu, Y. Wang, Energy-efficient hybrid capacitor switching scheme for SAR ADC. Electron. Lett. 50, 22–23 (2014)

L. Xie, W. Nie, X. Yang, M. Zhou, A group reset method for energy-efficient SAR ADC switching schemes. Analog Integr. Circuits Signal Process. 96, 183–187 (2018)

L. Xie, J. Su, Y. Wang, J. Liu, G. Wen, Switching scheme with 98.4% switching energy reduction and high accuracy for SAR ADCs. Analog Integr. Circuits Signal Process. 90, 681–686 (2017)

B. Yazdani, A. Khorami, M. Sharifkhani, Low-power DAC with charge redistribution sampling method for SAR ADCs. Electron. Lett. 52, 187–188 (2016)

T. Yousefi, A. Dabbaghian, M. Yavari, An energy-efficient DAC switching method for SAR ADCs. IEEE Trans. Circuits Syst. II Exp. Briefs 1, 41–45 (2018)

C. Yuan, Y. Lam, Low-energy and area-efficient tri-level switching scheme for SAR ADC. Electron. Lett. 48, 482–483 (2012)

Y. Zhang, Y. Li, Z. Zhu, A charge-sharing switching scheme for SAR ADCs in biomedical applications. Microelectron. J. 75, 128–136 (2018)

Y. Zhu, C.H. Chan, U.F. Chio, S.W. Sin, U. Seng-Pan, R.P. Martins, F. Maloberti, A 10-bit 100-MS/s reference-free SAR ADC in 90 nm CMOS. IEEE J. Solid-State Circuits 45, 1111–1121 (2010)

Z. Zhu, Y. Xiao, X. Song, V CM-based monotonic capacitor switching scheme for SAR ADC. Electron. Lett. 49, 327–329 (2013)

H.Y. Zhuang, Z. Zhu, Y.T. Yang, A 19-nW 0.7-V CMOS voltage reference with no amplifiers and no clock circuits. IEEE Trans. Circuits Syst. II Exp. Briefs 11, 830–834 (2014)

H.Y. Zhuang, W.J. Guo, J.X. Liu, H. Tang, Z. Zhu, L. Chen, N. Sun, A second-order noise-shaping SAR ADC with passive integrator and tri-level voting.IEEE J. Solid-State Circuits 54, 1636–1647 (2019)

Acknowledgements

This work is supported by the National Natural Science Foundation of China (No. 61306033) and the Science and Technology on Low-Light-Level Night Vision Laboratory (No. 61424120503162412005).

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Chen, Y., Zhuang, Y. & Tang, H. A 99.8% Energy-Reduced Two-Stage Mixed Switching Scheme for SAR ADC Without Reset Energy. Circuits Syst Signal Process 38, 5426–5447 (2019). https://doi.org/10.1007/s00034-019-01151-9

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-019-01151-9