Abstract

Quantum-dot cellular automaton (QCA) has emerged as one of the best alternatives to CMOS technology in nanoscale. In spite of the potential advantages of QCA technology over CMOS, QCA circuits often suffer from various types of manufacturing defects and are therefore prone to fault. Hence, the design of fault-tolerant circuits in QCA technology is considered a necessity. The implementation of multiplexer circuits in QCA technology has been of great interest to researchers due to its widespread use in memory circuits and ALUs. In most of the multiplexer circuits presented in QCA, the problem of fault-tolerant is ignored. In this paper, a novel fault-tolerant three-input majority gate is initially proposed. The proposed structure has been investigated against all kinds of cell omission, extra cell deposition, and cell displacement defects. The simulation results are verified by QCA Designer 2.0.3, and it showed that it is 100, 84.98, and 100% tolerant to single-cell omission, double-cell omission, and extra cell deposition, respectively. In addition, the proposed structure shows that it is robust against cell displacement defects. Moreover, physical investigations are provided in order to confirm the function of the proposed fault-tolerant structure. Finally, using the proposed structure, a novel single-layer 2:1 multiplexer is presented. The results of comparisons indicate that the proposed designs are more reliable than the existing designs. Furthermore, QCAPro power estimator tool is employed to estimate the energy dissipation of the proposed structure.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Within a short time, it is expected that CMOS technology will reach the end of its way due to limitations such as physical scalability, short channel effects, and high cost of lithography as well as heating and cooling challenges [1,2,3]. Therefore, emerging technologies such as single-electron transistor (SET), resonant tuning diode (RTD), carbon nanotube field effect transistor (CNTFET), and QCA have been able to overcome these problems. Based on the International Technology Roadmap for Semiconductor (ITRS), which offers a summary of future technologies, QCA has been introduced as one of the effective strategies. This technology is one of the options for designing high-density logic circuits due to its unique features such as high speed, small size, and low power consumption. The simplest element in QCA technology is a square structure in nanoscale that includes four quantum dots and two electrons. The electrons are able to tunnel between quantum dots if potential barrier that discriminates quantum dots is low [3,4,5]. According to Coulomb repulsion, electrons located two opposite corners of the QCA cell [3,4,5].

Although extensive research has so far been carried out to design and simulate various digital circuits such as basic logic gates, adders [6,7,8,9,10,11,12,13], multipliers [14,15,16,17,18], dividers [16, 19,20,21], and memory circuits [22,23,24,25,26] in QCA technology, due to the novelty of this technology, there are still many serious barriers that have not been sufficiently studied. One of the major barriers is the lack of mature QCA technology in the commercial production of circuits, which suffer from a high rate of defects [27]. The available defects in the manufacturing process may occur in the chemical synthesis and the deposition phases [27]. Cell misplacement defects occur during the deposition phase, which is among the most common defects [27]. The cell misplacement defects include cell omission, deposition of extra cells, and cell displacement [27, 28]. Occurrence of such defects in QCA logic devices causes a dramatic reduction in efficiency [28]. Therefore, the design of fault-tolerant logic circuits in QCA technology is absolutely necessary, and that is why in the last decade, QCA researchers have focused on designing fault-tolerant circuits. Since the inverter and majority gates are two basic gates designed for QCA circuits, their durable configurations can lead to the design of robust logic circuits for QCA technology. So far, several fault-tolerant circuits have been proposed. Lent et al. [3] have provided the conventional three-input majority gate that is only 20% fault-tolerant for a single-cell omission defect. In 2007, Huang et al. introduced a new fault-tolerant three-input majority gate called the orthogonal tile, which has 13 cells and occupies 0.01 μm2. It has 66.7 and 36.1% fault-tolerant against single- and double-cell omission defects, respectively [29]. In 2014, Sen et al. [30] presented a fault-tolerant three-input majority gate that achieved 95.65 and 78% fault-tolerant against single- and double-cell omission defects. It also consists of 27 cells and occupies 0.02 μm2. In 2016, Sen et al. suggested another three-input majority gate that is 75 and 42% robust against single- and double-cell omission defects. It has 12 cells with an area of 0.01 μm2 [31]. In addition, in 2016, Sen et al. [32] provided a novel fault-tolerant three-input majority gate that is 97.44 and 82.86% fault-tolerant against the single- and double-cell omission defects. They used cellular rotation in their design. This structure has 43 cells, and its occupied area is equal to 0.04 μm2. In 2016, Kumar et al. suggested a fault-tolerant three-input majority gate, which used two clocks. This has 87.5 and 60% fault-tolerant against single- and double-cell omission defects [9]. It includes 20 cells that occupy 0.01 μm2. In 2016, Du et al. [33] introduced a fault-tolerant three-input majority gate that used 5 × 3 tiles and has 60 and 31% fault-tolerant against single- and double-cell omission defects. This structure has 20 cells with an area of 0.01 μm2. In 2018, Sun et al. [34] proposed new three-input majority gate with 25 cells which covers an area of 0.01 μm2. This structure is 80.95 and 39.8% fault-tolerant to single- and double-cell omission defects. In 2018, Wang et al. [35] introduced a new three-input majority gate with 36 cells, which occupies an area of 0.03 μm2. This structure is 93.8% and 66.7 fault-tolerant against single- and double-cell omission defects. In 2018, Farazkish [36] suggested another fault-tolerant three-input majority gate with 13 cells, which covers an area of 0.01 μm2. This structure is 66.6 and 22.2% fault-tolerant to single- and double-cell omission defects.

The major contribution of this research can be summarized as followed:

This paper proposes a novel fault-tolerant three-input majority gate with 27 cells, which covers an area of 0.02 μm2.

-

The proposed structure is 100, 84.98, and 100% fault-tolerant against single-cell omission, double-cell omission, and extra cell deposition defects.

-

A novel single-layer fault-tolerant 2:1 multiplexer using the proposed structure is introduced.

-

Physical investigations are used to confirm the proposed structure.

-

The simulations were performed using the QCADesigner 2.0.03 and QCAPro tools to measure performance and energy consumption.

The rest of the paper is organized as follows: In Sect. 2, an overview of QCA technology is given in terms of cells, basic gates, wire crossing, clocking, and characteristic defects of QCA. In Sect. 3, the proposed fault-tolerant majority gate is introduced. The proposed fault-tolerant QCA multiplexer is described in Sect. 4. The simulation results of the proposed circuits are provided in Sect. 5. Finally, the paper ends with conclusion section.

2 Preliminaries

2.1 QCA review

The emerging technology of QCA is suitable for designing circuits at the nanoscale [5]. The basic computing element in QCA technology is a quantum cell. Each quantum cell consists of four quantum dots, which are located in the four corners of a square. Each cell contains two electrons, which can tunnel among these dots. As it is seen in Fig. 1, regarding Coulomb’s repulsion force, two stable arrangements of P = + 1 and P = − 1 are formed, which encode 1 and 0 in binary logic, respectively [3, 5, 37].

Wires in QCA technology are created using a sequence of QCA cells, which are able to propagate inputted signal to output. Figure 2 shows 90° and 45° wires in QCA technology. As you can see, in the 90° wire, the inputted signal is transferred to the output without change, while in the 45° wire, the inputted signal or its complement can be generated at the output.

Three-input majority gate (MV3) and inverter gate (NOT) are considered as two building blocks of the QCA circuit [5]. The MV3 gate output with inputs A, B, and C is defined using Eq. (1):

Moreover, Fig. 3 shows the circuit and cellular representation of MV3 (A, B, C) gate.

It should be noted that by simply keeping one of the inputs of MV3 gate constant at ‘0’ or ‘1,’ we can obtain two-input AND or two-input OR gates, respectively.

Another basic gate is inverter gate. Circuit representation and two different layouts of QCA NOT gate are depicted in Fig. 4.

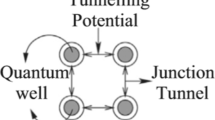

QCA circuits such as CMOS circuits require clock pulses in order to function correctly. The clock pulse in QCA technology follows two main goals: providing energy to circuit devices and controlling data propagation in the cells. Clock pulses facilitate the movement of electrons inside cells and thus allow the electrons to change their configuration in a predefined manner and change the barriers of tunneling between quantum dots [5]. Usually, a clocking design consists of four phases—switch, hold, release, and relaxation, as shown in Fig. 5.

The process of cell polarization starts at the switch phase (ascending edge) and continues until the cell is completely polarized. When the clock pulse reaches the high level (hold phase), the cell retains its polarization. A decrease in polarization of the cell occurs when the clock passes through the release phase (descending edge). Finally, at the relax phase, the cell is unpolarized [38].

2.2 Kink energy

The electrostatic energy between two electrons i and j is calculated using Eq. 2 as follows:

where Eij is kink energy, K is a constant value, qi and qj are electrical charges, and rij is the distance between two electrical charges of i and j. By substituting values of K = 9 × 109 and q = 1.6 × 10−38, kink energy between two electrons is obtained equal to \( E_{ij} = 23.04 \times 10^{ - 29} \left( {\text{J}} \right) \) [39,40,41]. The final electrostatic energy applied to qi electron is calculated by Eq. 3:

where N is the number of electrical charges.

2.3 Defects in QCA

Generally, the defects in QCA technology occur in the deposition process. These defects are basically divided into four categories as follows [42]:

-

1.

Cell omission This type of defect occurs due to omission of one cell (Fig. 6a).

-

2.

Cell displacement This type of defect occurs due to displacement of cells from their original position (Fig. 6b).

-

3.

Cell misalignment This type of defect occurs due to misalignment of cells (Fig. 6c).

-

4.

Extra cell deposition It occurs due to deposition of cells in the bed (Fig. 6d).

3 Proposed fault-tolerant majority gate

As mentioned above, the majority gate is applied as one of the most important building blocks of QCA circuits. Using common majority gate in the design of circuits reduces the fault-tolerant potential. As outlined in the introduction section, several fault-tolerant majority gates have been proposed so that their application in the design of circuits can increase the tolerability of the defects. In the following section, a novel fault-tolerant three-input majority gate has been presented and its function is investigated through some physical proofs and computer simulations.

The proposed gate consists of normal cells, not rotated cells. Cellular representation of the proposed gate is depicted in Fig. 7. As it can be seen, the cells of the sequential rows in the proposed design have 10 nm displacements with respect to each other.

As it can be seen in Fig. 7, the proposed fault-tolerant structure has 27 cells and is able to produce the output in one-clock phase.

3.1 Physical verification

In this section, we will show the correctness of the output of the proposed fault-tolerant structure with a single-cell omission defect through physical proofs. Since the proposed structure has 27 cells, we should test all the single-cell omission defects that may happen in cells to verify the correctness of this structure. Due to the large computations, only one possible defect had been verified and other single-cell omission defects can be proven similarly. For this analysis, it was necessary to first calculate the kink energies of other cells in the effective radius on the output cell for the single-cell omission defect using the equations in Sect. 2.2. As it can be seen in Fig. 8, the effective radius was supposed 77 nm. Furthermore, it is assumed that input vector is (A, B, C) = (1, 0, and 1) and single-cell omission defect occurs in the cell 14. Therefore, we have to determine the kink energy between electrons e1 to e20 for two states (a) and (b) with the x and y electrons of the output cell shown in Fig. 9. Since cells 1, 2, 3, 4, 5, 10, 11, 15, 16, 17, 22, and 23 are far from the output cell, their kink energy can be ignored.

The values of kink energy between electrons e1 and e20 with x and y electrons shown in Fig. 9, for two states of (a) and (b), are given in Tables 1 and 2, respectively.

Comparison of results revealed that the output cell electrons are positioned in Fig. 9a which is more stable and has lower kink energy. Thus, the output cell polarity is equal to ‘1’ and it had been obtained correctly.

3.2 Fault-tolerant analysis

In order to show the high reliability of the proposed structure, we analyze the function of the proposed structure under single-cell omission and double-cell omission, extra cell deposition, and cell displacement defects.

Table 3 presents the simulation results for the proposed structure under single-cell omission defect.

As it is shown in Table 3, the proposed majority gate has correct output (MV3 function) for all single-cell omission defects. Therefore, this structure is 100% tolerant under single-cell omission defects.

The simulation results of the proposed structure under double-cell omission defect are provided in Table 4.

As it can be seen in Table 4, there are a total of 253 states of double-cell omission defects in the proposed structure, and among them, 215 cases are MV3 function, 21 cases are wire function, 13 cases are NOT function, and finally, four cases are undefined functions. Therefore, this structure is 84.98% fault-tolerant under double-cell omission defects.

Table 5 provides comparisons of the fault-tolerant characteristics of the different majority gate under single- and double-cell omission defects. Furthermore, Fig. 10a–d shows the area, cell counts and fault-tolerant for the proposed structure.

An extra cell is located in the regions around the driver cells of the proposed structure to investigate the effects of defect arising out of additional cell deposition. The possible extra cell depositions in the proposed structure are A1 to A15 (Fig. 10). All possible additional cell depositions in the proposed structure are provided in Table 6.

According to Table 6, the proposed gate has MV3 function for all extra cell deposition defects. Therefore, this gate is 100% fault-tolerant under extra cell deposition defects.

At last, the proposed structure is analyzed under cell displacement and cell misalignment defects. The simulation results of the proposed structure under cell displacement and misalignment defects are shown in Table 7. It should be noted that the symbol ‘-‘ indicates that displacement or misalignment of the corresponding cell along that particular direction is not allowed. Note that a permissible displacement of 500 nm implies that the corresponding defect hardly has any effect on the functional behavior of the structure. It is shown by the symbol ‘∞.’

As it is shown in Table 7, the proposed design has proper resistance for all cell displacement and cell misalignment defects.

3.3 Energy dissipation

Energy dissipation of the proposed structure at three different levels 0.5EK, 1EK, and 1.5EK with temperature of 2.0 K has been calculated using the QCAPro tool [43]. The results are given in Table 8. Moreover, energy dissipation maps are shown in Fig. 11. It should be noted that high-power cells generate a lot of heat in which hot spots appear in darker colors.

4 Proposed fault-tolerant 2:1 multiplexer

One of the logic circuits is multiplexer that is used in a wide range of digital circuits such as RAM and ALU. Multiplexer is a circuit that is capable of selecting one of the inputs and transmits it to the output. So far, several approaches of designing multiplexes have been presented in QCA technology, which differs in cell counts and delays [24, 44,45,46,47,48]. In this section, a single-layer 2:1 multiplexer in QCA technology had been suggested first. Then, its fault-tolerant version was given by the proposed fault-tolerant majority gate.

The proposed 2:1 QCA multiplexer has two inputs, an address line, and an output. The inputs are labeled as A and B, and the output is shown by F. Here the address line named as S. When S is 0, input A is selected, and when S is 1, input B transmits at the output. The logic equation of the 2:1 multiplexer is as follows:

Layout of the proposed 2:1 QCA multiplexer is shown in Fig. 12. As it can be seen, this design includes 35 cells and produces correct output in four clock phases.

Furthermore, cellular view of the proposed fault-tolerant 2:1 multiplexer is shown in Fig. 13.

In addition, the fault-tolerant versions of the proposed 2:1 QCA multiplexer using fault-tolerant majority gates of [29, 33] are shown in Fig. 14.

5 Simulation results

QCA Designer software 2.0.3 has been used to simulate proposed designs. There are two simulation engines in the QCA Designer software called ‘Bistable Approximation’ and ‘Coherence Vector’ [38]. In this paper, the ‘Bistable Approximation Engine’ is used. All parameters and simulation conditions have default values of the software, as shown in Table 9.

Results of the proposed fault-tolerant 2:1 multiplexer for all combinations of S, A, and B inputs are shown in Fig. 15. Simulation results indicate that the proposed fault-tolerant multiplexer operates well. For instance, for inputs S = 1, A = 0 and B = 1, the correct output is obtained. As it can be seen in Fig. 15, the output is of very high quality.

Results of comparing the proposed fault-tolerant multiplexer with other designs from single- and double-cell omission defect viewpoints are shown in Table 10.

As it is shown in Table 10, the proposed fault-tolerant multiplexer has the ability for 89 and 62.59% tolerance under single- and double-cell omission defects, respectively. This indicates that the proposed multiplexer has a much higher resilience than other designs.

In addition, the temperature effect on the output polarization of the multiplexer circuits has been analyzed. Figure 16 shows the variation of polarization with respect to temperature in a range of 0–28 K.

As can be seen in Fig. 16, although the output of the multiplexer circuits in Fig. 14a, b, respectively, when temperature passes from 5 and 8 K, will be broken, the output of the proposed fault-tolerant multiplexer sustains full stability for a wide range of temperature. So, it can be concluded that the proposed fault-tolerant multiplexer is more robust against temperature variations than other designs.

6 Conclusion

In this paper, we first proposed a novel fault-tolerant three-input majority gate. The proposed structure was 100, 84.98, and 100% fault-tolerant under single-cell omission, double-cell omission, and extra cell deposition defects, respectively, as well as benefits a high output power. Physical proofs confirmed the simulation results. QCA Designer 2.0.3 software was used to simulate the proposed circuits. Using this structure, we proposed a novel fault-tolerant 2:1 multiplexer. The results of the comparisons showed that the proposed fault-tolerant multiplexer has higher degree of fault tolerance than other designs. Our future works include using the proposed fault-tolerant designs for other fault-tolerant structures such as ALU and RAM.

Change history

30 April 2019

The spelling of the city Dezful was incorrect in the author affiliation. The correct affiliation is given below.

30 April 2019

The spelling of the city Dezful was incorrect in the author affiliation. The correct affiliation is given below.

30 April 2019

The spelling of the city Dezful was incorrect in the author affiliation. The correct affiliation is given below.

References

Wilson M et al (2002) Nanotechnology: basic science and emerging technologies. CRC Press, Boca Raton

Toth G, Lent CS (1999) Quasiadiabatic switching for metal-island quantum-dot cellular automata. J Appl Phys 85(5):2977–2984

Lent CS et al (1993) Quantum cellular automata. Nanotechnology 4(1):49

Compano R, Molenkamp L, Paul D (2000) Roadmap for nanoelectronics. European Commission IST Programme, Future and Emerging Technologies

Lent CS, Tougaw PD (1997) A device architecture for computing with quantum dots. Proc IEEE 85(4):541–557

Seyedi S, Navimipour NJ (2018) Design and evaluation of a new structure for fault-tolerance full-adder based on quantum-dot cellular automata. Nano Commun Netw 16:1–9

Heikalabad SR, Asfestani MN, Hosseinzadeh M (2018) A full adder structure without cross-wiring in quantum-dot cellular automata with energy dissipation analysis. J Supercomput 74(5):1994–2005

Safavi A, Mosleh M (2016) Presenting a new efficient QCA full adder based on suggested MV32 gate. Int J Nanosci Nanotechnol 12(1):55–69

Kumar D, Mitra D (2016) Design of a practical fault-tolerant adder in QCA. Microelectron J 53:90–104

Bandani Sousan H-A, Mosleh M, Setayeshi S (2015) Designing and implementing a fast and robust full-adder in quantum-dot cellular automata (QCA) technology. J Adv Comput Res 6(1):27–45

Abedi D, Jaberipur G, Sangsefidi M (2015) Coplanar full adder in quantum-dot cellular automata via clock-zone-based crossover. IEEE Trans Nanotechnol 14(3):497–504

Navi K et al (2010) A new quantum-dot cellular automata full-adder. Microelectron J 41(12):820–826

Cho H, Swartzlander EE (2007) Adder designs and analyses for quantum-dot cellular automata. IEEE Trans Nanotechnol 6(3):374–383

Faraji H, Mosleh M (2018) A fast wallace-based parallel multiplier in quantum-dot cellular automata. Int J Nano Dimens 9(1):68–78

Pudi V, Sridharan K (2013) Efficient design of Baugh-Wooley multiplier in quantum-dot cellular automata. In: 13th IEEE Conference on Nanotechnology (IEEE-NANO), 2013. IEEE

Kim S-W (2011) Design of parallel multipliers and dividers in quantum-dot cellular automata

Cho H, Swartzlander EE Jr (2009) Adder and multiplier design in quantum-dot cellular automata. IEEE Trans Comput 58(6):721–727

Cho H (2006) Adder and multiplier design and analysis in quantum-dot cellular automata

Sayedsalehi S et al (2015) Restoring and non-restoring array divider designs in quantum-dot cellular automata. Inf Sci 311:86–101

Kong I, Kim S-W, Swartzlander EE (2014) Design of Goldschmidt dividers with quantum-dot cellular automata. IEEE Trans Comput 63(10):2620–2625

Kong I, Swartzlander EE, Kim S-W (2009) Design of a Goldschmidt iterative divider for quantum-dot cellular automata. In: IEEE/ACM International Symposium on Nanoscale Architectures, 2009. NANOARCH’09. IEEE

Chaharlang J, Mosleh M (2017) An overview on RAM memories in QCA technology. Majlesi J Electr Eng 11(2):9

Sadoghifar A, Heikalabad SR (2018) A content-addressable memory structure using quantum cells in nanotechnology with energy dissipation analysis. Phys B 537:202–206

Asfestani MN, Heikalabad SR (2017) A unique structure for the multiplexer in quantum-dot cellular automata to create a revolution in design of nanostructures. Phys B 512:91–99

Heikalabad SR, Navin AH, Hosseinzadeh M (2016) Content addressable memory cell in quantum-dot cellular automata. Microelectron Eng 163:140–150

Heikalabad SR et al (2015) Midpoint memory: a special memory structure for data-oriented models implementation. J Circuits Syst Comput 24(05):1550063

Tahoori MB et al (2004) Defects and faults in quantum cellular automata at nano scale. In: VLSI Test Symposium, 2004. Proceedings. 22nd IEEE. IEEE

Momenzadeh M et al (2004) Quantum cellular automata: new defects and faults for new devices. In: Parallel and Distributed Processing Symposium, 2004. Proceedings. 18th International. IEEE

Huang J, Momenzadeh M, Lombardi F (2007) On the tolerance to manufacturing defects in molecular QCA tiles for processing-by-wire. J Electron Test 23(2):163–174

Sen B et al (2014) Efficient design of fault tolerant tiles in QCA. In: India Conference (INDICON), 2014 Annual IEEE. IEEE

Sen B et al (2016) On the reliability of majority logic structure in quantum-dot cellular automata. Microelectron J 47:7–18

Sen B et al (2016) Towards the design of hybrid QCA tiles targeting high fault tolerance. J Comput Electron 15(2):429–445

Du H et al (2016) Design and analysis of new fault-tolerant majority gate for quantum-dot cellular automata. J Comput Electron 15(4):1484–1497

Sun M et al (2018) The fundamental primitives with fault-tolerance in quantum-dot cellular automata. J Electron Test 34(2):109–122

Wang X et al (2018) Design and comparison of new fault-tolerant majority gate based on quantum-dot cellular automata. J Semicond 39(8):085001-1–085001-8

Farazkish R (2018) Novel efficient fault-tolerant full-adder for quantum-dot cellular automata. Int J Nano Dimens 9(1):58–67

Tougaw PD, Lent CS (1994) Logical devices implemented using quantum cellular automata. J Appl Phys 75(3):1818–1825

Walus K et al (2004) QCADesigner: a rapid design and simulation tool for quantum-dot cellular automata. IEEE Trans Nanotechnol 3(1):26–31

Halloun IA, Hestenes D (1985) Common sense concepts about motion. Am J Phys 53(11):1056–1065

McDermott LC (1984) Research on conceptual understanding in mechanics. Phys Today 37:24–32

Halliday D, Resnick R, Walker J (2011) Fundamentals of physics, 9th edn. Wiley, Hoboken, NJ

Momenzadeh M, Ottavi M, Lombardi F (2005) Modeling QCA defects at molecular-level in combinational circuits. In: 20th IEEE International Symposium on Defect and Fault Tolerance in VLSI Systems, 2005. DFT 2005. IEEE

Srivastava S et al (2011) QCAPro-an error-power estimation tool for QCA circuit design. In: 2011 IEEE International Symposium on Circuits and Systems (ISCAS). IEEE

Ahmad F (2018) An optimal design of QCA based 2n: 1/1: 2n multiplexer/demultiplexer and its efficient digital logic realization. Microprocess Microsyst 56:64–75

Rashidi H, Rezai A, Soltany S (2016) High-performance multiplexer architecture for quantum-dot cellular automata. J Comput Electron 15(3):968–981

Chabi AM et al (2014) Efficient QCA exclusive-or and multiplexer circuits based on a nanoelectronic-compatible designing approach. International scholarly research notices

Sen B et al (2013) Multilayer design of QCA multiplexer. In: India Conference (INDICON), 2013 Annual IEEE. IEEE

Roohi A et al (2011) A novel architecture for quantum-dot cellular automata multiplexer. Int J Comput Sci Issues 8(1):55–60

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Ahmadpour, SS., Mosleh, M. A novel fault-tolerant multiplexer in quantum-dot cellular automata technology. J Supercomput 74, 4696–4716 (2018). https://doi.org/10.1007/s11227-018-2464-9

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11227-018-2464-9