Abstract

Since conventional CMOS technology has met its development bottleneck, an alternative technology, quantum-dot cellular automata (QCA), attracted researchers’ attention and was studied extensively. The manufacturing process of QCA, however, is immature for commercial production because of the high defect rate. Seeking for designs that display excellent performance shows significant potentials for practical realizations. In the paper we propose a 5 × 5 module, which not only can implement three-input majority gate but also can realize five-input majority gate by adding another two inputs. A comprehensive analysis is made in terms of area, number of cells, energy dissipation and fault tolerance against single-cell omission defects. In order to testify the superiority of the proposed designs, preexisting related designs are tested and compared. Weighing up above four kinds of factors and technical feasibility, proposed majority gates perform fairly well. Further, we take full adders and multi-bit adders as illustrations to display the practical application of proposed majority gates. The detailed comparisons with previous adders reveal that proposed 5 × 5 module behaves well in circuits, especially the high degree of fault tolerance and the relatively small area, complexity and QCA cost, thereby making it more suitable for practical realizations in large circuit designs.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Conventional CMOS technology has encountered some challenges, such as physical scalability limits, leakage power consumption, and short channel effects [18]. Under the circumstance, a large amount of research on nano-scale has been done extensively. Quantum-dot cellular automata (QCA), a promising alternative technology with potential advantages of fast speed, high density and ultra-low power consumption [27, 32], offers a new method of computation and information transmission. QCA was first proposed by Lent et al. in 1993 [27], and was developed rapidly in recent years. Some experimental devices have been fabricated and tested [4, 25, 46]. To date, the implementation for multi-layer circuits has not been reported [5, 14], while coplanar circuit have already been fabricated [32].

The most distinct feature of QCA is that interaction between cells is absolute Columbic repulsion. Thus there is no current in circuits, which has a potential for extremely low energy dissipation, even makes it lower than traditional kBT in the most optimistic condition [39, 40]. Nevertheless, as an emerging technology, it is necessary to characterize all aspects of QCA. Due to the small size and the fact that electrons actually involve in computation, power consumption is an important parameter. Analogous to conventional CMOS designs, power loss in clocked QCA circuit can be categorized into two types that are commonly used in circuit theory: switching power and leakage power [39]. Switching power which depends on input combinations happens at the time when the cell is changing its state. Leakage power which has nothing to do with input states occurs when the clock goes up or falls down so as to ‘depolarize’ or ‘polarize’ a cell. The proportion of the two in total power dissipation relates strongly to the clock energy. To solve the power consumption in QCA circuits, various estimation models have been proposed, of which two representatives are the accurate power dissipation model and the upper bound power dissipation model, proposed by John Timler et al. and Saket Srivastava et al., respectively [39, 41]. Power dissipation of QCA devices and circuits can be estimated using these models so that we can pick out the superior. QCAPro based on the upper bound power model can be used to assess the performance of QCA designs under power analysis attack, including average, maximum, and minimum power dissipation [40].

Yet QCA technology has not been put into production heavily. One principal limitation is the high fault rate in manufacturing, particularly for molecular QCA, since it is difficult to be high precision within nanoscale. The fault rate has been predicted as high as 50% of the devices [17, 48]. Any defect could result in possible invalidation of device functions. Thus a device with fault tolerance appears to be particularly significant in practice. Robustness and fault tolerance properties have been investigated during the past few years [23, 34]. There are various types of defects that may occur in QCA devices during the fabrication, such as cell misalignment, cell displacement, cell omission, cell rotation and so on. Functionalities of a device may still exist when these defects happen, namely reliability. This is just the direction we are pursuing for. In this paper, we analyze the reliability of QCA designs in presence of single-cell omissions. The designs with the property of insensitiveness to cell omissions will show good prospects in further development.

The main aim of our work is to seek out a three and five-input majority gates with fault tolerance. In order to characterize the proposed majority gates, comparisons are made with their counterparts in terms of area, number of cells, energy dissipation and fault tolerance. By applying the proposed designs to practical circuits and comparing with relevant circuits, the functionality and practicability of them are verified.

The reminder of the paper is organized as follows: Section 2 presents QCA theoretical background and some basic devices. Elaborately selected and our proposed designs as well as their applications will be shown and discussed in Section 3. The simulation results of all circuits are displayed in Section 4. Finally, conclusions are given in Section 5.

2 QCA

The elementary units in QCA are cells. A quantum cell can be viewed as a square with four dots positioned at the corners of it [42]. The cell contains two extra mobile electrons which can quantum mechanically tunnel between dots within the cell but not cells. Due to Columbic repulsion, electrons always occupy the diagonal positions of square in the absence of any external influence. Thus, two possible polarization states, i.e. “P = −1” and “P = +1”, can be used to represent logic “0” and logic “1” respectively, as shown in Fig. 1a [30]. There is another type of QCA cells, i.e. rotated cells, which are able to achieve the same result, as illustrated in Fig. 1b. The difference between these two types of cells is the way of information transmission according to Columbic repulsion of electrons. Two neighboring standard cells will achieve same polarization, while rotated cells will get reverse polarization. The rotated cells can be used to realize coplanar wire-crossing with standard cells.

Two fundamental building blocks utilized as critical elements in QCA circuits are inverters and majority gates [35]. Since every QCA circuit can be implemented only using majority gates and inverters, efficient constructions of them are of great importance [31]. Figure 2 shows two frequently-used inverters.

As depicted in Fig. 3a, a three-input majority gate is composed of five cells, with three input cells labeled as A, B, C, an output cell marked with F and the center one called device cell. The logic expression of it is F = M (A, B, C) = AB + BC + AC. The output of majority gate depends on the values of given inputs that occupy the major, just like a voter. Two-input “AND” gate or “OR” gate can be implemented by fixing a input into logic 0 or logic 1, respectively, as shown in Fig. 3b and c. The governing equations for “AND” and “OR” gates using 3-input majority gate are

With “AND”, “OR” and inverters, any logic function can be realized.

On account of the important role of 3-input majority gate in QCA, different designs have been investigated over last years. Even though the three-input majority gate in Fig. 3a is the simplest and the most elementary one, missing of any one cell could lead to defects. In Fig. 4 six formerly proposed types of 3-input majority gates with fault tolerance are shown. Seeking for high degree of fault tolerance, low power dissipation, small area and number of cells is beneficial to future realization. These layouts are designed to balance above factors.

The logic function of five-input majority gate can be presented as:

where A, B, C, D and E are inputs and F is output.

Similar to 3-input majority gate, “AND” or “OR” gate can also be realized using 5-input majority gate. By forcing two of the five inputs’ polarizations to −1 or + 1, a 3-input “AND” or “OR” gate is formed. As yet, several implementations of 5-input majority gate have been reported, as shown in Fig. 5.

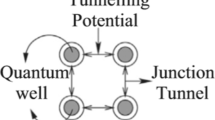

To minimize the power dissipation and hold the stable state of a QCA system consistently, the adiabatic switching mechanism, which is achieved by an external electric field, was introduced to solve the disadvantages of abrupt switching. This method is absolutely different from the clocking mechanism represented by the levels of voltage in CMOS-based circuits [19, 26, 41]. During the adiabatic switching, QCA system can always not only remain in instantaneous ground state, but also gain the least amount of power consumption. As shown in Fig. 6, the QCA clocking mechanism has four clocking zones, each of which is shifted from the previous one by 90° and has four phases: switch, hold, release and relax [43]. At the beginning, the cells in a system stand at the relax state because the inter-dot tunnel barriers are controlled at the lowest level. With the gradually increased barriers over switch phase and peaking in hold state, the polarizations of the cells will encode the binary information. During the release phase the tunnel barriers decrease and then reach the lowest value at relax state, which results in the complete loses of polarization information in each cell and preparation for the next cycle [22].

The equation for the instantaneous total power for a single QCA cell is written as

where \( \overrightarrow{\Gamma} \) represents the real 3-D energy vector, \( \overrightarrow{\uplambda} \) is the coherence vector. The first term P 1 in above equation represents the difference (P in - P out ) between power input (P in ) and power output (P out ) and the power (P clock ) transferred from clocking signal. The second term P 2 gives the dissipated power (P diss ) that is exactly our concerned. In a quasi-infinite QCA array, P in achieved from left neighboring cell is equal to P out released power to the right neighboring cell. Moreover, in switch phase, with the increasing of inter-dot barrier, an amount of energy transfers from clocking to cell. Afterwards, most of the energy returns to clocking over lowering phase of barrier, which leads to a trivial power dissipation just named P diss .

3 Proposed Fault-Tolerant Designs and Applications

3.1 Proposed Designs

Fault-tolerant design in QCA is an essential subject for representation of suitable functionality of the circuits. Faults always occur without expectation during the assembly of a circuit, such as “misalignment” cells (quantum cells are shifted from their intended locations), “missing” cells (a quantum cell or several quantum cells is or are missing), “dislocation” cells (quantum cells are rotated relative to other cells in the array), all of which may result in the termination of function of circuits. In the paper, we focus on the defects of cell omissions. We propose two kinds of novel designs with respect to majority gates including 3-input and 5-input. Three-input majority gate in Fig. 7a and five-input majority gate in Fig. 7b are both based on a 5 × 5 module. Three-input majority gate is added two more inputs to implement five-input majority gate, which is convenient to achieve the transformation between these two gates.

In order to authenticate the correctness and the functionality of our proposed designs as well as previously related designs, QCADesigner version 2.0.3 [44] with the bistable approximation engine setup summarized in Table 1 is used.

3.2 Physical Proof for Five-Input Majority Gate with One Cell Omission

Since proposed five-input majority gate has 27 cells and any cell missing could lead to invalidation of the design, we should check all the faults that may occur in cells to verify the correctness of the scheme. Here, as shown in Fig. 8, we just prove one of the faults that occurs in the third row, forth column of the 5 × 5 module. Similarly, other faults can be proved as well. Five inputs of the majority gate are assumed to A = C = E = 1 and B = D = 0. Figure 8a and b denote two possible states of the output F, respectively. By calculating the total electrostatic energy of these two configurations, we can find the more stable one with lower kink energy level. The electrostatic energy between two electrons is calculated using Eq. (5).

where U is electrostatic energy between two electrons, k is a constant, q 1 and q 2 are electron charges, and r is distance between these two electrons.

By computing the electrostatic energy between 14 electrons and x, y respectively, the total electrostatic energy can be achieved. Further detailed calculation is shown in Table 2. The eventual results (\( {U}_{T_1}<{U}_{T_2} \)) prove that the state in Fig. 8a is the more stable one. The functionality also can be verified using QCADesigner.

3.3 Application

As mentioned earlier, many QCA designs including adders, multipliers, multiplexers etc. can be implemented based on majority gates. Two novel one-bit full adders are displayed using three and five-input majority gates proposed, as shown in Fig. 9. Figure 9a displays a full-adder with three three-input majority gates. The other one shown in Fig. 9b is implemented using a three-input majority gate and a five-input majority gate. As illustrated in Fig. 10, the 4-bit carry flow adder, which has a 1.5 clock cycles, is implemented with coplanar crossovers in each unit. The n-bit carry flow adder can be constructed by cascading n proposed adders logically.

4 Simulation Results

4.1 Three-Input Majority Gate

Table 3 displays the physical properties of three-input majority gates from different references. P denotes the proposed 3-input majority gate. Figure 11 depicts the bar-graphs of these comparisons.

The gate in [26] has the smallest area, number of cells and energy dissipation in contrast with other gates. However, the design will lose its function when any one cell misses, namely the fault tolerance is 0, just as shown in Fig. 11c. P reaches 45.70% improvement in fault tolerance compared with [7] which can be viewed as a 3 × 3 tile. [38] is a grand design with largest area, maximum cell counts and highest average energy dissipation. The fault tolerance of it, 97.44%, is also the highest one. All the cases are correct except one on the left of the output cell F in the presence of single-cell omission. But limited by the manufacturing process of QCA technology, rotated cells used in the design are yet to come true, thereby making it unsuitable for practical realization. [3, 8] can be considered as a 4 × 7 module and a 3 × 5 module respectively. Fault tolerance of gate P leads to 25.91% and 34.92% improvements compared with that of them, respectively. The gate in [3], in terms of area, number of cells, energy dissipation and fault tolerance, always shows poorer performance in contrast with P. Fault tolerances of [9, 24] are almost equal to that of P. However, the superiority of gate P is that it can be extended into five-input majority gate by adding another two input cells as shown in Fig. 7b. Note that the structure of [9] is highly similar to that of P. But the simulation results with QCADesigner show erroneous outputs when adding two more inputs just like the way in Fig. 7.

Figure 11d-f illustrate the average energy, average leakage energy, average switching energy dissipation for the majority gates listed. Although the average energy dissipation of the proposed design is not the optimal, we can sum up that the three-input majority gate proposed in the paper displays significant practical value by comparisons and tradeoffs with previous proposed designs.

4.2 Five-Input Majority Gate

Table 4 displays the physical properties of different five-input majority gates. P is the proposed five-input majority gate. It is apparent that the fault tolerance of gate P is highest, achieving 47.62%, with relatively small area and number of cells. Figure 12 illustrate these characteristics lucidly. These characteristics make the design P a superior scheme. Although the structure of [31] is simplest, the fault tolerance of it is 0. Besides, the specificity of five inputs of design results in that the multi-layer structure must be needed if the design is employed to circuits. Analogous to above mentioned rotated cells, multi-layer structure is also a pitfall which has not been resolved so far. [1] in Fig. 5b, [1] in Fig. 5c and [8] can be regarded as a 3 × 3, 5 × 5 and 3 × 5 module respectively. As shown in Fig. 12c, the fault tolerance of [1] in Fig. 5b is 0. The structures of [1] in Fig. 5c and P are almost same apart from the positions of inputs and outputs. No matter from the view of area and number of cells or energy dissipation and fault tolerance, however, the design P surpasses the design in Fig. 5c. [8] has no significant difference compared with P in terms of area, number of cells and average energy dissipation. But the fault tolerance of it is far (35.12%) lower than that of P. [10, 13] both are magnificent structures with the bigger areas, the greater complexities, and the higher energy dissipations compared with other designs. However, neither [13] nor [10] can reach the same degree of fault tolerance of P, 3.17% and 13.53% lower than that of P respectively. Besides, the output cell of [10] is surrounded by other cells so that a multi-layer structure is needed to connect to circuits, which drastically reduces the feasibility of the scheme.

4.3 Proposed Multi-Bit Adders

The correct simulation results using QCADesigner verify the functional behaviors of the proposed full adders, as shown in Fig. 13a and b, respectively.

In order to judge the merits of the work, comparisons are made with other one-bit full adders with respect to area, delay and fault tolerance. Here, the reason why we don’t involve energy dissipation is that QCAPro used in the analysis of energy dissipation can be used for single-layer designs only, while most full adders are multi-layer constructions.

Table 5 presents the comparisons of full adders. Proposed one-bit full adders shown in Fig. 9a and b are labeled as P1 and P2 respectively. The areas of P1 and P2, shown in Fig. 14a, are in the middle position. P1 and P2 are both using three clock phases shown in Fig. 14b. The fault tolerance of carry of P1 and P2 is also high, achieving 85.12% and 93.58% respectively, which is at a higher level, as shown in Fig. 14c. What’s more, as apparent from Fig. 14d, fault tolerance of sum of P1 and P2 is above all others, up to 59.5% and 41.28% respectively. Especially P1, the improvement of it is quite significant. Weighing up these factors, P1 and P2 are of great value.

Table 6 lists the comparison for area of the multi-bit adders with several existing adders. To display the contrast effect of the area, the trend carves are made in Fig. 15a. Clock delay comparision is shown in Fig. 15b. Table 7 indicates the number of majority gates (MV), the number of inverters (INV), the number of crossings and the delay in various adders. The complexity of the adders is denoted as M + I + C, where M, I and C represent the number of majority gates, number of inverters, number of crossings, respectively, as demonstrated in Fig. 15c. Reference [28] described a criterion about the design of cost functions for QCA circuits as Cost = (M2 + I + C2) × T, where T(clock cycles) is the delay of one circuit. Figure 15d illustrates the comparison of the QCA cost listed in Table 7. From the trend curves of 12 multi-adders in Fig. 15, it is found to be that P surpasses the huge majority adders, ranking the fifth in area, the fourth in complexity and cost. Only the multi-bit adders in [6, 37] are always superior to the proposed one in these three aspects. The multi-adders in [35] is also better than P in terms of area and cost but the complexity. The value of our proposed multi-adders, however, is the implementation of crossing with coplanar types while adders in [6, 35, 37] are multi-layer crossings. Although the multi-layer designs will be area-efficient, they bring the fabrication difficulty at the same time because the multi-layer crossovers require at least three layers to design the circuits. Note that P shows the best performance in the present of all the coplanar crossings. Combined with forementioned analysis, the proposed adders will be better alternatives.

5 Conclusion

In this paper, we proposed a three-input majority gate based on a 5 × 5 module, the main method of module design methodology. Then a five-input majority gate was implemented with this gate by adding two more inputs on the basis of three-input majority gate, which distinguishes our designs from others. Both two designs showed better simulation results than prior work given area, number of cells, energy dissipation and fault tolerance into comprehensive consideration. Especially in fault tolerance, two designs are up to 80.95% and 47.62% respectively in the presence of one cell omission. One-bit full adders were implemented based on proposed three-input and five-input majority gates. Compared with existing designs, these two adders behave well, which verifies the practicability of the proposed majority gates at the same time. Moreover, to illustrate the applications of the proposed full adder and its scalability, the multi-bit designs were designed and also showed the better performance in terms of area, complexity and QCA cost in contrast to existing adders.

References

Akeela R, Wagh MD a five-input majority gate in quantum-dot cellular automata. In: Nanotechnology 2011: electronics, devices, fabrication, MEMS, fluidics and computational - 2011 NSTI nanotechnology conference and expo, NSTI-nanotech 2011, June 13, 2011 - June 16, 2011, Boston, MA, United States, 2011. Technical proceedings of the 2011 NSTI Nanotechnology Conference and Expo, NSTI-Nanotech 2011. Nano Science and Technology Institute, pp 13–16

Angizi S, Alkaldy E, Bagherzadeh N, Navi K (2014) Novel robust single layer wire crossing approach for exclusive OR sum of products logic design with quantum-dot cellular automata. J Low Power Electron 10(2):259–271. https://doi.org/10.1166/jolpe.2014.1320

Beard MJ (2006) Design and simulation of fault-tolerant quantum-dot cellular automata (QCA) NOT gates. Dissertation, Wichita State University

Bernstein GH, Imre A, Metlushko V, Orlov A, Zhou L, Ji L, Csaba G, Porod W (2005) Magnetic QCA systems. Microelectron J 36(7):619–624. https://doi.org/10.1016/j.mejo.2004.12.002

Chaudhary A, Chen DZ, Hu XS, Niemier MT, Ravichandran R, Whitton K (2007) Fabricatable interconnect and molecular QCA circuits. IEEE Trans Comput Aided Des Integr Circuits Syst 26(11):1978–1991. https://doi.org/10.1109/TCAD.2007.906467

Cho H, Swartzlander Jr EE (2009) Adder and multiplier design in quantum-dot cellular automata. IEEE Trans Comput 58(6):721–727. https://doi.org/10.1109/TC.2009.21

Das K, De D (2010) QCA defect and fault analysis of diverse nanostructure for implementing logic gate. International journal of recent trends in. Eng Technol 3(1)

Du H, Lv H, Zhang Y, Peng F, Xie G (2016) Design and analysis of new fault-tolerant majority gate for quantum-dot cellular automata. J Comput Electron 15(4):1484–1497. https://doi.org/10.1007/s10825-016-0918-y

Dysart TJ, M Kogge P (2017) S Lent C. An analysis of missing cell defects in quantum-dot cellular automata, Liu M

Farazkish R (2014) A new quantum-dot cellular automata fault-tolerant five-input majority gate. J Nanopart Res 16(2). https://doi.org/10.1007/s11051-014-2259-8

Farazkish R (2015) A new quantum-dot cellular automata fault-tolerant full-adder. J Comput Electron 14(2):506–514. https://doi.org/10.1007/s10825-015-0668-2

Farazkish R, Khodaparast F (2015) Design and characterization of a new fault-tolerant full-adder for quantum-dot cellular automata. Microprocess Microsyst 39(6):426–433. https://doi.org/10.1016/j.micpro.2015.04.004

Farazkish R, Navi K (2012) New efficient five-input majority gate for quantum-dot cellular automata. J Nanopart Res 14(11):1–6. https://doi.org/10.1007/s11051-012-1252-3

Gin A, Tougaw PD, Williams S (1999) An alternative geometry for quantum-dot cellular automata. J Appl Phys 85(12):8281–8286

Hanninen I, Takala J Robust adders based on quantum-dot cellular automata. In: 2007 I.E. International Conf on Application-specific Systems, Architectures and Processors (ASAP), 9–11 July 2007 2007. pp 391–396. https://doi.org/10.1109/ASAP.2007.4459295

Hayati M, Rezaei A (2015) Design of novel efficient adder and subtractor for quantum-dot cellular automata. Int J Circuit Theory Appl 43(10):1446–1454. https://doi.org/10.1002/cta.2019

Huang J, Momenzadeh M, Lombardi F (2007) On the tolerance to manufacturing defects in molecular QCA tiles for processing-by-wire. J Electron Test Theory Appl (JETTA) 23(2–3):163–174. https://doi.org/10.1007/s10836-006-0548-6

International Technology Roadmap for Semiconductors. (2011). http://www.itrs2.net

Janez M, Pecar P, Mraz M (2012) Layout design of manufacturable quantum-dot cellular automata. Microelectron J 43(7):501–513. https://doi.org/10.1016/j.mejo.2012.03.007

Kassa SR, Nagaria RK (2016) A novel design of quantum dot cellular automata 5-input majority gate with some physical proofs. J Comput Electron 15(1):324–334. https://doi.org/10.1007/s10825-015-0757-2

Kianpour M, Sabbaghi-Nadooshan R, Navi K (2014) A novel design of 8-bit adder/subtractor by quantum-dot cellular automata. J Comput Syst Sci 80(7):1404–1414. https://doi.org/10.1016/j.jcss.2014.04.012

Kim K, Wu K, Karri R (2006) Quantum-dot Cellular Automata design guideline. IEICE Trans Fundam Electron Commun Comput Sci E89-A(6):1607–1614. https://doi.org/10.1093/ietfec/e89-a.6.1607

Krishnaswamy S, Viamontes GF, Markov IL, Hayes JP (2008) Probabilistic transfer matrices in symbolic reliability analysis of logic circuits. ACM Trans Des Autom Electron Syst 13(1). https://doi.org/10.1145/1297666.1297674

Kumar D, Mitra D (2016) Design of a practical fault-tolerant adder in QCA. Microelectron J 53:90–104. https://doi.org/10.1016/j.mejo.2016.04.004

Kummamuru RK, Orlov AO, Ramasubramaniam R, Lent CS, Bernstein GH, Snider GL (2003) Operation of a quantum-dot cellular automata (QCA) shift register and analysis of errors. IEEE Trans Electron Devices 50(9):1906–1913. https://doi.org/10.1109/ted.2003.816522

Lent CS, Tougaw PD (1997) A device architecture for computing with quantum dots. Proc IEEE 85(4):541–557. https://doi.org/10.1109/5.573740

Lent CS, Tougaw PD, Porod W, Bernstein GH (1993) Quantum cellular automata. Nanotechnology 4(1):49–57. https://doi.org/10.1088/0957-4484/4/1/004

Liu W, Lu L, Oneill M, Swartzlander EE (2014) A first step toward cost functions for quantum-dot cellular automata designs. IEEE Trans Nanotechnol 13(3):476–487. https://doi.org/10.1109/TNANO.2014.2306754

Mohammadi M, Mohammadi M, Gorgin S (2016) An efficient design of full adder in quantum-dot cellular automata (QCA) technology. Microelectron J 50:35–43. https://doi.org/10.1016/j.mejo.2016.02.004

Nakagawa S, Eto M, Kawamura K (2001) Dynamic behavior of kink-solitons at junctions in quantum-dot cellular automata. Jpn J Appl Phys Part 1 - Regul Pap Short Notes Rev Pap 40(3B):2046–2049. https://doi.org/10.1143/jjap.40.2046

Navi K, Farazkish R, Sayedsalehi S, Rahimi Azghadi M (2010) A new quantum-dot cellular automata full-adder. Microelectron J 41(12):820–826. https://doi.org/10.1016/j.mejo.2010.07.003

Orlov AO, Amlani I, Toth G, Lent CS, Bernstein GH, Snider GL (1999) Experimental demonstration of a binary wire for quantum-dot cellular automata. Appl Phys Lett 74(19):2875–2877. https://doi.org/10.1063/1.124043

Pudi V, Sridharan K (2012) Low complexity design of ripple carry and Brent-kung adders in QCA. IEEE Trans Nanotechnol 11(1):105–119. https://doi.org/10.1109/TNANO.2011.2158006

Rejimon T, Lingasubramanian K, Bhanja S (2009) Probabilistic error modeling for nano-domain logic circuits. IEEE Trans Very Large Scale Integr VLSI Syst 17(1):55–65. https://doi.org/10.1109/TVLSI.2008.2003167

Roohi A, DeMara RF, Khoshavi N (2015) Design and evaluation of an ultra-area-efficient fault-tolerant QCA full adder. Microelectron J 46(6):531–542. https://doi.org/10.1016/j.mejo.2015.03.023

Sayedsalehi S, Moaiyeri MH, Navi K (2011) Novel efficient adder circuits for quantum-dot cellular automata. J Comput Theor Nanosci 8(9):1769–1775. https://doi.org/10.1166/jctn.2011.1881

Sen BABK (2013) Design of Efficient Full Adder in quantum-dot cellular automata. Sci World J 2013. https://doi.org/10.1155/2013/250802

Sen B, Dutta M, Mukherjee R, Nath RK, Sinha AP, Sikdar BK (2016) Towards the design of hybrid QCA tiles targeting high fault tolerance. J Comput Electron 15(2):429–445. https://doi.org/10.1007/s10825-015-0760-7

Srivastava S, Sarkar S, Bhanja S (2009) Estimation of upper bound of power dissipation in QCA circuits. IEEE Trans Nanotechnol 8(1):116–127. https://doi.org/10.1109/TNANO.2008.2005408

Srivastava S, Asthana A, Bhanja S, Sarkar S QCAPro - An error-power estimation tool for QCA circuit design. In: 2011 I.E. International Symposium of Circuits and Systems, ISCAS 2011, May 15, 2011 - May 18, 2011, Rio de Janeiro, Brazil, 2011. Proceedings - IEEE international symposium on circuits and systems. Institute of Electrical and Electronics Engineers Inc., pp 2377-2380. https://doi.org/10.1109/ISCAS.2011.5938081

Timler J, Lent CS (2002) Power gain and dissipation in quantum-dot cellular automata. J Appl Phys 91(2):823–831. https://doi.org/10.1063/1.1421217

Tougaw PD, Lent CS (1994) Logical devices implemented using quantum cellular automata. J Appl Phys 75(3):1818–1825. https://doi.org/10.1063/1.356375

Vankamamidi V, Ottavi M, Lombardi F (2008) Two-dimensional schemes for clocking/timing of QCA circuits. IEEE Trans Comput Aided Des Integr Circuits Syst 27(1):34–44. https://doi.org/10.1109/TCAD.2007.907020

Walus K, Dysart TJ, Jullien GA, Budiman RA (2004) QCADesigner: a rapid design and simulation tool for quantum-dot cellular automata. IEEE Trans Nanotechnol 3(1):26–31. https://doi.org/10.1109/TNANO.2003.820815

Wang W, Walus K, Jullien GA Quantum-dot cellular automata adders. In: 2003 3rd IEEE Conference on Nanotechnology, IEEE-NANO 2003, August 12, 2003 - August 14, 2003, San Francisco, CA, United states, 2003. Proceedings of the IEEE Conference on Nanotechnology. IEEE Computer Society, pp 461–464. https://doi.org/10.1109/NANO.2003.1231818

Wolkow RA, Livadaru L, Pitters J, Taucer M, Piva P, Salomons M, Cloutier M, Martins BVC Silicon atomic quantum dots enable beyond-CMOS electronics. In: 2013 Workshop on field-coupled Nanocomputing, FCN 2013, February 7, 2013 - February 8, 2013, Tampa, FL, United States, 2014. Lecture notes in computer science (including subseries lecture notes in artificial intelligence and lecture notes in bioinformatics). Springer Verlag, pp 33-58. https://doi.org/10.1007/978-3-662-43722-3_3

Zhang R, Walus K, Wang W, Jullien GA Performance comparison of quantum-dot cellular automata adders. In: IEEE International Symposium on Circuits and Systems 2005, ISCAS 2005, May 23, 2005 - May 26, 2005, Kobe, Japan, 2005. Proceedings - IEEE International Symposium on Circuits and Systems. Institute of Electrical and Electronics Engineers Inc., pp 2522–2526. https://doi.org/10.1109/ISCAS.2005.1465139

Zhang Y, Lv H, Liu S, Xiang Y, Xie G (2015) Defect-tolerance analysis of fundamental quantum-dot cellular automata devices. J Eng 2015. https://doi.org/10.1049/joe.2014.0344

Zhang Y, Lv H, Liu S, Xiang Y, Xie G (2015) Design of quantum-dot cellular automata circuits using five-input majority gate. J Comput Theor Nanosci 12(10):3675–3681. https://doi.org/10.1166/jctn.2015.4259

Zhang Y, Lv H, Du H, Huang C, Liu S, Xie G (2016) Modular design of QCA carry flow adders and multiplier with reduced wire crossing and number of logic gates. Int J Circuit Theory Appl 44(7):1351–1366. https://doi.org/10.1002/cta.2163

Acknowledgment

This work is supported by the National Natural Science Foundation of China (No. 61271122).

Author information

Authors and Affiliations

Corresponding author

Additional information

Responsible Editor: C. Metra

Rights and permissions

About this article

Cite this article

Sun, M., Lv, H., Zhang, Y. et al. The Fundamental Primitives with Fault-Tolerance in Quantum-Dot Cellular Automata. J Electron Test 34, 109–122 (2018). https://doi.org/10.1007/s10836-018-5723-z

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-018-5723-z