Abstract

Two different techniques, namely in-situ cycle annealing and post-growth patterning and annealing, were studied to reduce dislocation density in thick CdTe epilayers grown directly on (211) Si substrates using metal organic vapor phase epitaxy (MOVPE) for their applications in X-ray, gamma ray detector development. During in-situ annealing, it was observed that annealing initiated at a later stage of growth reduced the dislocation density more effectively than annealing initiated at the early growth stage. Nonetheless, in both cases, the dislocation density was reduced compared to the unannealed samples of similar thicknesses. On the other hand, the post-growth patterning of CdTe/Si into square islands, and subjecting these patterned samples to annealing was found to be more effective in reducing dislocations compared to the in-situ whole wafer annealing. However, subsequent growth of CdTe on the patterned and annealed samples to achieve thicker epilayers resulted rough surface, making them unsuitable for detector development.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Epitaxially grown high-quality single crystal CdTe layers on large-area alternative substrates, such as Si, GaAs, offer potential for diverse applications. These extensive crystals can be used in the development of large-area infra-red (IR) focal-plane arrays for defense and space application, tandem solar cells for efficient energy conversion, and X-ray, gamma ray detectors for nuclear medical imaging, security, as well as in a range of scientific applications [1,2,3,4,5]. Particularly, heteroepitaxy of CdTe on Si not only yields large-area crystals but also enables the integration of IR and X-ray imaging detector arrays with Si-based readout electronics. Nevertheless, the valence mismatch, along with substantial differences in lattice constants and thermal expansion coefficients between CdTe and Si poses considerable challenges in this heteroepitaxial growth. This difficulty results in the formation of highly defective epilayers with a high density of dislocations. Various techniques, including multistep growth with in-situ thermal annealing [4,5,6,7], selective growth on patterned substrates [8, 9], thermal cycle annealing on planar or mesa-structured samples [10,11,12,13], and the incorporation of strain superlattices, have been investigated to reduce the dislocation densities in mismatched heteroepitaxy [14, 15].

Recently, growth of CdTe on Si substrates by molecular beam epitaxy (MBE) or metalorganic vapor phase epitaxy (MOVPE), has resulted high-quality epilayers with dislocation densities in the low to mid-105 cm−2 range [5, 9, 10]. This is achieved by incorporation a thin ZnTe or Ge buffer layer before CdTe growth, followed by multiple cycles of thermal annealing. This approach is effective for IR detector technology, where CdTe layers serve solely as lattice-matched substrates for the subsequent growth of HgCdTe, and the device operates in the lateral direction. However, the addition of buffer layers creates a barrier for charge carriers in vertically operating devices, such as X-ray detectors or solar cells, where the photon-generated charge carriers traverse vertically across the heterointerface.

We investigated the direct growth of thick CdTe layers on (211) Si substrates without the use of buffer layers. To achieve thick epitaxial single crystal CdTe, we employed a specially designed Si substrates pretreatment technique, as detailed previously [16]. Subsequently, we utilized these layers to fabricate X-ray, gamma ray detectors in a p-CdTe/n-CdTe/n+-Si heterojunction diode structure [16]. Nevertheless, the performance of the detector was constrained by crystal defects. Dislocations that extend into the p-n junction contribute to a significant device dark current, thereby substantially degrading device property [17]. Therefore, it is imperative to reduce these dislocations to enhance device property.

In our previous work, we explored post-growth thermal cycle annealing of CdTe/Si and observed enhanced crystallinity through X-ray rocking curve and photoluminescence measurements [18, 19]. While the annealing process effectively reduced dislocations in thin layers, its effect was less prominent in thick layers. Additionally, the improvements in the gamma detection properties of the detector were limited.

In this work, we explored two dislocation reduction approaches for thick CdTe epilayers. Firstly, we examined the impact of in-situ annealing during the growth process to identify the optimal initial CdTe layer thickness before the onset of annealing that produces high-quality thick layers. Secondly, we investigated post-growth pattering of islands on the CdTe/Si, followed by annealing and regrowth. The aim was to reduce dislocations on the islands by guiding them toward the edges, facilitating their escape and achieving high-quality selective growth of thick layers on the islands.

Here, we discuss the properties of CdTe crystals and suggest the most suitable technique for growing the thick CdTe layers needed in the development of X-ray, gamma ray detectors.

2 Experimental details

CdTe layers were grown on (211) Si substrates in a vertical-type MOVPE reactor with a rotating heater/susceptor. The growth was performed using dimethylcadmium (DMCd) and diethyltelluride (DETe) precursors, maintaining a DETe/DMCd flow rate ratio of 3. The details of the growth process have been reported elsewhere [15]. In summary, (211) n-type Si substrates underwent chemical cleaning and etching before being placed in a dedicated horizontal quartz-tube chamber, alongside with clean GaAs pieces. The substrates were heated above 800 °C in a hydrogen environment maintaining a temperature gradient between Si and GaAs. This resulted a clean passivated Si surface. Following the treatment, the Si substrates were promptly transferred to the MOVPE growth chamber for CdTe growth. This pretreatment step was essential for achieving epitaxial growth.

We investigated two techniques detailed below to reduce dislocation density in the epilayer. All epilayers in this study were characterized using double crystal X-ray rocking curve (DCRC), and 4.2 K photoluminescence (PL). Dislocation density was estimated by subjecting the samples to dislocation decorative etching using Everson solution [20], and counting the triangular pits formed on the surface using an optical microscope.

2.1 Study of in-situ annealing

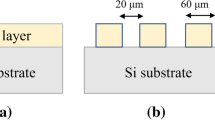

The samples were prepared as follows: Initially, a thin CdTe nucleation layer was grown at 350 °C for 10 min. Subsequently, the substrate temperature was raised to 450 °Cand CdTe layers of various thicknesses (buffer layers) were grown by varying the growth time from 30 to 60 min. In-situ annealing was applied to investigate the impact of annealing on the initial buffer layer thickness. The annealing temperature was varied from 500 to 600 °C, number of cycles one or two, and duration per cycle was kept fixed at 5 min. DETe precursor was introduced into the growth chamber during annealing to maintain a Te-environment. Then final CdTe growth occurred at 450 °C to make overall CdTe thickness of approximately 12 μm, as in Fig. 1a. A limited number of samples with similar thicknesses were also grown without subjecting the in-situ annealing. Finally, all CdTe/Si samples were cut into several 6 mm × 6 mm pieces for various characterizations.

2.2 Study of post-growth pattering, annealing and regrowth

In this study, initial thin CdTe epilayers of varying thicknesses (0.4 ~ 5 μm) were grown on Si substrates, followed by patterning using photolithography to form islands measuring 60 × 60 µm2, with a 20 μm gap between the islands. Subsequently, ex-situ thermal annealing was applied at 500 °C for 5 min, in a flowing hydrogen environment. This annealing condition was optimized in a separate study [19]. Following annealing, the samples were re-introduced into the MOVPE growth chamber and the final CdTe growth was carried out at temperatures varying from 350 to 500 °C. The schematic representation of sample structure is presented in Fig. 1b.

3 Results and discussion

3.1 In-situ annealing: effect of buffer layer thickness

All CdTe epilayers grown on the (211) Si substrates exhibited a single crystalline structure with growth orientation parallel to the substrate. The XRD pattern revealed only CdTe (422) peak, indicating the absence of twinned regions in the grown crystal. Figure 2 shows DCRC FWHM values from the CdTe (422) peaks as a function of buffer layer thickness (growth time). Following the buffer layer growth, the samples were subjected to in-situ annealing at 550 °C, in a Te-environment for 1 or 2 cycles, with a fixed annealing duration of 5 min per cycle. Subsequently, the final layer growth occurred at 450 °C. For comparison, the XRD DCRC value of a sample without in-situ annealing is also presented in the figure. The results reveal an improvement in the DCRC values after annealing, where better outcomes observed when annealing commenced at the later stage of buffer layer growth. However, samples, apart from the 30 min buffer layer growth, exhibit poor crystallinity during 2-cycle annealing. This could be attributed to surface roughening caused by CdTe etching due to the elevated sample temperature. It is probable that the actual surface temperature exceeds the set value with an increase in the number of annealing cycles.

We further examined the effect on annealing temperature using a fixed buffer layer thickness. Figure 3 shows DCRC FWHM values of the samples as a function of annealing temperature, with the buffer layers grown for 60 min before initiating the annealing. The annealing cycle was set either 1 or 2, and the duration per cycle was fixed at 5 min. The results suggest that a single-cycle annealing at 550 °C is optimal for enhancing crystallinity.

Figure 4 presents the surface morphology of Everson etched samples prepared through single-cycle, in-situ annealing at different temperatures. The surface morphology of a sample prepared without in-situ annealing is also included for comparison. Triangular pits corresponding to the CdTe (211)B face are clearly visible in the images. Based on this observation, we counted the pits on the surface and plotted them as a function of annealing temperature, as shown in Fig. 5. A notable reduction in the etch pit density (EPD) values was observed in the annealed samples compared to the unannealed one. The lowest EPD value, 9.5 × 105 cm−2, was achieved in the sample annealed at 550 °C. This indicates that thermal annealing effectively facilitated the motion of threading dislocations, activating their interactions in a way that resulted in the coalescence or annihilation of adjacent dislocations. As a result, their surface density decreased, as confirmed by lower etch pit counts. Similar reductions in threading dislocation density have been reported in various studies after thermal cycle annealing [5, 10, 21]. On the other hand, increasing the annealing cycle to two resulted in a higher pit density compared to the single-cycle anneal. This increase could be attributed to the elevated surface roughness, as discussed above. Nonetheless, the pit densities of the 2-cycle annealed samples remained lower than those of the unannealed samples.

The crystal properties were further examined by low-temperature (4.2 K) PL measurement, using a 488 nm semiconductor laser as the excitation source. Figure 6 shows the PL spectra of samples annealed at 500 and 600 °C. The (A°,X) peak at 1.593 eV becomes sharper in the 500 °C annealed sample, indicating improved crystallinity. In contrast, an additional broad peak appears at 1.565 eV in the 600 °C annealed sample, likely attributed to donor-acceptor pair (DAP) transition involving a cadmium vacancy- related acceptor center [22]. This may be due to cadmium leaving the sample surface due to increased surface temperature.

3.2 Post-growth patterning, annealing and regrowth

CdTe thin buffer layers of various thicknesses were grown on (211) Si substrates at temperatures ranging from 350 to 400 °C. Growth times were varied from 10 to 60 min at each temperature to achieve CdTe epilayers of various thicknesses. Subsequently, squared islands were patterned on these CdTe/Si buffer layers using photolithography. Thee patterned samples were subjected to ex-situ annealing at 500 °C for 5 min, followed by the regrowth of subsequent CdTe layers at temperatures from 325 to 500 °C. The objective was to reduce the dislocation density on the islands and achieve high-quality selective growth of thick layers. Figure 7a presents a representative patterned sample used in this study, where the growth was performed at 400 °C, 10 min, resulting in an approximate CdTe buffer layer thickness of 2 μm. XRD measurement performed (not presented here) before pattering showed that the epilayers were (211) oriented, parallel to the Si substrate. Shown in Fig. 7b is the morphology of the sample after a 500 °C, 5 min anneal, followed by CdTe regrowth at 400 °C. The result reveals that CdTe growth occurred not only on the islands but also between them, resulting in a rough and uneven sample surface. Samples with varying buffer layer thicknesses (ranging from 0.4 to 5 μm), subjected to annealing and regrowth at various growth temperatures also exhibited similar results. It was observed that the surface roughness increased with the buffer layer thickness. This suggests that the investigated growth temperatures and the buffer layer thickness (islands’ height) are excessive, necessitating further optimization of growth conditions to achieve selective epitaxy exclusively on the CdTe islands.

Separate study was performed to assess the impact of island patterning and annealing on dislocation reduction. The dislocation density of the patterned and annealed samples was examined using defect-decorating etch. The results indicated that etch pit density on the islands was nearly an order of magnitude lower than on the unpatterned flat area of the wafer. This suggests that patterning and annealing facilitate dislocation interactions, leading to their annihilation or coalescence onto a single dislocation. Additionally, it aids in gliding dislocations towards the sidewalls of the islands in patterned samples, facilitating their escape and, consequently, reducing their densities at the island surface. The detailed results are reported elsewhere [19].

4 Conclusion

We investigated dislocation density reduction techniques for MOVPE-grown thick CdTe layers grown directly on (211) Si substrates, using in-situ cycle annealing during growth and post-growth patterning, annealing, followed by regrowth.

In-situ single-cycle annealing applied during the later stage of growth resulted in improved crystallinity compared to annealing at the early growth stage. The lowest etch pit density (EPD) value, 9.5 × 105 cm−2, was achieved for a 12 μm thick sample annealed with a single cycle at 550 °C for 5 min, with the annealing initiated after growing the CdTe buffer layer for 60 min.

Post-growth pattering and ex-situ annealing in a hydrogen environment was found to be effective in dislocation reduction, where nearly an order of magnitude reduction in EPD was achieved compared to unpatterned samples of similar thicknesses. However, selective growth on these patterned and annealed samples to achieve higher thicknesses resulted in a very rough surface, rendering it unsuitable for detector applications. At current stage, the in-situ annealing technique appears to be the preferable choice for detector development.

Data availability

The data that support the findings of this study are available from the corresponding author upon reasonable request.

References

Q. Jiang, A.W. Brinkman, B.J. Cantwell, J.T. Mullins, F. Dierre, A. Basu, P. Veermani, P. Sellin, J. Electron. Mater. 38, 1548 (2009)

K. Iso, Y. Gokudan, M. Shiraishi, M. Nishikado, H. Murakami, A. Koukitu, J. Cryst. Growth. 506, 185 (2019)

R. Pandey, J. Drayton, C. Gregory, N.M. Kumar, K. Tyler, R. King, J. Sites, 47th IEEE Photovoltaic Specialists Conference, pp. 1326–1329 (2020). https://doi.org/10.1109/PVSC45281.2020.9300571

J.W. Garland, T. Biegala, M. Carmody, C. Gilmore, S. Sivananthan, J. Appl. Phys. 109, 102425 (2011)

S.R. Rao, S.S. Shintri, J.K. Markunas, R.N. Jacobs, I.B. Bhat, J. Electron. Mater. 40, 1790 (2011)

M. Reddy, J.M. Peterson, T. Vang, J.A. Franklin, M.F. Vilela, K. Olsson, E.A. Patten, W.A. Radford, J.W. Bangs, L. Melkonian, E.P.G. Smith, D.D. Lofgreen, S.M. Johnson, J. Electron. Mater. 40, 1706 (2011)

Y. Chen, S. Simingalam, G. Brill, P. Wijewarnasuriya, N. Dhar, J.J. Kim, D.J. Smith, J. Electron. Mater. 41, 2917 (2012)

I.B. Bhat, S.R. Rao, S. Shintri, R.N. Jacobs, Phys. Status Solidi C 9, 1712 (2012)

T. Seldrum, R. Bommena, L. Samain, J. Dumont, S. Sivananthan, R. Sporken, J. Vac. Sci. Technol. B 26, 1105 (2008)

Y. Chen, S. Farrell, G. Brill, P. Wijewarnasuriya, N. Dhar, J. Cryst. Growth. 310, 5303 (2008)

G. Brill, S. Farrell, Y.P. Chen, P.S. Wijewarnasurya, M.V. Rao, J.D. Benson, N. Dhar, J. Electron. Mater. 39, 967 (2010)

S. Simingalam, J. Pattison, Y. Chen, P. Wijewarnasuriya, M.V. Rao, J. Electron. Mater. 45, 4668 (2016)

A.J. Stoltz, J.D. Benson, M. Carmody, S. Farrell, P.S. Wijewarnasuriya, G. Brill, R. Jacobs, Y. Chen, J. Electron. Mater. 40, 1785 (2011)

W.W. Pan, R.J. Gu, Z.K. Zhang, W. Lei, G.A. Umana-Membreno, D.J. Smith, J. Anotoszewski, L. Faraone, J. Electron. Mater. 51, 4869 (2022)

Y. Du, B. Xu, G. Wang, Y. Miao, Z. Li, Z. Kong, Y. Dong, W. Wang, H.H. Radamson, Nanomaterials 12, 741 (2022)

M. Niraula, K. Yasuda, A. Watanabe, Y. Kai, H. Ichihashi, W. Yamada, H. Oka, T. Yoneyama, H. Nakashima, T. Nakanishi, K. Matsumoto, D. Katoh, Y. Agata, IEEE Trans. Nucl. Sci. 56, 836 (2009)

B.S. Chaudhari, H. Goto, M. Niraula, K. Yasuda, J. Appl. Phys. 130, 055302 (2021)

M. Niraula, K. Yasuda, J. Ozawa, T. Yamaguchi, S. Tsubota, T. Mori, Y. Agata, IEEE Trans. Nucl. Sci. 65, 2325 (2018)

B.S. Chaudhari, M. Niraula, Y. Takagi, R. Okumura, K.P. Sharma, T. Maruyama, J. Electron. Mater. 52, 3431 (2023)

W.J. Everson, C.K. Ard, J.L. Sepich, B.E. Dean, G.T. Neugebauer, H.F. Schaake, J. Electron. Mater. 24, 505 (1995)

S. Farrell, M.V. Rao, G. Brill, Y. Chen, P. Wijewarnasuriya, N. Dhar, D. Benson, K. Harris, J. Electron. Mater. 40, 1727 (2011)

D.P. Halliday, M.D.G. Potter, J.T. Mullins, A.W. Brinkman, J. Cryst. Growth. 220, 30 (2000)

Funding

The authors declare that no funds, grants, or other support were received during the preparation of this manuscript.

Author information

Authors and Affiliations

Contributions

All authors contributed to this work.

Corresponding author

Ethics declarations

Conflict of interest

The authors have no conflicts to disclose.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Niraula, M., Chaudhari, B.S., Okumura, R. et al. Strategies for dislocation density reduction in CdTe epilayers grown directly on (211) Si substrates using MOVPE. J Mater Sci: Mater Electron 35, 31 (2024). https://doi.org/10.1007/s10854-023-11842-4

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s10854-023-11842-4