Abstract

The dielectric responses of ultrathin (~6.65 nm) HfO2 films, in the form of Al/HfO2/Si capacitors were prepared by rf sputtering technique, has been studied in the wide frequency range as a function of deposition temperatures. Deposition temperatures were varied from room temperature (30 °C) to 500 °C. Thickness and the interfacial and surface roughness of heterostructures were extracted by fitting the specular X-ray reflectivity data. The impedance analysis combined with modulus spectroscopy was performed to get insight of the microscopic features like grain, grain boundary and film–electrode interfaces and their effects in the film properties. The films exhibited maximum frequency dispersion in both real and imaginary part of impedance at low frequency range. The frequency analysis of the modulus and impedance studies showed the distribution of the relaxation times due to the presence of grains and grain boundaries in the films. Impedance analysis revealed that the interfacial polarization caused by space charges in the film/electrode interfaces plays an important role in the dielectric behavior of the capacitor. In order to explain effectively that the impedance plots contain one or two arcs due to more than one relaxation contributions, the results are interpreted using the approach proposed by Abrantes (Z / vs. |Z //|/f representation). The dielectric loss (tan δ) curves exhibited the fact that there is possibility of existence of a Schottky barrier at the insulator semiconductor interface, which is due to traps distributed throughout the semiconductor-insulator interface and it is believed to be due to auto doping during deposition process. The ac conductivity, σ ac (ω), varies as σ ac (ω) = Bω n with n in the range 0.06–0.71.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

In last decades tremendous research has been undertaken to replace the conventional SiO2 gate dielectric in the ultra large scale integrated circuit (ULSIC), by new dielectric materials for the gate stack with permittivity (dielectric constant) higher than that of SiO2 [1–6]. Attempt to find new suitable gate dielectric materials for future 14 nm node CMOS technologies is because SiO2 has already been scaled down to its technological and direct tunnelling (<3 nm) limit [5]. Recent research focused mainly on HfO2, Al2O3, ZrO2, TiO2, Gd2O3, La2O3, Y2O3, CeO2, Sm2O3 and their silicates [7–14]. HfO2 and HfO2-based materials (silicates aluminates and oxynitrides) are being proposed to replace the silicon oxide as they have good dielectric properties with thermal stability on Si substrates [15, 16]. It has been observed that irrespective of deposition methods there are few issues with HfO2 when the thickness of the film is reduced below 10 nm. The performance of these devices is dependent especially on the formation of an insulator layer, native or deposited, at the MOS interface, interface states (Dit) localised at the semi conductor/insulator interface and series resistance Rs. Moreover, the change in bias voltage and frequency has important effect on the electrical and dielectric properties of thin films as a function of deposition temperatures. Therefore a systematic detailed study of effect of deposition temperature on the electrical and dielectric properties of ultrathin film is still a very important research investigation. When a MOS structure is biased in strong accumulation, the frequency-dependent properties of MOS devices can be described via complex impedance. The complex impedance spectroscopy technique is very common for bulk ceramics, has been utilised in case of thin films by many researchers. While a dc measurement corresponds to the response in time domain, ac measurements pertain to response in frequency domain. It is a powerful and versatile technique to analyze the microstructure property relationship and it also allows distinction between different region intrinsic (bulk) and extrinsic contributions (grain boundary, surface layer and electrode contact problem [17–19]. An equivalent circuit based on the impedance data provides information on the physical processes occurring inside the sample. In this work we present the impedance spectroscopic studies of MOS structure using HfO2 as gate dielectric on p-type silicon prepared by rf sputtering.

2 Experimental details

Ultra thin hafnium oxide (HfO2) films (thickness 6.65 nm) were deposited by radio frequency (rf) sputtering technique on 1–20 Ω/cm resistivity p-type silicon substrate. Sputtering was carried out at power of 100 W directly from a high purity HfO2 target of one inch diameter. Silicon substrates were cleaned by using RCA method. The cleaned substrates were then loaded into the sputtering chamber for deposition of HfO2 thin films. The base pressure and operating pressure of the sputtering chamber were 5 × 10−5, 0.180 mbar, respectively. The distance between the target and the substrate was maintained at 4 cm and the deposition was carried out for 45 min. The deposition was done in a reactive gas environment. Argon and oxygen gas was fed into the sputtering chamber in the ratio of 5:1 during sputtering process. Three samples were deposited by varying the deposition temperature from room temperature (30–500 °C) and keeping all other parameters constant. The thickness of film was measured using Grazing incidence X-ray reflectivity GIXRR measurements. Grazing incidence X-ray reflectivity measurements were performed using a Philips X-Pert PRO-MRD diffractometer with CuKα (λ = 0.15418 nm) radiation operated at 45 kV and 40 mA. The X-ray reflection intensity was collected by a counter with a reception slit of width 0.1 mm. The sample was mounted on a vertical sample stage controlled by a higher-resolution goniometer with a 2θ angular resolution of 0.0002°. For electrical measurements aluminium was deposited as top electrode on HfO2 thin film through shadow mask using thermal evaporation technique at a base pressure 5 × 10−5 mbar thus making Al/HfO2/Si MOS capacitors. The area of the top electrodes is 1.8 × 10−3 cm2. An ohmic contact was also formed on the back side of the silicon substrate by thermally evaporating aluminium metal. The impedance measurements were carried out using keithely 4200 SCS at room temperature in the frequency range 5 kHz–5 MHz.

3 Results and discussion

3.1 Thickness and interfacial roughness

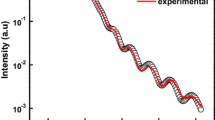

The surface and interface quality HfO2/Si heterostructures have been investigated through the analysis of X-ray reflectivity. Figure 1 shows the XRR spectrum of the film deposited at substrate temperature 500 °C. The specular reflectivity is plotted as a function of the vertical momentum transfer q z = 4πsinθ/λ (incidence angle equal to reflection angle), where q z is the momentum transfer perpendicular to the sample surface, θ is the grazing incidence angle, and λ is the wavelength of the X-rays. The specular reflectivity data has been fitted using the Parratt algorithm [20] in which the surface or interface root-mean-square (rms) roughness, thickness, and density of each constituent layer are the fitting parameters. Almost uniform oscillations in the reflectivity curve, starting from qz value of 0.05–1.2 are observed. This indicates that the deposited film is smooth with low surface and interface roughnesses. Fitting results revealed that there is a thin top surface layer of slightly different electron density from bulk HfO2 and thickness of the HfO2 layer is found to be 6.65 nm from fitting result. However an interfacial layer (SiO2) of thickness 1.2 nm is obtained from the fitting results. We attributed the SiO2 layer formation during deposition of the film at elevated temperature (Table 1).

3.2 Impedance analysis

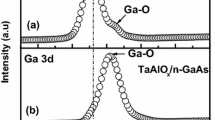

To study the frequency dependent property of the fabricated MOS capacitors the impedance spectroscopy analysis was performed on the three samples. For our convenience the film deposited at room temperature is named as X1, while film deposited at 300 °C and at 500 °C is named as X3 and X5, respectively. The use of impedance spectroscopy to characterise grain, grain boundary and electrode contributions by exhibiting successive semi circles (often with some distortion) of the impedance (real and imaginary part) in complex plane is well established [21, 22]. In case of AI/HfO2/p-Si MOS capacitors there is no distinct grain boundary but only bulk and interfaces (HfO2/p-Si and AI/HfO2) can contribute to the dielectric relaxation [23]. Figure 2 shows the impedance plane plots for all the three samples at various bias voltages.

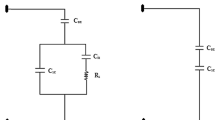

The characteristic semicircles could be obtained only in the depletion and accumulation region i.e. under the negative bias condition only. The impedance spectra (Z/ vs. Z//) are usually analysed in terms of complex formalism for the impedance \({\text{Z}}^{*} = {\text{Z}}^{/} + {\text{iZ}}^{//}\). Figure 2a–c show the impedance spectra of the three samples deposited at RT (X1), 300 °C (X3) and 500 °C (X5). The spectra depicted the characteristic semicircles. The semicircle in the high frequency region corresponds to the dielectric response of the bulk and the semicircles in the low frequency region correspond to the top and bottom interfaces. The impedance spectra of the sample X1 and X5 show two distinct semicircles while the impedance spectrum of the sample X3 also shows trace of a third semi circles in the low frequencies and at low voltages up to −1.5 V. To understand better the contributions from different relaxations with relatively small differences in time constants the alternative Z / versus |Z //|/f representation (at −1.5 V) proposed by Abrantes et al. [24] has been used. Accordingly, in Fig. 2d two well defined regions with different slopes are observed for all three samples. It confirms that there are two distinct regions of frequency response for the three samples originating from two different dielectric responses. It is also observed that frequency at which the two regions separated increased with increase in substrate temperature. The (Z/ vs. Z//) plots show that the semi circles in the low frequency region of X3 overlapped at higher voltages which indicates the very small difference in the relaxation time. The second semicircle of the sample X1 is almost a straight line making an angle ~45° with the real axis indicating very high resistance of the interfacial layer correspondingly very low relaxation frequency [25]. At low biasing voltages (<−3.5 V) the interfacial layer impedance dominates in all the samples. But from −3.5 V, the second semicircle in the lower frequency range in X3 and X5 bends indicating that the resistance of the grain-bulk region and the resistance of the interfacial region are comparable and both determine the observed frequency response. For all the samples the grain bulk resistance and the interfacial layer resistance decreased with increase in biasing voltage. The overall comparison of the impedance spectra of the three samples show that the resistance of grain bulk (Rg) and the resistance of interfacial layer (Ril) decreased with increase of deposition temperature. An electrical analog circuit representation applicable to our case will be a series combination of grain, interface and electrode elements and is shown in Fig. 3. The grain circuit consists of parallel combination of grain resistance (Rg) and grain capacitance (Cg), the grain boundary circuit i.e. the interfacial layer consists of parallel combination of interface resistance (Ril) and interface capacitance (Cil) and the electrode circuit (applicable only at −1.5 V for sample X3) consists of parallel combination of electrode resistance (Re) and electrode capacitance (Ce) [19].

The equivalent electrical equation can be represented by

From the intercepts of the semicircular arcs on the Z/ axis, Rg, Ril and Re, can be evaluated. The Re values of X3 are very high beyond the range of our instrument. The Ril values for lower voltages also could not be calculated for the same reason. The value of capacitance C can be calculated from the relation ωmax RC = 1 where ωmax = 2πfmax, where fmax is the frequency that corresponds to maximum peak of the semicircles. It is also known that the mean relaxation time (τ) can be calculated from the equation [19] ωmaxτ = 1 (Table 2).

The Ril value of the samples X1 X3 and X5 estimated from the impedance spectra at −3.5 V are 48, 15 and 5 kΩ, respectively. The τ values are calculated to be 1.7 × 10−5, 1.13 × 10−5 and 7.9 × 10−6 s, for X1, X3 and X5, respectively. The capacitance values are as follows 3.68 × 10−10, 7.58 × 10−10, 1.59 × 10−9 F. Hence, at higher voltages the relaxation time of the bulk grain varies from 10−6 to 10−8 s, while that of the interfacial layer varies from 10−5 to 10−6 s. The capacitance values for the bulk are in the range of 10−11 F while the capacitance of the interfacial layer is in the range of 10−9–10−10 F.

3.3 Dielectric permittivity

The dielectric properties of a structure can be obtained from complex permittivity defined as [26]

where ɛ/ and ɛ// are the real and imaginary parts of complex permittivity and can be expressed by the following equations.

where d, A and ε o are the thickness of HfO2 film, area of electrode and permittivity of free space (8.85 × 10−12 F/m), respectively.

Figure 4a–f illustrates the frequency dependence of the ɛ/ (real) and ɛ// (imaginary) parts of dielectric constant of all the three MOS capacitors. It is observed that the values of real part of complex permittivity (ɛ/) and imaginary part of complex permittivity (ɛ//) increases with decrease of frequency and is found to be high in the low frequency region. This can be attributed to the Maxwell–Wagner type of interface polarisation [27]. This may be due to the fact that the interfaces between HfO2 and p-Si have different conductivities; this causes an additional polarisation which boosts the dielectric constant. The high values of ɛ/ and ɛ// at low frequencies and small values at high frequencies suggests that strong dielectric relaxation occurs in the capacitors at low frequencies. This increase of ɛ/ values at low frequencies and decrease with increasing frequency is observed in many MOS systems [28, 29]. A simple way to explain this is to assume the presence of interfacial traps states. The lower the frequency, the more the interface traps can follow the alternate current variation and thus the larger the interface trap capacitance which leads to the anomalous frequency dispersion contributing to the total capacitance. The values of dielectric constant of HfO2 thin film obtained from our study are comparable with those of reported values [4]. The ɛ/ value increased with increase in biasing voltage in all the capacitors and its value is highest for the X5 capacitor. Figure 4d–f show the variation of dielectric loss (ɛ//) of the films with frequency at different voltages. It is observed that in the lower frequency region, dielectric loss is linearly decreases with the increase of frequency. The ɛ// values are highest in the capacitor X5 indicating its values increased with substrate temperature.

3.4 Dielectric loss (tan δ)

The dielectric loss (tan δ) of the thin films are calculated from the following equation

where Z/ and Z// are the real and imaginary parts of complex impedance.

Figure 5a–c shows the dielectric loss (tan δ) as a function of frequency of the Al/HfO2/p-Si MOS capacitors.

The tan δ is found to increase with frequency at different bias voltage, pass through a maximum value (tan δ) max, and thereafter decreases. As the bias voltage is increased, the frequency at which (tan δ) maximum occurred shifted to higher frequencies. This type of behaviour of tan δ has been reported by other researcher’s also [30]. It is similar to that reported by Simmons et al. [31] for thin films, having parallel resistance (R) and capacitance (C) of the materials in series with a parallel combination of Schottky barriers capacitances. The dielectric loss tangent peak in case of X1 and X5 shifted towards higher frequency with increase in the bias voltage. For X3 the peak value shift was less but the peak height decreased with increase in bias voltage. The X5 capacitor showed the highest dielectric loss among all three capacitors.

3.5 Impedance and modulus spectroscopy

Sinclair and West [15] suggested the combined use of impedance and modulus spectroscopy plots. The data regarding complex modulus can be expressed by the following equations.

\({\text{M}}^{/}\) is the real part of \({\text{M}}^{*}\) and \({\text{M}}^{//}\) is the imaginary part of \({\text{M}}^{*}\), where \({\text{M}}^{ /} = \frac{{\varepsilon^{//} }}{{ (\varepsilon^{{/^{2} }} + \varepsilon^{{//^{2} }} )}}\) and \({\text{M}}^{ / /} = \frac{{\varepsilon^{ /} }}{{ (\varepsilon^{{ /^{2} }} + \varepsilon^{{ / /^{2} }} )}}\)

The advantage of using impedance and modulus spectroscopy plots together is that Z// plots highlights the phenomena with largest resistance and M// plots picks up those with the smallest capacitance. The imaginary part of impedance Z// and modulus M// was plotted with frequency as shown in the Figs. 6a, b, 7a, b and 8a, b for different bias voltages. In an ideal Debye type relaxation the peaks in Z// and M// curves coincide and further the FWHM of these peaks should be less than 1.14 decades. Both these conditions are not satisfied by the curves of the fabricated MOS capacitors. Hence the relaxation observed is non Debye type relaxation [9]. This happens due to intrinsically dispersive nature of the thin films. The variation of Z// with frequency (f) at different voltages shows magnitude of Z// decreases with increase in frequency and bias voltage. At a low voltages (−1.5 V), a peak is observed. The peak height is least for the sample X3. The peak height for the three samples decreases with increase in bias voltage and finally they merge in the high frequency domain indicating presence of space charge polarisation at lower frequencies and its disappearance at higher frequencies. At high voltages two peaks are observed for X3 and X5 which confirms presence of two relaxation times in the system. The peaks of M// curves represents the conductivity relaxation peak. The peaks shift towards higher frequency with increase in biasing voltages revealed that the relaxation time decreases as the conductivity increases.

The conductivity relaxation time can be calculated from the relation as given below.

where τ σ is the conductivity relaxation time and \(f_{max}\) is the frequency corresponding to M// maximum.

Figure 9 shows that at a particular biasing voltage the conductivity relaxation time decreases with increase in substrate temperature.

3.6 ac conductance

The ac electrical conductivity σac of the dielectric MOS capacitors was obtained by the following equation

Figure 10a–c shows the frequency dependence of ac conductivity (σac) of X1, X3 and X5, respectively at different bias voltages. The curves show that ac conductivity is frequency independent in the lower frequency region and then increases rapidly with increase of frequency, which is representative of dc leakage current throughout the sample. The σac value also increased with increase of biasing voltage. The increase of conductivity with frequency could be due to release of trapped charges in the system. The onset (switch from frequency-independent region to frequency dependent region) varied with deposition temperature.

The variation of conductivity with angular frequency at different voltages can be investigated by applying Jonscher [32] law as given below

where B is a constant with voltage dependence σ dc is the dc conductivity, ω is the angular frequency. The term Bω n includes the ac dependence and represents all dispersion phenomena. The n value has been calculated from the linear part of σ ac versus ln ω curve at higher frequencies [9, 33]. The n values were found to vary between 0.06 and 0.708 for the film deposited at room temperatures (X1), and n values for the film deposited at 300 °C (X3) were almost equal to that of X1, however, it decreases with rise in deposition temperature to 500 °C (X5). So, it is evident the present observed ac conductivity with frequency obeys universal power law. The n values of the three capacitors increases with the increase in biasing voltage, however remains less than unity in all the cases (Table 3).

The table shows that the n value is highest in X5 in lower voltages but with increase in bias voltage the n value increase was less in X5 compared to X1 and X3.

4 Conclusions

We have fabricated MOS heterostructures with HfO2 as gate dielectric layer. Interfacial and surface roughnesses were extracted by fitting the specular X-ray reflectivity data using parrat simulation software. The frequency dependent dielectric properties and ac electrical conductivity of three Al/HfO2/p-Si (MOS) structures fabricated at different deposition temperature has been studied in detail in frequency range (5 kHz–5 MHz). The (Z/ vs. Z//) curves showed that the resistance of the interfacial layer is very high for the sample deposited at RT (X1) for all biasing voltages but in case of samples deposited at 300 and 500 °C (X3 and X5) the resistance of interfacial layer decreased and was compatible with the bulk resistance. The ɛ/ and ɛ// values were found to be very high in the low frequency region which may be attributed to the increase in mobility of the charge carrier at interface state. The tan δ curves indicated to the fact that there is possibility of existence of a Schottky barrier at the insulator semiconductor interface. Such barriers are possible if there are traps throughout the insulator band gap or insulator is auto doped during deposition process. The study of Z// and M// curves showed that the relaxation observed in the curves is non Debye type relaxation. The conductivity relaxation time decreased with increase in substrate temperature. The ac conductance increased with biasing voltage in all the capacitors. The study of variation of conductivity with angular frequency at different voltages using Jonscher law shows that the variation was least for the film obtained at deposition temperature 500 °C (X5). The dielectric constant varied between 8 and 14 for the films deposited at room temperature, 300 and 500 °C, respectively, at a frequency 50 kHz at a bias voltage of −3.5 V. An overall analysis of experimental results exhibited that the interfacial layer influences greatly the dielectric property of the fabricated (Al/HfO2/p-Si) MOS capacitors. The study revealed that the values of ɛ/ and ɛ//, tanδ, Z// and M// and σac are strongly dependent on both the applied voltage and frequency especially at depletion and accumulation regions.

References

G.D. Wilk, R.M. Wallace, J.M. Anthony, J. Appl. Phys. 89, 5243 (2001)

G. Ribes, J. Mitard, M. Denais, S. Bruyere, F. Monsieur, C. Parthasarathy, E. Vincent, G. Ghibaudo, IEEE Trans. Device Mater. Reliab. 5, 5 (2005)

M.L. Green, E.P. Gusev, R. Degraeve, E.J. Garfunkel, Appl. Phys. Rev. 90, 2057 (2001)

J. Robertson, Eur. Phys. J. Appl. Phys. 28, 265 (2004)

G. He, L. Zhu, Z. Sun, Q. Wan, L. Zhang, Prog. Mater. Sci. 56, 475 (2011)

G. He, B. Deng, Z. Sun, X. Chen, Y. Liu, L. Zhang, Crit. Rev. Solid State Mater. Sci. 38, 235 (2013)

R. M. Wallace, G. Wilk, MRS Bull. 27, 192 (2002)

E.P. Gusev Jr, C. Cabral, M. Copel, C. D’Emic, M. Gribelyuk, Microelectron. Eng. 69, 145 (2003)

D. Wei, T. Hossain, N.Y. Garces, N. Nepal, H.M. Meyer III, M.J. Jr. Kirkham, C.R. Eddy, J.H. Edgara, ECS J. Solid State Sci. Technol. 2(5), 110 (2013)

G. He, X. Chen, Z. Sun, Surf. Sci. Rep. 68, 68 (2013)

D. Wei, T. Hossain, N.Y. Garces, N. Nepal, H.M. Meyer III, M.J. Jr. Kirkham, C.R. Eddy, J.H. Edgara, ECS J. Solid State Sci. Technol. 2(5), N110 (2013)

W.C. Chin, K.Y. Cheong, J. Mater. Sci. Mater. Electron. 22, 1816 (2011)

G. He, L.D. Zhang, M. Liu, Z.Q. Sun, Appl. Phys. Lett. 97, 62908 (2010)

G. He, M. Liu, L.Q. Zhu, M. Chang, Q. Fang, L.D. Zhang, Surf. Sci. 576, 67 (2005)

J. Zhang, Z. Li, H. Zhou, C. Ye, H. Wang, Appl. Surf. Sci. 294, 58 (2014)

C.C. Lung, J.H. Horng, K.S. Chang-Liao, J.T. Jeng, H.Y. Tsai, Solid State Electron 54, 1197 (2010)

D.C. Sinclair, A.R. West, J. Appl. Phys. 66, 3850 (1989)

D.C. Sinclair, A.R. West, J. Mater. Sci. 29, 6061 (1994)

S. Saha, S.B. Krupanidhi, J. Appl. Phys. 87, 849 (2000)

L.G. Parratt, Phys. Rev. 95, 359 (1954)

N. Ortega, A. Kumar, P. Bhattacharya, S.B. Majumder, R.S. Katiyar, Phys. Rev B 77, 14111 (2008)

J.H. Lee, H. Chou, G.H. Wen, G.H. Hwang, J. Appl. Phys. 107, 23907 (2010)

G.Z. Liu, Can Wang, C.C. Wang, J. Qiu, M. He, J. Xing, K.J. Jin, H.B. Lu, Y.G. Zhen, Appl. Phys. Lett. 92, 122903 (2008)

J.C.C. Abrantes, J.A. Labrincha, J.R. Frade, Mater. Res. Bull. 35, 727 (2000)

B. Das, M.V. Reddy, G.V. Subba Rao, B.V.R. Chowdari, J. Mater. Chem. 21, 1171 (2011)

A.K. Jonscher, Dielectric Relaxation of Solids (Dielectrics Press, Chelsea, 1981)

V.V. Daniel, Dielectric Relaxation (Academic, London, 1967)

A. Tataroğlu, M. Yıldırım, H.M. Baran, Mater. Sci. Semicond. Process. 28, 89 (2014)

O. Pakma, N. Serin, S. Altindal, J. Phys. D Appl. Phys. 41, 215103 (2008)

K. Prabakar, S.K. Narayandass, D. Mangalaraj, Mater. Chem. Phys. 78, 809 (2003)

G.S. Nadkarni, J.G. Simmons, J. Appl. Phys. 47, 1 (1976)

A.K. Johnscher, Nature 267, 673 (1977)

C.K. Suman, J. Yun, S. Kim, D. Lee, C. Lee, Curr. Appl. Phys. 9, 978 (2009)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Nath, M., Roy, A. Complex impedance spectroscopy of high-k HfO2 thin films in Al/HfO2/Si capacitor for gate oxide applications. J Mater Sci: Mater Electron 26, 3506–3514 (2015). https://doi.org/10.1007/s10854-015-2862-1

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10854-015-2862-1