Abstract

Samarium oxide (Sm2O3) thin films with thicknesses in the range of 15–30 nm are deposited on n-type silicon (100) substrate via radio frequency magnetron sputtering. Effects of post-deposition annealing ambient [argon and forming gas (FG) (90% N2 + 10% H2)] and temperatures (500, 600, 700, and 800 °C) on the structural and electrical properties of deposited films are investigated and reported. X-ray diffraction revealed that all of the annealed samples possessed polycrystalline structure with C-type cubic phase. Atomic force microscope results indicated root-mean-square surface roughness of the oxide film being annealed in argon ambient are lower than that of FG annealed samples, but they are comparable at the annealing temperature of 700 °C (Argon—0.378 nm, FG—0.395 nm). High frequency capacitance–voltage measurements are carried out to determine effective oxide charge, dielectric constant and semiconductor-oxide interface trap density of the annealed oxide films. Sm2O3 thin films annealed in FG have smaller amount of effective oxide charge and semiconductor-oxide interface trap density than those oxide films annealed in argon. Current–voltage measurements are conducted to obtain barrier heights of the annealed oxide films during Fowler–Nordheim tunneling.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Due to the aggressive downscaling in silicon (Si)-based technology of metal–oxide–semiconductor (MOS) transistors, alternative high dielectric constant (κ) materials have excessively been investigated to replace the conventional SiO2-based gate dielectric films. In sub-100 nm Si-based MOS devices, thickness of SiO2 should be made thinner than 1.5 nm [1–3]. Shrinkage of the physical thickness of SiO2 films below 1.5 nm resulted in direct tunneling of charges through the dielectric films and led to large leakage current [3]. Many candidates such as Ta2O5 [4–6], TiO2 [7–9], ZrO2 [3, 10, 11], HfO2 [9, 10, 12, 13], La2O3 [14–16] and CeO2 [17–19] have been introduced as alternative dielectric material to substitute SiO2. Recently, rare earth oxides (REOs) [14–42] have emerged as promising candidates for next generation dielectrics. Of these REOs, La2O3 was reported as one of the most promising candidate that has been investigated to replace SiO2. La2O3 has the highest dielectric constant in the group of REOs [27]. However, it demonstrates the most hydroscopic property in the group [41], which may degrade electrical properties of the dielectric film. Thus, researchers have started to search for alternative REOs with similar dielectric features but less hydroscopic as a replacement. Sm2O3 is an attractive REO material to achieve the comparable dielectric properties as La2O3. κ values of the Sm2O3 thin film reported are in the range of 9–14 [21, 29, 32, 36, 40, 42], depending on the physical film thickness and deposition methods. Besides, Sm2O3 thin film has a wide band gap [31, 43], large conduction band offsets [33] and, thermodynamically stable on the underlying Si surface [34–36, 39, 40].

Previously, Sm2O3 films had been grown by different physical vapor deposition (PVD) [24, 25, 29–31, 34–36, 39, 40, 42] and chemical vapor deposition (CVD) [21, 26, 32] methods on Si. The reported chemical vapor deposited dielectric films were contained large amount of carbon due to incomplete decomposition of metal–organic precursor at low processing temperature and produced excess of carbon in the dielectric film [21]. As a result, PVD methods have an advantage compared to the CVD methods in producing a higher purity of the dielectric film. Recently, the oxide films are mostly deposited by radio frequency (RF) magnetron sputtering [34, 36, 39, 40, 42]. It is found that leakage current densities of the dielectric films deposited by this method with smaller κ values [36] are lower than the films produced by electron beam evaporation [25].

From literatures [17, 34, 36, 39, 42, 44], electrical properties of REOs dielectric films could be improved by employing post-deposition annealing (PDA). Temperature, ambient, and duration play an important role in PDA [17, 34, 36, 42, 44, 45]. It is reported that for RF-magnetron sputtered Sm2O3 films, PDA in N2 ambient showed better improvement of root-mean square (RMS) surface roughness [36] than in O2 ambient [39]. The PDA temperatures used are ranged from 600 to 800 °C [36, 39, 40, 42] as this is the range of phase transformation temperature of Sm2O3 from cubic C to monoclinic B [46]. Cubic C is the most stable phase of Sm2O3 at room temperature and it is preferably to produce the thin film in this phase [36, 40, 42, 46]. The PDA temperatures in this range was being selected in order to avoid the transformation of Sm2O3 into undesired monoclinic B phase at elevated temperature (>800 °C), and at the same time remains the optimum PDA performance of the Sm2O3 thin films [40, 42]. However, PDA of RF magnetron sputtered Sm2O3 films in argon (Ar) (inert gas) and forming gas (FG) (reducing gas) ambient within this range of temperatures have not been reported. Generally, FG annealing is employed to passivate Si dangling bonds at oxide–semiconductor interface by supplying electrons to reduce the Si cations [47]. These electrons also have been used to neutralize positive effective oxide charge existing in the film and thus, improving the negative flatband voltage shift (∆VFB) [47, 48]. In this study, physical and electrical characteristics of the Sm2O3 thin films deposited on n-type Si (100) substrate by means of RF-magnetron sputtering, followed by PDA process in Ar or FG (90% N2 + 10% H2) atmospheres at varies temperatures were investigated. The PDA temperatures are ranged from 500 to 800 with 100 °C interval. This interval is selected due to successful investigations from recent literatures for post deposition annealed Sm2O3 thin films in N2 ambient [36, 39, 40, 42].

2 Experimental procedure

Sm2O3 thin films were deposited on an n-type 3-in Si (100) substrate by RF magnetron sputtering. The substrate thickness used was in the range of 525 ± 25 μm with a resistivity of approximately 30 Ω-cm. Before the sputtering, Si substrate was cleaned by a standard Radio Corporation of America (RCA) cleaning method. 99.9% pure Sm2O3 sputtering target with a diameter of 3 in and a thickness of 0.125 in (manufactured by ACI, USA) was used as a sputtering target to deposit the Sm2O3 thin film on Si. During the sputtering process, Ar flow rate of 19.05 cm3 min−1 was used. The sputtering power was 150 W and the total pressure was 1.3 × 10−2 Torr. The sputtered samples were annealed in a horizontal tube at four different temperatures of 500, 600, 700, and 800 °C. They were held separately at each temperature for 30 min in Ar and FG (90% N2 + 10% H2) ambient. The heating rate was 10 °C min−1. After PDA, the samples were slowly cooled to room temperature in the tube with a cooling rate of approximately 5 °C/min. Thicknesses of the deposited films were in the range of 15–30 nm, measured by an ellipsometer (L 116S) that used a laser light source of 632.8 nm. Surface topography and RMS surface roughness of the annealed thin films were analyzed by a non-contact mode atomic force microscope (AFM) (Nano Navi SPI3800N). X-ray diffraction (XRD) (P8 Advan–Bruker) equipped with Cu-Kα radiation with the wavelength of 1.5406 Å operated under a voltage of 40 kV and a current of 40 mA was used to examine the phases and orientations of the oxide films on Si. The scan range was carried out from 2θ = 20°–80° with a step size and step time of 0.034208° and 71.599998s, respectively. In order to evaluate electrical characteristics of the investigated samples, MOS-capacitor test structure was fabricated. A layer of aluminium (Al) with thickness of 100 nm was coated on top of the oxide by a thermal evaporator (EMI TECH K950X). Then, an array of Al gate electrode with an area of 2.5 × 10−3 cm2 was patterned by photolithography process. Lastly, a layer of Al electrode was coated at the back of the substrate to form MOS capacitor structures. High frequency (1 MHz) capacitance–voltage (C–V) characteristics of the MOS capacitors were measured by a LCR meter (Agilent 4284) with an applied dc voltage of 24 mV and current–voltage (I–V) measurements were conducted by a semiconductor parameter analyzer (Agilent 4156C).

3 Results and discussion

3.1 Structural properties

Figure 1 shows the XRD pattern of as deposited Sm2O3 thin film on Si substrate with the scanning range of 2θ = 20°–80°. The strong peak detected at 2θ = 69.18° is consistent with the International Conference for Diffraction Data (ICDD) file no. 01-089-2749, which is corresponded to cubic Si with (400) plane and is paralleled to the Si (100) plane. Intensity of the Si (400) peak is extremely higher than the oxide diffraction peaks. In order to analyze the plane orientation of annealed oxide films, Fig. 1 has been zoomed into the range of 2θ in where the oxide peaks existed (2θ = 20°–60°).

Figure 2 shows the refined XRD patterns of Sm2O3 thin films annealed at various temperatures (500, 600, 700, and 800 °C) in Ar and FG atmospheres. All of the investigated samples are polycrystalline in nature. Four diffraction peaks are detected at 2θ = 32.8°, 47.9°, 54.5°, and 56.2°, which corresponded to Sm2O3 (400), (433), (541), and (622) planes, respectively. These diffraction peaks are well matched with the ICDD files no. 00-042-1461, which is denoted as C-type cubic phase of Sm2O3. The (400) peak has a stronger intensity than the other minor peaks and it is detected as a preferred oriented plane for all investigated samples. This suggests a preferential growth of the crystallites with the (400) plane of cubic Sm2O3 parallel to the Si (100) substrate. Previously, Pan et al. [36, 40] also had reported the same diffraction peaks in their investigation of RF-magnetron sputtered Sm2O3 on p-type Si (100) substrate annealed at 600, 700, and 800 °C. In our work, all of the diffraction peaks of samples being annealed in Ar ambient are growing stronger as the annealing temperatures is increased from 500 to 700 °C and dropped slightly at the annealing temperature of 800 °C. Increase of the intensities of diffraction peaks is attributed to the crystallization of Sm2O3 at elevated temperatures [49]. For FG annealed samples, no significant changes in the intensities of the diffraction peaks are observed as increased the annealing temperatures. This suggests FG annealing suppressed the crystallization of Sm2O3 thin films at high annealing temperatures.

Three-dimensional surface topographies of Ar and FG annealed Sm2O3 dielectric films were characterized by AFM with scanning area of 1 μm × 1 μm (Figs. 3, 4). Triangular-like protrusions are observed on the surface of all annealed oxide films. For Ar annealed oxide films, coarser protrusions are observed at annealing temperature of 500 °C and they are aligned in random orientations. As the annealing temperature is increased from 500 to 800 °C, they are getting finer in shape and their alignments have improved significantly. However, blunter shapes of protrusions are revealed in the FG annealed samples. They are randomly oriented throughout all of the annealing temperatures. The finest protrusions are observed for the samples annealed at 700 °C.

Typical two-dimensional sketch of the protrusion is illustrated in Fig. 5. The average peak-valley (P–V) length and average horizontal width were determined from 20 protrusions for each specific annealing ambient and temperatures. Relationships of these two parameters as a function of annealing temperatures for two different annealing ambient are plotted in error bars to show the maximum, mean and minimum values as shown in Fig. 6. Ar annealed samples behaved differently when compared with the FG annealed samples throughout the investigated annealing temperature range. As the annealing temperature increases from 500 °C to 600 °C, the protrusions grown in both horizontal and vertical directions for Ar annealed samples. These two parameters are reduced when further annealed the samples to 700 and 800 °C. As differ from Ar annealing atmosphere, reduction of the average P–V length and average horizontal width for FG annealed samples are observed from the annealing temperatures of 500 to 700 °C and increased slightly at 800 °C.

Figure 7 compares the RMS surface roughness of Sm2O3 films at various annealing temperatures in Ar and FG atmospheres. Five different points were taken in a particular sample from each PDA temperature to test for surface roughness and presented in error bars. Maximum, mean and minimum RMS roughness of each tested sample is shown in the error bars. The overall RMS roughness of Ar annealed thin films is smaller than the FG annealed thin films, but they showed a comparable value at the annealing temperature of 700 °C (Ar—0.378 nm, FG—0.395 nm). Both, the Ar and FG annealed samples, demonstrated different trends throughout the annealing temperatures, but they are in an agreement with the trend of average P–V length and average horizontal width measurements as presented in the earlier section. RMS surface roughness of the Ar annealed samples is increased as increasing the annealing temperatures to 600 °C, and it started to reduce when annealed at 700 and 800 °C. The increment of RMS surface roughness upon PDA is due to crystallization or grain growth mechanism of the oxide films during annealing [50]. For FG annealed samples, RMS surface roughness decreased as the annealing temperature is increased to 700 °C and roughened after annealed at 800 °C. Reduction of RMS surface roughness is attributed to the densification of the dielectric films upon PDA [49]. The trend of RMS surface roughness variation as a function of annealing temperature for FG annealed samples is consistent to the investigation reported by Pan et al. [36].

3.2 Electrical properties

Three samples from each specific PDA temperatures were tested electrically under LCR meter for C–V measurement. Figure 8 shows the typical average normalized capacitance (C/Co) versus gate voltage curves of three Al/Sm2O3/Si MOS capacitors annealed at each specific temperatures in Ar and FG atmospheres, where Co is the capacitance at Vg = 0 V. The gate bias was applied in a forward direction and swept from −4 to 2 V. No constant saturation at the accumulation is observed for 500 °C annealed sample in Ar ambient. This is due to the relatively high amount of trap charges in oxide film [17]. From high-frequency C–V curve, accumulation capacitances are extracted and they are used to determine κ values of oxide films based on the following equation [17]:

where Cox is oxide capacitance obtained from C–V curve, tox is gate oxide thickness, ε0 is permittivity of free space, and Aox is gate area.

Figure 9 displays the average κ values (maximum, mean and minimum) of Sm2O3 dielectric films annealed at different temperatures in Ar and FG ambient. The average κ values obtained for samples annealed in Ar ambient (6.6–9.5) and FG ambient (5.4–7.2) are comparable to the results reported by Pan et al. [36]. It is observed that κ values of Ar annealed samples are decreased upon increasing the annealing temperatures, whereas the FG annealed samples show an opposite observation throughout the annealing temperatures, except for 800 °C. Reduction of average κ values of the samples annealed in Ar ambient may due to the growth of lower κ interfacial layer sandwiched between the Sm2O3 dielectric film and Si substrate during PDA [50], in which it reduces the total capacitance of MOS capacitor. Amount of the total capacitance (CTotal) of a capacitor containing interfacial layer is modeled by a series of capacitances as shown in (2) [17]

where C1 is the oxide film capacitance and, C2 is the interfacial layer capacitance that proportional to its physical thickness. Thus, as the interfacial layer grows thicker at higher annealing temperature, the total capacitance of MOS capacitor will be reduced. However, increase of the κ value for FG annealed samples is due to densification of the Sm2O3 dielectric films upon PDA [49]. This justification is supported by the results of RMS surface roughness shown in the earlier section in which denser oxide films possessed smoother surface.

All of the investigated samples showed a negative shift of ∆VFB as presented in Fig. 10. This indicates the presence of positive effective oxide charges (Qeff) accumulated in the oxide films during PDA [17, 45, 50]. Qeff is calculated based on Eq. 3 [17].

where Cox is the oxide capacitance and q is the electronic charge. Figure 11 compares the Qeff determined from three investigated Sm2O3 dielectric films at each PDA temperatures in Ar and FG atmospheres, and they are presented in error bars. The overall ∆VFB and Qeff of FG annealed samples are smaller than Ar annealed samples. FG is a reducing gas and it tends to decompose to produce electrons at elevated temperatures [47]. During PDA, excess of electrons were supplied by the FG to neutralize the existing positive oxide charges in oxide films and thus, improving the ∆VFB of the samples.

Another important parameter that can be extracted from the C–V measurement is interface trap density (Dit) (Fig. 12). Dit was determined by using Terman method (Eq. 4) [17].

where ∆Vg is the difference of gate voltage in experiment and gate voltage of ideal curve and Φs is the surface potential of Si at a specific gate voltage.

The calculated amounts of Dit of FG annealed samples are smaller than the Ar annealed samples. For the samples being annealed in Ar ambient, the highest and the lowest Dit values are recorded at the annealing temperatures of 600 and 800 °C, respectively. Dit is influenced by the surface roughness of dielectric films. A rougher thin film surface contributed to a higher Dit as the charges are being trapped easily and vice versa [50]. The same justification is applied to the FG annealed samples. The variations of Dit and surface roughness as a function of annealing temperatures are demonstrated the same trend. The lowest Dit obtained in this study (Ar annealing: ~3.8 × 1012 eV−1 cm−2 and FG annealing: ~1.1 × 1012 eV−1 cm−2) is lower than the results reported by Jeon et al. (~2.0 × 1013 eV−1 cm−2) at the surface potential of −0.1 eV [25].

Figure 13 displays the average total interface trap density (DTotal) of the Sm2O3 thin films annealed in Ar and FG ambient at various temperatures. DTotal was calculated from the area under the curve of Dit versus (Ec–E) [17]. The numbers of total interface trap density of FG annealed samples are lower than the Ar annealed samples. The lowest DTotal obtained in this work are shown by the sample annealed at 700 °C in FG ambient (3.9626 × 1011 cm−2).

As the same with C–V measurement, three samples from each specific PDA temperatures were tested with SPA to examine the I–V behavior. The average current density versus breakdown field characteristics of the Al/Sm2O3/Si MOS capacitors at different annealing temperatures in Ar and FG atmospheres are illustrated in Fig. 14. The capacitor with dielectric films annealed in both different ambient showed an increasing trend of the average breakdown field as a function of annealing temperatures, except for the 800 °C annealed samples in FG ambient (Fig. 15). In overall, electric breakdown fields of all samples annealed in FG ambient are higher than the Ar ambient. The highest dielectric breakdown field (~6.76 MV cm−1) is attained by the samples annealed at 700 °C in FG ambient as it has the lowest Qeff, Dit, and DTotal when compared to the other samples [17, 45, 50].

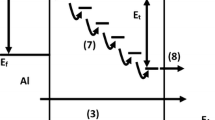

In order to compute the barrier height (ΦB) between conduction band edge of Sm2O3 film and of Si, Fowler–Nordheim (FN) tunneling model (Eq. 5) [17, 51] is employed. FN tunneling is a tunneling process whereby the electron passes through a triangular potential barrier into the conduction band of the oxide film [51].

where

and

where me is the free electron mass, m is the effective electron mass in the oxide and h is Planck’s constant. The effective electron mass of 0.13 me was used as it had been determined previously for the Sm2O3 film on Si [34]. By plotting ln (J/E2) vs 1/E (FN plot) (Fig. 16), ΦB could be extracted from the slope (B) of the linear region of the graph.

In this study, all of the 500 °C annealed samples (both in Ar and FG ambient) did not show FN tunneling behavior as their electric breakdown field occurred before FN tunneling [17]. Figure 17 presents the relationship of average ΦB of Sm2O3 dielectric films annealed at various temperatures in Ar and FG ambient. The overall ΦB of FG annealed dielectric films is higher than the Ar annealed samples. As increasing the annealing temperatures, ΦB of all investigated samples are increased, except for samples annealed at 800 °C in FG ambient. The highest ΦB is attained by 700 °C annealed sample in FG ambient (1.03 eV), which is higher than the values reported by Dahkel (0.85 eV) [31] and Ingram et al. (0.82 eV) [34]. ΦB plays an important role to the leakage current density of dielectric films [31]. As increased the ΦB, probability of the charges (electrons) passes through the oxide film will be reduced and therefore, contributes to a lower leakage current density.

4 Conclusions

Sm2O3 thin films were deposited on n-type Si (100) substrate via RF-magnetron sputtering. PDA was carried out separately on the deposited thin films in Ar and FG (90% N2 + 10% H2) ambient at different temperatures (500, 600, 700, and 800 °C) for 30 min. X-ray diffraction revealed that all the annealed samples possessed polycrystalline structure with C-type cubic phase. FG annealing ambient had suppressed crystallization of the oxide films upon PDA. Atomic force microscope results indicated RMS surface roughness of the samples being annealed in Ar ambient were lower than FG annealed samples, but they were comparable at the annealing temperature of 700 °C (Ar—0.378 nm, FG—0.395 nm). For electrical characterization, FG annealing had successfully improved the ∆VFB of MOS capacitor by supplying excess to electrons to neutralize the existing positive oxide charges in oxide film. Besides, the Sm2O3 thin films annealed in FG ambient showed smaller number of Qeff, Dit, and DTotal than the oxide films annealed in Ar ambient. The highest dielectric breakdown field (~6.76 MV cm−1) was attained by the samples annealed at 700 °C in FG ambient as it has the lowest Qeff, Dit, and DTotal.

References

G.D. Wilk, R.M. Wallace, J.M. Anthony, J. Appl. Phys. 89, 5243–5275 (2001)

M. Leskel, M. Ritala, J. Solid State Chem. 171, 170–174 (2003)

Y.H. Wong, K.Y. Cheong, J. Mater. Sci. Mater. Electron. 21, 980–993 (2010)

S.V.J. Chandra, S. Uthanna, G.M. Rao, Appl. Surf. Sci. 254, 1953–1960 (2008)

P. Pipinys, A. Rimeika, Central Eur. J. Phys. 6, 792–796 (2008)

C.-H. Kao, H. Chen, J.S. Chiu, K.S. Chen, Y.T. Pan, Appl. Phys. Lett. 96, 112901–112903 (2010)

H. Altuntas, A. Bengi, U. Aydemir, T. Asar, S.S. Cetin, I. Kars, S. Altindal, S. Ozcelik, Mater. Sci. Semicond. Process. 12, 224–232 (2009)

I. Ben Mbarek, F. Chaabouni, M. Selmi, M. Abaab, B. Rezig, Physica Status Solidi 7, 2311–2315 (2010)

T. Qian, G. Jursich, C. Takoudis, in Advanced Semiconductor Manufacturing Conference, IEEE/SEMI, pp. 17–22 (2010)

A.S. Zoolfakar, H. Hashim, in IEEE International Conference on Semiconductor Electronics, pp. 445–449 (2008)

T. Kurniawan, K.Y. Cheong, K. Razak, Z. Lockman, N. Ahmad, J. Mater. Sci. Mater. Electron. 22, 143–150 (2010)

X. Zhang, H. Tu, X. Wang, Y. Xiong, M. Yang, L. Wang, J. Du, J. Cryst. Growth 312, 2928–2930 (2010)

S. Tan, J. Elec. Mater. 39, 2435–2440 (2010)

S.J. Jo, J.S. Ha, N.K. Park, D.K. Kang, B.-H. Kim, Thin Solid Films 513, 253–257 (2006)

W.-H. Kim, W.J. Maeng, K.-J. Moon, J.-M. Myoung, H. Kim, Thin Solid Films 519, 362–366 (2010)

C. Yang, H. Fan, S. Qiu, Y. Xi, Y. Fu, J. Non Cryst. Solids 355, 33–37 (2009)

H.J. Quah, K.Y. Cheong, Z. Hassan, Z. Lockman, F.A. Jasni, W.F. Lim, J. Electrochem. Soc. 157, H6–H12 (2010)

K. Shubhakar, K.L. Pey, S.S. Kushvaha, S.J. O’Shea, M. Bosman, M. Kouda, K. Kakushima, H. Iwai, in 17th IEEE International Symposium on the Physical and Failure Analysis of Integrated Circuits, pp. 1–5 (2010)

C. Fu-Chien, Electron Dev. IEEE Trans. 57, 2719–2725 (2010)

W.C. Chin, K.Y. Cheong, Z. Hassan, Mater. Sci. Semicond. Process. (2010, in press)

J. Paivasaari, M. Putkonen, L. Niinist, Thin Solid Films 472, 275–281 (2005)

J. Päiväsaari, J. Niinistö, P. Myllymäki, C. Dezelah, C. Winter, M. Putkonen, M. Nieminen, L. Niinistö, Atomic Layer Deposition of Rare Earth Oxides, in Rare Earth Oxide Thin Films (2007), pp. 15–32

H.J. Osten, A. Laha, M. Czernohorsky, E. Bugiel, R. Dargis, A. Fissel, Physica Status Solidi A 205, 695–707 (2008)

V.A. Rozhkov, A.Y. Trusova, I.G. Berezhnoy, Thin Solid Films 325, 151–155 (1998)

J. Sanghun, I. Kiju, Y. Hyundoek, L. Hyelan, S. Hyunjun, C. Sangmu, J. Taesung, H. Hyunsang, in IEDM Technical Digest, pp. 20.6.1–20.6.4 (2001)

H. Ono, T. Katsumata, Appl. Phys. Lett. 78, 1832 (2001)

H. Iwai, S. Ohmi, S. Akama, C. Ohshima, A. Kikuchi, I. Kashiwagi, J. Taguchi, H. Yamamoto, J. Tonotani, Y. Kim, I. Ueda, A. Kuriyama, Y. Yoshihara, in IEDM '02. Digest, pp. 625–628 (2002)

S. Jeon, H. Hwang, J. Appl. Phys. 93, 6393 (2003)

D. Yang, L.J. Xue, R.A.B. Devine, J. Appl. Phys. 93, 9389 (2003)

D.F. Yang, L.J. Xue, Mat. Res. Soc. Symp. Proc. 780, Y1.3.1–Y1.3.6 (2003)

A.A. Dakhel, J. Alloys Compounds 365, 233–239 (2004)

K. Shalini, S. Shivashankar, Bull. Mater. Sci. 28, 49–54 (2005)

O. Engstrom, B. Raeissi, S. Hall, O. Buiu, M.C. Lemme, H.D.B. Gottlob, P.K. Hurley, K. Cherkaoui, Solid State Electron. 51, 622–626 (2007)

I.Y.-K. Chang, Y.-R. Hwang, P.-C. Juan, J.Y.-M. Lee, J. Electrochem. Soc. 155, G265–G268 (2008)

Y.-R. Hwang, I.Y.-K. Chang, M.-T. Wang, J.Y.-M. Lee, Integ. Ferroelect. Int. J. 97, 111–120 (2008)

T.-M. Pan, C.-C. Huang, S.-X. You, C.-C. Yeh, Electrochem. Solid State Lett. 11, G62–G65 (2008)

A.D. Stewart, A. Gerger, B.P. Gila, C.R. Abernathy, S.J. Pearton, Appl. Phys. Lett. 92, 153511 (2008)

H. Yang, H. Wang, H.M. Luo, D.M. Feldmann, P.C. Dowden, R.F. DePaula, Q.X. Jia, Appl. Phys. Lett. 92, 062905 (2008)

M.-H. Wu, C.-H. Cheng, C.-S. Lai, T.-M. Pan, Sens. Actuat. B Chem. 138, 221–227 (2009)

T.-M. Pan, C.-C. Huang, Appl. Surf. Sci. 256, 7186–7193 (2010)

M. Leskela, K. Kukli, M. Ritala, J. Alloys Compounds 418, 27–34 (2006)

C.H. Kao, H. Chen, S.P. Lin, Electrochem. Solid State Lett. 14, G9–G12 (2011)

S. Ohmi, S. Akama, A. Kikuchi, I. Kashiwagi, C. Ohshima, J. Taguchi, H. Yamamoto, C. Kobayashi, K. Sato, A. Takeda, K. Oshima, H. Ishiwara, H. Iwai, 200–204 (2001)

T.-M. Pan, L.-C. Yen, Appl. Surf. Sci. 256, 2786–2791 (2010)

H.J. Quah, K.Y. Cheong, Z. Hassan, Z. Lockman, J. Mater. Sci. Mater. Electron. (2010). doi:10.1007/s10854-010-0181-0

G.-Y. Adachi, N. Imanaka, Chem. Rev. 98, 1479–1514 (1998)

C.H. Ling, J. Bhaskaran, W.K. Choi, L.K. Ah, J. Appl. Phys. 77, 6350–6353 (1995)

J. Kwo, M. Hong, J.P. Mannaerts, Y.D. Wu, Q.Y. Lee, B. Yang, T. Gustafsson, Mater. Res. Soc. Symp. Proc. 811, E1.12.1–E1.12.6 (2004)

T.-M. Pan, J.-D. Lee, J. Elec. Mater. 36, 1395–1403 (2007)

W.F. Lim, K.Y. Cheong, Z. Lockman, Appl. Phys. A Mater. Sci. Process. (2010). doi:10.1007/s00339-010-6039-8

K.Y. Cheong, J.H. Moon, H.J. Kim, W. Bahng, N.-K. Kim, J. Appl. Phys. 103, 084113 (2008)

Acknowledgments

One of the authors (W.C.C.) would like to acknowledge the financial supports from Universiti Sains Malaysia—Research University grant (no. 8032036) and Universiti Sains Malaysia fellowship.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Chin, W.C., Cheong, K.Y. Effects of post-deposition annealing temperature and ambient on RF magnetron sputtered Sm2O3 gate on n-type silicon substrate. J Mater Sci: Mater Electron 22, 1816–1826 (2011). https://doi.org/10.1007/s10854-011-0368-z

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10854-011-0368-z