Abstract

The aim of this study is to reduce the oxide and interface-trap charges and also improve the stability at the oxide–semiconductor interface by growing a SiO2 interface layer on a Si wafer then depositing Al2O3 thin film. Effective oxide charges density (Nox), border trap charges density (Nbt), interface states density (Nit), diffusion potential (VD), donor concentration (ND), and barrier height \({(\varPhi }_{\mathrm{B}})\) were calculated using the capacitance–voltage (C–V) and conductance–voltage (G/ω–V) measurements at different annealing temperatures. The flat-band voltage (Vfb) changed with annealing temperature and the Vfb value for the 450 °C annealed sample was closest to the ideal Vfb. The sample also possessed a high dielectric constant. For these reasons, C–V and G/w–V values of this sample at different frequencies were obtained. Compared to previous studies, very low Nbtvalues (~ 109 eV−1 cm−2), low Nit values (~ 1010 eV−1 cm−2) and high \({\varPhi }_{\mathrm{B}}\) values for the annealed samples were obtained due to the SiO2 interface layer.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

The metal–oxide–semiconductor (MOS) capacitors have been the foundation for microelectronic and optoelectronic devices since the 1960s [1]. The oxide plays a major role in charge and energy storage due to its significant dielectric constant (k). This has made the MOS capacitor be used in MOS-based technology such as new-generation biosensors, radiation sensors, and charged-coupled devices [2, 3]. The oxide properties together with its stability on semiconductor materials affect the electrical characteristics of the entire MOS structure. These electrical characteristics determine the applicability of the structure in different technologies [4] and are usually investigated by taking capacitance–voltage (C–V) and conductance–voltage (G/ω–V) measurements. The conductance (G/w) measurement is based on the exchange of majority charge carriers between the majority charge carrier band of silicon and the interface states. This exchange results in conductance losses [4].

Initially, SiO2 was solely used as the oxide in MOS capacitors because of its good electrical and material properties such as excellent insulation and interfacial bonding especially with Si [5, 6]. However, later on, researchers suggested a need to replace SiO2 since it was associated with high current leakage especially for thicknesses less than 2 nm [7]. Another reason for the replacement was that SiO2 led to the poor performance of devices functioning at high temperatures or high electric fields. The investigated alternatives included high-k materials such as Al2O3, HfO2, and Sm2O3 [5]. The deposition of these high-k materials directly on Si results in the formation of uncontrollable silicate or oxide layers in the high-k/Si interface which causes a decline in the effective dielectric constant, device performance, and channel mobility. Therefore, since SiO2 is highly stable with Si, researchers suggested growing a SiO2 layer on Si then depositing a high-k dielectric on it to reduce the lattice mismatch at the high-k/Si interface [8,9,10,11].

Previously, a study [12] on the Al/Al2O3/Si MOS capacitor was done at our laboratory. Interface-trapped charges density, effective oxide charge density, series resistance, and flat-band shifts were the main electrical parameters analyzed. These electrical parameters were obtained by the aid of C–V and G/ω–V) measurements for samples annealed at different temperatures. However, some electrical parameters were unsatisfactory which indicated that the quality of the fabricated Al/Al2O3/Si MOS capacitor needs improvement. For example, we obtained big flat-band shifts, high series resistance (Rs) values, and the flat-band voltages were not close to the ideal one.

Here, we focus on improving the quality of the MOS capacitor by introducing a SiO2 layer in between the Al2O3/Si interface and also investigating the effects of SiO2 on the electrical characteristics of the newly fabricated Al/Al2O3/SiO2/n-Si MOS capacitor. In order to investigate the electrical characteristics, we take C–V and G/ω–V measurements at different frequencies for Al/Al2O3/SiO2/n-Si MOS samples annealed at different temperatures. The effect of the SiO2 layer is thoroughly analyzed by using the obtained electrical parameters including the barrier height which is a good parameter in determining electron injection or current leakage.

2 Experiments

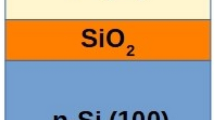

An n-type (100) wafer with thickness of 500 μm and resistivity of 2–4 Ω cm was dried using nitrogen just after undergoing the standard RCA (Radio Corporation of America) cleaning process [13]. SiO2 films were then grown on the Si wafer by dry oxidation in the diffusion furnace at 1000 °C; afterwards, the Al2O3 thin film (of purity 99.99%) was deposited on the wafer by electron beam (E-beam) evaporator for 10 min, at substrate temperature of 200 °C and starting base pressure of 4.8 × 10−4 Pa. The thicknesses of SiO2 and Al2O3 films measured by Angstrom Sun Spectroscopic reflectometer were 20 nm and 140 nm, respectively. The wafer was then divided into 4 samples; 1 was left as-deposited; 3 were annealed separately at temperatures of 250 °C, 450 °C, and 750 °C in an N2 ambient for 30 min with each sample annealed at 1 temperature value. A shadow mask with circular dots of diameter 1.5 mm was placed on the Al2O3/SiO2/n-Si samples, and the front aluminum contacts were deposited at 200 W by RF magnetron sputtering. The whole back contact was deposited without the shadow mask. The entire fabrication process was performed in the Class-100 clean-room laboratories in Centre for Nuclear Radiation Detector Applications and Research Center, Bolu Abant Izzet Baysal University. DC electrodes were connected to the HIOKI 3250 LCR meter from which the C–V and G/ω–V measurements of the MOS capacitors were obtained. This was done in the voltage range of − 10 V to 10 V and in the frequency range of 100 kHz to 1 MHz. In order to eliminate the series resistance (Rs) from the obtained measurements, corrections were done on both capacitance and conductance values. The first step in correction was to obtain Rs values from Eq. 1 using the measured conductance (Gm) and capacitance (Cm) values in strong accumulation [13]

where w is the angular frequency. Then, by using the Rs values we obtained the corrected capacitance (Cc) and conductance (Gc/w) as shown in Eqs. 2 and 3 [14, 15].

where \(a=\left({G}_{\mathrm{m}}\right)- \left[{\left({G}_{\mathrm{m}}\right)}^{2}+{\left(w{G}_{\mathrm{m}}\right)}^{2}\right]\)Rs.

The border trap charges density (Nbt) is used to estimate the oxide quality and it was calculated from Eq. 4 [16, 17].

where \({\Delta V}_{\mathrm{f}\mathrm{b},\mathrm{h}\mathrm{y}\mathrm{s}}\) is the flat-band voltage shift obtained from the forward–backward C–V hysteresis. Its values at different annealing temperatures are shown in Table 1. The oxide trap charges density (Nox) was calculated from Eq. 5 [18, 19].

where q is the charge of an electron, A is the area of the capacitor plate (front contact), and Cox is the effective capacitance of the oxides. The values of Cox were obtained from the strong accumulation region in the C–V curve.

The interface-trap charges density (Nit) values were calculated from Eq. 6 [4, 20, 21].

where Gc,max/w is the peak value of the corrected conductance and Cc is the corresponding corrected capacitance to Gc,max/w.

The built-in voltage or diffusion potential (VD), the energy difference between the bulk Fermi level and conduction band edge (EF), and barrier height (\(\varPhi\)B) were attained by the aid of the linear regions of the 1/C2–V graph that will be explained in the Results and discussion section. Best fits for the linear regions were done using OriginLab program from which the slopes and the intercepts were obtained. The relation between Cc and V is given in Eqs. 7 and 8 [4, 15, 22].

where \({\varepsilon }_{\mathrm{s}}\) is the dielectric constant of the semiconductor, \({\varepsilon }_{0}\) is the permittivity of free space, A is the front contact area of the capacitor, V is the applied bias, ND is the donor concentration, and V0 is where the lines intercept with the voltage axis is given in Eq. 9 [23, 24].

where T is the room temperature and kBis the Boltzmann constant. Equation 10 was used to obtain the barrier height (\({\varPhi }_{\mathrm{B}}\)) [22]

where EF is the energy difference between the bulk Fermi level and conduction band and is obtained from Eq. 11.

Ncis the effective density of traps in Si conduction band given by Eq. 12 [22].

m0 is the rest mass of the electron, \({m}_{\mathrm{e}}^{*}=0.55{m}_{0}\) is the effective mass of the electron, and h is the Planck’s constant. The image barrier lowering is ∆\(\varPhi\)Band was calculated from Eq. 13 [4].

Em is the maximum electric field and was calculated from Eq. 14 [4].

The values of VD, EF, ND, \(\Delta {\varPhi }_{\mathrm{B}}\), and \({\varPhi }_{\mathrm{B}}\) are listed in Table 1.

The effective capacitance for low frequencies (CLF) is obtained from Eq. 15 [25].

where w (\(w=2\pi f\)) is the angular frequency, Citis the excess capacitance due to interface traps, Cscis the capacitance in the semiconductor, and \(\tau\) is the life-time of the interface traps and is equal to CitRs. The effective capacitance for high frequencies (CHF) is obtained from Eq. 16 [26, 27]. As shown in Fig. 1Cit disappears in a high frequency limit.

3 Results and discussion

C–V measurements reveal reliable information about the oxide layer and the oxide–semiconductor interface in the MOS structure [25]. With the deposition of Al contact on the front and backside, the MOS structure is complete and these measurements can be done. Apart from the metal–semiconductor work difference (\({\varPhi }_{\mathrm{m}\mathrm{s}}\)), the MOS capacitor is affected by electrical charges in the oxide and traps at the interface. These charges are distributed as shown in Fig. 2: surface charges (QS) depend on the band bending due to applied bias and doping; interface-trapped charges (Qit) are charges that fill the empty traps at the interface [20, 25], the filling and emptying of traps enables the measurement of interface state density (Nit) using the C–V and G/ω–V measurements as will be discussed later; mobile ionic charges are the metal ions that escape into the oxide at high bias and at high temperatures; oxide-trapped charges are charges captured by the traps located inside the oxide layers, these traps can be eliminated by low-temperature annealing; fixed oxide charges are well established within the oxide layers about 3 nm from the oxide–semiconductor interface and cannot be eliminated or reduced even when large potentials are applied [20, 25, 28]. The effective oxide charge (Qeff) is the sum of Qf, Qot, and Qm[28].

The C–V and G/ω–V curves obtained from the Al/Al2O3/SiO2/n-Si MOS capacitors annealed at temperatures 250 °C, 450 °C and 750 °C for high frequency (1 MHz) are shown in Fig. 3a, b. The distortions and shifts in the C–V and G/ω–V stem from the interface states, border traps, dielectric constant of the interfacial layer, and series resistance (Rs) which occurs between the contacts and the substrate. Therefore much attention should be paid to these parameters in order to improve the performance of microelectronic and optoelectronic devices [28].

The oxidation of Si leads to growth of an oxide that has very few fixed oxide charges and less than 1010 interface states eV−1 cm−2. A significant amount of such interface states (especially those that are as a result of Si dangling bonds) are passivated by annealing at temperatures around 400 °C. Passivation does not ultimately eliminate the interfacial defects as they can emerge again after ionizing irradiation or energetic electron injection occurs across the SiO2/Si interface [29]. As shown in Table 1, the effective oxide trap density (Nox) and interface traps density (Nit) decreased for samples annealed at temperatures 250 °C and 450 °C. The sample annealed at 450 °C is seen to even possess the lowest border trap density (0.44 × 1010 cm−2). A low trap density signifies low electron injection or current leakage which is a significant problem in MOS field effect transistors. At high annealing temperature in an inert ambient both electron and hole traps are generated. It also results in the generation of a low field self-healing breakdown [29]. Hickmott [29] improved the speculation that a decrease of SiO2 at the SiO2/Si interface may occur due to the reaction:

where the SiO is a volatile gas presumed to move away from the interface leaving behind a deficiency in oxygen. Evidence given by a number of papers showed that SiO can diffuse through the oxide network and the activation energy required for the process is in the range of 4.2–4.4 eV. This value is close to 4.7 eV, which is the estimated value for O to diffuse through the oxide [29]. So, the oxygen deficiency defects due to the Si–O destruction [29, 30] at high temperatures (700–1060 °C) cause a reduction in the quality of the dielectric layer which drastically decreases the charge storing capability. This is the reason why the sample annealed at 750 °C had a very low accumulation region capacitance as observed in Fig. 3c. Unlike the Gc/w curves in Fig. 3d, a negligible change is observed between the C–V and Cc–V curves in Fig. 3a and c, respectively, this indicates that the effect of series resistance on capacitance is negligibly small. However, a kink is observed in the Cc–V curve of the as-deposited sample at the depletion-inversion region, this kink is as a result of the electrically active defects at the oxide–semiconductor interface and it fades as the annealing temperature increases [9]. There are shifts in the Cc–V curve for different annealing temperatures both in the accumulation region and the mid-gap. In an earlier study on the Al/Al2O3/Si MOS capacitor [12], it was proved that post-deposition annealing reduces the oxide traps that are as a result of nonstoichiometric and weak bonds that form after growth of the thin films. These traps are the major reason for the flat-band voltage (Vfb) shifts. In this study, the SiO2 layer led to the formation of stronger bonds because it is highly stable with silicon and as a result the border traps decreased. The border trap charges density (Nbt) for the as-deposited MOS capacitor is 3.11 × 1010 cm−2 which is about 10 times lower than that (7.47 × 1011 cm−2) in the previous study [12].

In Fig. 3a, it is observed that annealing at 250 °C caused the flat-band voltage (Vfb) to shift to the right. Again, for 450 °C, the Vfb extended farther to the right, closer to the ideal Vfb (− 0.27 V). These shifts were as a result of the decrease in the effective oxide charge density (Nox) which comprises of border trap density (Nbt) as shown in Table 1. An increase in annealing temperature leads to the formation of bonds; hence, the trap densities are reduced; the nitrogen used in the annealing process may also reduce these traps when the dangling bonds are chemically active [31,32,33]. At 750 °C, the Vfbshifted to the left because the bonds become weak or broken at very high temperatures leaving more traps in the oxides and at the Al2O3/SiO2 and SiO2/Si interfaces. The as-deposited sample had the highest capacitance in the accumulation region, this may be due to the interface traps that form layers in the SiO2/n-Si and Al2O3/SiO2 surface which cause an extra capacitance (Cit) that increases the effective capacitance. Annealing improves the surfaces by eliminating or reducing the interface traps density (Nit), this is why at 250 °C a significant decrease in the capacitance occurred in the accumulation region [8]. For the 450 °C annealed sample, an improvement of the dielectric constant occurred since farther annealing enables atoms to settle in their lattices [32], this sample had the lowest flat-band shift as shown in Fig. 4 and Table 1. This is the reason why its border trap density was the lowest compared to the other samples. At high annealing temperatures possible parasitic SiOx/AlSiOx layers are formed, these layers degrade the effective dielectric constant and increase the total thickness of the oxides which results into a huge decline in the capacitance [12]. This explains why the accumulation region capacitance at 750 °C was very low compared to others.

The conductance is essential in investigating the interface quality of MOS structure, conductance is a result of interactions between interface traps and majority carrier densities in the Si [12]. Interface-trap density (Nit) is calculated by using either the conductance method [34] or the high-low frequency capacitance method [25]. In this study, the conductance method by Goetzberger and Nicollian [15] was used since measurements were taken for only one frequency (1 MHz). According to Fig. 3d, the peaks of the corrected conductance curves are highest for the as-deposited sample, this is because it had the highest interface-trap density (Nit) value, and the lowest was with the sample annealed at 750 °C as shown in Table 1. We noticed that after annealing, the Nit values decreased from ~ 1011 to ~ 1010 eV−1 cm−2. These Nitvalues of the annealed samples in this study (double gate oxide layer Al2O3/SiO2 MOS capacitor) are 10 times lower than those in the previous study (single oxide layer Al2O3 MOS capacitor) [12]; therefore, the stronger bond between SiO2 and Si results in a decrease in the traps as the atoms settle in their lattices after annealing.

In Fig. 5b there is an intersection of the lines because of the capacitance variations in the depletion region. The Nit values in Table 1 only represent the total density of both the donor and acceptor interface traps. This means that these values cannot be used to determine the polarity of the interface traps separately. On the other hand, the barrier height (\({\varPhi }_{\mathrm{B}}\)) can give us a hint on the polarity of the interface traps. For the n-type semiconductor, while the negatively charged interface traps (acceptor-like) increase the barrier height, the positively charged interface traps (donor-like) decrease the barrier height. Therefore, the variation in \({\varPhi }_{\mathrm{B}}\) is caused by the existing and newly formed traps with a change in annealing temperature. Another cause of change in the barrier height is the internal electric field caused by the traps in the low quality oxide and interface [35]. A low barrier height results in high electron injection which means high tunneling possibility for electrons; therefore, a high barrier height reduces electron injection (leakage current). In Table 1, all barrier heights were high compared to the usual \({\varPhi }_{\mathrm{B}}\) values in the literature which range from 0.56 to 3.68 eV [22, 32, 36].

aC−2–V plots of the Al/Al2O3/SiO2/n-Si MOS capacitor with Al2O3/SiO2/n-Si films annealed at different temperatures and those left as-deposited taken at 1 MHz. bC−2–V plots of linear region of the Al/Al2O3/SiO2/n-Si MOS capacitor with Al2O3/SiO2/n-Si films annealed at different temperatures and those left as-deposited taken at 1 MHz

The frequency-dependent electrical characteristics of the Al/Al2O3/SiO2/n-Si MOS capacitor were studied with the aid of the C–V and G/ω–V measurements as shown in Fig. 6a, b. These measurements were taken for only the 450 °C annealed MOS capacitor because of its high Cox related to a high dielectric constant (\({\varepsilon }_{\mathrm{o}\mathrm{x}}\)), and its flat-band voltage (− 0.8 V) was the closest to the ideal flat-band voltage (~ − 0.27 V) compared to the other samples. Again, correction was performed in order to eliminate series resistance. Figure 7a, b contains the corrected capacitance (Cc) and corrected conductance (Gc/w) curves, while there was almost no difference between C–V and Cc–V curves, the difference between G/ω–V and Gc/w–V was significant. This explains that series resistance greatly affected conductance. As observed in Fig. 8a, the capacitance values decreased with increasing frequency due to time-dependent surface traps, particularly interface traps [26, 37, 38]. In Eq. 15, \(\tau\) is the life-time of the interface traps and is equal to CitRs, values of \(\tau\) in the literature are in the range (10−6 to 10−7 s) [17]. So, w\(\tau\) is extremely small for low frequencies (< 500 kHz). \({w}^{2}{\tau }^{2}\) is therefore neglected in Eq. 12. That is to say, an excess capacitance Cit evolves as a result of the interface-trapped charges which can follow the AC signal at low frequencies. Equation 15 then becomes Eq. 16 [26]. For high frequencies (\(\ge\) 500 kHz), \({w}^{2}{\tau }^{2}\) is quite higher compared to Cit, meaning that the interface-trapped charges can no longer follow the AC signal.

After correction, the conductance–voltage (Gc/w–V) peaks appeared for all frequencies. This means that series resistance (Rs) had a strong influence on the conductance. As observed in Fig. 9, maximum values of Rs are obtained in the depletion region and the amplitude of the peaks decreases with an increase in frequency. This indicates that Rs depends on the frequency-dependent charges such as interface charges and oxide-trapped charges [37, 39]. From these behaviors it can be evaluated that carriers possess sufficient energy to break free from their traps found between metal and silicon in the semiconductor band gap [37]. Furthermore, there was a significant deviation of the curves for low frequencies (< 500 kHz), while for high frequencies the deviations were too small. This is also because at high frequencies the charges in the traps found at the metal/Si interface acquire sufficient energy to leave these traps [4, 37].

A rare case in this study was that the effective oxide density as shown in Fig. 10 and Table 2 decreased with increasing frequency. A possible reason for this behavior is that the border trap charges were also affected by frequency. In the oxide, border traps are located near the interface, and carriers in the semiconductor can be captured in these traps after tunneling. The frequency affects these charges since an increase in the time constant for tunneling exponentially increases with the distance between interface and border traps [40].

4 Conclusion

The Al/Al2O3/SiO2/n-Si MOS capacitor was fabricated and the effect of the SiO2 on the electrical characteristics was analyzed. C–V and G/ω–V curves obtained from the Al/Al2O3/SiO2/n-Si MOS capacitors annealed at temperatures 250 °C, 450 °C, and 750 °C for high frequency (1 MHz). These curves distorted and shifted from the ideal ones due to presence of interface states density (Nit), border trap density (Nbt), effective oxide charge density (Nox), and series resistance (Rs). The closest flat-band voltage (Vfb) to the ideal one was with the sample annealed at 450 °C, this sample also had a high capacitance (Cox) which was related to its high dielectric constant (\({\varepsilon }_{\mathrm{o}\mathrm{x}}\)). Corrections were made for the C–V and G/ω–V measurements, and it was noticed that the effect of R on capacitance was negligible but that on conductance was significant. Nox and Nit values were very low (~ 109 eV−1 cm−2 and ~ 1010 eV−1 cm−2, respectively) indicating reduced lattice mismatches due to the highly stable SiO2.

A rare case in this study was that the effective oxide density decreased with increasing frequency. A possible reason for this behavior was that the border trap charges were also affected by frequency. So, in general, the SiO2 layer played a major role in improving the quality of both the oxide layers and the interfaces.

Data availability

We confirm that the data supporting the findings of this study are available within the article and its supplementary material.

Code availability

Not applicable.

References

L. Christophe, Making Silicon Valley: Innovation and the Growth of High Tech, 1930–1970 (Chemical Heritage Foundation, Philadelphia, 2006), pp. 253–256

S.S. Cetin, H.I. Efkere, T. Sertel, A. Tataroglu, S. Ozcelik, Silicon 100, 1–5 (2020). https://doi.org/10.1007/s12633-020-00383-8

A. Kahraman, U. Gurer, R. Lok, S. Kaya, E. Yilmaz, J. Mater. Sci. Mater. Electron. 29(20), 17473–17482 (2018)

A. Kahraman, E. Yilmaz, S. Kaya, A. Aktag, J. Mater. Sci. Mater. Electron. 26(11), 8277–8284 (2015)

M.I. Idris, N.G. Wright, A.B. Horsfall, Mater. Sci. Forum 924, 486–489 (2018)

Y. Wang, R. Jia, C. Li, Y. Zhang, AIP Adv. 5(8), 3–8 (2015)

A. Bouazra, S.A. Nasrallah, M. Said, A. Poncet, Res. Lett. Phys. (2008). https://doi.org/10.1155/2008/286546

N.M. Terlinden, G. Dingemans, V. Vandalon, R.H.E.C. Bosch, W.M.M. Kessels, J. Appl. Phys. 115(3), 033708 (2014)

R. Khosla, E.G. Rolseth, P. Kumar, S.S. Vadakupudhupalayam, S.K. Sharma, J. Schulze, IEEE Trans. Device Mater. Reliab. 17(1), 80–89 (2017)

S. Kitai, O. Maida, T. Kanashima, M. Okuyama, Jpn. J. Appl. Phys. 1(42), 247–253 (2003)

J. Robertson, Rep. Prog. Phys. 69, 327 (2006)

S. Kaya, E. Budak, E. Yilmaz, Turk. J. Phys. 42(4), 470–477 (2018)

R. Khosla, S.K. Sharma, J. Vac. Sci. Technol. B 36, 012201 (2018)

S. Demirezen, I. Orak, Y. Azizian-Kalandaragh, S. Altindal, J. Mater. Sci. Mater. Electron. 28, 12967–12976 (2017)

A. Tataroǧlu, G.G. Güven, S. Yilmaz, A. Büyükbas, Gazi Univ. J. Sci. 27(3), 909–915 (2014)

X.Y. Liu, Y.Y. Wang, Z.Y. Peng, C.Z. Li, J. Wu, Y. Bai, Y.D. Tang, K.A. Liu, H.J. Shen, Chin. Phys. B 24, 087304 (2015).

I. Hussain, M.Y. Soomro, N. Bano, O. Nur, M. Willander, J. Appl. Phys. 112, 064506–064507 (2012)

A. Kahraman, H. Karacali, E. Yilmaz, J. Alloys Compd. 825, 154171 (2020)

R. Khosla, P. Kumar, S.K. Sharma, IEEE Trans. Device Mater. Reliab. 15(4), 610–616 (2015)

G. Brammertz, H.C. Lin, K. Martens, D. Mercier, C. Merckling, J. Penaud, C. Adelmann, S. Sioncke, W.E. Wang, M. Caymax, M. Meuris, M. Heyns, ECS Trans. 16, 507 (2008)

P. Zhao et al., 2D Mater. 5, 3 (2018)

W. Bachir Bouiadjra, A. Saidane, A. Mostefa, M. Henini, M. Shafi, Superlattices Microstruct. 71, 225–237 (2014)

S. Kaya, E. Yilmaz, IEEE Trans. Electron Devices 62(3), 980–987 (2015)

A. Kahraman, E. Yilmaz, A. Aktag, S. Kaya, IEEE Trans. Nucl. Sci. 63(2), 1284–1293 (2016)

M. Pawlik et al., Energy Procedia 60(C), 85–89 (2014)

S. Kaya, R. Lok, A. Aktag, J. Seidel, E. Yilmaz, J. Alloys Compd. 583, 476–480 (2014)

J. Robertson, R.M. Wallace, Mater. Sci. Eng. R 88, 1–41 (2015)

S.M. Sze, Semiconductor Devices Physics and Technology (Wiley, Hoboken, 1985)

R.A.B. Devine, J. Phys. III France 6, 1569–1594 (1996)

N. Balaji, C. Park, S. Chung, M. Ju, J. Raja, J. Yi, J. Nanosci. Nanotechnol. 16, 4783 (2016)

W. Von Ammon, R. Hölzl, J. Virbulis, E. Dornberger, R. Schmolke, D. Gräf, J. Cryst. Growth 226(1), 19–30 (2001)

A. Kahraman, J. Mater. Sci. Mater. Electron. 29(10), 7993–8001 (2018)

T. Hosoi et al., Mater. Sci. Forum 679–680, 496–499 (2011)

W. Kern, J. Vossen, Thin Film Processes (Academic, New York, 1978)

T.P. Chen, IEEE Trans. Electron Devices 49, 1493–1496 (2002)

R. Lok, S. Kaya, H. Karacali, E. Yilmaz, J. Mater. Sci. Mater. Electron. 27(12), 13154–13160 (2016)

H. Xiao, S. Huang, Mater. Sci. Semicond. Process. 13, 395 (2010)

H.M. Baran, A. Tataroglu, Chin. Phys. B22, 047303–047304 (2013)

F. Parlaktürk, Ş. Altindal, A. Tataroǧlu, M. Parlak, A. Agasiev, Microelectron. Eng. 85, 81 (2008)

I. Dökme, Ş. Altindal, Physica B 393(1–2), 328–335 (2007)

Acknowledgements

This work is supported by the Presidency of Turkey, Presidency of Strategy and Budget under Contract Number 2016K12-2834.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflicts of interest

We declare that there is no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Kimbugwe, N.T., Yilmaz, E. Impact of SiO2 interfacial layer on the electrical characteristics of Al/Al2O3/SiO2/n-Si metal–oxide–semiconductor capacitors. J Mater Sci: Mater Electron 31, 12372–12381 (2020). https://doi.org/10.1007/s10854-020-03783-z

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10854-020-03783-z