Abstract

In this paper, new meminductor emulators have been proposed using operational transconductance amplifiers (OTA), a current differencing buffered amplifier (CDBA) and two grounded capacitors. Most meminductor emulators reported in the literature use memristor and resistor in their design but proposed emulators are memristor-less and resistor-less. The proposed emulators are designed for both decremental/incremental configurations of grounded and floating types of meminductors. The operating frequencies of the proposed emulators are extended up to 2 MHz for both grounded and floating configurations. The proposed circuits are electronically tunable as induced flux is controlled by changing the value of transconductance gain. The Monte-Carlo analysis and temperature analysis have been done and are found to be satisfactory. Simulation results have been obtained using Mentor Graphics Eldo simulation tool with 180 nm CMOS technology parameters. The performance of the proposed meminductor emulator has been verified by embedding the emulator in the design of adaptive learning circuits.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Resistors, capacitors and inductors are the three well known fundamental elements of any electrical and electronic circuits. The fourth fundamental element “memristor” was hypothesized by Leon Chua in 1971 [1], and its generalized concept of memristive devices was reported in 1976 [2]. The memristor was just a concept until the realization of the first physical memristor using TiO2 by Stanley Williams and his group in 2008 [3]. Thereafter, researchers have shown interest towards the realisations of memristors and their extensive usage in different applications of electrical and electronics engineering. Memristor is now viewed as the element having memory inside it that remembers the past events and reflects the reminiscence in the form of changing its resistance. Therefore, the property of remembrance of memristor (memory and resistor) is extended to two more elements namely memcapacitor (memory and capacitor) and meminductor (memory and inductor) [4]. These three elements (memristor, memcapacitor and meminductor) that are commonly referred as memelements having memory storage properties and thus their performances are dependent on the history of the system [5]. Memelements possess interesting characteristics that can be utilized in many areas of science and engineering. Memristors are available commercially but meminductor and memcapacitor are not widely available thereby improvement in the performance of mem-elements is still needed. Researchers and engineers are continuously trying to mimic the properties of these memelements with the help of emulator and mutator circuits. Various mutator circuits that can convert memristors into meminductors and memcapacitors have been reported in the literature. The emulators of both memcapacitors and meminductors have been realized using one traditional voltage operational amplifier (OP-AMP), memristor, resistor and a grounded capacitor [6]. Single and double-outputs current conveyors based memcapacitor and meminductor have been realized using memristor, inductor, resistor and capacitor [7]. Another meminductor and memcapacitor emulators have been realized using two AD844 types current feedback operational amplifiers (CFOAs) [8], one memristor emulator, resistor and capacitor [9]. A floating memristor-less meminductor emulator has been designed that uses four current conveyors, three traditional voltage OP-AMPs, one multiplier, seven resistors and two capacitors [10]. Another charge controlled memristor-less meminductor emulator has been realized using three conventional OP-AMPs, multiplier, inductor, MOSFETs, resistors and capacitors [11]. A mutator based meminductor emulator has been reported using two current conveyors, three traditional voltage OP-AMPs, one buffer, seven resistors, two dependent current sources, one multiplier and two capacitors [12]. A floating meminductor emulator has been realized using one memristor emulator, one AD844 type CFOA, one traditional voltage OP-AMP, three resistors and a capacitor [13]. The mutator based on the SPICE model has been reported in [14], that converts memristor into meminductor. A universal mutator has been suggested using trans-impedance OP-AMPs, buffers, resistors and capacitors [15]. A memristor-less meminductor emulator has been realized using three second generation current conveyors, one analog multiplier, three resistors and two capacitors [16]. A floating meminductor emulator has been reported using voltage controlled transconductor, resistors and capacitors [17]. The gyrator based meminductor emulator has been reported that converts memristor into meminductor using two traditional voltage OP-AMPs, few resistors and a capacitor [18]. A mutator has been reported using four AD844 type CFOAs, one traditional voltage OP-AMP, varactor diode, few resistors and capacitors that transform memristor into meminductor and memcapacitor [19]. A universal mutator has been reported using off-the-shelf components such as AD844 type CFOAs, AD633 four quadrant analog multiplier [20], few resistors and capacitor for the implementation of memristor, meminductor and memcapacitor [21]. Memristor, meminductor and memcapacitor emulators have been designed using several OP-AMPs, multipliers, resistors and capacitors [22]. A voltage differencing transconductance amplifier (VDTA) based meminductor emulator has been reported in both grounded and floating configurations that employs two VDTAs, one multiplier and two capacitors [23]. Fractional order memristor, meminductor and memcapacitor emulators have been designed using second-generation current conveyor, differential-input double-output transconductance amplifier, balanced-output current conveyor, differential voltage current conveyor, analog multiplier, resistor and capacitor [24]. A simple realization of meminductor and memcapacitor emulator has been reported using a current backward transconductance amplifier and grounded capacitor [25]. A meminductor emulator has been reported using nine OP-AMPs, five multipliers, several resistors and two capacitors [26]. A floating flux controlled meminductor emulator has been designed that employs an OTA, three AD844s, an analog multiplier, one OP-AMP, eight resistors and two capacitors [27]. Operational amplifier based grounded meminductor emulators have been reported using a memristor, resistors and capacitors [28]. Other meminductor emulators using VDTA, CDBA and grounded capacitor have been realized in [29]. VDCC based floating meminductor emulator has been reported using memristor and capacitor [30].

It has been observed in the literature survey that meminductor emulator’s realizations fall under two categories. In the first category, meminductor emulators have been realized using a mutator circuit that transforms memristor emulators into meminductor emulator circuits. The main disadvantage of the first method is that the characteristics of meminductor emulators are dependent on the memristor emulators’ characteristics. Additionally, the resulting circuit of the meminductor emulator is complex due to the usage of memristor emulator. The second method is based on memristor-less design of meminductor emulators. Some circuits of meminductor and memcapacitor emulators have been reported in the literature without using memristor [6, 10,11,12,13, 16, 17, 19, 21,22,23, 26, 27]. But, analog multipliers or an excess number of active and passive components are used in many realizations that lead to complex circuitry [11,12,13, 15, 16, 21, 26, 27]. Therefore, the main aim of this paper is to design memristor-less and resistor-less grounded/floating meminductor emulators using less number of active and passive components without using mutator and multiplier. The proposed meminductor emulator circuit consists of operational transconductance amplifiers (OTA), current differencing buffered amplifier (CDBA) and a capacitor. The advantages of the proposed circuit are (1) simple realization, (2) grounded and floating configurations and (3) resistor-less, memristor-less and multiplier-less realization. The content of this paper is presented in eight sections including introduction. The review of memelement is described in section 2. The characteristics of OTA and CDBA are explained in section 3. Section 4 covers the mathematical analysis of the proposed grounded and floating meminductor emulators. Simulation results of the proposed meminductor emulators in grounded/floating configurations have been shown in section 5. Section 6 shows the comparison of the proposed meminductor emulators with the existing meminductor emulators. Section 7 covers the application of the proposed meminductor emulators. Conclusions are given in section 8.

2 Review of mem-elements

Memristor, memcapacitor and meminductor are commonly referred to as mem-elements. The behaviours of mem-elements depend on the history of the devices. Memristor, the first component of mem-element, provides relation between two circuit variables namely flux (ϕ) and charge (q). Flux (ϕ) is the time integral of applied voltage V (t) whereas charge (q) is the time integral of current I (t) as given in Eqs. (1) and (2). The other mem-element namely memcapacitor establish relation between circuit variable σ and flux (ϕ) whereas meminductor relates ρ and charge (q). The circuit variables σ and ρ are the time integrals of charge (q) and flux (ϕ), respectively as given in Eqs. (3) and (4). The memristor (MR) can be defined as the derivative of flux (ϕ) with respect to charge (q). Similarly, memcapacitor (Mc) is defined as derivative of σ with respect to flux (ϕ) whereas meminductor is defined as derivative of ρ with respect to charge (q). These relations are given in Eqs. (5), (6) and (7). The pinched hysteresis loops among q–ϕ, q–V and I–ϕ planes are plotted for memristor, memcapacitor and meminductor, respectively. The current-voltage relationships of memristor, memcapacitor and meminductor are given in Eqs. (8)–(10). The summary of inter-relations between mem-elements is shown in figure 1.

System defining the inter-relation between the mem-elements [31].

3 Characteristics of voltage tunable OTAs and CDBA

The symbol of voltage tunable OTA is shown in figure 2. The input voltages \({\text{V}}_{1}\) and \({\text{V}}_{2}\) are applied to the input terminals of OTA that are converted into two output currents (\({\text{I}}_{{{\text{X}} + }}\) and \( {\text{I}}_{{{\text{X}} - }}\)) by the transconductance gain (\({\text{G}}_{{\text{m}}}\)) as given in Eq. (11). The transconductance gain (\({\text{G}}_{{\text{m}}}\)) of voltage tunable OTA depends upon the value of biasing voltage (\({\text{V}}_{{\text{B}}}\)) as given in Eq. (12) where µn is the mobility of electron, Cox is the gate-oxide capacitance and W/L is the aspect ratios of MOSFETs. The CMOS implementation of OTA is shown in figure 3 where biasing current (IB) of differential pair MOSFETs (M1 and M2) is provided with the help of MOSFETs M5, M6 and M7. The value of voltage (VB) applied at the gate terminal of MOSFET M7 is changed in order to change the value of transconductance gain (Gm).

Symbol representation of OTA [32].

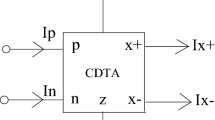

The active block, namely current differencing buffered amplifier (CDBA) has four terminals out of which “P” and “N” are low impedance input terminals whereas “W” and “Z” are output terminals as shown in figure 4. The input currents (IP and IN) are applied to “P” and “N” terminals of CDBA and the difference of these currents are conveyed at the “Z” terminal. The voltage across the “Z” terminal of CDBA is copied to the “W” terminal. The terminal characteristics of CDBA are given in Eq. (13). The circuit diagram of CDBA is shown in figure 5.

Symbolic representation of CDBA [33].

4 Proposed grounded and floating decremental/incremental meminductor emulator

The proposed grounded decremental/incremental meminductor emulator using OTAs and CDBA is shown in figure 6. In figure 6, input terminals “+” and “−” of OTA-1 are connected to the output terminals “X2−” and “X2+” of OTA-2, respectively. The output terminal “X1−”of OTA-1 is shortened to input terminal “+” of OTA-2 and is connected to capacitor C1. The other input terminal “−”of OTA-2 is grounded. The bias voltage “VB” is connected to the “W” terminal whereas the bias voltage “VB1” of CDBA is set to −0.1 V. The current “IX1+” of OTA-1 is given to the “P” terminal of CDBA that result in decremental meminductor emulator whereas incremental meminductor is realized if the current “IX1+” of OTA-1 is given to “N”. terminal of CDBA.

Capacitor C2 is connected to the “Z” terminal of CDBA. The voltage across the “Z” terminal of CDBA is copied to the “W” terminal of CDBA that is connected to biasing voltage “VB” of OTAs. The voltage “Vw” controls the transconductances (gm1 and gm2) of OTAs. The output current “IX1+” of OTA-1 is passed through the “P” or “N’ terminal of CDBA. CDBA transfers the applied input current (IX1+) to “Z” terminal either in the same or opposite direction and finally capacitor C2 gets charged. The same voltage is copied to the “W” terminal of CDBA that controls the value of meminductance by controlling the transconductance gains (gm1 and gm2) of OTAs. The value of meminductance (ML) depends on the value of transconductances of OTAs. Thereby, the value of meminductance is controlled according to the previous history i.e., charge stored in capacitor C2 of the circuit and the meminductor property is obtained. A pinched hysteresis loop has been achieved that validates the proposed configuration as a decremental or incremental meminductor emulator.

The routine analysis of the proposed grounded decremental meminductor emulator is as follows:

where Vin2+ is voltage across capacitor C1 that can be written as

Substituting the value of \(I_{X1 - }\) from Eq. (11) into Eq. (17) results in the same equation as in [23]

where \(\int V_{in} dt\) = \(\varphi \left( t \right)\) is the flux generated in meminductor emulator.

With the help of Eqs. (16) and (19), the value of input current (Iin) is obtaines as in [23]

Bias voltages (VB) of both OTAs are the same as can be seen from figure 6. Therefore, the transconductances (Gm1 and Gm2) of both OTAs are equal.

Substituting Gm1 = Gm2 = Gm into Eq. (20) result into

The relation between flux Φ (t) and current I (t) is given by

Therefore, after comparing Eqs. (21) and (22), the value of inverse meminductance is obtained as

Rearranging Eq. (23) will result in the value of meminductance as

The voltage across capacitor (C2) that is connected to “Z” terminal of CDBA can be written as

From the terminal equations of CDBA, the value of current (Iz) can be easily obtained as

Substituting the value of current Iz (t) from Eq. (26) into Eq. (25), we get

The voltage Vz is copied to the “W” terminal of CDBA by an internal buffer. Thus, the voltage Vw can be written as

Substituting the value of bias voltage VB from Eq. (28) to Eq. (12) results in

Substituting the value of Gm from Eq. (29) into Eq. (23), we get

After simplifying Eq. (30) the value of meminductance (ML) is obtained as

Rearranging the terms of Eq. (31) results in the value of meminductance (ML) for decremental meminductor as

Similarly, after interchanging the connections at input terminals of CDBA from “p” to “n” the value of meminductance (ML) for incremental meminductor is obtained as

It can be concluded from the Eqs. (32) and (33) that the first term of meminductance remains constant whereas the second term is variable due to its dependence on flux (ϕin). Both the terms of Eq. (32) are negative while both terms of Eq. (33) are positive and thereby represent the meminductances (ML) of decremental and incremental meminductor emulators, respectively.

The proposed floating decremental/incremental meminductor emulator using OTAs and CDBA is shown in figure 7. Connections of figure 7 are similar to the connections of figure 6 with only one difference in the applied voltages “Vin+” and “Vin−” at both the terminals (positive and negative) of OTAs, respectively. In the proposed emulator of figure 6, the negative terminal of OTA-1 is grounded while in figure 7 of the proposed floating meminductor emulator it is kept at voltage “Vin−”. Therefore, the meminductances (ML) derived in Eqs. (32) and (33) are equally valid for the proposed floating meminductor (ML) emulator of figure 7.

5 Simulation results

Simulation results have been obtained for the proposed meminductor emulators by Mentor Graphics Eldo Simulation tool using

180 nm CMOS technology parameters. The voltage supply VDD = −VSS = 0.9 V. The biasing voltage (VB1) is set to -0.1V. The values of capacitors C1 and C2 are chosen as 20 pF and 40 pF, respectively. The values of current sources (IB1 and IB2) used in the design of CDBA are 20 µA.

5.1 Selection of aspect ratios (W/L) of MOSFETs for the design of OTA and CDBA on the basis of inversion coefficient

The operational transconductance amplifier (OTA) used in the design of meminductor emulator is shown in figure 8 with values of aspect ratios (W/L) and inversion coefficients (IC) for each MOSFET. The bias current (2IB) of differential pair MOSFETs of OTA is selected as 100 μA. The OTA shown in figure 8 is balanced and symmetrical and therefore bias current (IB) can be assumed equal in all branches i.e. 50 μA. The design steps of OTA are presented here on the basis of inversion coefficient (IC) [34]. The inversion coefficient (IC) is expressed as

where ID is the drain current of MOSFET, I0 is the technology current that remains almost fixed (0.064103 μA for 0.18 μm technology) for a particular technology and W/L is the aspect ratio of the MOSFET. The range of inversion coefficients (IC) are represented in figure 9 for the MOSFETs operating in saturation regions with several trade-offs [34]. The aspect ratios (W/L) of each MOSFETs of OTA are appropriately selected such that the inversion coefficient (IC) of each MOSFET remains in the range of strong inversion. The lengths of MOSFETs are chosen large enough to avoid the several adverse effects that generally occur in strong inversion region.

The inversion coefficient for different regions and sub-regions of MOSFETs with corresponding performance trade-offs [34].

The circuit diagram of CDBA with aspect ratios (W/L) and inversion coefficients (IC) of each MOSFET is represented in figure 10. It can be seen that aspect ratios and bias currents (IB) are chosen such that their inversion coefficients (IC) lie in the range of moderate or strong inversion for the MOS transistors of CDBA.

The summary of aspect ratios of MOSFETs is shown in Table 1.

5.2 Proposed grounded decremental/incremental meminductor emulator

The transient analysis of the proposed grounded decremental meminductor emulator has been obtained by applying an input sinusoidal signal of amplitude 100 mV and frequency 100 KHz as shown in figure 11. The pinched hysteresis loops (PHLs) between flux and current of the proposed grounded decremental meminductor emulators have also been obtained by applying a sinusoidal signal having amplitude of 100 mV for different frequencies lies in the range of 30 KHz to 2 MHz as shown in figures 12(a)–(g). The pinched hysteresis loops of the proposed grounded incremental meminductor emulators have also been shown for different frequencies lie in the range of 30 KHz to 2 MHz as shown in figures 13(a)–(g).

5.3 Proposed floating decremental/incremental meminductor emulator

The transient analysis of the proposed floating meminductor emulator has been obtained by applying a sinusoidal voltage of amplitude 200 mV and frequency 100 KHz as shown in figure 14. The pinched hysteresis loop has also been obtained for the frequencies lie in the range of 30 KHz–2 MHz frequencies as shown in figure 15. The pinched hysteresis loops for floating incremental meminductor emulators are shown in figure 16.

5.4 Temperature analysis

The temperature analysis has been done for both proposed grounded and floating decremental meminductor emulators after applying an input sinusoidal signal of amplitude 100 mV and frequency of 50 KHz while the temperature is varied from −10 to 40°C. This analysis verifies that pinched hysteresis loops are not deformed even after variation in temperature as shown in figure 17 and thereby the proposed circuits are satisfactorily working for different temperatures.

5.5 Monte Carlo analysis of proposed grounded and floating decremental/incremental meminductor emulators

The Monte Carlo analysis has been performed for the proposed meminductor emulators at a frequency of 50 KHz for the 200 runs to check the robustness of the proposed designs. The gaussian random variations have been given for the variation in threshold voltages, aspect ratios of MOSFETs and in device capacitances. The pinched hysteresis loops for proposed meminductor emulators have been shown in figure 18 and 19 that confirms that the pinched hysteresis loops cross at zero for various cycles and converse flawlessly.

5.6 Shifting of pinched point at higher frequencies

The shifting of pinched points along the X-axis is clearly observed at higher frequencies from figures 12, 13, 15 and 16. The shifting of pinched points can be avoided with proper scaling of values of capacitors with frequency. The pinched hysteresis loops obtained from the simulation results of the proposed meminductor emulators depend on the product of angular frequency and value of capacitor (ωC). The pinched point gets shifted from the origin when frequency is increased without scaling the values of capacitors. To maintain the pinched point, the values of capacitors need to be scaled properly with increase in frequency. The pinched hysteresis plots after varying the values of capacitors for different operating frequencies have now been shown in figure 20 to show the effect. It is observed from the simulation results that keeping the product of angular frequency and capacitor constant, the shifting of pinched points in the hysteresis loop at higher frequencies may be avoided.

5.7 Effect of changing the bias voltages and currents on the pinched hysteresis loops

The pinched hysteresis loops for different bias voltages and currents are presented in figures 21(a)–(b). It is observed from figures that the proposed meminductor emulator maintains the hysteresis loops after varying the supply voltages and bias currents. This verifies the robustness of the proposed meminductor emulator.

6 Comparison of the proposed meminductor emulators with other meminductor emulators reported in literature

The comparison of the proposed meminductor emulators with other meminductor emulators has been given in Table 2.

The comparison has been done in terms of number of active/passive components, operating frequency range, power supply and type of realizations. The conclusion of Table 2 is as follows.

-

(1)

Most meminductor emulators reported in the literature are not electronically tunable but the proposed meminductor emulators are electronically tunable.

-

(2)

The meminductor emulators reported in [6, 7, 9, 12, 13, 15, 19,20,21, 24] employ mutator circuit or memristor emulator for the implementation of meminductor emulator. However, the proposed meminductor emulators are memristor-less.

-

(3)

In the meminductor emulators reported in [6, 7, 9,10,11,12, 15,16,17, 19,20,21, 24,25,26] use more number of active and passive components to realize meminductor emulator while the proposed meminductor emulator uses only two active and two passive component.

-

(4)

Analog multiplier has been used in the realization of meminductor emulators reported in [6, 11,12,13, 15, 16, 25, 26] whereas the proposed meminductor emulator has been designed without using a multiplier.

-

(5)

Almost all meminductor emulators reported in the literature use one or more resistors and capacitors as passive components; however, the proposed meminductor emulator is resistor-less and uses only two capacitors as passive components.

-

(6)

The operating frequency range of all meminductor emulators are very less in the Hz and kHz range but the proposed meminductor emulator works satisfactorily in MHz.

7 Application of the proposed meminductor emulator in adaptive learning circuit

To verify the performance of the proposed meminductor emulator, an adaptive learning circuit [35,36,37,38] has been realized as shown in figure 22. The proposed meminductor (ML) emulator circuit is connected in series with resistance (R) and capacitor (C). Mem-inductor remembers the past events and its performance is also dependent on the history of the circuit. To verify the property of remembrance, a piecewise linear (PWL) signal is applied to the input of the adaptive learning circuit realized in figure 22. The circuit first learns the pattern of PWL. It remembers the past input and tries to predict the pattern quickly. The same can be verified from the output (Vout) of figure 23 that it takes slightly more time to follow the first pulse but after learning the behavior of input pulse, it quickly follows the second and third pulses of the input. Fourth pulse is applied after some interval to verify the remembrance. It can also be verified that the circuit designed using meminductor is able to follow the fourth pulse that is applied after an irregular interval. The circuit behavior is analogous to amoeba’s learning (amoeba first learns and then acts on the basis of past events). To understand the analogy with amoeba, input voltage (Vin) can be considered as temperature that controls the amoeba’s motion. Output voltage (Vout) across the capacitor represents the locomotive speed of amoeba with respect to temperature variations. The variations in the locomotive speed (Vout) are according to environmental changes (Vin). It is clearly seen that if temperature (corresponds to Vin) slows down the voltage (Vout) corresponds to locomotive speed also falls down. The future temperature drops are predicted from the past occurrence drop which verifies the adaptive learning process steps of amoeba. The components values in the adaptive learning circuit are chosen as follows: R = 2 KΩ, C = 50 nF and the meminductor emulator component C1 = 20 pF and C2 = 40 pF.

8 Conclusions

Grounded and floating memristor-less and resistor-less decremental/incremental meminductor emulators have been proposed using two OTAs, one current differencing buffered amplifier and two grounded capacitors. The performances of the proposed meminductor emulators are found to be satisfactory for a wide range of frequencies. Temperature analysis and Monte Carlo analysis also satisfy the robustness of the proposed emulators. The performance of the proposed emulators has also been compared with other meminductor emulators reported in the literature. An adaptive learning circuit has also been realized to check the worthiness of the proposed meminductor emulators.

References

Chua L O 1971 Memristor-the missing circuit element. IEEE Transactions on Circuit Theory 18: 507–519

Chua L O and Kang S M 1976 Memristive devices and systems. Proceedings of the IEEE 64: 209–223

Strukov D B, Snider G S, Stewart D R and Williams R S 2008 The missing memristor found. Nature 453: 80–83

Ventra M D, Pershin Y V and Chua L O 2009 Circuit elements with memory: Memristors, memcapacitors, and meminductor. Proceedings of the IEEE 97: 1717–1724

Ventra M D, Pershin Y V and Chua L O 2009 Putting memory into circuit elements: memristors, memcapacitors, and meminductors. Proceedings of the IEEE 97: 1371–1372

Pershin Y V and Ventra M D 2009 Memristive circuits simulate memcapacitors and meminductors. Electronics Letters 46: 517–518

Pershin Y V and Ventra M D 2011 Emulation of floating memcapacitors and meminductors using current conveyors. Electronics Letters 47: 243–244

MHz 2000 V/μs Monolithic op-amp AD844 1990 Analog Devices, Inc. Norwood, MA 02062-9106, USA

Yu D S, Liang Y, Lu H H C and Hu Y H 2014 Mutator for transferring a memristor emulator into meminductive and memcapacitive circuits. Chinese Physics B 23(070702): 1–11

Liang Y, Chen H and Yu D S 2014 A practical implementation of a floating memristor-less meminductor emulator. IEEE Transactions on Circuits and Systems II: Express Briefs 61: 299–303

Sah M P, Budhathoki R K, Yang C and Kim H 2014 Charge controlled meminductor emulator. Journal of Semiconductor Technology and Science 14: 750–754

Sah M P, Budhathoki R K, Yang C and Kim H 2014 A mutator-based meminductor emulator circuit. In: 2014 IEEE International Symposium on Circuits and Systems (ISCAS), pp. 2249–2252

Yu D S, Chen H and Lu H H C 2013 A meminductive circuit based on floating memristive emulator. In: 2013 IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1692–1695

Wang H, Wang X, Li C and Chen L 2013 SPICE mutator model for transforming memristor into meminductor. In: Abstract and Applied Analysis Hindawi, pp. 1–5

Yu D, Liang Y, Lu H H and Chua L O 2014 A universal mutator for transformations among memristor, memcapacitor, and meminductor. IEEE Transactions on Circuits and Systems II: Express Briefs 61: 758–762

Fouda M E and Radwan A G 2014 Memristor-less current-and voltage-controlled meminductor emulators. In: 2014 21st IEEE International Conference on Electronics, Circuits and Systems (ICECS), pp. 279–282

Fouda M E and Radwan A G 2014 Simple floating voltage-controlled memductor emulator for analog applications. Radioengineering 23: 944–948

Wang S F 2016 The gyrator for transforming nano memristor into meminductor. Circuit World 42: 197–200

Yu D, Zhao X, Sun T, Lu H H and Fernando T 2019 A simple floating mutator for emulating memristor, memcapacitor, and meminductor. IEEE Transactions on Circuits and Systems II: Express Briefs 67: 1334–1338

A low cost four quadrant analog multiplier AD633 Analog Devices, Inc. Norwood, MA 02062-9106, USA

Zhao Q, Wang C and Zhang X 2019 A universal emulator for memristor, memcapacitor, and meminductor and its chaotic circuit. Chaos: An Interdisciplinary Journal of Nonlinear Science, 29: 013141 1-14

Yuan F and Li Y 2019 A chaotic circuit constructed by a memristor, a memcapacitor and a meminductor. Chaos: An Interdisciplinary Journal of Nonlinear Science, 29: 101101 1-15

Vista J and Ranjan A 2019 A High frequency meminductor emulator employing VDTA and its application. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 39: 2020–2028

Khalil N A, Said L A, Radwan A G and Soliman A M 2019 Emulation circuits of fractional-order memelements with multiple pinched points and their applications. Chaos, Solitons & Fractals 138: 109882

Taşkıran Z G C, Sağbaş M, Ayten U E and Sedef H 2020 A new universal mutator circuit for memcapacitor and meminductor elements. AEU-International Journal of Electronics and Communications 119(153180): 1–11

Yuan F, Jin Y and Li Y 2020 Self-reproducing chaos and bursting oscillation analysis in a meminductor-based conservative system. Chaos: An Interdisciplinary Journal of Nonlinear Science, 30: 053127 1-15

Sozen H and Cam U 2020 A novel floating/grounded meminductor emulator. Journal of Circuits, Systems and Computers 29(2050247): 1–25

Singh A and Rai S K 2020 Novel meminductor emulators using operational amplifiers and their applications in chaotic oscillators. Journal of Circuits, Systems, and Computers 30(2150219): 1–25

Yadav N, Rai S K and Pandey R 2021 New grounded and floating memristor-less meminductor emulators using VDTA and CDBA. Journal of Circuits, Systems and Computers 30(2150283): 1–31

Singh A and Rai S K 2021 VDCC-based memcapacitor/meminductor emulator and its application in adaptive learning circuit. Iranian Journal of Science and Technology, Transactions of Electrical Engineering,. https://doi.org/10.1007/s40998-021-00440-x

Biolek D, Biolek Z and Biolkova V 2009 SPICE modeling of memristive, memcapacitative and meminductive systems. In: Proc. 2009 European Conf. Circuit Theory and Design, pp. 249–252

Barranco B L, Vazquez A R, Sinencio E S and Huertas J L 1991 CMOS OTA-C high-frequency sinusoidal oscillators. IEEE Journal of Solid-State Circuits 26: 160–165

Acar Cevdet and Ozoguz Serdar 1999 A new versatile building block: current differencing buffered amplifier suitable for analog signal-processing filters. Microelectronics Journal 30: 157–160

Binkley D M 2008 Tradeoffs and optimization in Analog CMOS Design. Wiley, New York, pp 377–476

Pershin Y V, La F S and Di V M 2009 Memristive model of amoeba learning. Physical Review E 80: 021926

Pershin Y V and Di Ventra M 2010 Experimental demonstration of associative memory with memristive neural networks. Neural Networks 23: 881–886

Babacan Y and Kacar F 2017 FCS based memristor emulator with associative learning circuit application. Istanbul University-Journal of Electrical & Electronics Engineering 17: 3433–3437

Wang F Z, Chua L O, Yang X, Helian N, Tetzlaff R, Schmidt T, Li C, Carrasco J M G, Chen W and Chu D 2013 Adaptive neuromorphic architecture (ANA). Neural Networks 45: 111–116

Acknowledgement

This research work was financially supported by the University Grant Commision (UGC), New Delhi, India; by providing NFOBC fellowship (Student ID; 201819-NFO-2018-19-OBC-HAR-69999).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Yadav, N., Rai, S.K. & Pandey, R. New high frequency memristorless and resistorless meminductor emulators using OTA and CDBA. Sādhanā 47, 8 (2022). https://doi.org/10.1007/s12046-021-01785-z

Received:

Revised:

Accepted:

Published:

DOI: https://doi.org/10.1007/s12046-021-01785-z