Abstract

In this paper, a fully-integrated tunable grounded memristor emulator circuit based on voltage differencing transconductance amplifier (VDTA) has been proposed. The proposed memristor emulator circuit utilizes two VDTA active building blocks, two grounded resistors, a grounded capacitor and a four-quadrant analog multiplier. The working concept along with the detailed derivation of the mathematical model of the circuit has been discussed numerically and analytically to validate the operation of the proposed emulator. The operations of the proposed emulator circuit, as governed by the established model, have been verified by performing simulations in Cadence Virtuoso at 45 nm technology node. Robustness analyses performed, reveal significant process-variation tolerance at deep sub-micron technology node.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

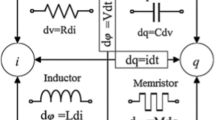

The memristor, often attributed as the “Missing Element” was postulated by Chua [1]. This fourth circuital element serves to provide the missing link between flux and charge. The developed mathematical model of the memristor, depicted the memritor’s unique property of retaining the value of its resistance. Further, the memristor was first fabricated in 2008 by using TiO2, by Hewlett-Packard (HP) laboratory [2]. The capability of the device to provide nonvolatile memory functionalities has attracted the attention of the scientific community for its potential in diverse fields of application. The discovery of the device has significantly impacted the advancement in neuromorphic circuits and their applications by featuring promising results in providing implementable compact synapses in neural networks. Extensive amount of research in this field has brought forth new resistive RAMs [3] and adaptive transistors [4, 5] which portray promising results in developing neuromorphic systems that can imitate the brain.

The TiO2-based memristor, as described by Strukov et al. [2] is uniquely characterized by a frequency-dependent pinched hysteresis loop in its I–V plot for sinusoidal excitations. The resistance of this two-terminal device depends on the voltage across its terminals or the amount of charge that has flowed through it. The operation of the memristor can be expressed mathematically by two nonlinear functions M(q) and W(φ), which are referred as memristance and memductance respectively, [6] i.e.,

where q is charge and φ is the flux.

From (1) we obtain a constitutive relationship between the memristor terminal voltage (v) and current (i), i.e.,

The relationships derived from (1) and (2) suggest that when φ–q curve is nonlinear, the resistance of the memristor will change with the variation in operating point q = qo at time t. The operating point (qo) does not change without applying any external voltage or current, thus the resistance of the memristor or the memristance (M) remains constant and consequently the signal is memorized.

The characteristic pinched hysteresis dependence between voltage and current are depicted for sinusoidal periodic excitations at relatively low frequencies. However, with increase in the frequency of excitation, the area of lobes of the hysteresis curve decrease and the whole curve gradually approaches the shape of a straight line. Thereby, at higher frequencies of operation, the memristor behaves like a linear resistor. Such unique features owe to its nonlinear properties which impart immense potential in high performance and high-density memory technology.

Despite its potential for widespread utilization, the TiO2-based memristor is still not commercially available as a result of technological difficulties and cost in fabrication of nanoscale devices. Recently, significant research work has been observed in the area of memristor emulator circuits which can mimic the unique properties of the TiO2 memristor and are also physically realizable [7,8,9,10,11,12,13,14,15,16,17,18]. Authors in these papers have proposed new memristor emulator circuits by using active building blocks (ABBs) and a number of passive elements. However, these emulators are lacking in certain novel features like, electronically tunable characteristics, occurrence of pinching of the hysteresis loop at relatively low-frequencies, range of operation and low power consumption, etc.

This paper presents a memristor emulator using CMOS-based voltage differencing transconductance amplifier (VDTA) as an active building block, which imparts characteristics like electronic tunability, improved range of frequency of operation, lower power consumption. Integration of the design with other VLSI circuits, while maintaining a simple structure and compatibility of the memristor characteristics with CMOS technology are the key features of the proposed circuit. Table 1 summarizes a comparative study between the proposed emulator circuit and pre-existing memristor emulator designs. The proposed memristor emulator utilizes two VDTA active elements, three grounded passive elements (i.e., two grounded resistors, a grounded capacitor) and an active analog voltage multiplier. The remainder of the paper is arranged as follows. Section 2 describes the operation of the VDTA and illustrates the CMOS implementation of it; followed by Sect. 3, which features the proposed emulator circuit along with the detailed mathematical explanation of its operation. Section 4 presents the results of various analyses performed and provides a brief explanation of the characteristics obtained. Section 5 concludes the paper by summarizing the various observations obtained.

2 Circuit description of VDTA

The VDTA is a versatile active building block [19] that is primarily used for analog signal processing applications/circuit designing such as filter [20], oscillator [21] etc. This state-of-the-art analog building block is a transconductance amplifier with multiple outputs and has the capability of electronically tunable transconductances. The advantages of utilizing VDTA as an active device are as follows: (a) VDTA does not require the use of external resistors and are substituted by internal transconductances, (b) it exhibits two different values of transconductances, which are electronically controllable by external bias currents, (c) It has the capability of operation in voltage mode, current mode as well as transconductance mode as compared to other active devices reported (d) All the ports of VDTA exhibit high impedance, (e) VDTA-based filters allow independent controllability of resonant frequency and quality factor as compared to other active devices (f) VDTA-based designs also possess low active and passive component sensitivities. Further, no component matching conditions are also required for VDTA-based designs. Moreover, VDTA-based designs provide electronically tunable active synthesis.

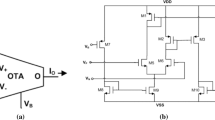

The equivalent representation of the VDTA with transconductance amplifiers is shown in Fig. 1. This active building block has six- terminals (as in Fig. 1) which are labelled as p, n, z, zc, x+, and x−. It also has the flexibility of both voltage and current modes [19] of operation. The VDTA is composed of two cascaded transconductance amplifiers (T-I and T-II). The differential-input differential-output transconductance amplifier of the first stage (T-I) has two high impedance inputs terminals ‘p’ and ‘n’; the terminal ‘z’ generates an output current (iz) which is proportional to the difference in the voltages at two input terminals ‘p’ and ‘n’ (i.e., vp − vn). The voltage drop at the ‘z’ (vz) terminal produces output current at the terminals ‘x+’ and ‘x−’ of the second transconductance stage (T-II). The currents at the terminals ‘x+’ and ‘x−’, are equal and opposite in directions. The ‘zc’ terminal is used for producing multiple copies of iz. Figure 2 illustrates the CMOS realization of the VDTA [22]. The mathematical equations that govern the relationship between the terminals are given as follows,

where gmf and gms are the first and second transconductances of the VDTA respectively and are termed as Arbel-Goldminz transconductances.

The transconductances can be adjusted electronically by the external DC bias current iB and are approximated as,

and

where gmni and gmpi are the transconductances of the ith NMOS and PMOS transistors respectively and is equal to,

and

where iB denotes the bias current; μN,P is the mobility of the carrier for transistors (N = NMOS, P = PMOS), Cox is the gate-oxide capacitance per unit area and (W/L) is the aspect ratio for the MOS transistors. The value of i varies from 1, 2…, 4.

3 The proposed memristor emulator circuit

The proposed emulator circuit emulates the change in the resistance of the memristor with the change in the applied input signal. This circuit consists of a two VDTAs, two grounded resistors, one grounded capacitor, a four-quadrant analog multiplier. The block-level representation and transistor-level representation of the proposed emulator circuit are shown in Figs. 3 and 4 respectively. The proposed emulator is simple, fully integrated and utilizes only on-chip elements. Nevertheless, most of the reported emulator designs use an off-chip multiplier circuit which increases the cost, power, area and the structural complexity for the integration of the entire circuit. The proposed design uses a MOS-based four quadrant analog multiplier circuit which is based on Gilbert cell architecture [23].

The multiplier circuit based on Gilbert cell architecture is composed of three NMOS differential pairs, two NMOS active loads and one active biasing resistor. The CMOS circuit diagram of the four-quadrant analog multiplier is illustrated in Fig. 5. Transistor M1, M2 acts as active biasing resistor and draws current iB from VDD. Transistors M3, M4 form a current mirror and behave like a tail current source. Transistors M5, M6, M7, M8, M9 and M10 form the three differential pairs for the applied differential inputs and transistors M11, M12 behave as active loads.

As depicted in the schematic (Fig. 5), the symmetrical configuration of the circuit allows for large output voltage swings. Voltage signals (‘vx’ and ‘vy’) to be multiplied are applied to input terminals ‘xp’, ‘xn’ and ‘yp’, ‘yn’ respectively. The inputs ‘xn’ and ‘yn’ are complementary to ‘xp’, ‘yp’, respectively. Assuming that transistors M5–M12 have identical value of β (i.e. \(\beta = \mu_{N} \cdot C_{ox} \cdot {W \mathord{\left/ {\vphantom {W L}} \right. \kern-0pt} L}\)), the output voltage of the multiplier can be expressed as,

where η is a constant for a definite value of β.

The operation of the proposed emulator can be explained mathematically by using the characteristic Eqs. (3) to (5). As shown in Figs. 3 and 4, VDTA1 consists of ‘p1’, ‘n1’, ‘z1’, ‘zc1’, ‘x+1’, ‘x−1’ terminals and ‘gmf1’, ‘gms1’ as the two transconductances. Similarly, VDTA2 consists of ‘p2’, ‘n2’, ‘z2’, ‘zc2’, ‘x+2’, ‘x−2’ terminals and ‘gmf2’, ‘gms2’ as the two transconductances. For VDTA1, the current at the ‘x−1’ terminal (ix1) is given by,

where vfb is the feedback voltage from the analog multiplier.

For VDTA2, Fig. 3 reveals the following at terminal ‘p2’,

From (10), the input current (iin) is related to the input voltage as,

Further analysis of VDTA2 using (3)–(5), we obtain the voltage at ‘p2’ terminal (vp2, vn2 = 0) and the current at ‘z2’ terminal (iz2), vp2, and iz2 are given respectively as,

and,

From (13), the voltage at the ‘z2’ terminal (vz2) can be obtained as,

Thereby, from (3) and (14), the currents at the ‘x+2’ and ‘x−2’ terminals of VDTA2 is given as,

Hence, from (15), the voltage at ‘x+2’ terminal (vx2+) is as follows,

The voltages drop vx2+ and vp2 are applied at the input of the four-quadrant analog multiplier to obtain the voltage (vfb) at the output of the multiplier. The feedback voltage (vfb), is obtained from (8), (12) and (16) and is given by,

Substituting (17) in (11), the characteristic equation of the voltage-controlled memristor equation is revealed as,

From (18), the memductance (GM) of the proposed emulator circuit is given as,

and,

For a particular case where the transconductances of both VDTA1 and VDTA2 are equal i.e. gmf1 = gmf2 = gmf, and gms1 = gms2 = gms, the value of GM from (20) is given by,

The dependence of GM of the proposed memristor emulator on the bias current iB is observed from Eqs. (4)–(7). The aforementioned equations govern the change in GM for any change in iB. Equations (20) or (21) suggest that, iB can be utilized to modulate the memductance, thereby imparting electronically tunable nature to the proposed emulator.

4 Analysis and results

This Section presents the results obtained from our investigations.

4.1 Frequency behavior analysis

As established in the previous section, in Eq. (21), the proposed memristor emulator circuit depicts a tunable memductance whose value largely depends on the input voltage, ‘vin’. From Faraday’s Law, we know that \(\phi (t) = \int {v(\tau ) \cdot d\tau }\). Therefore, Eq. (20) can be interpreted as,

Further, from Faraday’s law, we obtain,

and,

Thus, from (24), the memductance of the proposed flux-controlled memristor circuit can be presented as,

where \(W\left( {\phi_{in} (t)} \right)\) expresses the memductance function of the proposed memristor, which suggests that the memductance can be controlled by applying an input voltage. Further, Eq. (25) reveals that, \({\raise0.7ex\hbox{$1$} \!\mathord{\left/ {\vphantom {1 {R_{S} }}}\right.\kern-0pt} \!\lower0.7ex\hbox{${R_{S} }$}}\) is the time-invariant portion of the memductance \(W\left( {\phi_{in} (t)} \right)\).

The behavioral model of the proposed memristor derived in (25) can be used to gain an understanding of the frequency behavior of the circuit. In order to proceed with the study of frequency behavior of the emulator, let us assume that the proposed circuit is subjected to periodic sinusoidal excitations resulting in,\(v_{in} = A_{m} \cdot \sin (\omega t)\); where, the amplitude is ‘Am’, and the frequency of excitation is ‘f’ (which is given as,\(\omega = 2 \cdot \pi f\)). Therefore, we obtain,\(\phi_{in} = - \left( {{{A_{m} } \mathord{\left/ {\vphantom {{A_{m} } \omega }} \right. \kern-0pt} \omega }} \right) \cdot \cos \left( {\omega t} \right)\). Substituting the expressions corresponding to the assumed excitation in (25), we obtain,

Equation (26) reveals that, as the frequency of excitation (‘f’ or ‘ω’) gradually increases and approaches infinity, the time-varying portion of the memductance decreases and gradually approaches zero, thereby explaining the pinching effect of the characteristic hysteresis loop of the memristor emulator at very high frequencies. At high frequencies, the hysteresis loop pinches, areas enclosed by the hysteresis lobes decrease, and approaches the shape of a straight line. This behavior may be explained by (26), where the time-varying portion of \(W\left( {\phi_{in} (t)} \right)\) has a reduced overall contribution due to its inversely proportional relationship with ‘f’ (i.e.\(\left( {{{\eta \cdot g_{ms1} \cdot g_{ms2} \cdot g_{mf2} \cdot R_{M} \cdot A_{m} } \mathord{\left/ {\vphantom {{\eta \cdot g_{ms1} \cdot g_{ms2} \cdot g_{mf2} \cdot R_{M} \cdot A_{m} } {2\pi f \cdot C}}} \right. \kern-0pt} {2\pi f \cdot C}}} \right) \approx 0\), at very high frequencies of excitation). Hence, at high frequencies, \(W\left( {\phi_{in} (t)} \right)\) approaches the value of the time-invariant memductance, i.e.\(W\left( {\phi_{in} (t)} \right) \approx {1 \mathord{\left/ {\vphantom {1 {R_{S} }}} \right. \kern-0pt} {R_{S} }}\); this explains the pinching of the hysteresis loop to that of a straight line, suggesting the behavior of emulator as a linear time-invariant resistor. The relationship between the time-invariant and time-varying portions of \(W\left( {\phi_{in} (t)} \right)\), can be obtained from (26) as follows,

where ‘τ’, is the time constant of the emulator circuit, and ‘f’ is the frequency of excitation. Further, from (27) the time constant of the proposed emulator circuit is given as,

The frequency behavior of the proposed memristor emulator are governed by (27) and (28). The frequency analysis reveals three conditions relating K [in (27)] and the pinched hysteresis loop of \(W\left( {\phi_{in} (t)} \right)\). These conditions are delineated as follows:

- i.

K → 0, when f → \(\infty\), the behavior of the memristor emulator is dominated by the influence of the linear time-invariant portion of memductance.

- ii.

K → 1, when f → \({1 \mathord{\left/ {\vphantom {1 \tau }} \right. \kern-0pt} \tau }\), the emulator achieves the maximum pinched hysteresis loop.

- iii.

K\(\ge\) 1, when \(f \le {1 \mathord{\left/ {\vphantom {1 \tau }} \right. \kern-0pt} \tau }\), the period of the excitation (\({1 \mathord{\left/ {\vphantom {1 f}} \right. \kern-0pt} f}\)) is greater than the time constant ‘τ’ of the proposed emulator circuit. This results in the loss of the hysteresis loop.

To ensure the behavior of the frequency-dependent pinched hysteresis loop, it can be concluded that, the value of K must lie in the range from 0 to 1, i.e.\(0 \le K \le 1\). Further, the dependence of ‘τ’ on gm shows that the time constant can also be varied by modulating the bias current iB, thus tuning the characteristic hysteresis loop of the emulator circuit.

4.2 Analysis of simulation results

The proposed memristor emulator is simulated in Virtuoso Analog design Environment of Cadence at CMOS 45-nm CMOS process node. The supply voltage is taken as VDD = − VSS = 0.9 V. The transistor dimensions for the proposed memristor emulator are provided in Table 2. While conducting simulation analyses, all the VDTAs of the emulator have been identically biased with iB = 50 μA. Thus, we have gmf1 = gmf2 = gmf, and gms1 = gms2 = gms and from (21), (26), (27) and (28) we obtain the following expressions,

The emulator was subjected to a sinusoidal excitation of 1 kHz with an amplitude of 30 μA in order to examine the operation of the circuit. The input voltage and current, ‘vin’, ‘iin’ respectively, corresponding to the excitation are shown in Fig. 6. The transient responses of the proposed emulator are observed to be stable.

Further, Fig. 7 shows the frequency dependent pinched hysteresis loop for the same excitation, suggesting the stable operation of the circuit, where \(0 \le K \le 1\) is satisfied and the memductance, \(W\left( {\phi_{in} (t)} \right)\) has a dominant time-varying nature. To obtain the frequency range of operation of the memristor emulator, the frequency ‘f’, was varied from 800 Hz to 10 kHz. The hysteresis loop exhibited a decrease in the lobe areas as ‘f’ increased and approached a straight line at 10 kHz. Such observations are illustrated in Fig. 8, which suggest the frequency range of operation to be from 800 Hz (fmin) to 10 kHz (fmax).

Pinched hysteresis loop for the same excitation at a frequency of 1 kHz as in Fig. 5

As emphasized in Sect. 4.1, the operation range (\(0 \le K \le 1\)) of the memristor emulator circuit depends on the values of the different circuit elements [as in (29) and (31)]. Therefore, changing the values of the different circuital elements of the emulator can change the frequency range of operation. Table 3 enumerates the findings of such simulations by providing the different frequency ranges of operation for different values of iB and C, while keeping the values of the resistances RM, RS, (1 KΩ each) and amplitude of excitation Am constant.

Table 3 asserts the tunable nature of the proposed memristor emulator, where, by varying the iB the operating frequency range of the circuit may be varied. Figure 9 illustrates the time varying nature of the memductance for sinusoidal excitation of, Am = 30 μA, and f = 50 kHz. The power dissipation of the memristor emulator when subjected to such excitations, has been found to be 3.956 mW. Furthermore, the variation of memductance by varying ibias is depicted in Fig. 10 for different frequencies of operation. Thus, the GM and the frequency range of operation of the proposed memristor emulator can be tuned by the bias current.

4.3 Experimental results of proposed memristor emulator

This section presents the observations obtained from the experimental realization of the proposed memristor emulator circuit. The proposed VDTA based memristor emulator as in Fig. 3 has been implemented on breadboard using two commercially available LM13700 ICs, an analog multiplier AD633 IC, one capacitor (C) of 100 nF, two resistors of values 500 Ω (Rs), 5 kΩ (RM), along with a DC supply source of ± 10 V and bias current of 1.35 mA. A single LM13700 IC is composed of two current controlled transconductance amplifiers. Therefore a single VDTA building block can be easily realized by utilizing one LM13700 IC [24, 25].

The two LM13700 ICs are used as there are two VDTA elements in the proposed circuit (Fig. 3) and they are connected via the analog multiplier, which is implemented by AD633 IC. The experimental setup is shown in Fig. 11, which illustrates the characteristic hysteresis loop obtained from the realized emulator circuit. Figure 12 illustrates typical pinched hysteresis loop and Fig. 13 shows the transient input voltage and current characteristics for an input waveform of amplitude 500 mV at a frequency of 1.46 kHz.

The voltage-current curves gradually become narrower as the operating frequency is increased. For this reason, the behavior of the proposed emulator is analyzed at 2 kHz, 3.6 kHz, 4.3 kHz and 5.5 kHz frequency regions, as depicted in Fig. 14. The governing expression (25) can objectively explain this phenomenon; with increasing operating frequency, the linear time-variant portion of (25) decreases, thus the memristor emulator approaches linear characteristics at higher frequency regions. The experimental results presented here, suggests the memrisitve characteristics of the proposed VDTA based emulator circuit with variation in operating frequency. The simulation and exhaustive theoretical analyses along with the observations made in the experimental analyses reveals the feasibility of memristive behavior of the proposed emulator circuit in a packaged integrated MOS realization.

4.4 Reliability of proposed memristor emulator

Memristors exhibit unique nonvolatile memory characteristics, however they are profoundly impacted by variability, especially at highly scaled technology nodes [26, 27]. This has a profound impact on their operation especially at highly scaled technology nodes. With the current trends in aggressive scaling in order to keep up with the projections of Moore’s Law, it is important for memristive systems to retain their functionality even when subjected to extreme variations in device parameters. Keeping in view the importance to mitigate the impact of device variability, a study has been conducted to analyze the robustness of the proposed VDTA-based memristor emulator design.

The robustness of the proposed emulator has been assessed by subjecting the design to process variability. Due to the continued miniaturization of the MOS devices, process variation has a significant impact on performance of the circuit. Random variations in the wafer fabrication process, which include both intra-die and inter-die factors [28]; are responsible for variability in VLSI devices. Thus, the variation of any parameter x is,

Process sensitive MOS device parameters like the doping concentration NCH, channel length L, gate oxide thickness tox, channel width W, and etc. are major contributors to process variability. Further, at highly scaled deep-submicron technology nodes, oxide thickness variations (OTV), metal-gate work-function fluctuation (WKF), random dopant fluctuation (RDF), line-edge and line-width roughness (LER, LWR) are sources of intrinsic variability [29]. To model such fluctuations the device parameters like L, W, tox are considered to have independent Gaussian distributions with 3σ variations of ± 10% as projected by the guidelines of the International Technology Roadmap for Semiconductor Industry (ITRS) [30]. The influence of the aforementioned device parameters has a correlated impact on the threshold voltage Vt of the MOS device, hence due to the statistical interdependence of the fluctuating components the total variation in Vt can be estimated by [29],

where \(\sigma V_{t,total}\) is the total fluctuation in Vt, \(\sigma V_{t,RDF}\) is the fluctuation due to RDF, \(\sigma V_{t,PV}\) and \(\sigma V_{t,WKF}\) are the fluctuation components due to process variation- induced fluctuation in Vt and work-function respectively.

Hence, the overall impact of process variations resulting in device parameter fluctuations can be approximated by applying Gaussian distribution with 3σ variations of ± 10% only on the device threshold voltage Vt [31].

Monte Carlo simulation of 5000 iterations was carried out by applying Gaussian distribution to Vt and the memductance (GM) of the proposed memristor emulator was estimated. The overall impact of such variations can be estimated by Pelgrom’s Law [32] related to the current factor (β),

At deep-submicron CMOS technologies, the carrier mobility (\(\mu_{n}\)) saturates above the critical electric field (Ec) and very miniscule impact on the variation of β. Further, according to Pelgrom’s Law [32], the variance in any parameter P (ΔP) can be determined as,

where Dx is the separation between the matched devices and the area and spacing proportionality constants for P are represented as AP and SP respectively. From (35), the generalized expressions for variation in GM may be modeled as,

where \(\sigma_{{x_{i} }}\) is standard deviation of the device parameter x for the ith device.

The yield distribution for the meductance GM has been illustrated in Fig. 15. It is observed from Fig. 15 that there is a standard deviation (σ) of 97.079 μ℧ around the mean (μ) 1.11624 m℧, resulting in variability (σ/μ) of 0.08697. A limited spread in memductance value of the emulator circuit translates into a narrow spread in other design metrics of the memristor emulator, thereby validating the proposed design to be variation aware.

5 Conclusion

A novel memristor emulator circuit utilizing VDTA as active building elements is presented. The proposed emulator circuit consists of one grounded capacitor, two grounded resistors, one four quadrant analog multiplier, and two VDTAs. The circuit presented offers a simple circuit-topology, with fully integrated configuration, low power consumption, and tunable capability by which the characteristics of the emulated memristor can be varied electronically. The mathematical model for the proposed memristor emulator has been established in order to explain the characteristics and novel features of the circuit. Thorough analyses have been performed at CMOS 45 nm technology node using Virtuoso Analog Design Environment of Cadence, whose findings reported in this paper, reveal that the proposed emulator circuit is robust and variation-resilient to fluctuations in process parameters at deep-submicron technology nodes.

References

Chua, L. O. (1971). Memristor—the missing circuit element. IEEE Transactions on Circuit Theory,18(5), 507–519.

Strukov, D. B., Snider, G. S., Stewart, D. R., & Williams, R. S. (2008). The missing memristor found. Nature,453, 80–83.

Alibart, F., Gao, L., Hoskins, B. D., & Strukov, D. B. (2012). High precision tuning of state for memristive devices by adaptable variation-tolerant algorithm. Nanotechnology,23, 075201.

Alibart, F., Pleutin, S., Guérin, D., Novembre, C., Lenfant, S., Lmimouni, K., et al. (2010). An organic nanoparticle transistor behaving as a biological spiking synapse. Advanced Functional Materials,20(2), 330–337.

Agnus, G., Zhao, W., Derycke, V., Filoramo, A., Lhuillier, Y., Lenfant, S., et al. (2010). Two-terminal carbon nanotube programmable devices for adaptive architectures. Advanced Materials,22(6), 702–706.

Yu, D. S., Liang, Y., Chen, H., & Lu, H. H. C. (2013). Design of a practical memcapacitor emulator without grounded restriction. IEEE Transactions on Circuits and Systems II,60(4), 207–211.

Alharbi, A. G., Fouda, M. E., Khalifa, Z. J., & Chowdhury, M. H. (2017). Electrical nonlinearity emulation technique for current-controlled memristive devices. IEEE Access,5, 5399–5409.

Elwakil, A. S., Fouda, M. E., & Radwan, A. G. (2013). A simple model of double-loop hysteresis behavior in memristive elements. IEEE Transaction on Circuits Systems II, Express Briefs,60(8), 487–491.

Kim, H., Sah, M. P., Yang, C., Cho, S., & Chua, L. O. (2012). Memristor emulator for memristor circuit applications. IEEE Transactions on Circuits System I, Regular Papers,59(10), 2422–2431.

Petrovic, P. B. (2018). Floating incremental/decremental flux-controlled memristor emulator circuit based on single VDTA. Analog Integrated Circuits and Signal Processing,96(3), 417–433.

Sánchez-López, C., Mendoza-López, J., Carrasco-Aguilar, M. A., & Muñiz-Montero, C. (2014). A floating analog memristor emulator circuit. IEEE Transactions on Circuits Systems II Express Briefs,61(5), 309–313.

Sánchez-López, C., Carrasco-Aguilar, M. A., & Muñiz-Montero, C. (2015). A 16 Hz–160 kHz memristor emulator circuit. AEU International Journal of Electronics and Communications,69(9), 1208–1219.

Cam, Z. G., & Sedef, H. (2017). A new floating memristance simulator circuit based on second generation current conveyor. Journal of Circuits, Systems and Computers,26(2), 1–15.

Ranjan, R. K., Rani, N., Pal, R., Paul, S. K., & Kanyal, G. (2017). Single CCTA based high frequency floating and grounded type of incremental/decremental memristor emulator and its application. Microelectronics Journal,60, 119–128.

Sánchez-López, C., & Aguila-Cuapio, L. E. (2017). A 860 kHz grounded memristor emulator circuit. AEU-International Journal of Electronics and Communications,73, 23–33.

Yunus, B., Abdullah, Y., & Firat, K. (2017). Memristor emulator with tunable characteristic and its experimental results. AEU-International Journal of Electronics and Communications,81, 99–104.

Sozen, H., & Cam, U. (2016). Electronically tunable memristor emulator circuit. Analog Integrated Circuits and Signal Processing,89(3), 655–663.

Babacan, Y., & Kaçar, F. (2017). Floating memristor emulator with subthreshold region. Analog Integrated Circuits and Signal Processing,90(2), 471–475.

Biolek, D., Senani, R., Biolkova, V., & Kolka, Z. (2008). Active elements for analog signal processing: Classification, review, and new proposals. Radioengineering,17(4), 15–32.

Mehra, R., Kumar, V., & Islam, A. (2018). Reliable and Q-enhanced floating active inductors and their application in RF bandpass filters. IEEE Access,6, 48181–48194.

Kumar, V., Mehra, R., & Islam, A. (2017). A CMOS active inductor based digital and analog dual tuned voltage-controlled oscillator. Microsystem Technologies,25, 1–13.

Yesil, A., Kacar, F., & Kuntman, H. (2011). New simple CMOS realization of voltage differencing transconductance amplifier and its RF filter application. Radioengineering,20(3), 632–637.

Gilbert, B. (1968). A precise four-quadrant multiplier with subnanosecond response. IEEE Journal of Solid-State Circuits,3(4), 365–373.

Yeşil, A., Babacan, Y., & Kaçar, F. (2019). Design and experimental evolution of memristor with only one VDTA and one capacitor. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems,38(6), 1123–1132.

Kumar, P., Pandey, N., & Paul, S. K. (2017). Operational simulation of LC ladder filter using VDTA. Active and Passive Electronic Components,17, 1836727.

Querlioz, D., Bichler, O., Dollfus, P., & Gamrat, C. (2013). Immunity to device variations in spiking neural networks using memristive nanodevices. IEEE Transactions on Nanotechnology,12(3), 288–295.

Snider, G. S. (2008). Spike-timing-dependent learning in memristive nanodevices. In IEEE international symposium on nanoscale architectures. Anaheim (pp. 85–92).

Saha, S. K. (2014). Compact MOSFET modeling for process variability-aware VLSI circuit design. IEEE Access,2, 104–115.

Li, Y., Hwang, C.-H., Li, T.-Y., & Han, M.-H. (2010). Process-variation effect, metal-gate work-function fluctuation, and random-dopant fluctuation in emerging CMOS technologies. IEEE Transactions on Electron Devices,57(2), 437–447.

Semiconductor Industry Association. (2009). International technology roadmap for semiconductors. Retrieved January 15, 2018, from http://www.itrs2.net/itrs-reports.html.

Pal, I., & Islam, A. (2018). Circuit-level technique to design variation- and noise-aware reliable dynamic logic gates. IEEE Transactions on Device and Materials Reliability,18(2), 224–239.

Pelgrom, M. J. M., Duinmaijer, A. C. J., & Welbers, A. P. G. (1989). Matching properties of MOS transistors. IEEE Journal of Solid-State Circuits,24(5), 1433–1439.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Pal, I., Kumar, V., Aishwarya, N. et al. A VDTA-based robust electronically tunable memristor emulator circuit. Analog Integr Circ Sig Process 104, 47–59 (2020). https://doi.org/10.1007/s10470-019-01575-y

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-019-01575-y