Abstract

The variation of the temperature-dependent performance of an electronic device is one of the major concerns in predicting the actual electrical characteristics of the device as the bandgap of semiconducting material varies with temperature. Therefore, in this article, we investigate impact of temperature variations ranging from 300 to 450K on the DC, analog/ radio frequency, and linearity performance of dual material stack gate oxide-source dielectric pocket-tunnel-field-effect transistor (DMSGO-SDP-TFET). In this regard, a technology computer-aided design simulator is used to analyze DC, and analog/radio-frequency performance parameters, such as carrier concentration, energy band variation, band-to-band tunneling rate, \(I_\mathrm{DS}-V_\mathrm{GS}\) characteristics, transconductance (\(g_{m}\)), cut off frequency (\(f_{T}\)), gain-bandwidth product, maximum oscillating frequency (\(f_{\max }\)), transconductance frequency product, and transit time (\(\tau \)) considering the impact of temperature variations. Furthermore, linearity parameters, such as third-order transconductance (\(g_{m3}\)), third-order voltage intercept point (VIP3), third-order input-interception point (IIP3), and intermodulation distortion (IMD3) are also analyzed with temperature variations as these performance parameters are significant for linear and analog/radio-frequency applications. Moreover, the performance of the proposed DMSGO-SDP-TFET is compared with the conventional dual-material stack gate oxide-tunnel-field-effect transistor (DMSGO-TFET). From the comparative analysis, in terms of percentage per kelvin, the DMSGO-SDP-TFET demonstrates lesser sensitivity towards temperature variation. Hence, the proposed DMSGO-SDP-TFET is a suitable candidate for low-power switching, and biosensing applications at elevated temperatures as compared to conventional DMSGO-TFETs.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

To overcome the scaling issues of conventional MOSFETs, the tunnel field-effect transistor (TFET), based on the quantum tunneling mechanism, has emerged as an alternative device to conventional MOSFETs due to lower subthreshold swing (SS) below 60 mV/decade, immunity to various short channel effects, and low OFF-state current (\(I_\mathrm{OFF}\)) [1,2,3,4,5]. However, TFETs have been reported some major limitations, such as ambipolar current, lower ON-state current (\(I_\mathrm{ON}\)) and poor analog/radio frequency performance, due to inefficient band-to-band tunneling [6]. Therefore, to overcome the lower ON-state current issue, various methods have been reported by the researchers, such as double-gate TFET, work-function engineering, hetero-dielectric, stacked-gate structure, electrically doped (ED), pocket doping, dielectric pocket, Extended Source TFET, dual material and gate over source overlap [6,7,8,9,10,11,12,13,14,15,16,17,18,19,20,21,22]. Furthermore, to address the ambipolar current issue, various methods have been reported, such as hetero-dielectric, work-function engineering, stacked gate structure, pocket doping, dual material gate [23,24,25]. In addition to the above issues, performance variation with temperature is also one of the major causes of concern in TFETs. Several studies [26,27,28,29,30] have reported temperature dependence performance of various TFET structures.

In the previous work [21], to enhance the DC, analog/radio frequency performance of the device, authors have proposed DMSGO-SDP-TFET with optimized dielectric pocket at the source-channel junction and reported an improved performance in terms of higher ON-state current (\(I_\mathrm{ON}\) = 1.47 \(\times \)10\(^{-4}\) A) at (\(V_\mathrm{GS}\) = \(V_\mathrm{DS}\) =1.0 V), smaller point subthreshold swing (SS) = 15.7 mV/decade, maximum \(I_\mathrm{ON}\)/\(I_\mathrm{OFF}\) ratio (3.14\(\times \)10\(^{12}\)), transconductance (\(g_{m}\) = 1.02 \(\times \)10\(^{-3}\) S), and cut-off frequency (\(f_{T}\) = 193 GHz).

However, the operating temperature always impacts the on-chip performance of the device. With increase the number of transistors in the integrated circuits (ICs), level of heat dissipation increases, which leads to rise the operating temperature of the chip and hence of the device (transistor). Furthermore, from the perspective of transistor applications in some harsh environments (where the operating temperature differs from the room temperature) such as wireless/mobile/satellite communications, military, medical equipment, avionics, furnace temperature control, automobiles, etc. The integrated circuit chips employed for analog/RF applications needs a more accurate prediction of electrical characteristics of the device at higher temperatures. Hence, first time we have done extensive study for temperature sensitivity analysis of DMSGO-SDP-TFET as well as conventional DMSGO-TFET, also compared the temperature sensitivity of these devices under same bias conditions in terms of DC characteristics, analog/radio frequecncy, and linearity distortion performance parameters using TCAD Simulations.

The remaining part of this paper is organized as follows. Section 2 presents the structural and simulation setup details. Section 3 describes the temperature sensitivity of DMSGO-TFET and DMSGO-SDP-TFET in three parts. The first part presents a temperature sensitivity analysis of various DC parameters, the second part investigates the analog/radio frequency performance and the third part presents the linearity and distortion performance at different temperatures. Finally, the main findings of this work are concluded in Sect. 4.

2 Device structure, parameters and simulation details

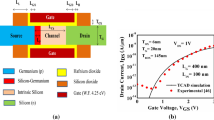

Fig. 1a, b illustrate the 2D structural views of conventional DMSGO-TFET and the proposed DMSGO-SDP-TFET for the parameters listed in Table 1. A stack gate oxide approach (low-k/high-k stack gate oxide i.e. \(\mathrm{{\rm SiO}}_{2}\)/\(\mathrm{{\rm HfO}}_{2}\) stack) is used to provide better quality oxide/channel interface which enhances the ON-state current [30]. The entire length of the stack gate (L\(_{G}\)) is considered 50 nm with \({\rm SiO}_{2}\) oxide layer thickness of (0.8 nm) and \({\rm HfO}_{2}\) oxide layer thickness of (1.2 nm) [19]. Furthermore, the total gate length (\(L_{G}\)) of both devices is partitioned into three parts: tunneling gate (\(M_{1}\)), control gate (\(M_{2}\)), and auxiliary gate (\(M_{3}\)) with different length (\(L_{1}\), \(L_{2}\), \(L_{3}\)) and work function (\(\phi _{1}\), \(\phi _{2}\), \(\phi _{3}\)), respectively. The control gate workfunction (\(\phi _{2}\)) is considered 4.4 eV which corresponds to the metal molybdenum (Mo) (4.36–4.95 eV). The work functions (\(\phi _{1}\) and \(\phi _{3}\)) are considered 4.0 eV which corresponds to metal aluminum (Al) (4.0–4.26 eV) [24]. The combination of stack gate oxide approach with workfunction engineering (\(\phi _{1}\) = \(\phi _{3}\) = 4.0 eV < \(\phi _{2}\) = 4.4 eV) and dielectric pocket at the source- channel interface is used to enhance the ON-state current, reduce leakage current, improve the switching ratio, subthreshold swing and analog /radio frequency performance of the device.

The temperature sensitivity of the proposed DMSGO-SDP-TFET is analyzed using TCAD simulations. For this, suitable models are incorporated such as the nonlocal band-to-band tunneling (BTBT) model is considered to measure the tunneling probability across the junctions. The Shockley-Read-Hall model is enabled to account for the minority carrier recombination effect. The bandgap narrowing model is used to consider the bandgap narrowing caused by high doping concentration. In our simulations, the Quantum confinement effect is not taken into account as it is significant only if the thickness of the Si body is less than 10 nm. In addition to these models, Newton’s method was used to provide strong coupling between the resulting equations in order to improve current convergence.

2-D schematic view of a conventional DMSGO-TFET and b DMSGO-SDP-TFET [21]

3 Results and discussion

3.1 Temperature sensitivity analysis of DC parameters

This section presents the comparative temperature-sensitive performance analysis of conventional DMSGO-TFET and proposed DMSGO-SDP-TFET in terms of carrier concentration, energy band variation, BTBT Variation, \(I_\mathrm{DS}-V_\mathrm{GS}\) characteristics, threshold voltage variation (\(V_\mathrm{TH}\)) and average subthreshold swing variation at elevated temperatures ranging from 300 to 450K.

Fig. 2a, b depict the ON-state carrier concentration variation with temperature ranging from 300 to 450K for conventional DMSGO-TFET and DMSGO-SDP-TFET, respectively. It is evident from these figures, due to stack gate oxide with lower work functions (\(\phi _{1}\) = \(\phi _{3}\) = 4.0 eV), at the source (drain) junctions, the electron (hole) concentration increases (decreases) in the channel, respectively, for both the devices. Moreover, as the temperature rises above room temperature, the covalent bond inside the lattice of semiconductor body material begins to break, resulting in a larger number of electron-hole pairs (EHPs) generation. The rate of EHPs generation is directly propositional to the intrinsic carrier concentration of semiconductor (\(n_{i}\)) [29]. The \(n_{i}\) is exponentially related to temperature as per the expression

Here, \(N_{a}\) represents the impurity (acceptor/donor) carrier concentration, \(E_{g}\) represents bandgap, K represents the Boltzmann constant, and T is the temperature.

To understand the BTBT process the energy band variation of DMSGO-TFET and DMSGO-SDP-TFET are illustrated in Fig. 2c, d respectively. The energy bandgap of the semiconductor material decreases as temperature increases, influencing device characteristics accordingly. The energy bandgap variation with temperature can be obtained using the equation [30, 32]

Where \(E_g(T)\) represents energy band gap at absolute temperature T, \(E_g(0)\) is the energy bandgap at T= 0 K, and \(\alpha \), \(\beta \) represents material-specific fitting parameters. The ON-state energy band variation with temperature ranging from 300 to 450K for DMSGO-TFET and DMSGO-SDP-TFET are illustrated in Fig. 2c, d respectively. These results demonstrate that at room temperature, a significant decrease in tunneling barrier width (\(\approx \) 4 nm) is observed at the source junction for DMSGO-SDP-TFET, which increases the inter-band tunneling rate for DMSGO-SDP-TFET as compared to conventional DMSGO-TFET. Furthermore, the impact of temperature variation is noted as very small in both devices.

Fig. 2e, f illustrate the inter-band tunneling rate with temperature ranging from 300 to 450K for DMSGO-TFET and DMSGO-SDP-TFET, respectively. The above figures show that, with temperature variation, the inter-band tunneling rate increases in both the devices as shown in the inset. Furthermore, results demonstrate that the inclusion of a low k dielectric pocket exhibits a higher tunneling rate due to a decrease in tunneling width at the source-channel junction for DMSGO-SDP-TFET compared to conventional DMSGO-TFET.

Fig. 3a, b illustrate the effect of temperature variations on \(I_\mathrm{DS}-V_\mathrm{GS}\) characteristics for conventional DMSGO-TFET and DMSGO-SDP-TFET, respectively. These figures show a smaller \(I_\mathrm{ON}\) variation with temperature for both devices because \(I_\mathrm{ON}\) depends mainly on the band-to-band tunneling instead of temperature. The temperature variations have a significant impact on the OFF-state current (\(I_\mathrm{OFF}\)) of the device because of its dependence on minority carrier concentration, which increases with temperature. It affects the reliability of the device for circuit-level applications because the switching (\(I_\mathrm{ON}\)/\(I_\mathrm{OFF}\)) ratio is highly influenced by temperature. A higher \(I_\mathrm{ON}\)/\(I_\mathrm{OFF}\) ratio results in faster switching. These results also demonstrate that the temperature dependence of DMSGO-SDP-TFET provides 0.23%/K change in \(I_\mathrm{ON}\). Whereas DMSGO-TFET provides 1.12%/K at \(V_\mathrm{GS}\) = 1.0 V. Hence, the \(I_\mathrm{ON}\) variation with temperature ranging from 300 to 450K is 0.89%/K lesser for the DMSGO-SDP-TFET as compared to conventional DMSGO-TFET. This indicates that DMSGO-SDP-TFET is more resistant to temperature compared to DMSGO-TFET. Furthermore, because of the dielectric pocket, DMSGO-SDP-TFET has a higher \(I_\mathrm{ON}\) than DMSGO-TFET. From the \(I_\mathrm{DS}\) \(-\) \(V_\mathrm{GS}\) characteristics shown in Fig. 3a, b various device parameters such as \(I_\mathrm{ON}\), \(I_\mathrm{ON}\)/\(I_\mathrm{OFF}\), \(\mathrm {SS}_\mathrm{avg}\) and \(V_\mathrm{TH}\) are extracted, presented in Tables 2 and 3.

The comparative threshold voltage (\(V_\mathrm{TH}\)) variation with temperature using the constant current method for conventional DMSGO-TFET and DMSGO-SDP-TFET is shown in Fig. 4a. The results reveal that \(V_\mathrm{TH}\) decreases for both devices as temperature increases. Moreover, DMSGO-SDP-TFET exhibits minimum \(V_\mathrm{TH}\) because of reduced tunneling width, and the temperature dependency of DMSGO-SDP-TFET exhibits 0.095%/K change in \(V_\mathrm{TH}\), whereas it exhibits 0.069 %/K change for DMSGO-TFET. Hence, the \(V_\mathrm{TH}\) variation with temperature ranging from 300 to 450K is 0.026 %/K higher for DMSGO-SDP-TFET compared to DMSGO-TFET. Hence, a substantial increase in drain current is observed at lower \(V_\mathrm{GS}\) in the proposed DMSGO-SDP-TFET as shown in the transfer characteristics.

Fig. 4b illustrates the effect of temperature variation on the average subthreshold swing (\(\mathrm {SS}_\mathrm{AVG}\)) for conventional DMSGO-TFET and DMSGO-SDP-TFET. The \(\mathrm {SS}_\mathrm{AVG}\) is formulated using the expression [6].

The subthreshold swing is inversely proportional to the steepness of \(I_\mathrm{DS}-V_\mathrm{GS}\) characteristics curve in the subthreshold region. Fig.4b shows that \(\mathrm {SS}_\mathrm{AVG}\) for both devices increases as the temperature rises due to an increase in OFF-state current. Moreover, temperature dependency of DMSGO-SDP-TFET provides 0.28%/K change in \(\mathrm {SS}_\mathrm{AVG}\), whereas it exhibits 0.32%/K change for DMSGO-TFET. Hence, \(\mathrm {SS}_\mathrm{AVG}\) variation with temperature ranging from 300 to 450K is 0.04%/K lower for DMSGO-SDP-TFET due to narrow tunneling barrier width at the source-channel junction.

3.2 Temperature sensitivity analysis of analog/radio frequency performance

This section presents the temperature dependence of various analog/radio frequency performance parameters such as \(g_{m}\), \(f_T\), GBP, \(f_\mathrm{max}\),TFP, \(\tau \) for conventional DMSGO-TFET and the proposed DMSGO-SDP-TFET.

The parasitic capacitances (\(C_\mathrm{gs}\) and \(C_\mathrm{gd}\)) are crucial parameters to analyze the analog/radio frequency and linearity performance of the device. In this regard, Fig. 5a, b illustrate the \(C_\mathrm{gs}\) variation with \(V_\mathrm{GS}\) at the temperature range from 300 to 450K for DMSGO-TFET and DMSGO-SDP-TFET, respectively. A significant decrease in \(C_\mathrm{gs}\) with increasing temperature in both the devices because the potential barrier at Source channel interface increases with temperature. Similarly, Fig. 5c, d illustrate the \(C_\mathrm{gd}\) variation for both the devices, respectively. As the thermally generated charge carriers in the channel region increase the inversion layer. The potential barrier across the drain channel interface decreases as temperature increases. Hence, \(C_\mathrm{gd}\) increases at higher gate bias in both the devices. Also, a similar trend is reported in [29]

Transconductance (\(g_{m}\)) is one of the most crucial parameters when evaluating a device for its analog/radio frequency and linearity performance. Therefore, higher \(g_{m}\) results in achieving higher gain, \(f_{T}\) and GBP in the design of analog circuits [31]. In this regard, Fig. 5e, f illustrate the \(g_{m}\) variation with temperature for DMSGO-TFET and DMSGO-SDP-TFET, respectively. It is evident from the results in the subthreshold region \(g_{m}\) of both the devices are very small and it starts increasing due to a steep rise in the ON-state current. However, it starts decreasing after a particular value of \(V_\mathrm{GS}\) because of mobility degradation [32]. The results also reveal that, with increasing temperature, a peak of \(g_{m}\) is shifted more towards lower \(V_\mathrm{GS}\) in DMSGO-SDP-TFET which means that a lower \(V_{GS}\) is needed to achieve better analog/radio frequency performance as compared to DMSGO-TFET. Moreover, DMSGO-SDP-TFET exhibits 0.37%/K variation in \(g_{m}\) for temperature ranging from 300 to 450K at \(V_\mathrm{GS}\) = 0.75 V, whereas for the same biasing conditions and temperature range DMSGO-TFET exhibits 0.55 %/K variation. Hence, \(g_{m}\) of DMSGO-SDP-TFET exhibits better immunity to temperature variations when compared to DMSGO-TFET. This indicates that the proposed device is appropriate for analog/radio frequency applications at higher temperatures.

Another critical parameter for evaluating the device’s analog/radio frequency performance is the cutoff frequency (\(f_{T}\)). It is defined as the frequency at which current gain becomes 0 dB [28]. It is obtained using the expression \(f_{T}= \frac{g_{m} }{2\pi ({C_\mathrm{gs}+C_\mathrm{gd}})}\). It can be noted that \(f_{T}\) depends on \(C_\mathrm{gs}\), \(C_\mathrm{gd}\) and \(g_{m}\) of the device. Fig. 6a, b depict the variation in \(f_{T}\) with \(V_\mathrm{GS}\) at temperatures ranging from 300 to 450K for DMSGO-TFET and DMSGO-SDP-TFET. As seen from Fig. 6a, b, \(f_{T}\) initially increases with \(V_\mathrm{GS}\) due to an increase in \(g_{m}\) and then decreases after a certain value of \(V_\mathrm{GS}\) due to the increased parasitic capacitances and reduced \(g_{m}\) because of mobility degradation. The results also reveal that, with increasing temperature, the peak of \(f_{T}\) is shifted more towards lower \(V_\mathrm{GS}\) in DMSGO-SDP-TFET which means that a lower \(V_\mathrm{GS}\) is needed to achieve better high-frequency performance as compared to DMSGO-TFET. Moreover, DMSGO-SDP-TFET exhibits 0.19%/K variation in \(f_{T}\) for temperature range from 300 to 450K at \(V_\mathrm{GS}\) =0.75 V, whereas for the same biasing conditions and temperature range DMSGO-TFET exhibits 0.39 %/K variation. Hence, the proposed DMSGO-SDP-TFET exhibits better immunity and reliability to temperature variations for high-frequency applications at higher temperatures when compared to DMSGO-TFET.

The GBP is another important parameter for evaluating the analog/radio frequency performance of the device. It is formulated as \(\mathrm GBP=\frac{g_m}{20\pi C_\mathrm{gd}}\). The GBP variations for DMSGO-TFET and DMSGO-SDP-TFET with \(V_\mathrm{GS}\) at the temperature range from 300 to 450K, is shown in Fig. 7a, b respectively. The results reveal that GBP of conventional DMSGO-TFET is inferior to DMSGO-SDP-TFET for the same reasons discussed earlier for the \(f_{T}\). Further, it is evident from the results as the temperature increases, GBP starts decreasing in both the devices due to mobility degradation. Also, the mobility degradation observed at lower \(V_\mathrm{GS}\) in DMSGO-SDP-TFET which means that a lower \(V_\mathrm{GS}\) is needed to achieve higher GBP as compared to DMSGO-TFET. Therefore, before the mobility degradation i.e, at \(V_\mathrm{GS}\) =0.75 V and temperature range from 300 to 450K, in terms of %/K variation DMSGO-TFET exhibits 0.27 %/K variation in GBP and DMSGO-SDP-TFET exhibits 0.09%/K. Hence, the proposed DMSGO-SDP-TFET shows better immunity to temperature variations compared to DMSGO-TFET.

Another crucial parameter for the analog/radio frequency performance evaluation of the device is the maximum oscillating frequency (\(f_\mathrm{max}\)). It is obtained as \(f_\mathrm{max}=\sqrt{\frac{f_T}{8\pi C_\mathrm{gd}R_\mathrm{gd}}}\). Fig. 7c, d illustrate the \(f_\mathrm{max}\) variation with \(V_\mathrm{GS}\) at temperature ranges from 300 to 450K for DMSGO-TFET and DMSGO-SDP-TFET, respectively. It is evident from the results, due to higher \(f_{T}\), \(f_\mathrm{max}\) of DMSGO-SDP-TFET is greater than that of DMSGO-TFET. Furthermore, as temperature rises, \(f_\mathrm{max}\) in both devices begins to fall due to a decrease in \(f_{T}\) caused by mobility degradation. Further, mobility degradation started at lower \(V_\mathrm{GS}\) in DMSGO-SDP-TFET which means that a lower \(V_\mathrm{GS}\) is needed to achieve higher \(f_\mathrm{max}\) as compared to DMSGO-TFET. Therefore, before the mobility degradation i.e, at \(V_\mathrm{GS}\) =0.75 V, and temperature range from 300 to 450K, in terms of %/K variation for \(f_\mathrm{max}\), DMSGO-TFET exhibits 0.104 %/K variation and DMSGO-SDP-TFET exhibits 0.075%/K. Hence, the proposed DMSGO-SDP-TFET shows better immunity to temperature variations and exhibits better analog/radio frequency performance at lower \(V_\mathrm{GS}\) and elevated temperatures compared to DMSGO-TFET.

TFP is also an important parameter to consider for the high-frequency performance assessment of the device. It is formulated as \(\mathrm TFP=\left( \frac{g_{m}}{I_\mathrm{DS}}\right) f_{T}\). Fig. 8a, b depict the TFP variation with temperature for DMSGO-TFET and DMSGO-SDP-TFET, respectively. It is evident from the results, for both devices, TFP increases linearly up to a certain value of \(V_\mathrm{GS}\) due to increased \(g_{m}\). After reaching its peak value, it begins to fall due to a decrease in \(g_{m}\) and increased parasitic capacitance. The results also reveal that, as the temperature rises, the TFP of both devices falls due to a decrease in \(f_{T}\) and \(g_{m}\) because of mobility degradation. Moreover, the results also reveal that at \(V_\mathrm{GS}\) = 0.75 V and temperature range 300 to 450K, in terms of %/K variation, DMSGO-TFET exhibits 0.32 %/K variation in TFP and the proposed DMSGO-SDP-TFET exhibits 0.13%/K. Hence, the proposed DMSGO-SDP-TFET shows better immunity to temperature variations compared to conventional DMSGO-TFET.

The transit time (\(\tau \)) is another important parameter for the radio frequency performance assessment of the device. It is defined as the time taken by the device to transfer the carriers from source to drain region [24]. It is formulated as \(\tau = \frac{1}{2\pi 10{f_{T}}}\). From the above expression, it is evident that transit time depends on \(f_{T}\). Fig. 8c, d depict the transit time varies with temperature for DMSGO-TFET and DMSGO-SDP-TFET, respectively. From Fig. 8c, it can be seen that with increasing \(V_\mathrm{GS}\), \(\tau \) decreases in both devices, whereas in the case of DMSGO-SDP-TFET shown in Fig. 8d after a certain \(V_\mathrm{GS}\) transit time starts increasing due to decrease in \(f_{T}\) because of mobility degradation. Moreover, the results also reveal that the effect of temperature variations on conventional DMSGO-TFET is negligible, whereas DMSGO-SDP-TFET exhibit significant variation in transit time. Finally, the temperature sensitivity of different device parameters in % per kelvin for conventional DMSGO-TFET and the proposed DMSGO-SDP-TFET are presented in Table 2, and the performance of the proposed device is compared to recent literature in Table 3.

3.3 Temperature sensitivity analysis of linearity and distortion figure of merits

In this section, the impact of temperature variations on the linearity and distortion performance parameters for conventional DMSGO-TFET and the proposed DMSGO-SDP-TFET have been analyzed. In this regard, various linearity and distortion parameters such as \(g_{m3}\), VIP3, IIP3, and IMD3 are considered for analysis. These parameters are defined as follows [31].

Where \(R_S\) is assumed to be 50 \(\Omega \) for most RF applications. To obtain better linearity and minimum distortion VIP3, IIP3 parameters of the device should be higher, and IMD3 parameter must be lower [26, 31]. Fig. 9a, b illustrate the impact of temperature variations ranging from 300 to 450K on higher-order transconductance (\(g_{m3}\)) for DMSGO-TFET and DMSGO-SDP-TFET, respectively. It is evident from the above figures that \(g_{m3}\) variation is negligible at lower \(V_\mathrm{GS}\) for both devices. Moreover, the results also reveal that DMSGO-SDP-TFET is more sensitive to temperature variations at higher gate voltage compared to DMSGO-TFET.

A device with a higher value of VIP3 shows better linearity [25, 31]. Here, Fig. 9c, d illustrate VIP3 variation with \(V_{GS}\) at a different temperature ranging from 300 to 450K for DMSGO-TFET and DMSGO-SDP-TFET, respectively. It is evident from the results VIP3 of the proposed DMSGO-SDP-TFET is higher and shows better linearity compared to DMSGO-TFET. Further, the results also reveal that both the devices are temperature sensitive for higher \(V_\mathrm{GS}\).

The impact of temperature variations on the IIP3 for DMSGO-TFET and DMSGO-SDP-TFET are illustrated in Fig. 10a, b respectively. It is evident from the results that IIP3 of the proposed DMSGO-SDP-TFET is higher than DMSGO-TFET, this increase in the IIP3 parameter indicates improvement in the linearity performance of the device. Therefore, DMSGO-SDP-TFET shows better linearity compared to DMSGO-TFET. Further, the results also reveal that as the temperature increases from 300 to 450K, both the devices are temperature sensitive at lower and higher \(V_\mathrm{GS}\).

A lower IMD3 parameter indicates that the device can withstand higher distortions [31]. In this regard, Fig. 10c, d illustrate the IMD3 variation with temperature. Results demonstrate that DMSGO-SDP-TFET exhibits 0.10%/K variation in IMD3 with temperature ranging from 300 to 450K at \(V_\mathrm{GS}\) = 1.2 V and \(V_\mathrm{DS}\) = 1.0 V, whereas, for the same operating temperature and biasing conditions, DMSGO-TFET exhibits 0.41 %/K variation. Hence, DMSGO-SDP-TFET shows better intermodulation distortion performance and more reliable to temperature variations as compared to conventional DMSGO-TFET.

4 Conclusions

A comparative temperature sensitivity analysis of DC, analog/radio frequency, linearity, and distortion performance has been carried out for conventional DMSGO-TFET and the proposed DMGOSDG-TFET at the temperature ranging from 300 to 450K. Based on this study, it can be stated that for the same biasing conditions and temperature range, the DC, analog/radio frequency, and linearity performance parameters of the proposed DMSGO-SDP-TFET are less sensitive to the temperature variation compared to conventional DMSGO-TFET. Further, the results summarized in Table 2 in % variation per kelvin, and Table 3 performance comparison with recent literature indicate that DMSGO-SDP-TFET is more reliable when compared to DMSGO-TFET. Hence, it can be concluded that the proposed DMSGO-SDP-TFET is a better choice for low power switching and analog/radio frequency applications for elevated temperature range .

Data availability

All the data taken from another resource has been given the corresponding reference. The data, for which reference is not provided, is the original data.

Code availability

The code has been implemented using technology computer-aided design (TCAD) tool.

References

Young, K.K.: Short-channel effect in fully-depleted SOI MOSFETs. IEEE Trans. Electron Devices 36(2), 399–402 (1989)

Bangsaruntip, S., Cohen, G.M., Majumdar, A., Sleight, J.W.: Universality of short-channel effects in undoped-body silicon nanowire MOSFETs. IEEE Trans. Electron Devices 31(9), 903–905 (2010)

Choi, W.Y., Park, B., Lee, J.D., Liu, T.K.: Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Lett. 28(8), 743–745 (2007)

Saurabh, S., Kumar, M.J.: Novel attributes of a dual material gate nanoscale tunnel field-effect transistor. IEEE Trans. Electron Devices 58(2), 404–410 (2010)

Pal, A., Sachid, A.B., Gossner, H., Rao, V.R.: Insights into the design and optimization of tunnel-FET devices and circuits. IEEE Trans. Electron Devices 58(4), 1045–1053 (2011)

Boucart, K., Ionescu, A.M.: Double gate tunnel FET with high k gate dielectric. IEEE Trans. Electron Devices 54(7), 1725–1733 (2007)

Ionescu, A.M., Riel, H.: Tunnel field-effect transistors as energy efficient electronic switches. Nature 479(7373), 329–337 (2011)

Lee, M.J., Choi, W.Y.: Effects of device geometry on hetero-gate-dielectric tunneling field-effect transistors. IEEE Electron Device Lett. 33(10), 1459–1461 (2012)

Jain, P., Prabhat, V., Ghosh, B.: Dual metal-double gate tunnel field-effect transistor with mono/hetero dielectric gate material. J. Comput. Electron. 14(2), 537–542 (2015)

Kale, S., Kondekar, P.N.: Charge plasma-based source/drain engineered Schottky Barrier MOSFET: Ambipolar suppression and improvement of the RF performance. Superlattices Microstruct. 113, 799–809 (2018)

Vijayvargiya, V., Vishvakarma, S.K.: Effect of drain doping profile on double-gate tunnel field-effect transistor and its influence on device RF performance. IEEE Trans. Nanotechnol. 13(5), 974–981 (2014)

Vivek Anand, I., Arun Samuel, T.S., Vimala, P.: Modeling and simulation of a dual-material asymmetric heterodielectric-gate TFET. J. Comput. Electron. 19, 1450–1462 (2020). https://doi.org/10.1007/s10825-020-01563-w

Raad, B.R., Sharma, D., Nigam, K., Kondekar, P.: Group III-V ternary compound semiconductor materials for unipolar conduction in tunnel field-effect transistors. J. Comput. Electron. 16(1), 24–29 (2017)

Kale, S., Kondekar, P.N.: Ferroelectric Schottky barrier tunnel FET with gate-drain underlap: Proposal and investigation. Superlattices Microstruct. 89, 225–230 (2016)

Kondekar, P.N., Nigam, K., Pandey, S., Sharma, D.: Design and analysis of polarity controlled electrically doped tunnel FET with bandgap engineering for analog/RF applications. IEEE Trans. Electron Devices 64(2), 412–418 (2017)

Loan, S.A., Rafat, M.: A high-performance inverted- C tunnel junction FET with source-channel overlap pockets. IEEE Trans. Electron Devices 65(2), 763–768 (2018)

Kale, S., Kondekar, P.N.: Design and investigation of dielectric engineered dopant segregated Schottky Barrier MOSFET With NiSi source/drain. IEEE Trans. Electron Devices 64(11), 4400–4407 (2017)

Rawat, G., Talukdar, J., Mummaneni, K.: A Novel Extended Source TFET with \(\delta \)p\(^+\) - SiGe Layer. Silicon 12, 2273–2281 (2020)

Kumar, S., Singh, S., Nigam, K., Tikkiwal, V.A.: Dual material dual-oxide dual-gate TFET for improvement in DC characteristics, analog/RF and linearity performance. Appl. Phys. A 125(5), 3531–3538 (2019)

Joshi, T., Singh, Y., Singh, B.: Extended-source double-gate tunnel FET with improved DC and analog/RF performance. IEEE Trans. Electron Devices 67(4), 1873–1879 (2020)

Nigam, K.: Low-K dielectric pocket and workfunction engineering for DC and analog/RF performance improvement in dual material stack gate oxide double gate TFET. Silicon 13, 2347–2356 (2020)

Chandan, B.V., Gautami, M., Nigam, K., Sharma, D., Tikkiwal, V.A., Yadav, S., Kumar, S.: Impact of a metal-strip on a polarity-based electrically doped TFET for improvement of DC and analog/RF performance. J. Comput. Electron. 18(1), 76–82 (2018)

Raad, B.R., Nigam, K., Sharma, D., Kondekar, P.: Dielectric and work function engineered TFET for ambipolar suppression and RF performance enhancement. Electron. Lett. 52(9), 770–772 (2016)

Nigam, K., Kondekar, P.N., Sharma, D.: Approach for ambipolar behavior suppression in tunnel FET by workfunction engineering. IET Micro Nano Lett. 11(8), 460–464 (2016)

Nigam, K., Pandey, S., Kondekar, P., Sharma, D., Parte, P.K.: A barrier controlled charge plasma-based TFET with gate engineering for ambipolar suppression and RF/linearity performance improvement. IEEE Trans. Electron Devices 64(6), 2751–2757 (2017)

Madan, J., Chaujar, R.: Temperature-associated reliability issues of heterogeneous gate dielectric gate all around Tunnel FET. IEEE Trans. Nanotechnol. 17(1), 41–48 (2018)

Paras, N., Chauhan, S.S.: Temperature sensitivity analysis of vertical tunneling based dual metal Gate TFET on analog/RF FOMs. Appl. Phys. A 125, 316 (2019)

Nigam, K., Pandey, S., Kondekar, P.N., Sharma, D., Parte, P.K.: Temperature sensitivity analysis of polarity controlled electrostatically doped tunnel field-effect transistor. Superlattices Microstruct. 97, 598–605 (2016)

Singh, P., Yadav, D.S.: Impact of temperature on analog/RF, linearity and reliability performance metrics of tunnel FET with ultra-thin source region. Appl. Phys. A 127, 1–15 (2020)

Kumar, S.: Temperature dependence of analogue/RF performance, linearity, and harmonic distortion for dual-material gate-oxide-stack double-gate TFET. IET Circuits Devices Syst. (2021). https://doi.org/10.1049/cds2.12049

Ghosh, P., Haldar, S., Gupta, R.S., Gupta, M.: An investigation of linearity performance and intermodulation distortion of GME CGT MOSFET for RFIC design. IEEE Trans. Electron Devices 59(12), 3263–3268 (2012)

Varshni, Y.P.: Temperature dependence of the energy gap in semiconductors. Physica 34(1), 149–154 (1967)

Tripathy, M.R., Singh, A.K., Baral, K., Singh, P.K., Jit, S.: III-V/Si staggered heterojunction-based source-pocket engineered vertical TFETs for low power applications. Superlattice Microstruct. 142, 106494 (2020)

Shaikh, M.R.U., Loan, S.A.: drain-engineered TFET with fully suppressed ambipolarity for high-frequency application. IEEE Trans. Electron Devices 66(4), 1628–1634 (2019)

Yadav, S., Sharma, D., Soni, D., Aslam, M.: Controlling ambipolarity with improved RF performance by drain/gate work function engineering and using high K dielectric material in electrically doped TFET: proposal and optimization. J. Comput. Electron. 16, 721–731 (2017)

Chauhan, S.S.: Design of double gate vertical tunnel field-effect transistor using HDB and its performance estimation. Superlattice Microstruct. 117, 1–8 (2018)

Funding

The authors did not receive any financial support from any agency/organization for this work.

Author information

Authors and Affiliations

Contributions

KN, SK and DN contributed equally to the design, analysis of the results, and writing of the manuscript.

Corresponding author

Ethics declarations

Conflict of interest

No conflicts of interest.

Ethical standard

The manuscript follows all the ethical standards, including plagiarism.

Consent to participate

Yes.

Consent for publication

Yes.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Nigam, K., Kumar, S. & Dharmender Temperature sensitivity analysis of dual material stack gate oxide source dielectric pocket TFET. J Comput Electron 21, 802–813 (2022). https://doi.org/10.1007/s10825-022-01902-z

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-022-01902-z