Abstract

This article proposes a novel device structure of electrically doped tunnel FET with drain/gate work function engineering by using hetero-dielectric material for the suppression of ambipolar behavior with improved DC and RF characteristics. For this, a P–I–N type structure was formed over an intrinsic silicon wafer by applying negative and positive voltages to create source and drain regions, respectively. Formation of source and drain regions by the concept of electrical doping is useful for reduction of random doping fluctuations and fabrication complexity. For suppression of ambipolar behaviour, the drain electrode is split into two different metal work functions (\(\phi _\mathrm{DE1}\) < \(\phi _\mathrm{DE2}\)), which alters the carrier concentration and increases the tunneling barrier at the drain/channel interface. Consequently, the proposed modification in terms of dual work functionality at the drain terminal offers better performance in terms of suppression of negative conductance (ambipolar current) and parasitic capacitances. However, the presence of dual work functionality at the drain electrode causes degradation in ON-state current and RF figures of merit. To resolve these problems, the control gate electrode is further split into two different work functions and uses hetero gate dielectric material, where the gate work function near the source/channel interface is greater than the gate work function near the drain/channel interface. It assists tunneling of carriers at the source/channel junction and improves ON-state current with RF performance. Apart from this, the use of hetero gate dielectric material provides further enhancement in DC and high frequency behaviour of the device.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

In the new era of technology, the tunnel field effect transistor (TFET) has various advantages over the MOSFET in low power applications. TFET posses steep slope in conduction state (subthreshold swing <60 mV/dec.), immune to short channel effects (SCEs) such as threshold roll-off and low OFF-state current [1, 2]. TFET holds these technical advantages because the flow of charge carriers is based on a quantum tunneling mechanism, which makes it a radical device and a potential replacement for conventional MOSFET [3]. But, due to miniaturization of the device dimensions, it is recently reported that process variation [random doping fluctuations (RDFs)] have become significant at the nano scale, which results in OFF-state current running unacceptably high and degrading the device performance due to reduction of abruptness at the source/channel junction [4,5,6]. In the case of TFET, an abrupt junction is indispensable for efficient tunneling at the source/channel interface, but it is difficult to maintain, since diffusion of dopant atoms at source/channel and drain/channel interface results in degradation of device performance [7, 8].

Thus, the introduction of charge plasma [9, 10], junctionless [11,12,13,14] and electrically doped [15,16,17,18] concepts are helpful for providing an abrupt junction profile, reduction in RDFs and fabrication complexity with cost effectiveness. In the case of charge plasma TFET (CP-TFET), the formation of source and drain regions is performed by the deposition of appropriate work function metal [19]. CP-TFET achieves these benefits, but the presence of a barrier between a gate and a source electrode at source/channel interface is responsible for severe degradation in ON-state current in comparison to physically doped TFET [20]. In this regard, the formation of junctionless TFET (JL-TFET) by using an N+ doped parent substrate improves the ON-state current, subthreshold slope and threshold voltage due to presence of an N+ doped pocket layer near the source/channel junction [11], but this approach retains the issues related to physically doped TFET [8, 21, 22]. Further, the use of group III–V materials in hetero junctionless TFET enhances the electrical characteristics (\(I_\mathrm{ON}\), SS and \(V_\mathrm{th}\)) of the device, containing the issues related to lattice mismatch [25, 26]. Apart from these, performance of JL-TFET is poor with respect to CP-TFET in terms of RDFs, fabrication complexity and capital investment. Hence, investigation of TFET by the electrically doped mechanism [15, 18, 23], in contrast to CP-TFET, is more beneficial for formation of better abrupt source/channel and drain/channel junctions. Electrically doped TFET architecture is also useful for overcoming the fabrication challenges of physically doped TFET and JL-TFET with low fabrication cost. It also possess ambipolar conduction due to prevention of Gaussian doping profile in the drain regions, low ON-state current, high parasitic capacitance, and poor high frequency figures of merit as CP-TFET and JL-TFET. In this paper, we use the dual work function concept at the drain electrode in electrically doped TFET for the first time to suppress ambipolar behaviour and parasitic capacitances. The presence of work function engineering at the gate electrode with hetero dielectric material enhances the ON-state current and RF performance of the device. The proposed device has the advantage of a dopingless substrate, which involves a simple fabrication process similar to conventional ED-DL-TFET. Although the proposed device, DMDG-ED-DL-TFET, has some different and complex fabrication steps because of the dual metal drain and gate electrodes with hetero dielectric material, advanced nanolithography techniques make it possible. Atomic layer deposition (ALD) and ion beam deposition (IBD) facilitate a single atom layer with complete control over deposition in one cycle. ALD provides pinhole-free deposition with a wide variety of oxides [27] (Al\(_{2}\)O\(_{3}\), HfO\(_{2}\), SiO\(_{2}\), TiO\(_{2}\), SrTiO\(_{3}\), Ta\(_{2}\)O\(_{5}\)) over silicon, InAs, etc. Apart from these due to the incompatibility of poly-silicon electrodes with high \(\kappa \) dielectric and downscaling, metal gates once again came into the picture [28]. By ALD, two different work function metals on the drain and gate electrodes can be integrated on the same wafer, which leads to fabrication simplicity [29]. From fa abrication point of view, we have considered molybdenum (Mo) as gate electrode because it possesses low resistivity \(5\times 10^{-6}\;\Omega \) cm, high melting temperature (2600 \(^{\circ }\hbox {C}\)) and a work function adjustable by nitrogen doping. By increasing the nitrogen implantation, a low work function can be achieved through Mo, and it facilitates dual work functionality of any length on the same metal [30]. In addition to this dual work function, metal can be deposited by the technique of interdiffusion of two metals [31].

This paper is organized as follows: the device description and simulation tactics are presented in Sect. 2. Section 3 depicts the DC characteristic of the proposed device, the Dual metal drain gate electrically doped-dopingless TFET (DMDG-ED-DL-TFET), along with the conventional devices, the electrically doped-dopingless TFET (ED-DL-TFET) and the dual metal drain electrically doped-dopingless TFET (DMD-ED-DL-TFET). Section 4 shows a comparative analysis of different RF parameters of these devices. The optimization of control gate work function (\(\phi _\mathrm{CG2}\)) and spacer length between gate and source (\(L_\mathrm{GS}\)) are discussed in Sect. 5. Finally, the important findings are covered in the conclusion, Sect. 5.

2 Device structure and simulation setup

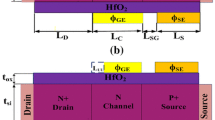

Figure 1a–c shows the cross sectional view of devices ED-DL-TFET, DMD-ED-DL-TFET and DMDG-ED-DL-TFET. An intrinsic silicon wafer is used as a substrate for all the devices. Source and drain regions were created by applying −1.2 V to create the P+ region and +1.2 V to create the N+ region, respectively, to develop a P–I–N type structure over the intrinsic silicon film [17]. A thin layer of oxide is grown to prevent the formation of silicide between the semiconductor and the metal electrodes over the source and drain regions [18, 19].

Nickel silicide (NiSi) has a near-mid-band gap metal work function, which is used for source and drain contacts with 0.45 eV barrier height [16, 17]. From these specifications, Fig. 1a is designated as ED-DL-TFET; further dual metal work function is applied at the drain electrode of the conventional ED-DL-TFET to form a DMD-ED-DL-TFET as shown in Fig. 1b. Dual drain work function and gate work function engineering are brought together with hetero-dielectric ,i.e. HfO\(_{2}\), in DMDG-ED-DL-TFET as depicted in Fig. 1c. Device dimensions and other structural parameters used in the simulation are given in Table 1.

All the electrical characteristic simulations were carried out by 2D ATLAS device simulator [24]. The models used to process the simulations were as follows:

-

Auger recombination model

-

Band to band tunneling model

-

Shockley Read Hall recombination model

-

Fermi–Dirac statistical model

The universal Schottky tunneling model was also incorporated into the simulation models because nickel silicide (NiSi) was used for drain and source contacts.

3 Results and discussion

This section describes the performance and comparison of all the devices (Fig. 1a–c) in terms of energy band levels, DC characteristics and analog/RF performance.

3.1 DC characteristics

The electrically doped tunnel FET is structurally the same as the classical gated P–I–N structure, except in the formation of drain and source regions, which are created by applying positive and negative voltages over the drain and source regions, respectively. In this regard, +1.2 V and −1.2 V were applied to the drain electrode (DE) and the source electrode (SE), respectively, and were kept constant; only the gate to source voltage (\(V_\mathrm{GS}\)) varied during device operations. The comparison of ED-DL-TFET, DMD-ED-DL-TFET with the proposed device, DMDG-ED-DL-TFET, in terms of electric field, energy band diagram and electron hole concentration is shown in Fig. 2a–c.

DMD-ED-DL-TFET and DMDG-ED-DL-TFET both imply dual work function metals at the drain electrode (Fig. 1b–c), whereas DMDG-ED-DL-TFET consists of dual work functions at the gate electrode along with hetero dielectric from gate to source. The impact of introducing dual work functions can be seen in Fig. 2a, which shows the electric field under thermal equilibrium conditions. It characterises a low electric field under the drain section DE2, because of its higher work functon (\(\phi _\mathrm{DE2}\)), which means it would offer a large barrier for tunneling of charge carriers at the drain/channel junction. Further, Figs. 2b, c show the energy band diagram and carrier concentration of devices in equilibrium. Figure 2b shows significant uplift in the energy bands under DE2 for DMD-ED-DL-TFET and DMDG-ED-DL-TFET, compared with conventional ED-DL-TFET, which shows reduction in electron concentration as given by Fig. 2c. This change in carrier concentration (electrons) results in a significant rise in the energy bands in the ambipolar-state, as can be seen in Fig. 2d; thus the tunneling rate reduces due to a wider tunneling width as depicted in Fig. 3. Here it is observed that DMD-ED-DL-TFET and DMDG-ED-DL-TFET exhibit lower hole tunneling rates due to the presence of dual work functions at the drain electrode in ambipolar state.

Once again, by inspection of Fig. 2a, a high electric field is observed (which supports the higher electron tunneling rate) for DMDG-ED-DL-TFET under the control gate2 (CG2). Figure 2b i.e. the energy band diagram in thermal equilibrium shows band bending or a decrement in the energy levels under CG2. CG2 in DMDG-ED-DL-TFET is strategically placed near the source/channel interface, so that more electrons accumulate in channel region as shown in Fig. 2c. So from Fig. 2b, c, it can be asserted that the presence of CG2 reduces the tunneling width due to an increase in the carrier concentration, which in turn increases the ON-state current (Fig. 4a).

a Electric field variation as a function of length for different device structures in equilibrium, b energy band profile versus length for different device structures in equilibrium, c carrier concentration versus length for different device structures in equilibrium and d energy band profile versus length for different device structures in the ambipolar state

Drain work function engineering reduces the ambipolar current drastically up to the level of the OFF-state current in the DMD-ED-DL-TFET, for a range of negative gate-to-source voltages (0 V \(\ge \) \({V}_\mathrm{GS}\) \(\ge -1.5\) V), as shown in Fig. 4a. But, at the same time, from the same figure, it is observed that the DMD-ED-DL-TFET suffers from a low ON-state current while suppressing ambipolarity, which is resolved in the DMDG-ED-DL-TFET by gate work function engineering and by using high \(\kappa \) dielectric material. From Fig. 4b, we can see drain current as a function of \(V_\mathrm{DS}\) for different values of \(V_\mathrm{GS}\). Initially, drain current increases for small values of \(V_\mathrm{DS}\), but after a certain drain voltage, drain current becomes independent and gets saturated. Further, from the same figure, it is noticed that DMDG-ED-DL-TFET has higher drain current and an earlier saturation point as compared to ED-DL-TFET and DMD-ED-DL-TFET, because of gate work function engineering. Moreover it has been found that DMD-ED-DL-TFET has low drain current as compare to ED-DL-TFET for \({V}_\mathrm{GS} = \) (1 and 1.5 V), due to work function engineering at the drain electrode (DE2). From this discussion, it is clear that two phenomena (gate work function and hetero dielectric engineering) in the DMDG-ED-DL-TFET with drain metal engineering are highly effective for enhancing ON-state current as well as suppressing ambipolar current, without any reliability issues. A comparative study of DC parameters is shown in Table 2.

3.2 Analog/RF analysis

In the present scenario, analog/RF performance is a crucial issue due to the need for low power but high frequency devices, which is a critical trade-off for device performance. Fundamental characteristics for interpreting analog performance of the device include parameters such as transconductance (\(g_{m}\)), output transconductance (\(g_\mathrm{ds}\)), gate-to-drain capacitance (\(C_\mathrm{gd}\)), cut-off frequency (\(f_\mathrm{T}\)), gain bandwidth product(GBP), transit time (\(\tau \)), intrinsic gain (IG), maximum oscillating frequency (\(f_\mathrm{max}\)), early voltage (\(V_\mathrm{A}\)) and transconductance generation factor (TGF). Transconductance is defined as the ability of a device to transform gate-to-source voltage into drain current. Transconductance \(g_{m}\) behaves as an increasing function for initial values of \(V_\mathrm{GS}\), but further increments in \(V_\mathrm{GS}\) cause degradation in \(g_{m}\) because of mobility saturation of carriers (electrons). When \(V_\mathrm{GS}\) increases beyond 0.37 V, in the case of DMDG-ED-DL-TFET, \(g_{m}\) starts increasing and attains peak value near about 0.8 V of \(V_\mathrm{GS}\), as shown in the Fig. 5a.

High \(\kappa \) dielectric used for half-length of the device from gate-to-source side, which also helps to improve \(g_{m}\) for DMDG-ED-DL-TFET due to efficient coupling of \(V_\mathrm{GS}\). Apart from these, DMD-ED-DL-TFET has lower \(g_{m}\) than ED-DL-TFET due to work function engineering at the drain electrode. Figure 5b shows output transconductance (\(g_\mathrm{ds}\)), which is the inverse of output resistance and is defined as \(g_\mathrm{ds} = \partial I_\mathrm{DS}/\partial V_\mathrm{DS}\) (A/V), where \(I_\mathrm{DS}\) is drain current and \(V_\mathrm{DS}\) is drain voltage. From the same figure, we can observe that initially \(g_\mathrm{ds}\) increases as a function of \(V_\mathrm{DS}\) and, after a certain voltage, it falls with \(V_\mathrm{DS}\). DMDG-ED-DL-TFET achieves higher values of \(g_\mathrm{ds}\) as compared to both ED-DL-TFET and DMD-ED-DL-TFET, due to flow of sufficient carriers from source to drain the region. In addition to these, DMD-ED-DL-TFET has poorer \(g_\mathrm{ds}\) than ED-DL-TFET because of lower drain current. Gate-to-drain capacitance (\(C_\mathrm{gd}\)) is Miller capacitance and its accurate analysis is very important for designing high frequency circuits, since \(C_\mathrm{gd}\) behaves as parasitic capacitance for lower values of \(V_\mathrm{GS}\), but for higher values of \(V_\mathrm{GS}\), it behaves as inversion capacitance (\(C_\mathrm{gd,inv}\)) [32, 33]. Both types of gate-to-drain capacitance should be as low as possible to improve switching speed of the TFET. Higher work function (\(\phi _\mathrm{DE2}\)) drain electrode DE2, causes abruptness in drain doping profile at the drain/channel interface and reduces gate-to-drain coupling, due to the fact that \(C_\mathrm{gd}\) trims down drastically in the case of DMDG-ED-DL-TFET, as compared to ED-DL-TFET , asshown in the Fig. 5c. However, it can be seen from the same figure that \(C_\mathrm{gd}\) of the DMDG-ED-DL-TFET is slightly greater than that of DMD-ED-DL-TFET, due to the high \(\kappa \) dielectric near the gate/source junction, but it is negligible. Cut-off \(\hbox {frequency}(f_\mathrm{t}\)) or unity gain frequency is defined as the frequency at which short circuit current gain of the device in the common source configuration becomes unity [15]. It is formulated as

Figure 5d shows the variation in \(f_\mathrm{t}\) as a function of \(V_\mathrm{GS}\). Note that \(f_\mathrm{t}\) increases with \(V_\mathrm{GS}\) because of increments in \(g_{m}\). With further increases in \(V_\mathrm{GS}\), \(f_\mathrm{t}\) starts falling because of some increment in \(C_\mathrm{gd}\) and degradation in carrier mobility. It can be seen from the same figure that DMD-ED-DL-TFET has a lower \(f_\mathrm{t}\) than ED-DL-TFET because DMD-ED-DL-TFET has an improved \(C_\mathrm{gd}\) but poor \(g_{m}\), which is comparatively more dominant than \(C_\mathrm{gd}\). Further, it is found that DMDG-ED-DL-TFET has greater \(g_{m}\) due to gate work function engineering, so it is clear that DMDG-ED-DL-TFET has better performance than both ED-DL-TFET and DMD-ED-DL-TFET at low \(V_\mathrm{GS}\). This indicates that the device is suitabile for a wide range of frequencies in low power applications. Another important parameter of RF analysis is gain bandwidth product (GBP), which illustrates the trade-off between gain and bandwidth for a given device and follows the same trend as \(f_\mathrm{T}\). For a certain DC gain of 10, GBP can be formulated as follows: GBP \( = g_{m}/20\pi \) (\(C_\mathrm{gd}\)). The proposed device has high GBP due to its structural configuration, including a dual metal gate and high \(\kappa \) dielectric material near the source channel junction. This reflects that the device is able to maintain gain as well as optimum bandwidth, as shown in the Fig. 6a. However, from the same figure we can see that DMDG-ED-DL-TFET has higher values of GBP as compared to ED-DL-TFET and DMD-ED-DL-TFET. In parallel with GBP and \(f_\mathrm{t}\), transit time (\(\tau \)) is also one of the significant parameters for defining the RF performance of the device; it measures the time taken by charge carriers to sweep out from the channel region. Transit time decides the switching speed of device, and is defined as \(\tau = 1/(2\pi f_\mathrm{t}\)), an equation that shows the dependency of \(\tau \) on \(f_\mathrm{t}\). Figure 6b shows the behaviour of \(\tau \) as a function of \(V_\mathrm{GS}\) for all the three structures. \(\tau \) for DMDG-ED-DL-TFET decreases rapidly with increments in \(V_\mathrm{GS}\) because \(f_\mathrm{t}\) is a function of \(V_\mathrm{GS}\); the low \(\tau \) of DMDG-ED-DL-TFET represents that the sweep time of the carriers in the channel region (below the gate electrode) is much reduced when compared to ED-DL-TFET and DMD-ED-DL-TFET.

Intrinsic gain is the product of transconductance and output resistance (\(R_\mathrm{o}\)), where \(R_\mathrm{o}\) is the dominating factor. Figure 7a shows variation of intrinsic gain (IG) with respect to \(V_\mathrm{GS}\); it depicts high IG under the subthreshold region, which then falls with \(V_\mathrm{GS}\). Below threshold voltage, \(R_\mathrm{o}\) is very high due to low drain current, but after exceeding \(V_\mathrm{th}\) TFETs fall under the influence of BTBT, which results in a sudden rise in \(g_{m}\) and a drop in \(R_\mathrm{o}\). This action results din egradation in IG with \(V_\mathrm{GS}\) [25]. DMDG-ED-DL-TFET has the highest IG at lower values of \(V_\mathrm{GS}\) as compared to other two structures. \(f_\mathrm{max}\) is the frequency at which the power gain of the device is unity; by the small signal model it can be formulated as:

From the above equation, it can be seen that \(f_\mathrm{max}\) includes \(g_{m}\), \(C_\mathrm{gd}\) and \(C_\mathrm{gs}\), which means that \(f_\mathrm{max}\) is influenced by geometrical parameters. \(f_\mathrm{max}\) rises with \(V_\mathrm{GS}\), then after achieving peak it falls; DMDG-ED-DL-TFET achieves 3250 THz of \(f_\mathrm{max}\) higher than the other two devices as shown in Fig. 7b. High transconductance and low parasitic capacitances are two main reasons for better performance of the proposed device, which indicates that DMDG-ED-DL-TFET is suitable for high frequency applications. Figure 8a shows increments in early voltage (\(V_\mathrm{A}\)) with respect to \(V_\mathrm{DS}\) in a comparative manner for three structures ED-DL-TFET, DMD-ED-DL-TFET and DMDG-ED-DL-TFET. DMDG-ED-DL-TFET shows higher \(V_\mathrm{A}\) than the other two devices, because DMDG-ED-DL-TFET has a steep subthreshold slope due to the dual metal gate and high-K dielectric material at the source/channel junction [34]. High \(V_\mathrm{A}\) results in an improvement in the low frequency open loop gain of the device.

Transconductance generation factor (TGF) refers to device efficiency in converting DC parameter (drain current) into AC parameter (\(g_{m}\)). It gives an idea of the degree to which a device optimizes drain current for efficient amplification with low power dissipation [35]. Under the subthreshold region, drain current is negligible and TGF presents the ratio of \(g_{m}\) to \(I_\mathrm{DS}\), which is why TGF has been plotted from 0.4 V (near threshold voltage) as shown in Fig. 8b. DMDG-ED-DL-TFET shows the highest TGF as compared to ED-DL-TFET and DMD-ED-DL-TFET near threshold voltage, but further increments in \(V_\mathrm{GS}\) cause a fall in TGF for all structures, because after \(V_\mathrm{th}\), the drain current increases rapidly with \(V_\mathrm{GS}\) and the drain current, rather than \(g_{m}\), behaves as the dominating factor in the case of TGF.

4 Optimization

4.1 Work function optimization of DE2

Suppression of ambipolarity without any trade-off with ON-state current requires selection of an appropriate work function. This section is dedicated to the work function optimization of DE2. Figure 9a shows the energy band diagram of the DMDG-ED-DL-TFET for different drain work functions in the ambipolar state, where upliftment of bands near the drain/channel interface can be seen with increments in \(\phi _\mathrm{DE2}\). Figure 9b shows the electric field on an enlarged scale in the ambipolar state; it presents degradation of electric field in DMDG-ED-DL-TFET under electrode DE2 as \(\phi _\mathrm{DE2}\) increases. So from Fig. 9, it can be concluded that the tunneling barrier for charge carriers increases with increments in \(\phi _\mathrm{DE2}\).

From the Fig. 10, it is seen that significant suppression of ambipolar current occurs as \(\phi _\mathrm{DE2}\) increases from 5.0 to 5.4 eV. Although for \(\phi _\mathrm{DE2}\) > 5.4 eV the ambipolar current is not much affected, it reduces the ON-state current by significant orders. So a sufficient amount of suppression is found in ambipolar current for \(\phi _\mathrm{DE2} = 5.4\) eV in DMDG-ED-DL-TFET without any compromise in the ON-state current.

4.2 Optimization of \(L_\mathrm{GS}\) along with scaling of CG2

Spacer length (\(L_\mathrm{GS}\)) is the gate-to-source electrode gap, which affects DC and AC characteristics of the device. Therefore, optimization of \(L_\mathrm{GS}\) is necessary for desired performance of the device. Variation in \(L_\mathrm{GS}\) indirectly changes the length of control gate 2 (CG2) in the case of DMDG-ED-DL-TFET. Figure 11a, b shows the energy band diagram for different spacer lengths in equilibrium and ON-state, respectively. Both the figures show increments in tunneling width as spacer length increases from 1 to 7 nm at the source/channel interface. Variation in \(L_\mathrm{GS}\) also reflects changes in the electric field, where we can see higher a electric field for \(L_\mathrm{GS} = 1\) nm and the least electric field for \(L_\mathrm{GS} = 7\) nm under the spacer length as shown in Fig. 12a. The narrow tunneling width (Fig. 11a) and high electric field for \(L_\mathrm{GS} = 1\) nm (Fig. 12a) support a higher tunneling rate at the source/channel interface, so that ON-state current becomes optimum. Figure 12b shows the drain current versus the gate-to-source voltage characteristic for different \(L_\mathrm{GS}\) values. This indicates that a change in \(L_\mathrm{GS}\) does not affect the ambipolar current, but it causes a reduction in the ON-state current. For \(L_\mathrm{GS}= 1\) and 3 nm, ON-state current shows negligible changes, but as \(L_\mathrm{GS}\) increases (\({L}_\mathrm{GS}>3\) nm), drastic suppression can be seen in ON-state current.

Similarly, we have plotted tarnsconductance as function of \(V_\mathrm{GS}\) for different \(L_\mathrm{GS}\) values as shown in Fig. 13. It is found that maximum \(g_{m}\) is achieved for \(L_\mathrm{GS} =\) 1 nm, which then decreases with further increments of \(L_\mathrm{GS}\). Overall results of this optimization section are presented in Table 3, which shows the variation in several DC and AC characteristics due to changes in spacer length along with scaling of CG2.

4.3 Performance analysis of DMDG-ED-DL-TFET at \({L}_\mathrm{GS} = 5\) nm without scaling of CG2

To ease the fabrication process, gate-to-source spacer length could be increased to 5 nm without changing the length of CG2. So \({L}_\mathrm{GS}\) increases by scaling down the drain electrode of 4 nm. This section shows the effect on device performance of choosing L\(_\mathrm{GS} =\) 5 nm. Figure 14a shows the variation in drain current with \({V}_\mathrm{GS}\); when \({L}_\mathrm{GS} = 5\) nm, it decreases from 3\(\times 10^{-5}\) to \(2\times 10^{-6}\)) A/\(\upmu \hbox {m}\). Transconductance (\(g_{m}\)) increases with \(V_\mathrm{GS}\) and achieves a maximum value of 1.75 \(\upmu \hbox {S}\) near about 1.4 V, as shown in Fig. 14b. Incrementing \(L_\mathrm{GS}\) from 1 to 5 nm results in drastic suppression in gate-to-drain capacitance due to less coupling between the gate and drain electrodes as shown in Fig. 15a. Apart from this, cut-off frequency has an increasing trend with \(V_\mathrm{GS}\); after achieving optimum value, it drops down as shown in Fig. 15b. Cut-off frequency reaches about 200 GHz near \(V_\mathrm{GS} = 0.4\) V at \(L_\mathrm{GS}= \) 5 nm.

4.4 Optimization of \(V_\mathrm{GS}\) and \(V_\mathrm{DS}\)

For optimization purposes, both supply and gate voltages are scaled down to 0.5 V. The effect of scaling on DC and RF performance of DMDG-ED-DL-TFET is analysed in this section. Figure 16a shows \(I_\mathrm{D}-V_\mathrm{GS}\) characteristic of the three structures at \(V_\mathrm{GS} = V_\mathrm{DS} =\) 0.5 V. Maximum values of drain current for ED-DL-TFET and DMD-ED-DL-TFET degraded, but the proposed DMDG-ED-DL-TFET device performed well with small changes in terms of maximum value of drain current, subthreshold swing and threshold voltage. Further variation of transconductance \((g_{m})\) with respect to \(V_\mathrm{GS}\) is shown in Fig. 16b, which indicates increments in \(g_{m}\) with \(V_\mathrm{GS}\) and DMDG-ED-DL-TFET have better performance in terms of maximum value of \(g_{m}\) than the other two structures. Down scaling of \(V_\mathrm{DS}\) and \(V_\mathrm{GS}\) results in reduction in \(C_\mathrm{gd}\), due to less coupling between the gate and drain electrodes, as shown in Fig. 17a. Unity current gain frequency increases with \(V_\mathrm{GS}\). DMDG-ED-DL-TFET has highest cut-off frequency (165 GHz) as compared to DMD-ED-DL-TFET and ED-DL-TFET, due to drastic suppression of \(c_\mathrm{gd}\) at scaled \(V_\mathrm{GS} = V_\mathrm{DS} = 0.5\) V as shown in Fig. 17b.

4.5 Performance analysis of DMDG-ED-DL-TFET with alignment and misalignment of the dual-metal gate and the hetero-gate dielectric interface

The length of high-K dielectric material is 94 nm and LCG2 \(=\) 12 nm (110–122 nm), so there is a misalignment of 16 nm between the interface of the dual material gate and the hetero-gate dielectric interface in DMDG-ED-DL-TFET, which is purposely created. If they are aligned then device performance degrades. Alignment of CG2 and the hetero gate dielectric causes a reduction in ON-state current and tarnsconductance as given by Fig. 18a and b, respectively. Alignment of the dual-metal gate and the hetero gate dielectric interface reduces the length of the high-K dielectric to 78 nm from 94 nm. This causes variation in the threshold voltage, subthreshold swing and the maximum value of \(g_{m}\), as can be seen from the same figures. From a fabrication point of view, we have considered molybdenum (Mo) as the gate electrode because it facilitates dual work functionality of any length on the same piece of metal. So fabrication complexity can be managed by means of a misalignment of the hetero gate material and the dual metal control gate.

5 Conclusion

A thorough study of electrically doped TFET using high \(\kappa \) dielectric material with work function engineering shows the various advantages of DMDG-ED-DL-TFET in terms of DC and RF performance. Presence of dual work function metal in DMD-ED-DL-TFET at the drain reduces ambipolar current drastically but, at the same time, it has an adverse effect on DC characteristic and RF performance, such as transconductance, ON-state current, cut-off frequency and gain bandwidth product. On the other hand, the presence of a dual work function at the control gate (CG) and drain electrode along with high \(\kappa \) dielectric over half the length of the device at the gate/source side in DMDG-ED-DL-TFET shows improvement in DC and RF characteristics as compared to conventional ED-DL-TFET and DMD-DL-TFET. To simplify fabrication complexity of DMDG-ED-DL-TFET, performance analysis of the proposed device with variation in \(\phi _\mathrm{DE2}\) and \(L_\mathrm{GS}\) is shown in the optimization section. This effect of scaling of \(V_\mathrm{GS}\) and \(V_\mathrm{DS}\) and the alignment of the dual metal gate with the hetero gate dielectric interface has been included in the same section for the proposed device.

References

Ionescu, A.M., Riel, H.: Tunnel field-effect transistors as energy-efficient electronic switches. Nature/em 479(7373), 329–337 (2010)

Choi, W.Y., Park, B.-G., Lee, J.D., Liu, T.-J.K.: Tunneling field-effect transistor (TFETs) with subthreshold swing (SS) less than 60 mV/Dec. IEEE Electron Device Lett. 28(8), 743–745 (2007)

Koswatta, S.O., Lundstrom, M.S., Nikonov, D.E.: Performance comparison between p–i–n tunneling transistors and conventional MOSFETs. IEEE Trans. Electron Devices 56(3), 456–465 (2007)

Damrongplasit, N., Shin, C., Kim, S.H., Vega, R.A., Liu, T.J.K.: Study of random dopant fluctuation effects in germanium-source tunnel FETs. IEEE Trans. Electron Devices 58(10), 3541–3548 (2011)

Chiang, M.-H., Lin, J.-N., Kim, K., Chuang, C.-T.: Random dopant fluctuation in limited-width FinFET technologies. IEEE Trans. Electron Devices 54(8), 2055–2060 (2007)

Royer, C.L., Mayer, F.: Exhaustive experimental study of tunnel field effect transistors (TFETs): from materials to architecture. In: Proceedings of the 10th International Conference Ultimate Integration of Silicon, pp. 53–56. (2009)

Jhaveri, R., Nagavarapu, V., Woo, J.C.S.: Effect of pocket doping and annealing schemes on the source-pocket tunnel field-effect transistor. IEEE Trans. Electron Devices 58(1), 80–86 (2011)

Damrongplasit, N., Kim, S.H., Liu, T.-J.K.: Study of random dopant fluctuation induced variability in the raised-Ge-source TFET. IEEE Electron Device Lett. 34(2), 184–186 (2013)

Nadda, K., Kumar, M.J.: Thin-film bipolar transistors on recrystallized polycrystalline silicon without impurity doped junctions: proposal and investigation. J. Disp. Technol. 10(7), 590–594 (2014)

Kumar, M.J., Nadda, K.: Bipolar charge-plasma transistor: a novel three terminal device. IEEE Trans. Electron Devices 59(4), 962–967 (2012)

Ghosh, B., Akram, M.W.: Junctionless tunnel field effect transistor. IEEE Electron Device Lett. 34(5), 584–586 (2013)

Nigam, K., Kondekar, P., Sharma, D.: A new approach for design and investigation of junction-less tunnel FET using electrically doped mechanism. Superlattices Microstruct. 98(5), 1–7 (2016)

Gundapaneni, S., Bajaj, M., Pandey, R.K., Murali, K.V.R., Ganguly, S., Kottantharayil, A.: Effect of band-to-band tunneling on junctionless transistors. IEEE Trans. Electron Devices 59(4), 1023–1029 (2012)

Colinge, J.-P., Lee, C.-W., Afzalian, A., Akhavan, N.D., Yan, R., Ferain, I., Razavi, P.: Nanowire transistors without junctions. Nat. Nanotechnol. 5(3), 225–229 (2010)

Kumar, M., Jit, S.: Effects of electrostatically doped source/drain and ferroelectric gate oxide on subthreshold swing and impact ionization rate of strained-Si-on-insulator tunnel field-effect transistors. IEEE Trans. Nanotechnol. 14(4), 597–599 (2015)

Lahgere, A.: Electrically doped dynamically configurable field-effect transistor for low-power and high-performance applications. Electron. Lett. 51(16), 1284–1286 (2015)

Lahgere, A., Sahu, C., Singh, J.: PVT-aware design of dopingless dynamically configurable tunnel FET. IEEE Trans. Electron Devices 62(8), 2404–2409 (2015)

Nigam, K., Kondekar, P.: DC characteristics and analog/RF performance of novel polarity control GaAs-Ge based tunnel field effect transistor. Superlattices Microstruct. 92, 224–231 (2016)

Kumar, M.J., Janardhanan, S.: Doping-less tunnel field effect transistor: design and investigation. IEEE Trans. Electron Devices 60(10), 3285–3290 (2013)

Boucart, K., Ionescu, A.M.: Double-gate tunnel FET with high-k gate dielectric. IEEE Trans. Electron Devices 54(7), 1725–1733 (2007)

Ahish, S., Sharma, D., Kumar, Y.B.N., Vasantha, M.H.: Performance enhancement of novel InAs/Si hetero double-gate tunnel FET using Gaussian doping. IEEE Trans. Electron Devices 63(1), 288–295 (2016)

Raad, B.R., Sharma, D., Kondekar, P.: Dual workfunction tunnel field-effect transistor with shifted gate for ambipolar suppression and ON current improvement. In: IEEE, ICCTICT. (2016)

Nigam, K., Pandey, S.: Temperature sensitivity analysis of polarity controlled electrostatically doped tunnel field-effect transistor. Superlattices Microstruct. 97, 598–605 (2016)

ATLAS Device Simulation Software. Silvaco Int., Santa Clara (2014)

Goswami, Y., Ghosh, B., Asthana, P.K.: Analog performance of Si junctionless tunnel field effect transistor and its improvisation using II–IV semiconductor. R. Soc. Chem. 4, 10761–10765 (2014)

Asthana, P.K., Ghosh, B., Goswami, Y., Tripathi, B.M.M.: High-speed and low-power ultradeep-submicrometer IIIV heterojunctionless tunnel field-effect transistor. IEEE Trans. Electron Devices 61(2), 479–486 (2014)

Wheeler, D., et al.: Deposition of HfO\(_{2}\) on InAs by atomic-layer deposition. Microelectron. Eng. 86, 1561–1563 (2009)

Ana, F., Najeeb-ud-din: Gate workfunction engineering for deep sub-micron MOSFETs: motivation, features and challenges. IJECT 2, 2230–9543 (2011)

Hussain, M.M. et al.: Dual work function high-k/metal gate CMOS FinFETs. In: IEEE Conference. (2007)

Lin, R., Lu, Q., Ranade, P., King, T.-J., Hu, C.: An adjustable workfunction technology using Mo gate for CMOS devices. IEEE Electron Device Lett. 23(1), 4951 (2002)

Polishchuk, I., Ranade, P., King, T.-J., Chenming, H.: Dual work function metal gate CMOS transistors by NiTi interdiffusion. IEEE Electron Device Lett. 23(4), 200–202 (2002)

Cho, S., Lee, J.S., Kim, K.R., Park, B.G., Harris, J.S., Kang, I.M.: Analyses on small-signal parameters and radio-frequency modeling of gate-all-around tunneling field-effect transistors. IEEE Trans. Electron Devices 58(12), 4164–4171 (2011)

Yang, Y., Tong, X., Yang, L.T., Guo, P.-F., Fan, L., Yeo, Y.-C.: Tunneling field-effect transistor: capacitance components and modeling. IEEE Electron Device Lett. 31(7), 752–754 (2010)

Singh, M., Mishra, S., Mohanty, S.S., Mishra, G.P.: Performance analysis of SOI MOSFET with rectangular recessed channel. Adv. Nat. Sci. Nanosci. Nanotechnol. 7(1), 8 (2016)

Madan, J., Chaujar, R.: Interfacial charge analysis of heterogeneous gate dielectric-gate all around-tunnel FET for improved device reliability. IEEE Trans. Device Mater. Reliab. 16(2), 227–234 (2016)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Yadav, S., Sharma, D., Soni, D. et al. Controlling ambipolarity with improved RF performance by drain/gate work function engineering and using high \(\kappa \) dielectric material in electrically doped TFET: proposal and optimization. J Comput Electron 16, 721–731 (2017). https://doi.org/10.1007/s10825-017-1019-2

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-017-1019-2