Abstract

Junctionless transistors, which do not have any pn junction in the source-channel-drain path have become an attractive candidate in sub-20 nm regime. They have homogeneous and uniform doping in source-channel-drain region. Despite some similarities with conventional MOSFETs, the charge-potential relationship is quite different in a junctionless transistor, due to its different operational principle. In this report, models for potential and drain current are formulated for shorter channel symmetric double-gate junctionless transistor (DGJLT). The potential model is derived from two dimensional Poisson’s equation using “variable separation technique”. The developed model captures the physics in all regions of device operation i.e., depletion to accumulation region without any fitting parameter. The model is valid for a range of channel doping concentrations, channel thickness and channel length. Threshold voltage and drain-induced barrier lowering values are extracted from the potential model. The model is in good agreement with professional TCAD simulation results.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Junctionless transistors (JLT) avoid the ultrahigh doping concentration gradients at the junctions and high thermal budgets, and hence their fabrication steps are comparatively easier than junction-based metal oxide field-oxide transistors (JB MOSFETs). They offer low OFF-state currents and hence can be scaled to lower channel lengths compared to JB MOSFETs. JLT has near ideal subthreshold slope (SS \(\sim \)60 mV/dec), high ON-state to OFF-state current ratio (\(I_{ON}/I_{OFF}>10^{7}\)), low drain induced barrier lowering etc. There is less degradation of mobility with gate voltage and temperature in JLT than classical transistors [1]. The transconductance in junctionless (JL) transistor is however lesser compared to JB transistor. Device variability and the parasitic source/drain resistances are acknowledged as important limitations of the JL nanowire field-effect transistors [2].

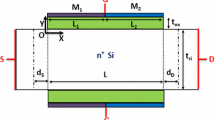

The working physics of a DGJLT is different from JB MOSFET counterpart. A cross-sectional view of symmetric n-channel DGJLT is shown in Fig. 1. JLT has highly doped \(({\sim }8\times 10^{18}-8\times 10^{19}\;\hbox {cm}^{-3})\) channel to have desirable threshold voltage \((V_{T})\). Also, to have full depletion in the subthreshold region, channel should be adequately thin. For gate voltage \(V_{GS}<V_{T}\), the channel of a DGJLT is fully depleted. When \(V_{GS}\) exceeds \(V_{T}\), the channel becomes partially depleted. When \(V_{GS}\) = flat band voltage \((V_{FB})\), bulk current flows and on further increasing \(V_{GS}\), surface current dominates in the channel current [3].

Looking at the low leakage currents and many advantages as mentioned above, a JLT can be a prospective candidate for low power circuit design applications in future technology nodes, and therefore, an analytical compact model of junctionless transistor is sought after. Since the device physics of DGJLT is fundamentally different than the JB MOSFETs [1], the existing models for DG JB MOSFETs do not directly apply. There are many reports on analytical/semi-analytical modelling for potential and drain current either for long-channel or short-channel length junctionless transistor in double-gate, trigate or gate-all-around architecture till date [2–27]. Some of them are valid only in subthreshold region and some are applicable from subthreshold to accumulation region. There are few potential models for shorter channel length double-gate junctionless transistors which are valid in subthreshold region only. Jiang et al. proposed a physics-based analytical model of electrostatic potential for short-channel junctionless double-gate MOSFETs (JLDGMTs) operated in the subthreshold regime only, by solving 2D Poisson’s equation in channel region using method of series expansion similar to Green’s function. Jin et al. derived potential model by solving 2-D Poisson’s equation using “variable separation technique” for deep nanoscale short channel asymmetric junctionless double-gate MOSFETs valid in the subthreshold region. Holtij et al. reported analytical 2D potential model within ultra-scaled junctionless double-gate MOSFETs valid in the subthreshold regime using the Schwarz–Christoffel transformation. Also, some of the models are developed piecewise (region-wise) and some are non-piecewise. Accurate potential and drain current models, valid from depletion to accumulation regions of operation, for shorter channel length double-gate junctionless transistor, are still rare in literature. In this work, potential and drain current models, covering all regions of operation, are targeted for a shorter channel length double-gate junctionless transistor (DGJLT). A two-part approach, known as the “variable separation technique” is applied to derive the channel potential, in which the total potential is divided into long channel part and short channel part. Such a method gives quite accurate results in short channel regime, because, while deriving the short channel part of potential, one can include a large set of eigen values and details will be presented later in Sect. 2.2. In this work, we have obtained good accuracy with two eigen values, however, if more number of iterations are used, correspondingly, the simulation time may increase. Threshold voltage and drain induced barrier lowering (DIBL) parameters are extracted from the model. The potential model as well as the extracted parameters is then compared to professional TCAD simulation results.

2 Potential model derivation

The Poisson’s equation considering both fixed and mobile charges in the silicon region can be written as

where, \(\Psi (x,y)\) is the channel potential, \(\varepsilon _{si}\) is the permittivity of silicon, V is electron quasi-Fermi potential, \(U_{T}=kT/q\) is the thermal voltage, \(N_{D}\) is the channel doping concentration and q is the charge of electron. Hole density is neglected as compared to electron density. The coordinates, x and y are as shown in Fig 1. Equation (1) has no direct analytical solution. One way to solve (1) is variable separation technique, which states that the total potential can be divided into long channel part (1D) and short channel part (2D) i.e.,

where, \(\Psi _I(y)\) is the potential which is related to only y direction (long channel part) and \(\Psi _{II}(x,y)\) is the potential variation related to both x and y directions (short channel part) with boundary conditions, as stated below.

2.1 Expression for \(\Psi _{I}(y)\)

\(\Psi _I (y)\) is expressed as

with boundary conditions

Equation (4) has no closed form solution even though it looks simple. Integrating (4), we obtain

where, \(\Psi _{S}\) and \(\Psi _{0}\) are the potentials at the surface and centre of the channel respectively. Thus, once the relation between \(\Psi _{S}\) and \(\Psi _{0}\) is known, the potential at any point in the silicon body can be determined. The Gauss’s law connects the surface potential with gate voltage as

\(Q_{SC}\) being the space charge density per unit area, \(C_{ox} =\varepsilon _{ox}/T_{ox}\) is the oxide capacitance, \(V_{FB}\) is the flat band voltage. Combining (5) and (6)

(a) For depletion region \(\left( {V_{FB} <V_G <V_{FB} +V_{DS}} \right) {\textit{ with }} V_{DS} >0\), after some mathematical reformulations, the Eq. (7) can be written as [4]

where, Lambertw is the Lambert W-function, which is the inverse of the function \(\hbox {z}=\hbox {W(z)}\times \hbox {e}^{\mathrm{W(z)}}\). \(V_{T}\) is the threshold voltage and \(\left( {\Psi _{0}-\Psi _{S}}\right) \) is the difference between centre and surface potentials, given by,

The expression of \(V_{T}\) in (9) is valid when channel length is higher. The \(V_{T}\) for shorter-channel device is given in Sect. 2.3.

(b) For accumulation region \(\left( {V_G >V_{FB} +V_{DS} } \right) \)

The relation between centre and surface potentials \(\left\{ {\Psi _{S}-\Psi _{0}\left( {=\alpha , \hbox {say}} \right) }\right\} \) is given by [5]

Equation (10) can also be expressed as [17]

Now, using (7) and (11), the relation between surface potential with gate voltage can be obtained as [17]

For accumulation region \(\left( {V_{GS} >V_{FB} +V_D } \right) \), \(\alpha >0\). Equation (12) can be solved numerically. The centre potential can be derived using Eqs. (8)–(12), as explained in [18].

2.2 Expression for \(\Psi _{II} (x,y)\)

\(\Psi _{II}(x,y)\) is expressed as

with the boundary conditions

Equation (13) is a mixed boundary value problem and it is already solved by many groups [28, 29]. The final solution is

where,

\(\Psi _{S\hbox {(Long)}}\) is the long channel surface potential. The eigenvalue \(\mu _{n}\) is the periodic \(\hbox {n}^{\mathrm{th}}\) root of this equation and is determined using the permittivity and thickness values of both silicon and oxide. It can have infinite possible values for \(\upmu \), however, first 1-2 iteration(s) give quite good result.

Now, putting the expressions of \(\Psi _{I}(y)\) and \(\Psi _{II}(x,y)\) in Eq. (2), the total potential in the channel region of a shorter channel DGJLT can be determined.

2.3 Threshold voltage and DIBL value extraction

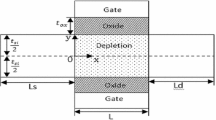

A schematic plan for calculating the threshold voltage \((V_{T})\) is given in Fig. 2. The threshold voltage is given by the following expression, and it is valid for longer as well as shorter channel length devices [30]

\(\Psi _{\min (V_{GS1})}\) and \(\Psi _{\min (V_{GS1})}\) are the minimum potentials at two gate-to-source voltages \(V_{GS1}\) and \(V_{GS2}\). Assuming a linear relationship between \(\Psi _{\min }\) and \(V_{GS}\), in the subthreshold region, threshold voltage can be extracted using (13).

Drain induced barrier lowering (DIBL) is defined as the change in threshold voltage when drain voltage changes from 50 mV to 1 V i.e.,

2.4 Discussion and verification of model

To validate the model results, they are compared with electrical characteristics of the devices simulated using 2D ATLAS device simulator with version 5.19.20.R [31]. Lombardi mobility model is employed, accounting for the dependence on the impurity concentrations as well as the transverse and longitudinal electric field values. Shockley-Read-Hall (SRH) recombination model is included in the simulation to account for leakage currents. Because of high channel doping concentration, Fermi-Dirac carrier statistics without impact ionization is utilized in the simulations. Band gap narrowing model (BGN) is also incorporated to take care of the band gap narrowing effect which may arise due to highly doped channel regions. Quantum effect is not considered here. Channel doping concentration \(N_{D}\) of \(5\times 10^{18}\) and \(1\times 10^{19}\; \hbox {cm}^{-3}\), equivalent gate oxide thickness (EOT) = 2 nm, silicon thickness \((T_{si})=10\), 15 nm are considered for TCAD simulation. Channel width (W) is \(1\upmu \hbox {m}\). In addition, p-type polysilicon is used having doping concentration \(10^{20}\;\hbox {cm}^{-3}\). The interface charge concentration \((N_{SS})\) is considered as \(5\times 10^{10}\;\hbox {cm}^{-3}\). A constant mobility \((\mu _{e})\) of \(100\;\hbox {cm}^{2}\)/V.s is assumed. For channel length of \(1\;\upmu \hbox {m}\), source/drain extension length \((L_{S}/L_{D})\) is taken as 50 nm; and for channel length of 30 nm-80 nm, \(L_{S}/L_{D}\) is taken as 10 nm to avoid parasitic resistance effect. Calculations are done on Mathematica computational software. Figure 3 shows the surface potential with respect to gate voltage, for different values of \(V_{D}=0\) V, 50 mV, 0.5 V and 1 V respectively for a channel length of \(1\;\upmu \hbox {m}\). The simulation and model curves are in close agreement. Figure 4 shows the surface potential with respect to gate voltage, for different values of \(V_{D}=0\) V, 50 mV, 0.5 V and 1 V respectively for a channel length of 30 nm. The marginal difference may be due to the inclusion of source and drain extension resistances in TCAD characteristics; and the exclusion of fringing electric fields in the model. Figure 5a, b shows the potential along the channel direction, 0.5 nm away from the \(\hbox {Si-SiO}_{2}\) interface, at \(\hbox {V}_{\mathrm{DS}}= 50\) mV and 1 V respectively keeping \(\hbox {V}_{\mathrm{GS}}=0\) V for gate lengths of 80 and 30 nm. Both the simulation and model plots are in close agreement. There is marginal difference of potential towards the drain side between model and simulation. For example, for L = 30 nm at \(\hbox {V}_{\mathrm{DS}}=1\) V this difference are 86.4 mV. Figure 6a, b show the threshold voltage and drain induced barrier lowering characteristics extracted from model and simulation, for different gate lengths. The values obtained from model and simulations are in close agreement. The marginal difference of threshold voltage between model and TCAD results for say, L = 20 nm and L = 60 nm are 0.013 and 0.003 V respectively. The difference of DIBL between model and TCAD results are 9 mV and 1 mV for L = 20 nm and L = 60 nm respectively.

Surface potential with respect to gate voltage near the drain side for \(V_{D}=0\) V, 50 mV, 0.5 V and 1 V. \(L=1\;\upmu \hbox {m}\), \(T_{si}=15\) nm, \(T_{ox}=2\) nm, \(N_{D}=5\times 10^{18}\;\hbox {cm}^{-3}\) and source/drain extension \(\hbox {length}=50~\hbox {nm}\). Flat band voltage \((V_{FB})\) considered is \({\sim }1.1\) eV

Surface potential with respect to gate voltage near the drain side for \(V_{D}=0\) V, 50 mV, 0.5 V and 1 V. \(L=30\) nm, \(T_{si}=15\;\hbox {nm}\), \(T_{ox}=2\) nm, \(N_{D}=5\times 10^{18}\;\hbox {cm}^{-3}\) and source/drain extension length = 10 nm. Flat band voltage \((V_{FB})\) considered is \({\sim }1.1\) eV

Surface potential along the channel for a \(L=80\) nm (long channel) at \(V_{D}=50\) mV, 1 V, b \(L=30\) nm (short channel). \(T_{si}=10\) nm, \(T_{ox}=2\) nm, \(N_{D}=1\times 10^{19}\;\hbox {cm}^{-3}\), \(V_{GS}=0\) V and source/drain extension length=10 nm. Flat band voltage \((V_{FB})\) considered is \({\sim }1.1\) eV

3 Drain current model

The mobile charge density \(Q_{m}\) can be written as

\(Q_d =qN_D T_{si}\) is the fixed charge density. The drain current can be expressed as (using (7))

It is assumed that \(V_{S}=0\) and \(V_{D}=V_{DS}\). W is the width of the device and \(\Psi _{S}\) (long-channel part + short-channel part) is the surface potential. Figure 7 shows the drain current with respect to gate voltage for different values of \(N_{D}\) i.e., \(8\times 10^{18}\;\hbox {cm}^{-3}\) and \(1\times 10^{19}\;\hbox {cm}^{-3}\) at a drain voltage of 1 V. Same current values are plotted in both logarithmic (left) and linear (right) scales. The model results (symbols) are in close agreement with TCAD simulation (lines) in all regions of device operation, i.e., from subthreshold to accumulation regions. The subthreshold slope obtained from model is almost equal to TCAD results. As expected, current saturates at higher gate voltages. Also, saturation current increases with increase in channel doping concentration, as usual. The current in the accumulation region is obtained numerically. The subthreshold slope extracted from model and TCAD are in close agreement for long as well as short channel DGJLT. For example, for a DGJLT with \(L=30\hbox {nm}\), \(T_{si}=10\) nm, \(T_{ox}=2\) nm and \(N_{D}=1\times 10^{19}\;\hbox {cm}^{-3}\), the subthreshold slope is 63 mV/dec as extracted from TCAD, which is almost similar to the value extracted from model. Figure 8 shows the transfer characteristic for Tsi=10 nm, L=30nm, \(T_{ox}=2\) nm and \(N_{D}=1\times 10^{19}\;\hbox {cm}^{-3}\) at gate voltages \(V_{GS}\) of 50 mV and 1 V. Both TCAD (solid line) and model results (symbols) are in close agreement. Figure 9 shows the drain current with respect to gate voltage for \(L=80\) nm, \(T_{si}=15\) nm, \(T_{ox}=2\) nm, \(N_{D}= 1\times 10^{19}\;\hbox {cm}^{-3}\) at \(V_{DS}=1\) V. Lines show the TCAD simulations and symbols shows model results. TCAD (solid line) and model results (symbols) are in good agreement. Figure 10 presents the drain current with respect to drain voltage for different values of \(N_{D}\; i.e\)., \(8\times 10^{18}\;\hbox {cm}^{-3}\) and \(1\times 10^{19}\;\hbox {cm}^{-3}\) at a gate voltage of 1 V. The models (symbols) are in close accord with TCAD simulation (lines). The transconductance with respect to gate voltage for L=30 nm, \(T_{si}=15\) nm, \(T_{ox}=2\) nm, \(N_{D}=1\times 10^{19}\;\hbox {cm}^{-3}\) at \(V_{DS}=1\) V is shown in Fig. 11. TCAD simulations (symbols) and model results (lines) are not in close match at higher gate voltages. Figure 12 shows the output conductance with respect to drain voltage for \(L=30\) nm, \(T_{si}=15\) nm, \(T_{ox}=2\) nm, \(N_{D}=1\times 10^{19}\;\hbox {cm}^{-3}\) at \(V_{GS}=1\) V. Both TCAD and model results are in close agreement.

Drain current with respect to gate voltage for \(N_{D}=5\times 10^{18}\;\hbox {cm}^{-3}\) and \(1\times 10^{19}\;\hbox {cm}^{-3}\). \(L=30\) nm, \(T_{si}=15\) nm, \(T_{ox}=2\) nm, \(V_{DS}=1\) V and source/drain extension \(\hbox {length}=10~\hbox {nm}\). Flat band voltage \((V_{FB})\) considered is \({\sim }1.1\) eV. Lines show the TCAD simulations and symbols shows model results

Drain current with respect to drain voltage for \(N_{D}=5\times 10^{18}\;\hbox {cm}^{-3}\) and \(1\times 10^{19}\;\hbox {cm}^{-3}\). \(L=30\) nm, \(T_{si}=15\) nm, \(T_{ox}=2\) nm, \(V_{GS}=1\) V and source/drain extension \(\hbox {length}=10~\hbox {nm}\). Flat band voltage \((V_{FB})\) considered is \({\sim }1.1\) eV. Lines show the TCAD simulations and symbols shows model results

4 Conclusion

In this work, we have proposed a semi-analytical model to calculate the channel surface potential as well as drain current for shorter channel length symmetric double-gate junctionless transistor by a two parts approach. Carrier mobility is assumed to be constant and the quantum effects are not considered. The model is valid in depletion to accumulation regions of operation. Threshold voltage and drain induced barrier lowering parameters were extracted from model. Assessment of the model with TCAD simulations confirms its legitimacy. Consideration of short-channel and quantum effects in the model is another scope for future research.

References

Colinge, J.-P., Lee, C.-W., Afzalian, A., Akhavan, N.D., Yan, R., Ferain, I., Razavi, P., O’Neill, B., Blake, A., White, M., Kelleher, A.-M., McCarthy, B., Murphy, R.: Nanowire transistors without junctions. Nat. Nanotechnol. 5, 225–229 (2010)

Gnani, E., Gnudi, A., Reggiani, S., Baccarani, G.: Theory of the junctionless nanowire FET. IEEE Trans. Electron Devices 58, 2903–2910 (2011)

Duarte, J.P., Choi, S.-J., Choi, Y.-K.: A full-range drain current model for double-gate junctionless transistors. IEEE Trans. Electron Devices 58, 4219–4225 (2011)

Chen, Z., Xiao, Y., Tang, M., Xiong, Y., Huang, J., Li, J., Gu, X., Zhou, Y.: Surface-potential-based drain current model for long-channel junctionless double-gate MOSFETs. IEEE Trans. Electron Devices 59, 3292–3298 (2012)

Sallese, J.-M., Chevillon, N., Lallement, C., Iñiguez, B., Prégaldiny, F.: Charge-based modeling of junctionless double-gate field-effect transistors. IEEE Trans. Electron Devices 58, 2628–2637 (2011)

Lime, F., Santana, E., Iñiguez, B.: A simple compact model for long-channel junctionless double gate MOSFETs. Solid State Electron. 80, 28–30 (2013)

Duarte, J.P., Choi, S.-J., Choi, Y.-K.: A full-range drain current model for double-gate junctionless transistors. IEEE Trans. Electron Devices 58, 4219–4225 (2011)

Duarte, J.P., Choi, S.J., Moon, D.I., Choi, Y.K.: Simple analytical bulk current model for long-channel double-gate junctionless transistors. IEEE Trans. Electron Devices 32, 704–706 (2011)

Duarte, J.P., Kim, M.-S., Choi, S.-J., Choi, Y.-K.: A compact model of quantum electron density at the subthreshold region for double-gate junctionless transistors. IEEE Trans. Electron Devices 59, 1008–1012 (2012)

Duarte, J.P., Choi, S.-J., Moon, D.-I., Choi, Y.-K.: A nonpiecewise model for long-channel junctionless cylindrical nanowire FETs. IEEE Electron Device Lett. 33, 155–157 (2012)

Chiang, T.-K.: A quasi-two-dimensional threshold voltage model for short-channel junctionless double-gate MOSFETs. IEEE Trans. Electron Devices 59, 2284–2289 (2012)

Gnudi, A., Reggiani, S., Gnani, E., Baccarani, G.: Semianalytical model of the subthreshold current in short-channel junctionless symmetric double-gate field-effect transistors. IEEE Trans. Electron Devices 60, 1342–1348 (2013)

Trevisoli, R.D., Doria, R.T., Souza, M., Pavanello, M.A.: A physically-based threshold voltage definition, extraction and analytical model for junctionless nanowire transistors. Solid-State Electron. 90, 12–17 (2013)

Trevisoli, R.D., Doria, R.T., Pavanelloc, M.A.: Analytical model for the threshold voltage in junctionless nanowire transistors of different geometries. ECS Trans. 39, 147–154 (2011)

Trevisoli, R.D., Doria, R.T., de Souza, M., Pavanello, M.A.: Accounting for short channel effects in the drain current modeling of junctionless nanowire transistors. ECS Trans. 49, 207–214 (2012)

Gnudi, A., Reggiani, S., Gnani, E., Baccarani, G.: Analytical model for the threshold voltage variability due to random dopant fluctuations in junctionless FETs, pp. 5–7. SISPAD, Denver (2012)

Cerdeira, A., Estrada, M., Iniguez, B., Trevisoli, R.D., Doria, R.T., Souza, M., de, M., Pavanello, A.: Charge-based continuous model for long-channel symmetric double-gate junctionless transistors. Solid-State Electron 85, 59–63 (2013)

Cerdeira, A., Estrada, M., Trevisoli, R.D., Doria, R.T., de Souza, M., Pavanello, M.A.: Analytical model for potential in double-gate juntionless transistors. Symposium on Microelectronics Technology and Devices (2013)

Jin, X., Liu, X., Wu, M., Chuai, R., Lee, J.-H., Lee, J.-H.: Modelling of the nanoscale channel length effect on the subthreshold characteristcs of junctionless field-effect transistors with a symmetric double-gate structure. J. Phys. D 45, 375102–375107 (2012)

Yesayan, A., Prégaldiny, F., Sallese, J.-M.: Explicit drain current model of junctionless double-gate field-effect transistors. Solid-State Electron. 89, 134–138 (2013)

Hu, G., Xiang, P., Ding, Z., Liu, R., Wang, L., Tang, T.-A.: Analytical models for electric potential, threshold voltage, and subthreshold swing of junctionless surrounding-gate transistors. IEEE Trans. Electron Devices 61, 688–695 (2014)

Woo, J.-H., Choi, J.-M., Choi, Y.-K.: Analytical threshold voltage model of junctionless double-gate MOSFETs with localized charges. IEEE Trans. Electron Devices 60, 2951–2955 (2013)

Li, C., Zhuang, Y., Di, S., Han, R.: Subthreshold behavior models for nanoscale short-channel junctionless cylindrical surrounding-gate MOSFETs. IEEE Trans. Electron Devices 60, 3655–3662 (2013)

Trevisoli, R.D., Doria, R.T., Souza, M., Das, S., Ferain, I., Pavanello, M.A.: Surface-potential-based drain current analytical model for triple-gate junctionless nanowire transistors. IEEE Trans. Electron Devices 59, 3510–3518 (2012)

Jiang, C., Liang, R., Wang, J., Xu, J.: A two-dimensional analytical model for short channel junctionless double-gate MOSFETs. AIP Adv. 5, 057122 (2015)

Xi, L., Kwon, H., Lee, J., Lee, J.: A subthreshold current model for nanoscale short channel junctionless MOSFETs applicable to symmetric and asymmetric double-gate structure. Solid-State Electron. 82, 77–81 (2013)

Holtij, T., Schwarz, M., Kloes, A., Iñíguez, B.: Threshold voltage, and 2D potential modeling within short-channel junctionless DG MOSFETs in subthreshold region. Solid-State Electron. 90, 107–115 (2013)

Hamid, H.A.E., Guitart, J.R., Iniguez, B.: Two-dimensional analytical threshold voltage and subthreshold swing models of undoped symmetric double-gate MOSFETs. IEEE Trans. Electron Devices 54, 1402–1408 (2007)

Liang, X., Taur, Y.: 2-D analytical solution for SCEs in DG MOSFETs. IEEE Trans. Electron Devices 51, 1385–1391 (2004)

Holtij, T., Schwarz, M., Kloes A., Iniguez, B.: 2D analytical potential modeling of junctionless DG MOSFETs in subthreshold region including proposal for calculating the threshold voltage. 13th International Conference on Ultimate Integration on Silicon (ULIS), pp. 81– 84 (2012)

Atlas User’s Manual: Device Simulation Software (2008)

Acknowledgments

This work was partially supported by DST SERB, Government of India, under Grant No. SB/FTP/ETA-268/2012.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Baruah, R.K., Paily, R.P. A surface-potential based drain current model for short-channel symmetric double-gate junctionless transistor. J Comput Electron 15, 45–52 (2016). https://doi.org/10.1007/s10825-015-0723-z

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-015-0723-z