Abstract

This paper presents a dual-input extended-dynamic-range, high-PCE rectifier for dedicated far-field RF energy harvesting systems. Two identical input RF energy supply source are applied into two individual rectifier. The rectifier with the highest PCE is selected to deliver dc power to a single-load element. A logic control circuit senses Pin from the rectified dc voltage and toggles between the rectifiers by generating two control voltage to attain high-PCE across Pin. Simulated in a 65nm CMOS process, the proposed system achieves an extended DR of 26 dB for an output load, RL = 100 kΩ. Furthermore, a peak PCE of 54.85% and 47.87% was achieved for RL = 100 kΩ and RL = 150 kΩ, respectively. The sensitivity for an output voltage of 1 V with RL = 100 kΩ is -20.6 dBm.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

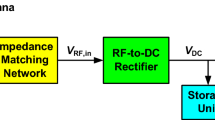

Internet of things (IoT) is an emerging technology that has been perceived by the semiconductor industry as the next technological revolution that will transform the consumers need. The vision of realizing IoT requires major enabling technologies such as wireless sensor nodes (WSNs) which are group of spatially dispersed sensors used to monitor the physical conditions of the environment as illustrated in Fig. 1. Though WSN has significant applications in various IoT infrastructure, the technology comes with a major bottleneck in its requirement of a reliable and extended power source.

Energy harvesting has gained widespread attention as an alternative power source for WSNs [1, 2]. However, ambient energies is dependent on the available energy in the free space environment, inhibiting the reliability of the power source. A dedicated far-field Radio Frequency (RF) energy source which transmits RF energy in the surrounding environment can alternatively be used to power-up WSNs [3]. Despite the effectiveness of radiating RF energy as a power source, the energy density received by each WSN in a network of dispersed sensors varies according to its distance from the transmitter. This prompts the need of a high power conversion efficiency (PCE) rectifier in Far-Field RF energy harvesting (RFEH) systems to efficiently convert the RF energy to DC across wide variation of input RF power (Pin) level. Hence, a wide-PCE range rectifier with satisfactory performance in sensitivity for a given output load (RL) is desirable.

Initiatives to improve the dynamic range (DR) performance of rectifiers in RFEH systems have been reported in [4,5,6] where DR is defined in this work as the Pin range for PCE above 20% [6] and PCE is expressed as,

where Pout is the power consumption of the load, RL and Vout is the rectified output voltage. A cross-connected Dickson rectifier is employed in [6] to minimize the detrimental effect of Vth to obtain a peak PCE of 60% and a sensitivity of -21 dBm. However, the performance was only reported for open load condition. Generally, RL has significant effect on PCE and sensitivity performances which are inherent trade-offs in RFEH systems [2]. In [5], an adaptive CCDD scheme is proposed to extent the high-PCE range of the rectifier. A 2-stage CCDD rectifier is configured in series/parallel (cascade/cascode) configuration through a control circuit according to the level of Pin. Despite achieving a DR of 11 dB, it reports a poor sensitivity of 0 dBm which is not suitable for far-field RFEH systems. A dual-path rectifier is proposed in [6] to extend the high-PCE range for RFEH systems. The rectifier consists of a low-power path and a high-power path to rectify the RF energy at low and high, Pin, respectively. An adaptive control circuit selects the rectifier path according to Pin. A DR of 11 dB and a peak sensitivity of -17.7 dBm was achieved. However, the adaptive control circuit consumes a portion of the harvested Pin which impairs the achievable PCE.

To overcome the aforementioned challenges, this work propose a dual-input rectifier to achieve an extended-dynamic-PCE range for dedicated far-field RFEH systems. The novelty of this system is in the integration of a dual-input rectifier scheme to harvest RF energy from two individual energy sources with identical Pin level inspired by [7]. A logic control circuit complements the system to sense and toggle between the two rectifiers to select the path of high-PCE with respect to Pin. Section II presents the proposed rectifier scheme. The design methodology of the rectifier is discussed in Section III. Section IV presents the simulation results and Section V concludes the findings.

2 Proposed dual-input rectifier

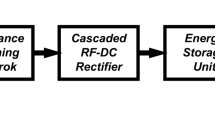

Figure 2 shows the block diagram of the proposed rectifier scheme. The scheme harvests RF energy of the same frequency as two input sources [7]. Alternatively, two dissimilar rectifier topologies – CCDD and Dickson – are utilized into a single unit to achieve an extended DR performance. MNS1, MPS2, MPS3 and MPS4 are gate switching transistors for selecting the rectifier according to Pin. Across Pin level, the logic control circuit sense the output rectified DC voltage and generate two control voltages (Vctrl1 and Vctrl2) to select the rectifier with high-PCE to extend the DR performance. Section III further elaborates the design of the rectifier.

3 Design methodology

3.1 Rectifier

The Dickson and CCDD rectifiers are the two primary rectifier topology for RFEH [10]. Their performances are restricted by the intrinsic Vth drop of the transistors during forward conduction and reverse leakage current [11, 12]. In addition, the PCE range of the rectifier for a specific RL differs across Pin, which is an inherent trade-off. The PCE curve of the Dickson and CCDD rectifier for RL = 150 kΩ is shown in Fig. 3. Generally, the CCDD rectifier attains peak PCE at low Pin levels due to its active Vth cancellation scheme, resulting in a small on-resistance [10]. However, at high Pin levels, the small on-resistance promotes high reverse leakage current which detriments the rectifier’s PCE. Inversely, the Dickson topology achieves peak PCE when the level of Pin is high as the diode-connected transistors configuration of this topology acts as an effective voltage pumping devices [12]. At low Pin the Vth of the transistors creates a large voltage drop resulting in lower voltage harvested, degrading the PCE. By exploiting the high-PCE range for each topology for a specific RL, the cumulative PCE from of each rectifier maximize the performances of the architecture as illustrated in Fig. 3.

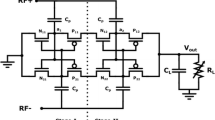

Figure 4(a) and Fig. 4(b) shows schematic diagram of adopted Dickson and parallel CCDD rectifier, respectively. Multi-stage configuration delivers higher output voltage and enhances the peak PCE performance compared to a single-stage rectifier. In addition, each rectifier topology has an optimum number of stages to achieve peak PCE for a given RL. However, exceeding the number of optimal stages could degrade rather than improve the PCE performance [3, 11]. Figure 5(a) and (b) shows the simulated PCE plot of CCDD and Dickson rectifier for different number of stages in the adopted technology. It was found that the optimum number for both rectifiers is 4-stage. Therefore, 4-stage rectifier are adopted for the CCDD and Dickson topology.

An additional design consideration in improving the PCE performance of the CCDD rectifier can be attributed to the number of stage configuration in the rectifier. As reported in [7], two modular CCDD rectifier connected in parallel achieves higher PCE at low Pin compared to a single modular CCDD rectifier. Figure 6 describe the PCE plot for the conventional 4-stage CCDD and two 4-stage modular CCDD in parallel. The plot in Fig. 6 shows a higher peak of PCE can be achieved at lower Pin when incorporating two modular CCDD rectifier in parallel. Hence, a CCDD rectifier with a second modular CCDD rectifier (1b, 2b, 3b, and 4b) as shown in Fig. 4(a), connected in parallel with the first modular CCDD rectifier (1a, 2a, 3a, and 4a) is adopted in this work to attain higher PCE performance at low Pin.

3.2 Logic control circuit

Figure 7 shows the schematic diagram of the logic control circuit. Two digital inverters cascaded in series forms the logic control switch. Voltage VM1 act as the input supply voltage of the inverter cells and VM2 being the input signal voltage. A voltage divider that consist of two resistors, R1 and R2 establishes a voltage at the gate terminal of the MOSFETs to be lower than VM1. Two control voltages, Vctrl1 and Vctrl2 are generated with an extreme magnitude (digital LOW and digital HIGH) respectively to the magnitude of VM2 to control the operation of the control gates and the rectifiers across the harvesting range, Pin.

At low Pin, a digital LOW Vctrl2 will switch on MPS4 where the CCDD rectifier will supply power to the load and a digital HIGH Vctrl1 switches off MPS3 where the Dickson rectifier does not supply any power to the load (Fig. 2). Therefore, only the CCDD rectifier operates when Pin is low. Alternatively, a digital LOW Vctrl2 switches on MPS2 to maximize the input signal voltage of the logic control circuit. Maximizing the overdrive voltage of MPS2 allows the voltage to exceed the MOSFETs’ Vth at the desired switching point. In addition, a digital LOW Vctrl2 partially switches on MNS1 to minimize the voltage feed from MNS1 to the source terminal limiting the amount of voltage necessary to power up logic control circuit. This is to improve the output voltage delivered to the load, thus, upholding the PCE performance.

At high Pin, the operation is inversed where the voltage from MPS2 into the logic control circuit will be higher than the MOSFETs’ Vth. This generates a digital LOW control voltage, Vctrl1 (with magnitude almost equal to zero) and a digital HIGH control voltage, Vctrl2 (with magnitude almost equal to VM1). The digital HIGH Vctrl2 switches MPS4 off to cut off the power from the CCDD rectifier and the digital LOW Vctrl1 switches on MPS3 for the Dickson rectifier to supply power to the load. MPS2 will be partially switched off to maximize the generation of the digital HIGH control voltage Vctrl2 when the input signal voltage into the logic control circuit from MPS2 is higher than the MOSFETs’ Vth. A digital HIGH Vctrl2 switches on MNS1 to maximize the input supply voltage from MNS1 into the logic control circuit to uphold the PCE. Table1 summarizes the operation of logic control circuit.

4 Simulation results

The proposed rectifier is simulated on a 65-nm CMOS technology. The rectifier is optimized for a frequency of 953 MHz and covers an active chip area of 0.657 mm2 as shown in Fig. 8(a). The equivalent circuit of the RFEH front-end is represented in Fig. 8(b) where Lp1,2, Cp1,2 and Rp1,2 represents the parasitic inductance, capacitance and resistance, respectively. The parasitic components are derived from bond wire inductances, bonding pads and package capacitances and sheet resistance of the polysilicon [13].

(a) Chip layout of proposed rectifier, (b) equivalent circuit of RFEH front-end [6]

Figure 9(a) present the PCE results which show a peak PCE of 47.87% and 54.85% for a load of RL = 150 kΩ and RL = 100 kΩ, respectively. Also, the rectifier observes a peak sensitivity of -20.6 dBm from a load of RL = 100 kΩ. A significant performance of 25 dB and 26 dB in DR (PCE > 20%) was achieved for a load of 150 kΩ and 100 kΩ, respectively. Figure 10 plots the simulated output noise across RL. Table 2 summarize and compare the performances of the proposed rectifier. The comparison shows that the performance in DR range, peak PCE and sensitivity for similar RL superseding that of prior-art solutions. The proposed rectifier shows a significant enhancement in DR compared to [6, 12] with competitive performance in peak PCE where [6] has adopted similar concept of rectifying the RF energy from two separate path to feed a single load element. In addition, the solution of harvesting RF energy of the same frequency from two individual source of antenna far exceeds that of dual-band CMOS RF rectifiers [8, 9].

5 Conclusion

A dual-input extended-dynamic-PCE rectifier in 65 nm CMOS technology is proposed for dedicated far-field RFEH systems. Exploiting the high-PCE range of the CCDD and Dickson for a given RL, the proposed system achieved an extended PCE across a wide Pin range. A logic control circuit complements the system to passively switch between the rectifiers by sensing the rectified dc voltage. The proposed rectifier achieves an extended DR performance of 26 dB (RL = 100 kΩ, PCE > 20%), a peak PCE of 54.85% (RL = 100 kΩ) and a peak sensitivity of -20.6 dBm (RL = 100 kΩ) for a 1 V output.

References

Yuen, P. W., Chong, G., & Ramiah, H. (2019). A high efficient dual-output rectifier for piezoelectric energy harvesting. AEU - International Journal of Electronics and Communications, 111, 152922.

Chong, G., Ramiah, H., Yin, J., Rajendran, J., Wong, W. R., Mak, P. I., & Martins, R. P. (2018). Ambient RF energy harvesting system: a review on integrated circuit design. Analog Integrated Circuits and Signal Processing, 97, 515–531.

Stoopman, M., Keyrouz, S., Visser, H. J., Philips, K., & Serdijn, W. A. (2014). Co-design of a CMOS rectifier and small loop antenna for highly sensitive RF energy harvesters. IEEE Journal of Solid-State Circuits, 49(3), 622–634.

Scorcioni, S., Larcher, L., & Bertacchini, A. (2013). A reconfigurable differential CMOS RF energy scavenger with 60% peak efficiency and -21 dBm sensitivity. IEEE Microwave and Wireless Components Letters, 23(3), 155–157.

Li, C., & Lee, T. (2014). 2.4-GHz high-efficiency adaptive power harvester.IEEE Transactions on Very Large Scale Integration Systems, 22(2), 434–438.

Lu, Y., Dai, H., Huang, M., Law, M. K., Sin, S. W., et al. (2017). A wide input range dual-path CMOS rectifier for RF energy harvesting. IEEE Transactions on Circuits and Systems II: Express Briefs, 64(2), 166–170.

PC KK, Ramiah H, Ahmad MY, Chong G and Rajendran J. Analysis of a Single-Frequency Multi-Channel Ambient RF Energy Harvesting in CMOS Technology. IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), p. 97–100 (2019).

Li, B., Shao, X., Shahshahan, N., Goldsman, N., Salter, T., & Metze, G. M. (2013). An Antenna Co-Design Dual Band RF Energy Harvester. IEEE Transactions on Circuits and Systems I: Regular Papers, 60(12), 3256–3266.

Li, C., Yu, M., & Lin, H. (2017). A compact 0.9-/2.6-GHz dual-band RF energy harvester using SiP technique. IEEE Microwave and Wireless Components Letters, 27(7), 666–668.

Chong, G., Ramiah, H., Yin, J., Rajendran, J., Wong, W. R., Mak, P. I., & Martins, R. P. (2019). CMOS cross-coupled differential-drive rectifier in subthreshold operation for ambient RF energy harvesting—model and analysis. IEEE Transactions on Circuits and Systems II: Express Briefs, 66(12), 1942–1946.

Chong, G., Ramiah, H., Yin, J., Rajendran, J., Mak, P. I., & Martins, R. P. (2020). A wide-PCE-dynamic-range CMOS cross-coupled differential-drive rectifier for ambient RF energy harvesting. IEEE Transactions on Circuits and Systems II: Express Briefs.

Hameed, Z., & Moez, K. (2015). A 3.2 V –15 dBm adaptive threshold voltage compensated RF energy harvester in 130 nm CMOS. IEEE Transactions on Circuits and Systems I: Regular Papers, 62(4), 948–956.

Mandal, S., & Sarpeshkar, R. (2007). Low-power CMOS rectifier design for RFID applications. IEEE Transactions on Circuits and Systems I: Regular Papers, 54(6), 1177–1188.

Acknowledgement

This work was supported by RU Grant-Faculty Program (GPF056B-2020). This manuscript has no associated data.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Poo, C.M., Chong, G. & Ramiah, H. A dual-input extended-dynamic-PCE rectifier for dedicated far-field RF energy harvesting systems. Analog Integr Circ Sig Process 107, 567–573 (2021). https://doi.org/10.1007/s10470-021-01802-5

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-021-01802-5