Abstract

This study introduces a nine-level multilevel (MLI) inverter based on the switched-capacitor method. Not only does the suggested inverter ensure that the switches’ maximum voltage stress is lower than the incoming voltage, but it also includes a voltage double boost capacity. As a result, it is indeed appropriate for high-voltage tasks. The suggested inverter has horizontal extension strategies that assist it to reach a higher level of output with voltage boost. This nine-level inverter could be made with two capacitors owing to a benefit of low voltage stress and devices with cheap power consumption. Furthermore, the self-balancing capability of capacitor voltage helps reduce control circuit complexity. The topology, working principles, modulation approach and the evaluation of the inverter's capacitor are presented. The proposed inverter's superiority is explored by comparing it to recently suggested hybrid and switched-capacitor multilevel inverters. Finally, a nine-level prototype is built to verify the theoretical analysis' accuracy as well as the suggested inverter's feasibility and efficiency.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Multilevel inverters (MLIs) are key components in power electronics circuits because of their large power capability, lower operating voltage stress, low cost, design with low harmonics, modularity and stability.

1.1 Motivation and incitement

The topology that combines the neutral point clamp (NPC) and flying capacitor (FC) is one of the appealing solutions to reach a better level of output and enhance extensibility [1, 2]. In addition, the cascaded H-bridge (CHB) inverter has been tweaked to cut down on the number of power switches. These enhancements broaden the range of MLIs available. They all share the benefit of keeping all semiconductor switches' voltage stress to the dc input. These inverters cannot enhance voltage. Furthermore, NPC inverters still struggle with voltage balancing of capacitors. The presence of flying capacitors necessitates the use of more complicated control circuits. To meet the load demand and output diverse voltage levels, the inverters [2] utilize unique switch arrangements to interconnect multiple dc power supplies in series. It is possible to produce various dc voltage ratios, which improves their flexibility. On the other hand, their switches have maximum voltage stress (MVS) from two dc voltage supplies. Additionally, they lack voltage boosting capabilities and just have a single topology horizontal/vertical extension technique.

The switched-capacitor approach is a great method to address the issues outlined above [3] and [4]. There's no need for a more sophisticated signal circuit in switched-capacitor-based multilevel inverters. This may enhance low source dc voltages to high ac voltages by linking the pre-charged capacitors together. The benefits of such inverters include their compact size, great power density, weightless and minimal harmonic elements [2] and [5].

1.2 Literature review

Several SCMLIs have indeed been suggested throughout the open literature [6] and [7]. The SCMLIs are described in [8,9,10,11] can keep capacitor voltages balanced. Furthermore, they are distinguished by the use of only a dc power supply capable of boosting the voltage. On the other hand, utilizing H-bridges to accomplish voltage orientation transformation will constrain their application since H-bridge raises the MVS of the switches while also increasing the capital cost. The H-bridge was eliminated without impacting the voltage orientation conversion [12]. However, some switches must sustain the output voltage's peak value, preventing their use in high-voltage applications. Although the architecture presented in [13,14,15] decreases the MVS of switches, the MVS of switches remains double that of the dc supply voltage. The suggested topologies in [16,17,18] can effectively decrease the switches' voltage stress. However, it has a greater number of switches. The suggested inverters in [19,20,21,22] use appropriate components to limit the MVS of switches from the power supply voltage. However, in the configurations presented in [19,20,21, 23, 24] there is room for improvement by using fewer capacitors.

1.3 Contribution and paper organization

The multilevel inverter based on the switched-capacitor approach has indeed been developed in this study to alleviate the disadvantages of the previously mentioned inverters in terms of requiring many components, excessive MVS of power switches and absence of voltage gain and voltage self-balancing in capacitors. The suggested inverter may improve the input voltage and achieve voltage self-balancing in capacitors when compared to existing MLIs. Moreover, inverter switches have an MVS that is restricted to lower than the power supply voltage. In comparison with low-voltage-stress SCMLIs, the suggested MLI uses fewer components. Furthermore, the suggested inverter is better in terms of its flexibility and capacity to provide inductive loads. Among the good aspects that make the suggested inverter, an appealing solution for low- and high-photovoltaic (PV) power generation applications is its low voltage stress.

2 Suggested multilevel inverter

2.1 Circuit arrangement

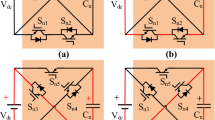

The topologies suggested in [19,20,21,22] have a common feature that one dc voltage source and two T-type voltage-dividing switched capacitors to accomplish a seven-level inverter. The two T-type capacitors are employed to develop the voltage step of \({V}_{\text{dc}}/2\), reducing the output waveforms' step voltage to a value less than \({V}_{\text{dc}}\), which can efficiently minimize the output voltage's total harmonic distortion (THD). However, SCs are not fully used because they are primarily used to divide the voltage and it is not possible to power the load by connecting it in series with the dc power source. As a consequence, such configurations require extra capacitors to create multilevel outputs.

A new nine-level switched-capacitor inverter has been developed in this study to cut down on the number of capacitors and so optimize the usage of the two capacitors as illustrated in Fig. 1b. The proposed topology consists of one dc power source, 11 switches and two capacitors. In this design, the two switched capacitors are used not only to produce the voltage level of \({V}_{\text{dc}}/2\) and also to operate as switched capacitors (SC), obviating the requirement for extra capacitors. Furthermore, the suggested topology is a rebuild of the topology presented in Fig. 1a [25]. The recent topology presented in Fig. 1a develops the seven level only using 10 switches. On the other hand, the proposed architecture generates the nine level while adding one switch. Moreover, the switched-capacitor arrangement ensures boost ability while allowing for a voltage gain of two with the assistance of the half H-bridge to convert the voltage polarity on the load. This feature results in a significant reduction in the MVS of switches as shown in Fig. 1. The suggested inverter can produce nine different levels of output: \(\pm 2{V}_{\text{dc}}\), \(\pm 3{V}_{\text{dc}}/2\), \({\pm V}_{\text{dc}}\), \({\pm V}_{\text{dc}}/2\) and \(\pm 0\).

2.2 Operating principle

The operation of a nine-level inverter is described in this section. Various output voltage steps are produced by switching the off and on positions of each switch. All of the operational positions for the various modes are listed in Table 1.

The numbers 0 and 1 denote the off and on positions of the corresponding switches. The positions of the capacitors are indicated by the symbols "CH," "DS," and "NC" which stand for charging, discharging and no change, respectively.

The current paths and direction in each working mode are depicted in Fig. 2. In addition, charging loop current (\({I}_{\text{ch}}\)) resistive load loop current (\({I}_{\text{o}}\)) and inductive load loop current (\({I}_{\text{L}}\)) directions are presented to show the inductive load handling capability of the proposed inverter. It should be noted that the operating modes from \(0\) to \({V}_{\text{dc}}\) have three current routes and boosting modes \({3V}_{\text{dc}}/2\) and \({V}_{\text{dc}}\)allow two current routes. The first route is that the capacitors are charged in series by the input voltage. The capacitor could power the load in the second path. Finally, the third path proves that the proposed inverter is capable of powering inductive loads.

To charge the capacitors \({C}_{1}\) and \({C}_{2}\), switches \({S}_{5}\), \({S}_{6}\) and \({S}_{9}\) are continuously turned on at levels zero, one and two. During this time, only three switches rather than four compare to recent topology [25] required a high-current rating. To complete the power loss estimate, Table 2 shows the current stresses of all semiconductor switches on each level. Here, \({I}_{\text{ch}}\) is capacitors inrush current and \({I}_{o}\) is the sum of load current. The proposed inverter's main advantage in terms of cost reduction is that only three switches are used to circulate the capacitor current in this circuit.

2.3 Modulation strategy

There are three types of pulse width modulation (PWM): carrier wave PWM, selective harmonic eliminated PWM (SHE-PWM) and space-vector PWM (SV-PWM). The SHE-PWM can minimize the switching frequency, lowering switching losses and increasing the dc voltage usage. However, it is difficult to execute. The SV-PWM approach is appropriate for inverters with three to five voltage steps. This is not suited for inverters that deliver more than five voltage steps due to its intricacy.

In this study, the phase disposition PWM (PD-PWM) is used to create the controlling signals for all switching devices form of carrier signal PWM. This approach has the advantage of being simple to implement, decreasing the intricacy of the driver circuit significantly. To create pulses in a nine-level inverter, eight triangular carriers plus and a sinusoidal modulation wave are needed. Various logic combinations of these pulses are governed by the off and on positions of every switch. Figure 3 shows a block representation of the PD-PWM. The magnitude (\({A}_{c}\)) and frequency (\({f}_{c}\)) of the eight triangular carriers are identical, but their offsets vary. The sinusoidal modulation wave has a magnitude of \({A}_{\text{ref}}\) and a frequency of \({f}_{o}\).

The modulation index is calculated by the magnitude of the carrier and reference waveforms. As a result, the modulation index Mi can be written by

when \({M}_{i}\) varies, and the suggested inverter can alter its output appropriately. Table 2 shows the link between various \({M}_{i}\) values and output levels.

2.4 Design of voltage balancing capacitors

In switched-capacitor-based MLIs, capacitors serve a critical role in power distribution. Their voltage fluctuations should be kept to a manageable level. Capacitor voltage ripple is related to its capacitance, the weight of the load and the time it takes to discharge it. Reduced voltage ripple may enhance output voltage quality, minimize ripple loss and increase inverter efficiency.

It is required to understand a capacitor's maximum discharge quantity to calculate its capacitance. Figure 3 shows that whenever the output voltage is (\({3V}_{\text{dc} }/2\)) and \({2V}_{\text{dc}}\), the capacitor \({C}_{2}\) is discharged. As a result, \({C}_{2}\)'s maximum discharge quantity is equal to the total of C2’s discharge quantities throughout the three t2–t3, t3–t4 and t4–t5 periods. The instants ti (\(i\) = 1, 2, 3, 4, 5) are the points at which the sine and triangle waves intersect and they can be determined using the following equations:

In 1 (2)–(8), M denotes the modulation index (in this case, \({M}_{i}\) = 0.9) and \({f}_{o}\) is the output frequency. The capacitor's discharge amount from \({t}_{1}\) to \({t}_{3}\) can be computed using the following formula:

where \(\Delta {Q}_{1}\) is the discharge amount over the time interval \({t}_{2}\) to \({t}_{3}\) and \({I}_{o}\) denotes the output current. The discharge amount \(\Delta {Q}_{2}\) during the period \({t}_{3}\) to \({t}_{4}\) can be calculated using the same method:

The parameters in (9) are identical to those in (10). The capacitor's operational status is the same during \({t}_{2}\) to \({t}_{3}\) and \({t}_{4}\)–\({t}_{5}\), and the discharge quantity is also identified during the two intervals. As a result, the maximum amount of \({C}_{2}\) that can be discharged is equal to

The capacitance may be calculated using the following formula, suppose \(k\) is the factor indicating the highest permissible ripple voltage:

where \({V}_{C2}\) is the rated voltage of the capacitor of \({C}_{2}\).

Voltage ripples of two capacitors are the same when the symmetrical properties of the operating states of \({C}_{1}\) and \({C}_{2}\) in the positive and negative half-cycles are considered. Thus, \({C}_{2}\) is used as an example. The greatest continuous discharge quantity of \({C}_{2}\) is \(\Delta {Q}_{C2}\) as may be observed from (11). As a result, the voltage ripple of \({C}_{2}\) could be calculated as:

where \(\Delta {V}_{C2}\) is the voltage ripple of capacitor \({C}_{2}\). As shown in (11) by selecting the appropriate capacitance, the ripple can be kept within a tolerable range.

3 Power losses analysis

Three types of losses are considered in switched-capacitor inverters which contain the capacitor ripple losses \(({P}_{\text{rip}})\), conduction losses \(({P}_{\text{con}})\) and switching losses \(({P}_{\text{sw}})\).

3.1 Capacitor ripple losses

The voltage fluctuation of the capacitors produces \(({P}_{\text{rip}})\). Owing to the symmetrical functioning states of the two capacitors, \({C}_{2}\) is still used as an example. The voltage ripple of \({C}_{2}\) is \(\Delta {V}_{C2}\) as indicated in (13); hence, the \(P\) can be computed as follows:

Further computation can be made as follows:

3.2 Conduction losses

The parasitic characteristics of devices are responsible for inverter conduction losses, such as the switch's on-state resistance (\({r}_{s})\) and each capacitor's equivalent series resistance ( \({R}_{c})\).

The equivalent circuit for load supply is shown in Fig. 5. In Fig. 4, \({r}_{\text{eq}}\), \({R}_{o}\) and \({V}_{o}\) are equivalent parasitic resistance, load resistance and output voltage, respectively. Table 3 shows the corresponding parameters in the four operating modes of the positive half cycle.

The output voltage level varies between 0 and \({V}_{\text{dc}}/2\) in the period of [\(0, {t}_{1}\)] as shown in Fig. 3. As a result, the power losses period [\(0, {t}_{1}\)] can be computed using the formula:

In the same approach, the power losses of the additional three operating modes can be calculated.

As a result, the \({P}_{\text{con}}\) can be written as:

3.3 Switching losses

The discharging and charging operations of the parasitic capacitor \({C}_{s}\) in the switches can be used to quantify switching losses. The parasitic capacitor is supposed to have a linear capacitance. The parasitic capacitor's voltage is progressively charged to \({V}_{s}\) when the switch is turned off, where \({V}_{s}\) is the MVS of the switches, and \({V}_{s}\) is reported in Table 4 for each switch.

As a result, the \({P}_{\text{sw}}\) can be determined using the following formula:

where \({f}_{s}\) is the switching frequency of the switches, which may be found in the following formula

\({N}_{s}\) is the number of switching transitions in a single period of the reference waveform.

The switches are periodically turned on or off in the appropriate periods, as shown in Fig. 3. If the switch operates for the entire span, the \(N\) of every switch could be calculated approximately as the ratio of \({f}_{c}\) and \({f}_{o}\). On the other hand, the suggested inverter switches will operate at specific intervals.

As a result, each switch's \({N}_{s}\) can be determined:

where \({t}_{s}\) denote the switch's functioning duration and Figs. 2 and 3 can be used to get it. \({T}_{s}\) is the duration of a single cycle. As a result, \(P\) can be determined using the following formula:

In summary, the proposed inverter's efficiency can be determined as follows:

where \(\eta \) and \({P}_{o}\) denote the proposed inverter's efficiency and output power.

The above losses can be calculated mathematically at varying output powers. It is important to remember that \({r}_{s}\), \({R}_{c}\), \({f}_{c}\), \({f}_{o}\) and \({C}_{s}\) are taken into account at 4 mΩ, 50 mΩ, 50 \(\text{Hz}\), 5 \(\text{kHz}\) and 400 \(\text{pF}\), respectively, for the loss estimates. Figure 5a depicts the proposed nine-level inverter's theoretical efficiency. The three forms of losses can be calculated using a 120 \({V}_{\text{dc}}\) supply and a 60 Ω + 100 \(mH\) load as shown in Fig. 5b follows: \({P}_{\text{rip}}\) = 0.43 W, \({P}_{\text{con}}\) = 0.12 W and \({P}_{\text{sw}}\) = 0.3 W. The proportion of the three categories of losses is shown in Fig. 5c.

4 Horizontal extension topology

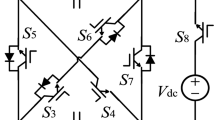

The suggested nine level can be structurally extended to provide a higher number of voltage levels. Figure 6 shows the horizontal extension topology.

The cells extend to the first cell, then to the second and so on until the \({N}{\text{th}}\) cell is reached. Except for the half H-bridge and switch \({S}_{10}\), every cell in the horizontal extension (HE) has the same structure up to the \({N}\)th cell. In the 1st cell, the switches are named \({S}_{11}\), \({S}_{61}\), \({S}_{71}\), \({S}_{81}\)and \({S}_{91}\) and capacitors \({C}_{11}\) and \({C}_{21}\). Similarly, for the 2nd cell, the switches are S52, \({S}_{62}\), \({S}_{72}\), \({S}_{82}\) and \({S}_{92}\) and capacitors \({C}_{11}\) and \({C}_{21}\). Such arrangement can be expanded up to \({N}\)th cell. Here the capacitors are linked parallel and thus boost the voltage levels of an inverter. To bring boosting the operation of HE topology, the steps mentioned below are used.

For double boosting, \({N}\)th cell’s capacitors are discharged while the remaining cell’s capacitors, i.e., [\({1}^{st}\) to \({(N-1)}\)th] are charging. For triple boosting, \({N}\)th and \({(N-1)}\)th cell’s capacitors are discharged while other cell’s [1st to \({(N-2)}\)th] capacitors are charged at the same time and continuously. Similarly, the capacitors are discharged gradually from higher-order to lower-order cells to increase voltage levels step by step. Table 4 portrays the proposed HE switching sequence corresponding to the circuit structure depicted in Fig. 6. Further, Table 5 formulates the states of the capacitors such as charging, discharging and “NO” change to show the boost voltage. In addition, the generalized Eqs. (26)–(31) are given to construct the proposed nine-level S3CMLI (HE).

where \({N}_{IS}\) represents the number of power electronics switches, \({N}_{\text{DC}}\) represents the number of driver circuits, \({\text{N}}_{\text{VL}}\) represents the number of voltage levels, \(N_{C}\) represents the number of flying capacitors, \(V_{{{\text{MOV}}}}\) represents maximum output voltage and \(n\) represents the maximum voltage gain generated by the \(N^{th}\) cell with a single source. At this point, the inverter must satisfy the condition \(n \ge { }2\).

5 Comparison of the proposed topology with others

Table 5 shows the comparison of the proposed topology. Here \(N_{{{\text{IS}}}}\) is the number of power electronic switches, \(N_{{{\text{VL}}}}\) is the number of different voltage levels, \(Nv_{{{\text{dc}}}}\) is the number of input, \(N_{C}\)is the number of flying capacitors, \(N_{{{\text{SC}}}}\) is the number of the switches in the conduction path, \(V_{C} \left( V \right)\) is voltage across the capacitors, \(V_{{{\text{TS}}}} \left( V \right)\) is total standing voltage of the inverter, \(V_{{{\text{BV}}}} \left( V \right)\) is maximum blocking voltage on switches, \(N_{{{\text{CD}}}}\) is number of active devices including diodes, \(V_{{{\text{MOV}}}} \left( V \right)\) is maximum output voltage, \( N_{{{\text{comp}}{. }}} \left( {N_{{\text{IS }}} + N_{D} } \right)\) is the number of components, \(N_{{{\text{ch}}}}\)is the number of devices in the charging loop and \(S = V_{{{\text{TS}}}} \left( V \right)/V_{{{\text{MOV}}}} \left( V \right)\), the ratio of the number of times discharging and charging—\({\text{DC}}/C\) minimum value).

5.1 Comparison of the number of active devices (\(N_{{{\text{CD}}}}\)) and standing voltage per unit (\(S\))

For the nine-level output, the proposed topology takes ten switches that are less than the configurations described in the references [3,4,5, 11, 14, 22, 23].

Table 6 shows that the number of conduction switches in the suggested topology is lower than any of the other topologies. As a result, conduction losses are minimized due to the lesser switch count. Furthermore, with a gain of two, the nine-level architecture utilizes just two capacitors. However, the topologies described in the references [5, 9, 14] employ three capacitors to provide the same voltage gain. Due to these reduced active switches, the power consumption is less, and therefore, the cost of switches becomes low when compared to other topologies. It is one of the notable advantages of the suggested topologies. As compared to other circuits, the nine-level topology is the best in overall efficiency, low voltage stress on the switch and the least amount of loss.

Another significant parameter for switched-capacitor-based topologies is the number of devices in the charging loop (\(N_{{{\text{ch}}}}\)). To manage the capacitor's charging current, the devices in the charging loop must have a greater current rating.

The proposed topology has only two higher-current-rated devices that are needed, whereas the topologies presented in the all references, except [5], require a greater number of devices in the charging loop. The number of switches in the conduction path (\(N_{{{\text{SC}}}} )\) indicates the total number of conduction switches at each voltage level. The ratio of total standing voltage to the maximum output voltage (\(S\)) is also lower in comparison with other MLI except [11]; however, this design needs a higher number of components and capacitors.

5.2 Comparison of cost function (\(CF\))

The cost function is utilized to calculate the overall inverter cost. It is depends on the count of switches, capacitor, switches in the capacitor charging loop, conduction switches in each level and voltage stress per level on the inverter.

A cost function \({\text{CF}}_{{\left( {{\text{Nine}}} \right){ }}}\) has been specified by Eq. (32) for further analysis.

Table 7 shows the multilevel inverter's projected cost function (\({\text{CF}}\)). In addition, \(CF\) is calculated for various combinations of \(\alpha\) and \(\beta\) values. Here, \(\alpha\) and \(\beta\) are the weight coefficients of S and \(N_{{{\text{SC}}}} \left( {{\text{avg}}} \right),\) respectively. When compared to the other described inverter, the proposed topology has a lower \({\text{CF}}_{{\left( {{\text{Nine}}} \right){ }}}\) value. Further, the suggested topology has the fewest numbers of conducting switches at each level compared to other topologies.

5.3 Comparison with voltage levels and low-voltage-stress SCMLIs

Table 8 compares the suggested inverter to the hybrid MLIs that was recently suggested. The comparison was made assuming that almost all inverters have the same MVS across each switch.

These hybrid inverters can keep the voltage burden on the switches to a minimum, which is a quality of the suggested inverter as well. In comparison with the suggested inverter, the hybrid MLIs use additional capacitors except for recent topology however, that recent topology has seven levels only.

Furthermore, the majority of them cannot raise the input voltage. The suggested inverter is better concerning maximum discharge capacity and the number of capacitors, as shown by the \(Q_{m}\) of these inverters. As a result, the suggested inverter has the benefit of having a lower capacitance. Table 7 shows that the suggested inverter addresses the aforementioned flaws and provides superior overall performance.

5.4 Comparison of cost function (CF) for 13-level inverter

The extension of the proposed topology operates with six active switches to produce the triple boost 13-level voltages with the total standing voltage of sixteen. The proposed topology has low voltage stress compared to other topologies shown in Table 8. A cost function \({\text{CF}}_{{\left( {{\text{13\_Level}}} \right){ }}}\) has been specified by Eq. (33).

where \(N_{{{\text{DR}}}}\)—number of driver circuits and \(T_{{{\text{CV}}}}\)—total capacitors voltage.

Table 9 shows the cost factor \({\text{CF}}_{{\left( {{\text{13\_Level}}} \right){ }}}\) for a 13-level inverter is low when compared to other topologies. In addition, the total capacitor voltage (\(T_{{{\text{CV}}}}\)) is low for the extension topology of the proposed topology.

6 Simulation verification and experimental validation

6.1 Simulations

To test the performance of the proposed inverter, a simulation of a nine-level inverter is created in MATLAB/Simulink. Table 11 lists the parameters used in the simulations. The simulation results are depicted in Fig. 7 that the inverter generates PWM waves with nine levels and the current lags the voltage.

6.2 Steady-state analysis

To show the suggested inverter's viability, a nine-level prototype was developed to test its steady-state and dynamic performance. The parameters of the prototype Fig. 8 as well as the experimental apparatus are listed in Table 11. The voltage and current waveforms are analyzed as well as the voltage waveforms of the two capacitors and the voltage stress of switches.

The voltage and current waveforms are analyzed as well as the voltage waveforms of the two capacitors and the voltage stress of switches. An experiment was done in an RL load (60Ω + 100) to assess the suggested inverter's steady-state effectiveness.

The waveforms of output voltage, current and capacitor voltage are shown in Fig. 9a under 50 \({\text{Hz}}\). Each stage has a voltage of 60 V with a maximum output voltage of 240 V. The boost gain of two is reached since the input source voltage is 120 \(V\).

Figure 9a and b depicts the steady-state capacitor voltages. The two capacitors appear to be self-balancing through modest voltage ripples. It is compatible with the capacitor's voltage balancing analysis. Under the same \(RL\)—load conditions, increase the frequency value to 200 \(Hz\). Figure 9b depicts the results. The output reduced magnitude current lags behind the voltage, demonstrating the capacity to supply inductive loads under high frequency.

Figure 10 depicts the voltage stress on the switches. A benefit of the proposed inverter is that the MVS of the switches is restricted to the input power voltage \(V_{{{\text{dc}}}}\). A total of 11 switches are utilized in the proposed nine-level inverter. The voltage stress of \(S_{1}\) to \(S_{9}\) is \(V_{{{\text{dc}}}}\) and \(V_{{{\text{dc}}}} /2\) of \(S_{10}\)(back to back connected).

The current stress of the power switches was tested, and the results are presented in Fig. 11

Because of the capacitors' small voltage changes, all switch current stress is kept to a minimum.

The switches in the capacitor charging circuit are subjected to a maximum current stress of about 4.3 \(A\)

6.3 Dynamic analysis

An effective inverter should be flexible to changing operating conditions such as load fluctuations, input voltage fluctuations, modulation wave frequency and amplitude fluctuations and so on. The inverter's performance in dynamic conditions was further evaluated in the following trials. Figure 15 depicts the output voltage as the modulation wave's amplitude changes. The output voltage changes from nine to seven levels when \(M_{i} \) is changed from 1 to 0.75, as shown in Fig. 12a. The transient procedures are completed quickly, demonstrating the suggested inverter's high dynamic performance. The experimental results are likewise in conformity with the findings of Table 3's analysis.

The proposed inverter can adjust appropriately when the output frequency of the modulation wave varies. As the frequency changes, Fig. 12b illustrates the output voltage, current and capacitor voltage. It is noticed in circumstances where the inverter could transit appropriately with a quick transient reaction (50–200 \(Hz\)).

Figure 13a depicts the experimental findings under the situation of a quick shift in load. The load changes from RL load (60Ω + 100 \(mH\)) to a resistance load (120Ω). The output shows that when the load fluctuates, the inverter operates admirably. Capacitors \(C_{1}\) and \(C_{2}\) charges and discharges when the dc source voltage changes from 120 \(V\) to 100 \(V\) processes, which may simulate the solar cell’s input voltage sudden variations. The inverter functions healthy with the sudden shift in its input voltage, as shown in Fig. 13b. The test results reveal that the inverter has the strong dynamic response in adjusting to changes in the input voltage and can swiftly establish a new steady state.

6.4 Efficiency analysis

The efficiency against different load conditions at various supply voltages is shown in Fig. 14. Furthermore, the efficiency rises as the input voltage rises when the load power remains constant, as shown in Fig. 14. This is due to the fact that the load current will drop, resulting in lower power losses.

6.5 Discussion

Through simulation verification and experimental validation, the suggested inverter's output voltage boosting, capacitors self-balancing and capacity to provide inductive loads were explored. The experimental results demonstrate that with a 120 \(V\) input signal, the output voltage magnitude is 240 \(V\), resulting in a voltage boost of two. The experiment also shows that the capacitor voltages can balance themselves. Furthermore, the capacity to deliver the inductive load is proved through experiments with 60 Ω and 100 \(mH\) loads. The suggested inverter has a low MVS when compared to other SCMLIs: All switches' voltage stress does not surpass the input dc voltage. Furthermore, when the inverter is turned on, the working circumstances may vary, for example rapid variations in the resistive/inductive load, input voltage, as well as the magnitude and output frequency of the sinusoidal wave modulation. These situations are also evaluated by dynamic tests, which demonstrate that the suggested inverter can react to dynamics and swiftly stabilize in a new functional state.

7 Conclusion

This research proposes a new switched-capacitor multilevel inverter with reduced voltage stress and capacitor voltage self-balancing capability. Only two capacitors are necessary to achieve a nine-level output without impacting the switch count.

This topology has the following outcomes and characteristics: (1) Compared to traditional SCMLIs, the proposed inverter's maximum voltage stress of the switches can be limited to less than the input dc voltage. One of the good aspects that result in the suggested inverter being an appealing solution for medium- and high-voltage photovoltaic (PV) power generation applications is its low voltage stress. (2) A voltage boost gain of two can also be achieved thanks to the low voltage stress. (3) To attain a larger voltage boost gain and higher output level, topology extension approaches have been presented, which are superior in their flexible extensibility and ability to feed inductive loads. (4) The suggested inverter's capacitor voltages can be self-balanced, reducing its management complexity. (5) In each working mode, the bidirectional energy loop ensures the capacity to supply the inductive load.

A nine-level experimental prototype has been used to validate the proposed inverter's properties. The inverter exhibits good performance in both steady-state and dynamic settings, according to the experimental results.

References

Li G, Liang J, Ma F et al (2019) Analysis of single-phase-to-ground faults at the valve-side of HB-MMCs in HVDC systems. IEEE Trans Ind Electron 66(3):2444–2453

Sheng W, Ge Q (2018) A novel seven-level ANPC converter topology and its commutating strategies. IEEE Trans Power Electron 33(9):7496–7509. https://doi.org/10.1109/TPEL.2017.2772885

Siddique MD, Iqbal A, Ali JSM et al (2020) Design and implementation of a new unity gain nine-level active neutral point clamped multilevel inverter topology. IET Power Electron 13(14):3155–3162

Nakagawa Y, Koizumi H (2019) A boost-type nine-level switched capacitor inverter. IEEE Trans Power Electron 34(7):6522–6532

Siddique MD, Mekhilef S, Shah NM, Ali JSM (2020) New switched-capacitor-based boost inverter topology with reduced switch count. J Power Electron 20(4):926–937

Kannan M, Kaliyaperumal S (2021) A high step-up sextuple voltage boosting 13S–13L inverter with fewer switch count. IEEE Access 9:164090–164105

Kim KM, Han JK, Moon GW (2021) A high step-up switched-capacitor 13-level inverter with reduced number of switches. IEEE Trans Power Electron 36(3):2505–2509

Barzegarkhoo R, Moradzadeh M, Zamiri E et al (2018) A new boost switched-capacitor multilevel converter with reduced circuit devices. IEEE Trans Power Electron 33(8):6738–6754

Siddique MD, Mekhilef S, Padmanaban S, et al (2021) Single-phase step-up switched-capacitor-based multilevel inverter topology with SHEPWM. IEEE Trans Ind Appl 57(3). Accessed September 7, 2021

Zhang Y, Wang Q, Hu C et al (2020) A nine-level inverter for low-voltage applications. IEEE Trans Power Electron 35(2):1659–1671

Siddique MD, Mekhilef S, Shah NM et al (2019) A new single phase single switched-capacitor based nine-level boost inverter topology with reduced switch count and voltage stress. IEEE Access 7:174178–174188

Samadaei E, Kaviani M, Bertilsson K (2019) A 13-levels module (K-Type) with two DC sources for multilevel inverters. IEEE Trans Ind Electron 66(7):5186–5196

Panda KP, Bana PR, Panda G (2021) A switched-capacitor self-balanced high-gain multilevel inverter employing a single DC source. IEEE Trans Circuits Syst II Express Briefs 67(12):3192–3196

Sandeep N (2021) A 13-level switched-capacitor-based boosting inverter. IEEE Trans Circuits Syst II Express Briefs 68(3):998–1002

Lin W, Zeng J, Hu J, Liu J (2021) Hybrid nine-level boost inverter with simplified control and reduced active devices. IEEE J Emerg Sel Top Power Electron 9(2):2038–2050

Taghvaie A, Adabi J, Rezanejad M (2018) A self-balanced step-up multilevel inverter based on switched-capacitor structure. IEEE Trans Power Electron 33(1):199–209

Ye Y, Chen S, Wang X, Cheng KWE (2021) Self-balanced 13-level inverter based on switched capacitor and hybrid PWM algorithm. IEEE Trans Ind Electron 68(6):4827–4837

Ye Y, Zhang G, Wang X et al (2022) Self-balanced switched-capacitor thirteen-level inverters with reduced capacitors count. IEEE Trans Ind Electron 69(1):1070–1076

Lee SS, Bak Y, Kim SM et al (2019) New family of boost switched-capacitor seven-level inverters (BSC7LI). IEEE Trans Power Electron 34(11):10471–10479

Liu J, Zhu X, Zeng J (2020) A seven-level inverter with self-balancing and low-voltage stress. IEEE J Emerg Sel Top Power Electron 8(1):685–696

Liu J, Wu J, Zeng J (2018) Symmetric/asymmetric hybrid multilevel inverters integrating switched-capacitor techniques. IEEE J Emerg Sel Top Power Electron 6(3):1616–1626

Lee SS, Lee KB (2019) Dual-T-type seven-level boost active-neutral-point-clamped inverter. IEEE Trans Power Electron 34(7):6031–6035

Mohamed Ali JS, Krishnasamy V (2019) Compact switched Capacitor Multilevel Inverter (CSCMLI) with self-voltage balancing and boosting ability. IEEE Trans Power Electron 34(5):4009–4013

Zeng J, Lin W, Cen D, Liu J (2020) Novel k-Type multilevel inverter with reduced components and self-balance. IEEE J Emerg Sel Top Power Electron 8(4):4343–4354

Wang Y, Yuan Y, Li G et al (2021) A T-Type switched-capacitor multilevel inverter with low voltage stress and self-balancing. IEEE Trans Circuits Syst I Regul Pap 68(5):2257–2270

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Oorappan, G.M., Pandarinathan, S. & Arumugam, J. A new nine-level switched-capacitor-based multilevel inverter with low voltage stress and self-balancing. Electr Eng 105, 867–882 (2023). https://doi.org/10.1007/s00202-022-01703-4

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00202-022-01703-4