Abstract

This paper presents a switched-capacitor topology with fewer switching components and reduced voltage stresses. The circuit contains eight switches and two capacitors to generate a five-level voltage waveform. This paper provides in-depth descriptions of the structural design, operation, and loss analysis. Inherently self-balanced capacitors are utilized in the proposed topology, which eliminates the need for additional charge balancing circuits and sensors. The control action was implemented using a simple logic-based multicarrier pulse width modulation (PWM) strategy. A brief comparative analysis with state-of-the-art topologies has been presented to demonstrate the merits of the developed topology. Finally, the feasibility and efficacy of the suggested topology have been evaluated using simulation and experimental testing to ensure that it is both feasible and effective.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Renewable and sustainable energy sources, such as solar and wind farms, have gained considerable attention from researchers and industry in recent years due to their reduced environmental effect and increasing economic benefits. Due to the rapid improvements in power electronics equipment technology, numerous power converter topologies for new energy/power systems have been developed. Multilevel inverters (MLIs) are the most popular of these topologies. This is to the reduced dv/dt stress on the switch, high power quality, reduced filter size, greater efficiency, reduced EMI, etc. [1, 2].

Standard multilevel inverters are generally classified as diode clamped, flying capacitor (FC), and cascading H-bridge (CHB) inverters. These traditional inverters have several advantages over two-level inverters. These advantages include lower switching and conduction power losses, better efficiency, and a significantly improved power quality. On the other hand, these topologies have several drawbacks. Diode clamped and flying capacitor inverters having issues with capacitor voltage balancing and requiring more clamping diodes to achieve higher voltage levels [3]. Requiring several isolated DC sources for an increased number of voltage levels constitutes the main constraint of CHB inverters [4]. The voltage gain of all of the modules listed above is limited to one, which is a common limitation among classical multilevel inverters. These difficulties may make these converters unsuitable for industrial uses. Achieving the maximum voltage level from a DC source is advocated in [5]. In addition, there is a lack of voltage boosting capacity in modified structural designs.

As a result, there is a rising trend towards designing novel switched-capacitor (SC) inverter topologies with integrated voltage boosting, self-balancing of capacitor voltage self, and a reduced number of device components. SC configurations can be classified into two categories: single-stage and two-stage structures. Single-stage configurations have several advantages over two-stage configurations, especially the absence of a rear-end H-Bridge. The rear-end H-bridge provides switches with high voltage stress [6, 7]. As a result, high voltage applications are restricted since the backside H-bridge requires switches with a rated voltage that is equal to the peak output voltage. In [8], a single-stage five-level topology was proposed with lower voltage stress and a reduced component count when compared to previous designs. The authors of [9,10,11,12,13] presented multiple cases of five-level topologies. However, these topologies have a limited ability to boost input voltage. Similarly, in [14,15,16,17], 5-level topologies employed an increased number of switching components to achieve a voltage gain of two. In [18, 19], a five-level architecture was presented that is deficient in terms of its boosting capability. The authors of [20], proposed a nine-tier topology that used 11 switches and two capacitors to achieve a voltage gain of two. In addition, the topology in [21] can enhance the gain. However, generalized SC structures require more switching components. The authors of [22, 23] proposed a five-level flying capacitor topology that consists of ten switches and four capacitors. In practice, this is less attractive since it has more switching elements. The authors of [24, 25] presented the simplest topology with the smallest number of power components. However, it needs to use two separate dc sources, which severely restricts its application. The configurations in [26,27,28] allow multilevel inversion while having a high step-up voltage level and a compact design, which is largely due to the switched-diode capacitor cell. However, additional capacitors and diodes were required, and their modulation schemes were complex.

The abovementioned deficiencies were the main reason for developing new single-stage SCMLI architecture with the following unique features.

(a) 2 × boosting capability.

(b) The use of a single dc source.

(c) A reduction in the number of switching components.

(d) The capacitor voltage is automatically balanced to ensure proper operation.

(e) Twenty-five percent of the switches are conducting for any generating level other than zero.

(f) It is well suited for low and medium-voltage applications.

2 Proposed topology

2.1 Circuit description

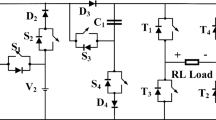

Figure 1 shows the structural design of the five-level SC topology. In the proposed topology, the requirements of the power switches are such that out of eight switches (S1–S8), two switches (S1, S5) need to be unidirectional-conducting-unidirectional-blocking (UCUB), while the remaining switches need to be bidirectional-conducting-unidirectional-blocking (BCUB). Five voltage levels (\(\pm 2{V}_{\mathrm{DC}},\pm 1{V}_{\mathrm{DC}},0\)) are generated by single dc source and two capacitors. Table 1 shows the proper switching pattern at various voltage levels. In this table '0' and '1' symbolize switch OFF and switch ON. The charging and discharging of capacitors are identified by “\(\Delta\)” and “\(\nabla "\), respectively. Capacitors charge in the direction of the red-dotted line, while the blue dotted line represents the path taken to synthesize the voltage level. The terminals x and y are depicted as the load terminals.\({v}_{xy}\left(t\right)\) shows the load voltage. In Fig. 1, the terminals labeled x and y are the load terminals.

2.2 Circuit operation

For better understanding, the equivalent circuits illustrated in Fig. 2a–f are used to describe the operating principle of the proposed topology.

-

(a)

Level 1 \({{\varvec{v}}}_{{\varvec{x}}{\varvec{y}}}\left({\varvec{t}}\right)=0\)

The switches S1, S3, S5, and S7 can simultaneously turn on to reach this level. Both of the capacitances C1 and C2 are charged to \({V}_{\mathrm{DC}}\). Figure 2a, b depict the direction of the load current as well as the charging route of the capacitors.

-

(b)

Level 2 \({{\varvec{v}}}_{{\varvec{x}}{\varvec{y}}}\left({\varvec{t}}\right)={+1{\varvec{V}}}_{\mathbf{D}\mathbf{C}}\)

To reach this level, make sure the switches S3, S5, and S6 all turn on simultaneously. At this level, the capacitor C2 is charged to \({V}_{\mathrm{DC}}\). Figure 2c depicts the direction of the load current and the charging route of the capacitors.

-

(c)

Level 3 \({{\varvec{v}}}_{{\varvec{x}}{\varvec{y}}}\left({\varvec{t}}\right)={+2{\varvec{V}}}_{\mathbf{D}\mathbf{C}}\)

To reach this level, turn the switches S3, and S8 on. The stored energy of the capacitor is transferred to the load along with the voltage \({V}_{\mathrm{DC}}\). This circuit is represented using the equivalent circuit diagram in Fig. 2d.

-

(d)

Level 4 \({{\varvec{v}}}_{{\varvec{x}}{\varvec{y}}}\left({\varvec{t}}\right)={-1{\varvec{V}}}_{\mathbf{D}\mathbf{C}}\)

It is possible to attain this level by turning switches S1, S2, and S7 on simultaneously. C1 is charged to the voltage \({V}_{\mathrm{DC}}\). An equivalent circuit diagram for this level is shown in Fig. 2e.

-

(e)

Level 5 \({{\varvec{v}}}_{{\varvec{x}}{\varvec{y}}}\left({\varvec{t}}\right)={-2{\varvec{V}}}_{\mathbf{D}\mathbf{C}}\)

The switches S4 and S7 are turned on concurrently for this level. Together with \({V}_{\mathrm{DC}}\), the capacitor C1 releases the energy to the load. Figure 2f depicts the equivalent circuit for this particular level.

2.3 Acceptable capacitance design standards

Capacitance has a significant impact on the cost, size, and efficiency of DC/AC converters. In this case, the capacitance needs to be optimized. The capacitance value is calculated using the following parameters. The length of time the capacitor must be discharged before the next charge, the maximum load current, and the tolerable voltage ripple. Thus, capacitors should be chosen to satisfy the following criterion:

According to the proposed topology, the discharging amount of the capacitor C2 can be represented as in [6] so that:

Considering the modulation index unity, the values of \({t}_{1}\), \({t}_{2}\), \({t}_{3}\), and \({t}_{4}\) can be obtained from the staircase output voltage of the inverter.

where ‘f’ and ‘\({i}_{0}\)’ represents the fundamental frequency and peak inverter output current respectively. In addition, \(\varnothing\) is the power factor angle of the load. Therefore, the required capacitance value can be estimated with a maximum permissible voltage ripple of 10% of the maximum capacitor voltage as:

The value of C1 can be assessed in a similar fashion.

2.4 Self-balancing mechanism of capacitors

The switching Table 1 and the voltage levels are shown in Fig. 2a–f demonstrate that the capacitors C1 and C2 are charging and discharging as a result of the series/parallel approach [20]. The capacitor C1 and C2 are charged to VDC during the level of zero and \(\pm 1{V}_{\mathrm{DC}}\). C1 dissipates energy during the negative half of the cycle, while C2 dissipates energy during the positive half of the cycle. This results in an output voltage that is twice the supply voltage. Due to these charging and discharging processes, the capacitors are naturally self-balanced. As a result, the need for a separate circuit to assist the circuit in self-balancing is eliminated.

3 Control strategy

Inverter switching pulses are generated using a variety of control techniques. There are two types of control techniques: low switching frequency and high switching frequency [21]. A universal multicarrier pulse width modulation (PWM) method, as shown in Fig. 3a, has been implemented and tested in this study. Four carrier frequencies (\({f}_{c1}\sim {f}_{c4}\)) with magnitudes of 2 kHz are constantly compared with the modulating signal of the frequency (\({f}_{r})\) of 50 Hz. Their outputs are combined to produce an aggregated signal a(t). According to Fig. 3a, the aggregated signal is compared with constant using mapped values. Figure 6b depicts the reference signal, the carrier signal, and the output voltage.

4 Power losses analysis

The following section provides information on the switching losses, conduction losses, and capacitor ripple losses associated with the proposed topology. The total power losses \({(P}_{T})\) can be expressed as:

4.1 Switching losses (\({{\varvec{P}}}_{\mathbf{s}\mathbf{w}})\)

Switching losses occur when switches are turned on and off. The switching power losses can be expressed mathematically as [21]:

where \({V}_{\mathrm{on}},{ V}_{\mathrm{off}}\) are the voltages across the switches before and after they are turn-on. \({I}_{\mathrm{on}},{ I}_{\mathrm{off}}\) are the currents flowing through the switches after turn-on and before the turn off respectively.\({t}_{\mathrm{on}}\), \({t}_{\mathrm{off}}\) are the turn-on and turn-off time of the switch. \(f\) denotes the fundamental frequency.

4.2 Conduction losses \({({\varvec{P}}}_{{\varvec{c}}})\)

The internal resistance of the power switches (\({R}_{s}\)) and the diode \({(R}_{d}\)) dissipates power when they are in the conduction mode, which results in conduction losses. The losses associated with the power switches and diodes can be expressed as follows [21]:

where \({V}_{\mathrm{s},\mathrm{on}}\),\({V}_{\mathrm{d}.\mathrm{on}}\) are the on-state voltages of switch and diode, respectively. \({I}_{\mathrm{s},\mathrm{avg}}, {I}_{\mathrm{d},\mathrm{avg}}{, I}_{\mathrm{s},\mathrm{rms}}, {I}_{\mathrm{d},\mathrm{rms}}\) Specify the average and rms currents of the switch and diode, respectively. As a result, the total conduction losses associated with the proposed topology are:

where \(i\) is the number of switches/diodes, and \(k\) is the number of the conduction path.

4.3 Ripple losses (\({{\varvec{P}}}_{{\varvec{R}}}\))

The potential difference between the power source and the capacitor during the charging/discharging intervals causes ripple losses in SC inverters. The voltage ripple (\(\Delta {V}_{c}\)) of each capacitor can be expressed as follows [5]:

where \({i}_{C}(t)\) is the current flowing through the capacitor during the discharge interval (\({t}_{a}, {t}_{b}\)). (\({t}_{1}\), \({t}_{2}\)) and (\({t}_{3}\), \({t}_{4}\)) are the longest discharge intervals of C2 and C1 for the proposed inverter. It is then possible to compute the ripple loss associated with a fundamental cycle of the output voltage as:

Consequently, the overall efficiency of the proposed five-level inverter can be represented as:

\({P}_{\mathrm{out}}\) is the output power of the proposed inverter.

5 Simulation and experimental results

To ensure the theoretical validity and usability of the suggested topology, it has been tested on both the MATLAB/Simulink program and a hardware configuration. Table 2 presents the simulation and environmental parameters that have been used.

5.1 Simulation outcomes

The proposed topology has been examined theoretically in MATLAB/Simulink under transient conditions. Figure 4a–c show the output voltage, output current, and capacitors voltage under transient conditions. It has been observed that the peak value of the load voltage is two times the supply voltage (i.e., vxy(t) 100\(V\)), and the capacitors maintained their self-balancing effect in all of the cases. Moreover, Fig. 4a shows that the load voltage remains unchanged during a step change in load conditions. Figure 4b shows a change in the switching frequency from 100 Hz to 2 kHz. Figure 4c shows output voltage changes according to the modulation index (0.95–0.5 and 0.5–0.2) and rapidly reached the new state. To determine the switching and conduction losses associated with the proposed model, simulations were performed using PLECS software with a 30Ω pure resistive load.

5.2 Experimental outcomes

With a resistive load of 30Ω, the FFT analysis of \({v}_{xy}\left(t\right)\) results in a rms output voltage of 67.54 V, with a total harmonic distortion (THD) of 11.6%. Similarly, the FFT analysis of \({i}_{xy}\left(t\right)\) reveals a rms current of 2.214 A, with a 5.2% THD. 152, 5.845, 3.465, and 0.4 W represent the total output power, switching losses, conduction losses, and ripple losses, respectively. In this case, the efficiency of the inverter is 93%.

A laboratory prototype has been developed to experimentally evaluate the effects and practicality of the proposed five-level SC architecture. The UCUB configuration for the switches S1 and S5 is implemented with MOSFETs (IRF640NPBF) with series-connected diodes (MBR30100CT). In this experimental work, for the 8 power switches (S1–S8) a total of 8 gate-driver ICs (TLP250) soldered at the back of the PCB with a multi-output (multi-winding) transformer was also employed for electrically isolated supplies. Figure 5 shows the experimental setup designed with the parameters given in Table 2.

(i) Steady-state analysis Figure 6a shows the results of experiments in the absence of a load and under steady state conditions. In the absence of a load, it generates a voltage of five levels, and has a maximum value of 100 V. Moreover, a steady-state study was performed for a R–L load (30Ω, 50 mH). Figure 6a shows that the suggested architecture provides five-level voltages with 50 V in each of the steps. The capacitors are self-balanced, and the voltage ripples are minimal.

(ii) Dynamic response analysis Dynamic conditions such as a step-change in the load, a change in the switching frequency, and a change in the modulation index are used to assess the performance of the inverter. Results of these dynamic conditions are depicted in Fig. 6b–d. Figure 6b shows a step-change in the loading condition. It can be seen that, despite the abrupt change in load, the voltage level of the system stays unchanged, and the voltage of the capacitors is completely self-balanced. Figure 6c shows that the changes in the switching frequency affect the output voltage and current i.e., when the switching frequency was changed from 100 Hz to 2 kHz, it shows that the output voltage and current quickly respond to the sudden change. The modulation index changing from 0.95 to 0.5 and then back to 0.5 to 0.2 is shown in Fig. 6d. This shows that the inverter completes its transient processes quickly. Experimental results of the FFT analysis are displayed in Fig. 7a, b. The efficiency obtained from the experimental setup by a power quality analyzer (fluke 43B) is 92.86%. The obtained efficiency is slightly lower than the findings from the simulation. The test findings coincide with the modeling result, which demonstrates the viability of the proposed structure.

6 Comparative analyses

The merits of the proposed SC topology have been compared with the conventional and prior state-of-the-art topologies in terms of the number of switching components per level factor, total standing voltage, DC source requirements, boosting capability, and cost function. Table 3 includes a comprehensive comparison of several aspects of various designs.

6.1 DC sources

Table 3 shows that the CHB architecture and the architecture in [19] necessitate several dc supply inputs to generate five voltage levels. This ultimately increases the cost and complexity of the circuit by including many input sources. Since the proposed topology needs only one DC source, the circuit design is inexpensive and simple.

6.2 Switching components per level factor

The switching components per level factor \({F}_{c/l}\) is defined as the relationship between the total number of switching components and the total number of possible voltage levels. This factor can be mathematically expressed as:

This is a proportional factor since it is proportionate to the topologies total cost and overall size. The suggested topology has the benefit of low switching components per level factor when compared to the CHB, NPC, FC, and the topologies in [10,11,12,13, 17, 22]. The topology in [11] has the least components per level factor. However, its gain is limited.

6.3 Total standing voltage (TSV)

Total standing voltage is defined as the sum of the blocking voltages of all individual switches. For the creation of the novel multilevel inverter architecture, this is extremely important. The topologies in [22, 27] have higher values of TSV + PIV. When compared to the proposed topology, the topologies [9,10,11, 13, 15, 17, 26, 32] have a comparatively low total standing voltage. However, other factors such as the absence of boosting capability and the high component count per level factor make them less attractive and economical.

6.4 Voltage boosting capability

The quality of the power is determined by the THD. It also serves the needs of various interconnection systems such as renewable grid systems, electric vehicles, and so on. In Table 3, it can be seen that the traditional topology and the topologies in [9,10,11,12,13,14, 19, 26, 32] are unable to increase the input voltage. Therefore, electric cars cannot use these topologies.

6.5 Cost function

This section is crucial for evaluating the overall cost since it allows for the assessment of the overall cost. The switching components and the total standing voltage (TSV + PIV) are closely related to the cost function and are expressed as (20):

When the TSV and switching components are given equal significance, the value of ∝ is one, and when the switching components are given more priority, the value of \(\propto\) is larger than one, and vice versa. For the proposed topology ∝ is treated as a single entity. Except for [10,11,12,13, 15, 26, 27], it is clear from Table 3 that the total cost of the proposed structural design is projected to be modest.

7 Discussions of findings and applicability

As demonstrated by the simulation and experimental results for the proposed architecture, a five-level waveform with twice the voltage gain is generated. The chosen values ensure that the capacitors operate satisfactorily in terms of voltage ripples at a full load. The power loss distribution in the switches indicates that the proposed topology is more efficient. In terms of possible applications for the suggested topology, the following have been found based on a review of the literature on SCMLIs.

7.1 High-frequency ac distribution

The high-frequency alternating current (HFAC) power distribution system (PDS) has become increasingly popular in high-power density applications such as telecommunication, spacecraft, and computer systems due to its significant reduction in the number of power conversion stages [28], transformer size, and filter size. The use of a HFAC PDS in small-scale networks such as micro grids, buildings [29], and electric vehicles [24] is another new application for this technology. Due to the capacitor voltage imbalance difficulties in these applications, standard multilevel topologies with more than five levels are less feasible [30]. Thus, SCMLIs have become a preferred choice for HFAC applications [8]. SCMLI topologies reduce the need for magnetic circuits or dc-dc boost converters at low voltage sites.

7.2 Photovoltaic (PV) based power generation systems and electric vehicle (EV) traction system

The power available through renewable energy, such as photovoltaic systems, is relatively low. Voltage boosting is achieved either by cascading PV modules, using a dc-dc boost inverter, or using a step-up transformer. All of these technique increases the number of components, costs, volume, and power losses [31]. However, the use of SCMLIs provides a good voltage gain, capacitor self-balancing, high-resolution waveforms for grid compatibility, and decreased filtering requirements [32].

8 Conclusion

A new innovative SC multilevel inverter with five voltage levels and a lower device count was presented in this article. In-depth descriptions of the topological design, operation, and power losses were provided. A simple logic-based PWM technique was implemented to provide a smooth control approach. The proposed architecture can include a small number of switching components, a self-balancing capacitor voltage, and a low-cost function. The advantages of the proposed topology over prior state-of-the-art topologies were shown via comparative investigations. Proofs of the concept were given with experimental results that show good agreement with MATLAB/Simulink findings, which indicates the efficacy and practicality of the proposed topology.

References

Gupta, K.K., Ranjan, A., Bhatnagar, P., Sahu, L.K., Jain, S.: Multilevel inverter topologies with reduced device count: a review. IEEE Trans. Power Electron. 31(1), 135–151 (2016)

Leon, J.I., Vazquez, S., Franquelo, L.G.: Multilevel converters: control and modulation techniques for their operation and industrial applications. Proc. IEEE 105(11), 2066–2081 (2017)

Rodriguez, J., Lai, J.S., Peng, F.Z.: Multilevel inverters: a survey of topologies, controls, applications. IEEE Trans. Ind. Electron. 49(4), 724–738 (2002)

Malinowski, M., Gopakumar, K., Rodriguez, J., et al.: A survey on cascaded multilevel inverters. IEEE Trans. Ind. Electron. 57, 2197–2206 (2010)

Gupta, K.K., Jain, S.: Topology for multilevel inverters to attain the maximum number of levels from given DC sources. IET Power Electron. 5(4), 435–446 (2012)

Hinago, Y., Koizumi, H.: A switched-capacitor inverter using series/parallel conversion with an inductive load. IEEE Trans. Ind. Electron. 59(2), 878–887 (2012)

Babaei, E., Gowgani, S.S.: Hybrid multilevel inverter using switched capacitor units. IEEE Trans. Ind. Electron. 61(9), 4614–4621 (2014)

Jena, K., Panigrahi, C. K. Gupta, K. K.: A single-phase step-up 5-level switched-capacitor inverter with reduced device count. In 2021 1st International Conference on Power Electronics and Energy (ICPEE), pp. 1–6 (2021)

Siddique, M.D., Mekhilef, S., Shah, N.M.: New switched-capacitor-based boost inverter topology with reduced switch count. J. Power Electron. 20(4), 926–937 (2020)

Saeedian, S.M., Hosseini, J.: Adabi: Step-up switched-capacitor module for cascaded MLI topologies. IET Power Electron. 11(7), 1286–1296 (2018)

Samanbakhsh, R., Taheri, A.: Reduction of power electronic components in multilevel converters using new switched capacitor-diode structure. IEEE Trans. Ind. Electron. 63, 7204–7214 (2016)

Wang, H., Kou, L., Liu, Y.F., et al.: A seven-switch five-level active-neutral point-clamped converter and its optimal modulation strategy. IEEE Trans. Power Electron. 32, 5146–5161 (2017)

Gautam, S.M., Sahu, L., Gupta, S.: A single-phase five-level inverter topology with switch fault tolerance capabilities. IEEE Trans. Ind. Electron. 64(3), 2004–2014 (2017)

Barzegarkhoo, R., Zamiri, E., Vosoughi, N., Kojabadi, H.M., Chang, L.: Cascaded multilevel inverter using the series connection of novel capacitor-based units with minimum switch count. IET Power Electron. 9, 2060–2075 (2016)

Meysam, S., Hosseini, S.M., Adabi, J.: A five-level step-up module for multilevel inverters: topology, modulation strategy, and implementation. IEEE J. Emerg. Sel. Top. Power Electron. 6(4), 2215–2226 (2018)

Lee, S.S., Lim, C.S., Siwakoti, Y.P., Lee, K.: Dual-T-Type 5-Level cascaded multilevel inverter (DTT-5L-CMI) with double voltage boosting gain. IEEE Trans. Power Electron. 35(9), 9522–9529 (2020)

Niu, D., Hao, T., Gao, F., Qin, F., Ma, Z., Zhou, K., Li, W.: A novel switched-capacitor five-level T-Type inverter. In IEEE, 2nd International Conference on Smart Grid and Renewable Energy (SGRE) (2019)

Ye, Y., Chen, S., Zhang, X., Yi, Y.: Half-bridge modular switched-capacitor multilevel inverter with hybrid pulse width modulation. IEEE Trans. Power Electron. 35(8), 8237–8247 (2020)

Ruiz-Caballero, D.A., Ramos-Astudillo, R.M., Mussa, S.A., Heldwein, M.L.: Symmetrical hybrid multilevel dc/ac converters with a reduced number of insulated dc supplies. IEEE Trans. Ind. Electron. 57(7), 2307–2314 (2010)

Taghvaie, A., Adabi, J., Rezanejad, M.: A self-balanced step-up multilevel inverter based on switched-capacitor structure. IEEE Trans. Power Electron. 33(1), 199–209 (2017)

Bhatnagar, P., Agrawal, R., Dewangan, N.K., Jain, S.K., Gupta, K.K.: Switched capacitors 9-level module (SC9LM) with reduced device count for multilevel DC to AC power conversion. IET Electric Power Appl. 13(10), 1544–1552 (2019)

He, L., Cheng, C.: A flying-capacitor-clamped five-level inverter based on bridge modular switched-capacitor topology. IEEE Trans. Ind. Electron. 63(12), 7814–7822 (2016)

Panda, K.P., Bana, P.R., Panda, G.: A switched-capacitor self-balanced high-gain multilevel inverter employing a single DC source. IEEE Trans. Circuits Syst. II Express Briefs. 67, 3192–3196 (2020)

Liao, Y.H., Lai, C.M.: Newly-constructed simplified single-phase multi string multilevel inverter topology for distributed energy resources. IEEE Trans. Power Electron. 26(9), 2386–2392 (2011)

Gupta, K.K., Jain, S.: A novel multilevel inverter based on switched DC sources. IEEE Trans. Ind. Electron. 61(7), 3269–3278 (2014)

Gao, F.: An enhanced single-phase step-up five-level inverter. IEEE Trans. Power Electron. 31(12), 8024–8030 (2016)

Chen, J., Wang, C., Li, J.: Single-phase step-up five-level inverter with phase-shifted pulse width modulation. J. Power Electron. 19(1), 134–145 (2019)

Chen, J., Hou, S., Deng, F., Chen, Z., Li, J.: An interleaved five-level boost converter with voltage-balance control. J. Power Electron. 16(5), 1735–1742 (2016)

Antaloae, C.C., Marco, J., Vaughan, N.D.: Feasibility of high frequency alternating current power for motor auxiliary loads in vehicles. IEEE Trans. Veh. Technol. 60(2), 390–405 (2011)

Ceglia, G., Guzman, V., Sanchez, C., Ibanez, F., Walter, J., Gimenez, M.I.: A new simplified multilevel inverter topology for DC-AC conversion. IEEE Trans. Power Electron. 21(5), 1311–1319 (2006)

Kuncham, S.K., Annamalai, K., Subrahmanyam, N.: A two-stage Type hybrid five-level transformerless inverter for PV applications. IEEE Trans. Power Electron. 35(9), 9510–9521 (2020)

Chen, M., Loh, P.C., Yang, Y., Blaabjerg, F.: A six-switch seven-level triple-boost inverter. IEEE Trans. Power Electron. 36(2), 1225–1230 (2021)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Jena, K., Panigrahi, C.K., Gupta, K.K. et al. Generalized switched-capacitor multilevel inverter topology with self-balancing capacitors. J. Power Electron. 22, 1617–1626 (2022). https://doi.org/10.1007/s43236-022-00456-4

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s43236-022-00456-4