Abstract

In this paper, a two-stage, single-phase, multilevel dc/ac converter for PV system is proposed. The typical two-stage inverter in PV systems requires a high dc-link voltage, and a step-up dc/dc converter is used. However, a two-stage power conversion requires a high number of power electronic components, resulting in higher cost and lower efficiency. Compared to the similar seven-level inverter, the proposed topology provides three times step-up voltage ratio and a smaller number of circuit components. The introduced topology consists of two stages, the front stage is a step-up dc/dc converter-based switched capacitor circuit. This stage provides high voltage boasting ratio and self-balancing dc-link voltage capacitors capability. Furthermore, a soft switching operation for the power switching devices is implemented using the LC-resonant circuit; thus, peak current amplitude can be regulated, electromagnetic noise and switching losses are significantly decreased. The second stage is a seven-level dc/ac inverter and has the advantages of fewer numbers of semiconductor devices. The operating principles and the modulation scheme of both stages are analyzed and discussed. Simulation and experimental results are provided to prove the effectiveness of the presented topology under different operating conditions.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Nowadays, non-conventional energy resources are popular because of the growing concerns of electric power sustainability and global warming. The long-term plan for energy production mainly depends on the non-conventional energy resources [1, 2]. In conjunction with the conventional energy sources, the photovoltaic and wind energy systems as clean renewable energy sources are built around the world to accommodate power demands, avoid energy crises, and in some cases operate as power conditioning units. The single-phase or the three-phase power converters are used as an interface between renewable energy sources and power systems, and these converters can be either grid-connected or stand-alone. Typically, the employment of these power converters mainly relies on their cost, which limits the implementation of the renewable energy sources in the power system applications. Therefore, developing low-cost and high-quality power converters can be the main challenges for renewable energy sources integration [3]. Depending on the voltage range of PV modules, the PV system can be directly connected to the voltage source inverter, or a boost stage can be inserted to further extend the voltage level [4,5,6,7]. For the implementation in residential or commercial sector, the two-level inverter is commonly used as an interface with the PV system. However, for the application of grid-connected systems, power grid standards, power quality, robustness, and reliability must be ensured. In the last decade, multilevel inverters have become a mature technology and draw more attention in renewable energy applications. It is intensively used in high- and medium-voltage conversion systems [8, 9]. The main distinct features of the multilevel inverters include higher-voltage level and better quality in the output waveform. These advantages result in smaller filter size, lower switching losses, and higher electromagnetic interface immunity. Furthermore, the multilevel structure enables converter using switching devices with low voltage stress; thus, high efficiency can be achieved, and low-cost devices can be selected. Additionally, utilizing the recent development of semiconductor devices, multilevel inverters are further improved in their efficiency and size reduction for different applications.

Various multilevel topologies are introduced in many papers, and other new are still analyzed and investigated for different applications. Among these topologies, the cascaded H-bridge (CHB) inverter is the most deployed topology to synthesize a multiple output voltage level [10]. It was first proposed in 1990s, the symmetric structure, modularity, and high redundant switching states are the most prominent features of the topology [11]. However, the large number of switching devices, multiple dc sources, and dc-links are the most drawbacks of CHB topology. And as each of the dc-links require a large size of electrolytic capacitors, the lifetime and reliability of the converter are greatly reduced. These drawbacks can increase the cost, size, and the control complexity. Another widely used topology is the neutral point clamped (NPC) converter [12,13,14]. This topology has the drawback of unbalanced capacitor voltage problems. Therefore, a very complicated control strategy is needed. Other various common topologies implemented in different applications include active NPC topology [15], hybrid NPC topology [16], flying capacitor topology, modular multilevel topology [17], T-type topology [18], and other hybrid combined topologies based on CHB topology, flying capacitors topology, and NPC topology [19,20,21].

Nowadays, multiple researchers have studied the challenges of multilevel inverters and new configurations to reduce the implementation cost and packaging size are proposed. In other words, topologies with a smaller number of power electronics devices and dc power sources are required [22]. In a single-phase topology, the imbalance voltage of the dc-link capacitors and voltage step-up are other obstacles of the implementation of multilevel inverters. In [23], a single-phase seven-level packed U-cell inverter is proposed and analyzed. It consists of one dc source and six power switches, and one flying capacitor. The topology shows a massive reduction in the number of switching devices and storage elements. However, the packed U-cell inverter suffers from the imbalance voltage problem and requires front-stage step-up dc/dc converter to generate higher-voltage level at the output. One method to reduce the number of independent dc sources and generate higher output voltage is using switched capacitor circuits. Switched capacitor circuit requires a high number of switching devices and capacitors, but the inherited voltage boosting and self-voltage balancing capabilities are the prominent features. The switched capacitor circuits use the series and parallel switching conversion to generate multilevel voltages from a single dc voltage source. A discrete multilevel output voltage is generated by connecting single or multiple capacitors in parallel with the input dc source and discharged in series. Switched capacitor circuits are free of magnetic components such as inductors and transformers, which make it an attractive solution for many applications that require voltage boosting stage and small size packaging. The multilevel inverters with a two-stage structure are introduced in [24, 25]. Typically, the front-end stage is a switched capacitor unit, and the back-end stage is a traditional H-bridge inverter. It is noticeable that as the switched capacitor unit increases the total voltage level increases. But the peak inverse voltage of the H-bridge inverter is the total voltage sum of all switched capacitor units. In [26], an asymmetrical multiport switched capacitor-based multilevel inverter is presented. However, due to asymmetrical structure, the multilevel inverter must withstand a very large peak inverse voltage. In [27], a novel two-stage multilevel structure is proposed. The total standing voltage of the switching devices equals the input dc source, but it has no boosting capability, and the amplitude of output voltage equals the input voltage. In [28], a seven-level switched capacitor-based multilevel with cascaded H-bridge inverter is proposed. Although multiple dc sources are required, this topology only uses one dc source and replaces others with electrolytic capacitors; however, a complex voltage balancing technique limits its application. In [29], a self-balanced switched capacitor multilevel inverter is proposed. The voltage stress for all devices equals the input voltage, but many power switches are required.

In this article, a two-stage single-phase, seven-level dc/ac converter for solar PV system is proposed. The topology can solve the previously discussed drawbacks of using switched circuit in multilevel inverters. The first stage is switched capacitor circuit-based dc/dc converter, and the main function is providing three times voltage boosting ratio and balancing the dc-link capacitors voltages. The topology requires one input dc source to produce seven-level output voltages. The dc/dc converter is fully operated with soft switching technique and the maximum voltage for the switching devices is the same and equals the input voltage. The second stage is a seven-level dc/ac inverter with a greatly reduced number of power switching devices. Since the dc-link voltage is balanced by the first stage, a simple level-shifted carrier-based modulation scheme is implemented. Furthermore, a techno-economic analysis for a two-stage system based on a comparative study among different topologies is conducted. Various techno-economic analysis methods are proposed in literature [30,31,32], and using these techniques explore the system improvement in the performance and the cost reductions. The paper structure is as follows: Sect. 2 introduces the proposed two-stage converter and Sect. 3 presents the voltage tripler balancing dc/dc converter and its operating principles. Section 4 discusses the proposed seven-level dc/ac inverter, and the implemented modulation scheme. To verify the operation principles of the proposed two-stage converter, simulation results are provided in Sect. 5, and the experimental results are given in Sect. 6.

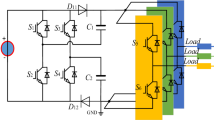

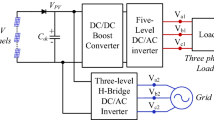

2 Proposed Two-Stage Seven-Level DC/AC Inverter

Figure 1 illustrates the proposed two-stage multilevel dc/ac converter. The front-end stage is a voltage tripler dc/dc converter, where the voltage of the PV arrays is boosted up to three times. The converter consists of two identical units, and each unit represents a single dc/dc converter-based switched capacitor circuit. The units share the same input dc voltage, and the output voltage of each unit is a Vdc. However, the overall output voltage of the first stage is the output voltage sum of all units in addition to the input dc voltage. The second stage is a single-phase seven-level dc/ac inverter. The prominent features of the proposed topology are the following:

-

1.

The proposed topology has triple output voltage using a fewer number of power switching devices when compared to the conventional topologies; thus, the system size can be greatly reduced.

-

2.

The proposed topology is capable of self-balancing the dc-link capacitor voltages. In the convention single-phase multilevel inverter, it is very difficult to increase the number of voltage levels higher than five, due to the complexity of dc-link voltage balancing. However, the proposed step-up dc/dc converter enables the voltage self-balancing of the dc-link capacitor voltages.

-

3.

The soft switching principle can be implemented to all semiconductor devices of the dc/dc converter. A small stray inductance is inserted in series to form a resonant switching loop which can operate at high switching frequency.

-

4.

The first stage and the second stage of the proposed converter can be independently controlled. In the first stage, a constant duty ratio is implemented, and a simple carrier-based PWM scheme is used in the second stage. Therefore, the inverter can operate under a wide range of modulation indices and power factors.

3 Voltage Tripler Balancing DC/DC Converter

3.1 Operating Principle

Figure 2 shows the schematic of the step-up dc/dc converter. The converter has two separate cells, and each of them can be controlled individually. The converter takes input power from the PV modules, and the output voltage of the PV arrays is defined as Vpv which is shared between the two cells. The structure is identical, and the number of passive and active elements is the same. The two cells perform in a similar manner and all elements have the same current and voltage characteristics. Taking the upper cell as an example, the cell consists of two capacitors (C1, C2), four active switching devices (S1, S2, S3, and S4), and two current limiting stray inductances Ls1 and Ls2. Here, the stray inductances are employed to limit the charging current of capacitors C1 and C2, and it could be a wire or a PCB trace. The intermediate capacitor C1 and the output capacitor C2 are rated at Vpv. The overall output voltage of the converter is the voltage combination of the output capacitor of each cell in addition to the input voltage. Hence, three levels of output voltage can be generated, + 1Vdc, + 2Vdc, and + 3Vdc, respectively. Referring to Fig. 2, and in order to output the first level + 1Vdc, the power switching devices in the lower cell are active, whereas the switching devices in the upper cell are inactive. Therefore, the output voltage equals the voltage across capacitor C5; thus, + 1Vdc is generated, and the current i1 = Id. Similarly, in order to produce the second level, the capacitor C5 is connected in series with the capacitor C3, where the input voltage Vpv is inserted; therefore, the overall output voltage is a series combination of capacitor C5 and capacitor C3, and thus, the output voltage + 2Vdc is generated, and the current i2 = Id. Similarly, the third voltage level can be produced by activating the upper cell and inserting the output capacitor (VC2) in series with the capacitor VC3 and capacitor VC5; thus, the overall output voltage is + 3Vdc, and the current i3 = Id. The circuit analysis including soft switching, current, and voltage stresses is provided in the following section.

3.2 Self-Balancing Dc-Link Voltage

The converter consists of two cells as illustrated in Fig. 2, and these cells are identical, the following circuit analysis only considers the upper switching cell. Figure 3 illustrates the equivalent circuit of each switching state of the upper cell. The cell structure takes advantage of the basic principle of the switched capacitor circuit, where the capacitors and switching devices are the main circuit components. The soft switching operation can be easily implemented using the LC resonance switching loop; thus, zero current switching (ZCS) can be achieved for all switching devices. There are two switching states, and the equivalent circuit for the first switching state is shown in Fig. 3a, switches S1 and S2 are turned on, capacitor C1 is charged by the input voltage Vdc, and the inductor Ls1 resonates with the capacitor C1, and in the meantime switches S3 and S4 are turned off, the output capacitor C2 is discharged to the load.

The current profile of switches S1, S2 and voltage profile of capacitors C1, C2 are illustrated in Fig. 4. The switches S1 and S2 have a sinusoidal current wave shape, and both start and end with zero current, so the charging current is1(t) which flows through Ls1 can be represented by:

where A1 is the peak amplitude of charging current, and ω1 is the resonance frequency of the first switching sate, and it can be calculated from the following:

where C = C1 = C2, and LS = LS1 = LS2, at the condition that the current flow through S1 and S2 at the beginning and the ending of charging process is zero; therefore, the turn on time of the first switching state is given by

The equivalent circuit of the second switching state is illustrated in Fig. 3b, switches S3 and S4 are turned on and switches S1 and S2 are turned off. Figure 4 shows that indicator Ls2 resonates with the output capacitor C2, switches S3 and S4 are turning on and turning off at zero current; thus, ZCS is realized. The current is3(t) is the sum of charging current of capacitor C2 and the output current Id; hence, is3(t) and iC2(t) can be expressed as:

where A2 is the peak value of charging current of both is3(t) and iC2(t), and ω2 is the resonance frequency of the second switching sate, and it can be estimated from the following:

at the condition that the current is3(t) starts and ends with zero, from Eq. (4) the following result is obtained.

from Eq. (6), the turn on time of second switching state can be estimated from the following.

Since the sum of turn on switching time of both switching states equal the total switching cycle, therefore, from (3) and (7), the duty cycle of each switching state can be obtained as follows:

The maximum amplitude current A1 and value of angle φ in Eq. (4) can be calculated using the current second balance on capacitor C2; therefore,

Solving Eq. (9), the maximum amplitude A2 can be estimated as follows:

By substituting Eq. (10) into (5), and solving for φ, the following result is obtained.

Solving (11) numerically, the phase φ = − 9.58°, and from (10), the peak current A2 = 3.13 Id. From the obtained results, Eq. (4) can be rewritten as:

Based on results from (11), the duty ratio D1 and D2 in Eq. (8) becomes 0.56 and 0.44, respectively.

The current second balance can be applied on C1 in order to obtain the peak amplitude A1 of the first switching state in Eq. (1); thus,

Solving Eq. (13), the peak amplitude of A1 is estimated to be A1 = 2.8 Id. Based on the previous analysis, the current of intermediate capacitor C1 can be expressed as

Similarly, the current of the output capacitor C2 can be expressed as follows:

Using Eqs. (14) and (15), the voltage variation of intermediate capacitor C1, and output capacitor C2, can be balanced and estimated as follows:

3.3 Efficiency Analysis of the dc/dc Converter

The conduction losses are only considered since the switching losses are eliminated due to soft switching operation. The power devices and capacitors are characterized by their RMS and average current value. The power losses estimation is illustrated in Table 1, it shows that the conduction losses for switches S3, S4, S7, and S8 are high compared to other switches. And this is due to the higher RMS current carried by these switches during switching state 2 as illustrated in Fig. 4. Furthermore, the intermediate capacitors C1 and C2 experience more power losses than output capacitors C4 and C5, this is because capacitors C1 and C2 provide both charging and load current during the second switching state as presented in Fig. 3b.

4 DC/AC Single-Phase Seven-Level Inverter

4.1 Circuit Overview

Figure 5 depicts the single-phase seven-level dc/ac inverter. The inverter takes its input from the front stage where the step-up dc/dc converter is placed. Applying the proper modulation strategy, seven output voltage levels between node A and node B (VAB) can be generated, which are defined as + 3Vdc, + 2Vdc, + Vdc, 0, − Vdc, − 2Vdc, and − 3Vdc. The topology consists of two phase legs, eight switching devices, and the dc-link is a series connection of capacitors, C1, C2, and C3. The power switches (S1–S6) operate at the switching frequency, whereas switches S7 and S8 are switched at the fundamental frequency, 60 Hz. Therefore, the first leg is constructed with Si MOSFET devices, whereas the second leg is utilized with two Si IGBTs, leading to higher-voltage blocking capability, lower cost, and simpler circuit structure. The detailed operating principles are explained in the following section.

4.2 Operating Principle

The inverter has seven operating modes and eight switching states. The equivalent circuits of these switching states are depicted in Fig. 6a–h and listed in Table 2. The output voltage VAB can be generated by summing capacitors voltages VC1, VC2, and VC3 at the dc-link; thus, a seven-level stair-case waveform is obtained. The operating principle and the switching states for each mode are discussed in the following:

Mode 0 (VAB = 0 V): There are two switching states during this mode, the equivalent circuit during first switching states is illustrated in Fig. 6a, this state can be only used in the first half of the fundamental cycle when the output voltage VAB is switched between + Vdc and 0 and the output current id(t) flows in the positive direction. Switches S4, S6, and S8 are turned on and other switches are turned off. However, the second switching state is illustrated in Fig. 6b, and it is only employed in the negative half of the fundament cycle when the output current id(t) flows in the reverse direction and the output voltage VAB = 0 V. Switches S1, S3, and S7 are turned on and other switches are turned off. Thus, during “M0” the dc-link capacitors voltages are maintained constant and have no charging or discharging process.

Mode 1 (VAB = + Vdc): Fig. 6c illustrates the equivalent circuit. During this switching state, switches S4, S5, and S8 are turned on, and others are turned off, the load current id(t) flows in the positive direction, the capacitor C3 only provides energy to the load and the output voltage VAB = VC3 = Vdc.

Mode 2 (VAB = + 2Vdc): The equivalent circuit during this mode is depicted in Fig. 6d. Switches S2, S3, and S8 are turned on, the current flows in the positive direction. The generated output voltage VAB is the series connection of capacitor C3 and C2; thus, the output voltage can be expressed as VAB = VC3 + VC2 = + 2Vdc.

Mode 3 (VAB = + 3Vdc): The equivalent circuit during this switching state is shown in Fig. 6e. In this state, switches S1, S3, and S8 are turned on and the current id(t) flows in the positive direction. The three capacitors C1, C2, and C3 are connected in series and provide energy to the load. The output voltage is a combination of the three voltages, VC1, VC2, and VC3; thus, VAB = + 3Vdc.

Mode 4 (VAB = − Vdc): In this mode, the current id(t) flows in the reverse direction and the output voltage becomes negative. The equivalent circuit is shown in Fig. 6f. In this state, switches S2, S3, and S7 are turned on and capacitor C1 becomes the main energy provider to the load; thus, the output voltage VAB = − Vdc.

Mode 5 (VAB = − 2Vdc): In this mode, switches S4, S5, and S7 are turned on and the output current flows in the reverse direction. The equivalent circuit is shown in Fig. 6g. Capacitors C1 and C2 are connected in series and supported the load with the required energy. The output voltage VAB becomes VC1 + VC2; thus, VAB = − 2Vdc.

Mode 6 (VAB = − 3Vdc): The equivalent circuit in this mode is illustrated in Fig. 6g. The current flows in the reverse direction and switches S4, S6, and S7 are turned on. The output voltage is a series combination of three capacitors C1, C2, and C3; therefore, the voltage VAB becomes VC1 + VC2 + VC3, and thus, VAB = − 3Vdc.

4.3 Modulation Scheme

The multicarrier-based PWM technique is adopted to obtain the switching gate signals of the proposed seven-level inverter. Figure 7 illustrates six carriers, and one voltage reference waveform is employed to generate seven levels at the output in one fundamental cycle. Using Fig. 7 and Table 2, the switching between the seven-voltage levels is explained as follows:

-

Level + Vdc [0 ~ θ1 and π–θ1 ~ π]: In this level, the output current id(t) is positive and the output voltage VAB switches between + Vdc and 0. The inverter is switching between Mode “M0” and Mode “M1” as described in Table 2 with the equivalent circuit presented in Fig. 5a and c, respectively. During this level, the switching patterns occur mutually between switch S4 and switch S5, while other switches have no change in their status; thus, low switching loss can be achieved. Furthermore, the charging and discharging process during this level occurs for capacitor C3; therefore, the lower cell in front-end stage is only activated.

-

Level + 2Vdc [θ1–θ2 and π–θ2 ~ π–θ1]: The output voltage is switched between + Vdc and + 2Vdc; thus, the switching between Mode “M1”and Mode “M2” is employed during this level. The current id(t) is positive, and capacitors C1 and C2 are charged and discharged during this level. The lower cell in front-end stage is only active, switch S2 can be always on, so switching patterns only occur between switch S3 and switch S4.

-

Level + 3Vdc [θ2–θ3]: In this level, the output voltage is switched between + 2Vdc and + 3Vdc. All dc-link capacitors C1, C2, and C3 are charged and discharged during this level, both lower and upper cells in front-end stage are activated. The output current id(t) is positive and Mode “M2” and Mode “M3” are employed, switch S2 is always on, and the switching patterns occur between switch S1 and switch S3.

-

Level − Vdc [π–π + θ1 and 2π − θ1 − 2π]: The output voltage varies between 0 and − Vdc. Modes “M0” and “M4” are employed, and the equivalent circuit is shown in Fig. 6b and f. In this level, the output current is in the reverse direction and the charging and discharging process only occurs for capacitor C1; hence, upper cell in front-end stage is active, whereas lower cell is inactive. Switch S2 can be always on, and switching pattern only occurs between switch S1 and switch S3.

-

Level − 2Vdc [π + θ1 − π + θ2 and 2π − θ2 − 2π − θ1]: The output current id(t) is negative, and the voltage is switched between − Vdc and − 2Vdc. Modes “M4” and “M5” are used in this level, the switching occurs between switch S3 and switch S4, and charging and discharging process in this level only occurs for capacitor C1 and capacitor C2.

-

Level − 3Vdc [π + θ2 and 2π-θ2]: In this level, the output voltage varies between − 2Vdc and − 3Vdc and the current is in the reverse direction. Modes “M5” and “M6” are used and switching patterns occur between S5 and S6. All dc-link capacitors are involved in charging and discharging process.

4.4 Efficiency Analysis of 7L-dc/ac Inverter

For the 7L-inverter, there are two main types of power losses, conduction and switching losses. Conduction losses are a result of the load current, and switching losses result from dv/dt and di/dt, and the energy is consumed by the output capacitance of the switching device.

4.4.1 Switching Loss

The switching losses can be estimated directly from the energy transferred to the output parasitic capacitance Coss for each switching transition. Therefore, the switching loss during one switching cycle can be calculated from the following equation.

where Coss and Vb are the output parasitic capacitance and the block voltage of each switch, and fs is the switching frequency.

4.4.2 Conduction Losses

The conduction losses are mainly associated with the power devices. Referring to Fig. 7, the conduction losses for each switching device are estimated according to the worst-case scenario when the inverter operates at unity power factor. Therefore, if the inverter operates in first half of the fundament cycle when \( 0 \le \theta \le \pi\), the instantaneous duty ratio for each voltage level is calculated as follows:

However, when the inverter operates in the second half of the fundament cycle when \( \pi \le \theta \le 2\pi\), the instantaneous duty ratio for each voltage level becomes

where \(\theta_{1}\) and \(\theta_{2}\) can be estimated from the following.

where m is the modulation index. Using switching states in Table 2 and Eqs. (19) and (20), the RMS current of each power device can be obtained. Based on previous analysis, switches S1 and S6 have the same conduction time; therefore, the RMS current can be estimated as:

where \(\Upsilon = 9\cos \theta_{1} + 9\cos \theta_{2} - \cos 3\theta_{2} - \cos 3\theta_{1} - 8\), \(\beta = 2sin2\theta_{2} + sin2\theta_{1} - 2\theta_{1} - 4\theta_{2}\)

Similarly, switches S2 and S5 are conducting for the same period of time; hence, RMS current can be estimated from the following equation,

Furthermore, switches S3 and S4 will conduct for the same period and the RMS current can be calculated as follows:

Additionally, switches S7 and S8 operate mutually, and each conduct for one half of the fundamental cycle, the RMS current can be estimated as:

Table 3 shows the RMS current, conduction loss, and voltage stress of each power device for the 7L-inverter. Switches S1, S2, S5, and S6 have the lowest voltage blocking value with 1/3 Vdc; however, the switches S6 and S7 have the maximum reverse voltage blocking with Vdc.

4.5 Comparative Study

A comparative study of the proposed single-phase seven-level inverter and the existing topologies is conducted and presented in Table 4. Among different topologies, the switched capacitors-based multilevel inverters are selected. The number of switches, diodes, flying capacitors, and dc-link capacitors are the main parameters chosen for comparison. Compared to the presented topology in [33] and topology in [34], the proposed topology has fewer number of power switching devices, and lower total voltage stresses. The proposed topology and the topology in [35, 36] have the same number of power devices and dc-link capacitors. However, the voltage stress across switches in proposed topology is 14/3 Vdc, and for other topologies are 6Vdc and 16/3 Vdc; thus, the proposed topology has smaller value of total voltage stresses. The presented one in [37] has six switches and eight diodes, and the topology in [38] has seven switches and two diodes. Compared to the proposed topology, they show fewer number of active power devices but at the expense of adding passive diodes with higher total voltage stress across devices, 26/3 Vdc and 19/3 Vdc, respectively. The presented topology in [29, 39, 40] has a lower number of dc-link capacitors when compared to the proposed topology but needs more flying capacitors. The ones presented in [39, 40] have two flying capacitors and one dc-link capacitor; however, the presented topology in [29] uses one flying capacitor and two-dc-link capacitors. In general, the proposed topology shows a fewer number of switching devices, lower total voltage stresses when compared to similar topologies.

5 Simulation Results

The PSMI simulation model was built to confirm the operating principle of proposed topology for both the step-up dc/dc converter and the seven-level dc/ac inverter. Table 5 shows the circuit parameters used in the model, the PV input voltage Vpv is 100 V, the switching frequency is 100 kHz, and the fundamental frequency is 60 Hz. The LC parameters are selected according to Eqs. (3) and (7). The switching time Ts is constant for one switching cycle, and it is the sum of time T1 in Eq. (3) and time T2 in Eq. (7), and by selecting capacitance C = 3 uF, the resonance inductance Ls is calculated to be 1 uH.

5.1 Simulation Results of Voltage Tripler Converter

Figures 8 and 9 introduce simulation results of the step-up dc/dc converter. The boosting stage is designed to generate output three times the input voltage, the input voltage is 100 V and the output is 300 V. The stray inductance is 1 uH and all capacitors are similar and 3 uF. Figure 8 presents the load current id(t), and the input voltage VPV, the output dc-link voltage Vdc, the output voltage of the upper cell VC2, and the output voltage of lower cell VC5. Figure 8a illustrates the zoomed-in instantaneous load current id(t), and its peak value equals 6.6 A, and Fig. 8b shows the output of the PV arrays which equals VPV = 100 V. And Fig. 8c shows output voltage with average value equals 300 V and a voltage ripple is ΔV = 17 V. Figure 8d presents the output voltage of upper cell VC2 with average value of 100 V and the voltage variation is nearly 5 V which is consistent with the calculated result in Eq. (5); Fig. 8e shows the output voltage of lower cell VC5 equals 100 V and the voltage ripple is 12 V. Figure 9b demonstrates current flows of switches S1 and S3 in upper cell, and Fig. 9c illustrates the current flow of switches S5 and S7 in lower cell of the converter. The peak current occurs at the peak value of load id(t); therefore, according to the calculated value in Table 1, the maximum current of switches S1, S3, S5, and S7 is 18 A, 24 A, 8 A, and 10 A, respectively. Figure 9d and e shows voltages of the intermediate capacitor VC1 in upper cell and VC4 in the lower cell, both have the same average voltage which is 100 V, and the ripple voltage 20 V and 9 V, respectively.

5.2 Simulation Results of Seven-Level DC/AC Inverter

The performance of seven-level inverter is investigated under the same parameters illustrated in Table 3. Figures 10 and 11 demonstrate the performance under different working conditions. Figure 10 shows dc-link voltage (Vdc), seven-level output voltage VAB, and output current id(t). Modulation index “M” is chosen as 0.9, and dc-link voltage is balanced at 300 V and the maximum voltage ripple is 17 V, output voltage VAB clearly shows seven-level waveform with RMS voltage of 191 V. Figure 10 illustrates the inverter operating performance under different modulation indices. Dc-link voltage is constant at 300 V and the voltage ripple decreases as modulation index decreases. In Fig. 11, the modulation index varies between 0.9, 0.6, and 0.3; consequently, the output voltage waveform shows different output levels: seven-level, five-level, and three-level; hence, circuit performances under different modulation indices are verified.

The simulated results in Fig. 12a show that the proposed 7L-inverter has seven-voltage levels with low harmonics. The THD of the output voltage is low as 22%, and compared to traditional two-level inverter, the THD distortion is reduced by 34%. As shown in Fig. 12b, the THD is about 35% of five-level operation, and for three-level operation is 64% as presented in Fig. 12c. Thus, as the number of voltage levels increases, the THD is reduced, and the output power quality is improved.

Using system parameters listed in Table 5 and the power losses calculation in Tables 1 and 3, the efficiency curve for the two-stage 7L-inverter is obtained and presented in Fig. 13. From the curve, the input power ranges from 100 W to 1 kW; in the beginning, when low output power is required, the switching losses is dominant, and the conduction losses are quite low, the curve starts with low efficiency point. As the output power become higher, the efficiency starts increasing till it reaches the maximum point at 97.3%. And this is because the switching losses remain the same, and the conduction losses increase slightly. However, when the output power increases, the conduction losses become dominant and results in considerable decrease in the efficiency of the system.

6 Experimental Results

A 1-kW single-phase dc/ac converter was built and tested using parameters in Table 5. The input voltage is 100 V, the dc-link voltage is 300 V, and the step-up dc/dc converter and the dc/ac inverter operate at 100 kHz. The capacitors are chosen to be 3 uF and stray inductance Ls is measured as 1 uH. The experimental results of two stages are studied and presented as follows.

6.1 Experimental Results of Voltage Tripler Converter

Figures 14 and 15 show the experimental results of the step-up dc/dc converter. Figure 14 presents the output voltage of upper cell VC2, the output voltage of lower cell VC5, the dc-link voltage Vdc, and the voltage stress across switch S3, VS3. It is obvious that the output voltage is three times the input voltage, which is 300 V, and the voltage across the dc-link capacitors is balanced and settled at 100 V. Additionally, the voltage stress for all switches is the same and equals 100 V; from Fig. 14, the voltage across switch S3 in the upper cell is measured and equals 100 V. Figure 15 shows the gate signals and the current flow of switches S1 and S3. By employing the stray inductance of the charging loop, the soft switching operation is achieved. The figure shows that the current starts and ends with zero current; thus, zero current switching is realized for switches S1 and S3, and all switches can experience the same current profile and switch at zero current switching. Furthermore, the measured peak currents for switches S1 and S3 are 18 and 22 A, and this is consistent with the calculated values in Eq. (5), and due to similarities, other switches in the lower cell can see the same voltage and current profile.

6.2 Experimental Results of Seven-Level Inverter

The experimental result of the second stage of the seven-level dc/ac inverter is presented in this section. Figure 16 demonstrates the waveforms of dc-link voltage, output current, and capacitors voltage VC1 and VC2. Modulation index is set at 0.9, output filter is 1 mH, and load is R = 36 Ω. The figure shows the seven-level output voltage with RMS value of 190 V, and the RMS output current is 5 A. The capacitor voltages VC1 and VC2 are settled at 100 V each. Figure 17 illustrates the performance of the inverter under different modulation indices. The figure shows that as the modulation index changes from 0.9 to 0.6 and to 0.3, the number of the output voltage levels changes from seven to five and to three, respectively, and during these variations, the dc-link voltage is self-balanced and very stable. To further verify the effectiveness of the proposed topology, the inverter is tested at different power factor conditions. Figure 18 shows the performance when the load is set at 0.9 lagging power factor, and Fig. 19 shows the performance when the load is set at 0.9 leading power factor. The output voltage maintained its seven-level waveforms and the dc-link is self-balanced and stable. The presented experimental results prove the effectiveness of the proposed dc/ac inverter under different load conditions and wide range of modulation indices.

7 Conclusion

In this paper, a seven-level step-up dc/ac inverter is proposed. The main features include voltage boosting, self-balancing dc-link capacitors voltages, and smaller number of power switching devices when compared to similar multilevel inverters. Furthermore, the converter is built using switched capacitor circuit principle, and it can achieve soft switching operation; thus, the switching loss is reduced and the inrush current of the charging loop is minimized; moreover, the voltage stress across all switching devices equals the input voltage. The self-balance capability enables the inverter to employ a simple modulation scheme, and a complex control strategy was avoided. The working principle of the dc/dc stage and the dc/ac stage was analyzed under different modulation indices and different load conditions. A 1-kW prototype was built and tested for both stages. The soft switching operation in the dc/dc converter was experimentally verified, and the results show that the zero current switching was achieved at turning on and turning off switching devices, also the maximum charging current was regulated and matched to the calculated values. The seven-level output voltage waveforms were clearly illustrated and presented along with output current, and the voltage across the dc-link capacitors.

References

Gulzar, M.M.; Iqbal, A.; Sibtain, D.; Khalid, M.: An innovative converterless solar PV control strategy for a grid connected hybrid PV/wind/fuel-cell system coupled with battery energy storage. IEEE Access 11, 23245–23259 (2023)

Grigoletto, F.B.: Five-level transformerless inverter for single-phase solar photovoltaic applications. IEEE J. Emerg. Sel. Top. Power Electron. 8(4), 3411–3422 (2020)

Khan, M.N.H.; Forouzesh, M.; Siwakoti, Y.P.; Li, L.; Kerekes, T.; Blaabjerg, F.: Transformerless inverter topologies for single-phase photovoltaic systems: a comparative review. IEEE J. Emerg. Sel. Top. Power Electron. 8(1), 805–835 (2020)

Ali, J.S.; Sandeep, N.; Almakhles, D.; Yaragatti, U.R.: A five-level boosting inverter for PV application. IEEE J. Emerg. Sel. Top. Power Electron. 9(4), 1–10 (2021)

Priyadarshi, A.; Kar, P.K.; Karanki, S.B.: A single source transformer-less boost multilevel inverter topology with self-voltage balancing. IEEE Trans. Ind. Appl. 56(4), 3954–3965 (2020)

Sathik, M.J.; Sandeep, N.; Almakhles, D.J.; Yaragatti, U.R.: A five-level boosting inverter for PV applications. IEEE J. Emerg. Sel. Top. Power Electron. 9(4), 5016–5025 (2021)

Lee, S.S.; Bak, Y.; Kim, S.; Joseph, A.; Lee, K.: New family of boost switched-capacitor seven-level inverters (BSC7LI). IEEE Trans. Power Electron. 34, 10471–10479 (2019)

Amamra, S.A.; Meghriche, K.; Cheri, A.; Francois, B.: Multilevel inverter topology for renewable energy grid integration. IEEE Trans. Ind. Electron. 64(11), 8855–8866 (2017)

Vijeh, M.; Rezanejad, M.; Samadaei, E.; Bertilsson, K.: A general review of multilevel inverters based on main submodules: structural point of view. IEEE Trans. Power Electron. 34, 9479–9502 (2019)

Odeh, C.I.; Lewicki, A.; Morawiec, M.: A single-carrier-based pulse width modulation template for cascaded H-bridge multilevel inverters. IEEE Access 9, 42182–42191 (2021)

Yu, H.; Chen, B.; Yao, W.; Lu, Z.: Hybrid seven-level converter based on T-type converter and H-bridge cascaded under SPWM and SVM. IEEE Trans. Power Electron. 33(1), 689–702 (2018)

Taghvaie, A.; Haque, M.E.; Saha, S.; Mahmud, M.A.: A new step-up switched-capacitor voltage balancing converter for NPC multilevel inverter-based solar PV system. IEEE Access 8, 83940–83952 (2020)

Sathik, M.J.; Sandeep, N.; Blaabjerg, F.: High gain active neutral point clamped seven-level self-voltage balancing inverter. IEEE Trans. Circuits Syst. II, Exp. Briefs 67(11), 2567–2571 (2020)

Siwakoti, Y.; Mahajan, A.; Rogers, D.; Blaabjerg, F.: A novel seven-level active neutral point clamped converter with reduced active switching devices and DC-link voltage. IEEE Trans. Power Electron. 34, 10492–10508 (2019)

Zeng, J.; Lin, W.; Liu, J.: Switched-capacitor-based active-neutral-point-clamped seven-level inverter with natural balance and boost ability. IEEE Access 7, 126889–126896 (2019)

Lee, S.S.; Lim, C.S.; Siwakoti, Y.P.; Lee, K.-B.: Hybrid seven-level boost active-neutral-point-clamped (H-7L-BANPC) inverter. IEEE Trans. Circuits Syst. II Express Briefs 67(10), 2044–2048 (2020)

Karasani, R.R.; Borghate, V.B.; Meshram, P.M.; Suryawanshi, H.M.; Sabyasachi, S.: A three-phase hybrid cascaded modular multilevel inverter for renewable energy environment. IEEE Trans. Power Electron. 32(2), 1070–1087 (2017)

Lee, S.S.; Lee, K.: Dual-T-type seven-level boost active-neutral-point-clamped inverter. IEEE Trans. Power Electron. 34, 6031–6035 (2019)

Samadaei, E.; Sheikholeslami, A.; Gholamian, S.A.; Adabi, J.: A square T-type (ST-type) module for asymmetrical multilevel inverters. IEEE Trans. Power Electron. 33(2), 987–996 (2018)

Davis, T.T.; Dey, A.: Investigation on extending the DC bus utilization of a single-source five-level inverter with single capacitor-fed H-bridge per phase. IEEE Trans. Power Electron. 34(3), 2914–2922 (2019)

Niu, D.; Gao, F.; Wang, P.; Zhou, K.; Qin, F.; Ma, Z.: A nine-level T-type packed U-cell inverter. IEEE Trans. Power Electron. 35(2), 1171–1175 (2020)

Siddique, M.D.; Saad, M.; Shah, N.M.; Ali, J.S.M.; Meeraj, M.; Iqbal, A.; Al-Hitmi, M.A.: A new single phase single switched-capacitor based nine-level boost inverter topology with reduced switch count and voltage stress. IEEE Access 7, 174178–174188 (2019)

Sathik, M.J.; Bhatnagar, K.; Sandeep, N.; Blaabjerg, F.: An improved seven-level PUC inverter topology with voltage boosting. IEEE Trans. Circuits Syst. II Express Briefs 67(1), 127–131 (2020)

Roy, T.; Sadhu, P.K.: A step-up multilevel inverter topology using novel switched capacitor converters with reduced components. IEEE Trans. Ind. Electron. 68(1), 236–247 (2021)

Saeedian, M.; Adabi, M.E.; Hosseini, S.M.; Adabi, J.; Pouresmaeil, E.: A novel Step-up single source multilevel inverter: topology, operating principle, and modulation. IEEE Trans. Power Electron. 34(4), 3269–3282 (2019)

Bahrami, A.; Narimani, M.: A new five-level T-type nested neutral point clamped (T-NNPC) converter. IEEE Trans. Power Electron. 34(11), 1053410545 (2019)

Zeng, J.; Wu, J.; Liu, J.; Guo, H.: A quasi-resonant switched-capacitor multilevel inverter with self-voltage balancing for single-phase high-frequency AC microgrids. IEEE Trans. Power Electron. 13(5), 2669–2679 (2017)

Sun, X.; Wang, B.; Zhou, Y.; Wang, W.; Du, H.; Lu, Z.: A single DC source cascaded seven-level inverter integrating switched-capacitor techniques. IEEE Trans. Ind. Electron. 63(11), 7184–7194 (2016)

Liu, J.; Zhu, X.; Zeng, J.: A seven-level inverter with self-balancing and low-voltage stress. IEEE J. Emerg. Sel. Top. Power Electron. 8(1), 685–696 (2020)

Topal, H.; Taner, T.; Naqvi, S.A.; Altınsoy, Y.; Amirabedin, E.; Ozkaymak, M.: Exergy analysis of a circulating fluidized bed power plant co-firing with olive pits: a case study of power plant in Turkey. Energy 140, 40–46 (2017). https://doi.org/10.1016/j.energy.2017.08.042

Taner, T.; Naqvi, S.A.; Ozkaymak, M.: Techno-economic analysis of a more efficient hydrogen generation system prototype: a case study of PEM electrolyzer with Cr-C coated SS304 bipolar plates. Fuel Cells (2019). https://doi.org/10.1002/fuce.201700225

Taner, T.; Sivrioglu, M.: A techno-economic and cost analysis of a turbine power plant: a case study for sugar plant. Renew. Sustain. Energy Rev. 78, 722–730 (2017). https://doi.org/10.1016/j.rser.2017.04.104

Najafi, E.; Yatim, A.H.M.: Design and implementation of a new multilevel inverter topology. IEEE Trans. Ind. Electron. 59(11), 4148–4154 (2012)

Li, X.; Dusmez, S.; Prasanna, U.R.; Akin, B.; Rajashekara, K.: A new SVPWM modulated input switched multilevel converter for grid-connected PV energy generation systems. IEEE J. Emerg. Sel. Top. Power Electron. 2(4), 920–930 (2014)

Khan, S.A.; Guo, Y.; Habib Khan, M.N. Siwakoti, Y.; Zhu, J.: Model predictive control without weighting factors for T-type multilevel inverters with magnetic-link and series stacked AC–DC modules. In: 2019 IEEE Energy Conversion Congress and Exposition (ECCE), pp. 5603–5609 (2019)

Chen, J.; Liu, D.; Ding, K.; Wang, C.; Chen, Z.: A single-phase double T-type seven-level inverter. In: 2018 IEEE Energy Conversion Congress and Exposition (ECCE), pp. 6344–6349 (2018)

Wu, F.; Duan, J.; Feng, F.: Modified single-carrier multilevel sinusoidal pulse width modulation for asymmetrical insulated gate bipolar transistor-clamped grid-connected inverter. IET Power Electron. 8(8), 1531–1541 (2015)

Choi, J.; Kang, F.: Seven-level PWM inverter employing series-connected capacitors paralleled to a single DC voltage source. IEEE Trans. Ind. Electron. 62(6), 3448–3459 (2015)

Chen, J.; Wang, C.; Li, J.: A single-phase step-up seven-level inverter with a simple implementation method for level-shifted modulation schemes. IEEE Access 7, 146552–146565 (2019)

Hinago, Y.; Koizumi, H.: A switched-capacitor inverter using series/parallel conversion with inductive load. IEEE Trans. Ind. Electron. 59(2), 878–887 (2012)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Alsolami, M. Single-Phase, Seven-Level Inverter with Triple Voltage Boosting and Self DC-Link Voltage Balancing. Arab J Sci Eng 49, 6815–6830 (2024). https://doi.org/10.1007/s13369-023-08523-z

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s13369-023-08523-z