Abstract

This work explores anti-serial (anti-parallel) memristive switches—ASMs (APMs)—as potential cross-point elements in nano-crossbar resistive random access memory arrays. The memory operation principles for both device combinations are shown in detail. The effectiveness of these memristive structures to the solution of the parasitic conducting (current sneak paths) problem is presented via an analytical approach which is based on the basic setup of resistive crossbar memories. Simulation results of crossbars of up to 4,096 elements, arranged in quadratic configurations, are conducted. The provided results supplement this comprehensive analysis of APMs and ASMs, outlining their overall performance characteristics and commenting on their applicability to the practical realization of large crossbar memory systems. Finally, a special array topology is applied to an ASM-based crossbar memory. Its performance is compared to the performance of the pure ASM-based memory. The conducted simulations reveal significantly improved read-out voltage margins which further contribute to addressing the parasitic current paths which prevent the reliable operation of memristive crossbar circuit topologies.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Many emerging memory technologies, like phase change memory (PCM) [1] and resistive random access memory (ReRAM) [2, 3], are nowadays being investigated as promising candidates to overcome the scaling limits of the charge-based flash memory. As far as ReRAM is concerned, this type of storage devices is based on two-terminal resistance switching elements called memory resistors (memristors). The memristor is a nonlinear device that exhibits a “pinched” hysteresis loop between current and voltage (I–V), satisfying the Ohm’s law with a nonconstant resistance [4]. The existence of the memristor as the fourth fundamental circuit element was predicted by Leon Chua in 1971 via an axiomatic approach based on symmetry and on a missing relationship between the four fundamental circuit variables, namely, current, voltage, charge, and flux linkage [5].

Although it has been almost 6 years since the experimental realization of the first “modern” memristor prototype by Strukov et al. at Hewlett Packard Laboratories [6], many details of the internal memristive mechanisms of the reported materials are still unknown [7]. Nevertheless, recent experimental demonstrations are very encouraging for the potential utilisation of memristors in a variety of emerging applications [8–11]. Among others, such applications mostly include non-volatile memories [12], large scale associative and content-addressable memories [13, 14], as well as new configuration memory cells for FPGAs in embedded applications [15, 16]. Specifically, ReRAM storage elements, i.e. memristors, with scalability down to sub-10 nm, comparable read/write times with present day memories and good retention time projected to >10 years [17], prove up to now to be the most promising solution for future storage systems. Nevertheless, when ReRAMs are implemented in the nano-crossbar geometry [18], parasitic conducting (current sneak paths) disturbs reading operations and makes the use of large sensing circuits inevitable. Sneak paths are an inherent disadvantage of passive crossbar arrays and significantly limit the size of the grid, i.e. the maximum achieved number of rows and columns [19]. Some of the proposed solutions to this problem include additional nonlinear elements in series with the memristors. Actually, introducing diodes to each cross-point structure appears as one of the most attractive candidates [20], but diodes with sufficiently high forward current density and stable unipolar memristive elements are still under investigation. Moreover, adding diodes to the array will increase the delay of the system by adding capacitive loads, and diode threshold voltages will decrease the output swing [21]. A programming scheme was developed in [22] where parallel current paths were blocked using external diodes at the outside of the array and asymmetric protecting voltages which were applied to the unselected word and bitlines. However, intrinsic current-rectifying characteristic of the cross-point resistance switching elements plays a crucial role in making this approach feasible. Also, using CMOS transistors for gating the memristors will certainly solve the sneak paths problem. On the other hand, this method will ruin the high density of memristive memory, since the size of the CMOS switches is much larger than that of a memristor [23]. Moreover, a cross-point cell structure consisting of one bipolar selector, with nonlinear resistance, and one memristor shows to be able to best utilize the stable bipolar memristive properties while the read process remains non-destructive [24]. However, the reported bipolar selectors so far have limited nonlinearity, only sufficient for small array sizes, and significant improvements on the selector characteristics are needed for high-density crossbar arrays.

Recently, anti-serial memristive switches (ASMs) were proposed as cross-point devices to address interfering current paths between neighbouring memory cells, where each ASM device consists of two memristors connected in series with opposing polarities [25]. However, anti-parallel memristive switches (APMs) have been also fabricated and characterized [26], where each APM comprises two memristors with opposing polarities connected in parallel. Therefore, it was proved that anti-parallel-connected memristors can be effectively combined, and hence, they could be potentially used in memory applications as well. The resulting I–V characteristics of both the aforementioned device combinations strongly depend on the parameters of the individual switches. However, their unique feature which appears in simulation and in fabrication testing as well is their symmetric I–V curve made out of asymmetric I–V curves of single memristors.

In the present work, we discuss the notion of introducing APMs or ASMs as potential cross-point elements in nano-crossbar memory arrays. We present the corresponding memory operation principles for both device combinations according to the switching characteristics that the individual memristive elements may have. Moreover, we compare the effectiveness of these memristive structures to the addressing of the current sneak path problem via an analytical approach which is based on the basic setup of a resistive crossbar memory. Using a memristor device model, developed by the present authors [27], we also include simulation results of crossbar memory arrays with up to 4,096 elements. We provide a comprehensive and comparative presentation between APMs and ASMs, commenting on their overall performance and the most appropriate switching characteristics that the structuring memristors should have in order for their parallel or serial combinations to better fit to memory applications. Finally, we employ a special crossbar topology pattern [28], which introduces insulating junctions inside the grid, and evaluate its impact on the memory read-out voltage margins of ASM-based memories. The presented mathematical analysis, supported with the provided simulation results, constitutes a useful tool for electronic engineers and circuit designers from academia and industry who wish to experiment with such memristive structures in emerging memory applications.

2 Memristor Modelling and Memory Cell Operation Principles

In this section, we analyze the composite behaviour of circuits comprising memristors connected in a serial or a parallel manner; we provide the operation principles for both types of memristive switches when they are used as cross-point storage structures in crossbar memory arrays. Depending on their internal state, their polarity, and the device-specific properties, which are represented by the values of the parameters of the employed model, the simulation results reveal that such compositions of memristors respond in a much unexpected manner. Such response is particularly exploited when memristors are used as memory cells.

In this work, all simulations are conducted using the MATLAB® environment employing a memristor device model which explains memristive behaviour by investigating the occurrence of quantum tunnelling as the primary electronic transport mechanism [27]. More specifically, it is a threshold-type switching model of a two-terminal voltage-controlled electronic device that exhibits memristive behaviour, whose general definition is given by the following equations:

We define as L the tunnel barrier width and also the single state variable of the system, indicating the internal memristor state. G is the conductance of the device and parameters I and V M represent current and applied voltage, respectively. We define as R_t the tunnelling resistance (memristance) of the device for a certain restricted range of the state variable L. We calculate it using the following equation:

where f 0 is a model fitting parameter. The resistance of such devices as a function of L illustrates an exponential behaviour. Moreover, we developed a heuristic equation which qualitatively gives the response of the tunnel barrier width as a function of the applied voltage. Its mathematical formula follows:

where L 0 is the maximum value that L(V M, t) can attain and m is a fitting parameter that determines the boundaries of the barrier width. By considering tunnelling as the dominant physical mechanism, Eq. (4) introduces the initial as well as the current position of the tunnelling barrier which is limited within two boundary values. This model is based on the assumption that the switching rate of L is small below (fast above) a threshold voltage (V SET or V RESET), which is viewed as the minimum voltage required to impose a change on the physical structure of the device. This assumption is encapsulated in the use of the voltage-dependent function r(V M, t) whose time derivative, given by the following expression, is slow or fast depending on the applied voltage.

Several thresholds can be programmed by tuning the shaping parameters of r(V M, t), namely, a, b, and c. Equation (5) incorporates sigmoid functions in the regions above the voltage thresholds, whereas a linear relation of the applied voltage is used for the region below the thresholds. Parameters a, b, and c are fitting constants that are used to shape the intensity of the state variable dynamics, i.e. the rate of memristance change, with a > > b and 0 < c < 1. Setting b equal to zero imposes a hard switching behaviour, i.e. there is no state change in the memristor unless a certain voltage threshold is exceeded. Consequently, parameter r(V M, t) defines both the device dynamics and the corresponding state. Its value is monitored at each time step and maintained within a valid defined range; i.e. in cases when r < r min or r > r max, it is set equal to r min or r max, respectively. As a consequence, the device memristance is correspondingly set to R ON or R OFF.

Figure 1 illustrates the response of a single memristor under ac voltage bias according to the used model. Model parameter values are used as given in {α, b, c, m, f o, L o, V RESET, V SET} = {3 × 104, 5, 0.1, 83, 180, 8, −1 V, 2 V}, and the resulting resistance ratio is set to R OFF/R ON ≈ 103 with R OFF ≈ 2 MΩ and R ON ≈ 2 ΚΩ. We note here that, according to the mathematical formulation of the model, when {a, b} > 0, then a positive (negative) voltage applied to the top terminal with respect to the bottom terminal, denoted by the black thick line (see inset of Fig. 1 for the corresponding schematic), always tends to decrease (increase) the memristance. In this context, hereinafter we will refer to forward (reversely) polarized memristors as FPMs (RPMs). Single memristors with opposite polarities present a flipped I–V characteristic and generally demonstrate reversed behaviour to the applied signals; in brief, a positive applied voltage tends to SET (RESET) an FPM (RPM) device from OFF to ON (from ON to OFF). Therefore, during a single period of an applied ac voltage, the complementary devices will be likely changing their states in a reciprocal way. The characteristics demonstrated in Fig. 1 will serve as a reference when studying the composite behaviour of APMs and ASMs throughout this paper, under similar applied voltages of the same frequency. Whenever different values are applied to the parameters of the model, it will be clearly stated.

Simulation results from the response of the memristor model [27] to a triangular ac applied voltage, showed in the upper-left graph. The hysteretic current–voltage (I–V) characteristic of a device with (V RESET, V SET) = (−1, 2 V) is demonstrated in the upper-right graph, and the corresponding change of the resistance (memristance) with time and with the applied voltage is shown in the graphs which are placed below

2.1 Anti-Serial Memristive Switch (ASM)

In the anti-serial memristive switch (ASM) concept, a memory cell is formed by two memristors vertically stacked in an anti-serial manner on top of each other. In an individual memristor, logic values ‘0’ and ‘1’ can be represented with high (OFF) and low (ON) resistance states, respectively. However, the unique aspect of ASMs is in using a combination of low and high resistances to represent the aforementioned binary values; i.e. using the following notation to denote the placement of the devices as UPPER/LOWER, then an ON/OFF combination could represent logic ‘1’ and the opposite one, namely, OFF/ON, could respectively represent logic ‘0’. Since the memristance change behaviour is dependent on the initial state of the devices, their initial memristances should be set to either of the aforementioned boundary value combinations directly after manufacturing by appropriate biasing, prior to further processing.

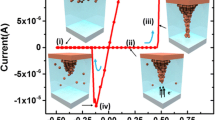

In the simulation results presented in Fig. 2, an ASM is subjected to a triangular ac voltage sweep of appropriate magnitude (here 5 V) to make sure that the corresponding voltage drop will cause both memristors to change their state. Three different cases are examined, considering switching threshold voltages for both memristive elements set to the following values: (a) V RESET = −1 V with V SET = 2 V, (b) |V RESET| = |V SET| = 2 V, and (c) V RESET = −2 V with V SET = 1 V. In particular, first a positive voltage is applied, thus creating the necessary conditions to either change the state of the RPM (i.e. the lower placed device) from ON to OFF or to change the state of the FPM from OFF to ON. As it can be seen in the corresponding graphs, when voltage reaches a particular point, then the state of the FPM changes first and the current rises to very high values until the RPM finally switches to the OFF state. At this point, the initial state configuration FPM/RPM = OFF/ON of this complementary switch has been flipped to ON/OFF. Next, the circuit exhibits an ohmic behaviour until the voltage reaches a specific negative value, when the RPM first changes to the ON state. As the negative voltage sweep continues, the FPM is also flipped and the circuit continues exhibiting ohmic behaviour again until the end of the voltage sweep. An important observation regarding the resulting I–V characteristic of the anti-serially connected memristors is that the current is linear with the applied voltage, except in two finite voltage intervals where it remains linear but with different gradient due to the much higher observed conductance.

Simulation results for the current–voltage (I–V) characteristics of anti-serial and anti-parallel memristive switches under a single triangular voltage sweep of appropriate amplitude and the same frequency as in Fig. 1. The switches are initialized to the given state configurations. Three different cases are examined regarding the threshold voltages of the individual elements, namely, |V RESET| > |V SET| with V RESET = −2 V and V SET = 1 V, |V RESET| = |V SET| with V RESET = −2 V and V SET = 2 V, and |V RESET| < |V SET| with V RESET = −1 V and V SET = 2 V, respectively

In such memristive element configurations, the switching voltages cannot be formerly known exactly. The connected devices form a voltage divider circuit; therefore, the voltage drop over each element depends on the total external applied voltage, on the internal states of the devices and on their particular switching characteristics. In order to utilize an ASM as a memory cell, starting from its corresponding I–V graph of Fig. 2, appropriate programming voltages and reading voltages need to be selected. The first must exceed the voltage limits where the state transitions are completed, whereas the latter must be selected within the specific region where presence of high (low) current will determine reading an OFF/ON (ON/OFF) binary state. Here, we choose to programme the device using ±5 V pulses, whereas reading their state could be done by applying pulses whose amplitude falls within the voltage window specified by the limits of the observed high conduction lobes. However, as shown in Fig. 2, the width of these reading windows depends on the threshold voltage values of the individual memristors. The cases where |V RESET| > |V SET| or |V RESET| = |V SET| are definitely preferable because the high conduction intervals are better defined, compared to the case of having |V RESET| < |V SET|. Proper selection of the devices will be useful in order to overcome inevitable process, voltage, and temperature (PVT) variations between different individual devices. Nevertheless, in all conducted simulations here we consider individual memristive elements with identical switching characteristics (i.e. threshold voltages, memristance value limits, model parameters). Starting with the ASM preprogrammed at the state OFF/ON, if we apply a read pulse, then the measured current will result high. This happens because when reading this specific logic state, the internal state of the ASM changes to the intermediate state ON/ON, which is why this has been identified in the literature as a destructive read-out operation [29]. Therefore, after reading the OFF/ON state, it is necessary to restore the ASM immediately afterwards by rewriting it; thus, we should apply a negative write pulse (here −5 V). Whenever this procedure is repeated, the less resistive combination occurs, i.e. the ON/ON state; hence, there is always an instant current peak which is characteristic of this transition. Finally, if we wish to change the state of the ASM from OFF/ON to ON/OFF, we have to apply a positive programming pulse (here +5 V). Then, a reading pulse will identify the cell’s state with the measured current being low this time, given that no change is induced to the state of the cell during read-out.

2.2 Anti-Parallel Memristive Switch (APM)

Considering again a single memristive device as a structural element, we analyze the behaviour of two connected memristors with opposing polarities, this time in parallel, forming an APM. In the rest of the paper, whenever necessary, we will use operator ‘||’ to denote two memristors connected in parallel. Likewise in the ASM case, a combination of low and high resistances is used for the representation of the stored digital values. More specifically, the combination (FPM, RPM) = (OFF, ON) could denote logic ‘1’, whereas the opposite combination could denote logic ‘0’. The initial memristances of individual memristors should be set to either of the aforementioned boundary value combinations after manufacturing, prior to further processing. In the APM case, since the same voltage is simultaneously applied to both memristors, we do not notice any induced shift in the switching threshold voltages that dominate the composite behaviour of APM structures, compared to the response of the individual structuring elements. However, unlike the series connection, in the parallel connection, the lower resistance values (R ON) will dominate the total resistance of each APM.

In Fig. 2, the simulation results of a pair of anti-parallel memristors are shown. Compared to the previously described case, we now notice a major difference in the overall composite memristance switching; the memristance is kept at low values except for two certain intervals. This is because, as we have concluded before, devices with opposite polarities have opposite switching characteristics; each time a voltage is applied, one of the devices tends to switch to the OFF state and the other to the ON state, respectively. Hence, there will almost always be a device at the ON state, dominating this way the total memristance. The resulting I–V characteristic looks like a truncated Ohm’s law; the current is linear with the voltage exclusive of two finite intervals, where both devices are found at the OFF state. The (FPM, RPM) = (OFF, OFF) state combination is found only as an intermediate state during the state transitions of the circuit components, likewise happened with the ON/ON combination in ASMs. This behaviour is opposite to the I–V characteristic of the in-series complementary configuration of memristors forming ASMs. Of course, proper selection of devices which demonstrate appropriate threshold voltages (or carefully engineering the desired threshold values [30]) will correspondingly affect the period of duration of the OFF/OFF combination. Nevertheless, according to Fig. 2, the case where |V RESET| < |V SET| seems to be the only viable option in APMs which guarantees the expected operation. When |V RESET| = |V SET|, we again notice a short period of very low conduction, even though practically, no such conducting state is expected since both memristors switch simultaneously, and hence, the equivalent resistance of the APM remains the same (R OFF||R ON = R ON||R OFF). On the other hand, different switching rates for SET (OFF to ON) and RESET (ON to OFF) operations could be attributed to the interaction of the external applied field, the internal field of the concentrated defects (e.g. charge traps, mobile ions, oxygen vacancies in metal-oxide material stack configurations, etc.), and the diffusion, all acting in the same or in opposite directions according to the applied voltage bias [4], [6]. In our model, the RESET process is completed faster than the SET counterpart, which is where the aforementioned short low conduction periods are derived from. Nonetheless, given that such differences in the switching rates are device-dependent, |V RESET| = |V SET| is not considered an appropriate option in order to form well-defined APMs.

Furthermore, if the threshold voltages of individual memristors belong to the case where |V RESET| > |V SET|, then the APM operation is completely ruined. Indeed, it is quite intriguing to notice that two memristors with |V RESET| > |V SET|, when connected in an anti-parallel configuration forming an APM, actually behave like an ASM. This particular choice, however, compared to really anti-serially connected memristors, although it is obviously well defined, with the composite threshold voltages being equal to those of the individual structuring memristors, it delivers a much smaller ratio between the two distinct conducting states and thus will be less useful when used as storage element in large crossbar memory arrays, whose basic operation we describe later in this work.

2.3 Pulse Properties of ASMs and APMs

Figure 3 presents the simulation results of a pulse driven memory cell when comprising either an ASM (a, b) or an APM (c, d) switch. As described previously, single memristors with opposite polarities generally demonstrate reversed behaviour to the applied signals; therefore, for any applied voltage, the complementary devices will be changing their states in a reciprocal way. Starting with the ASM preprogrammed as FPM/RPM = OFF/ON, a positive read pulse will result in high measured current because the internal state of the ASM changes to the intermediate state ON/ON; i.e. the FPM changes its state first as a result of the voltage divider between the FPM and the RPM. High measured current is always indicative of the transition to the less resistive combination (i.e. ON/ON). Afterwards, both memristors remain unaffected since the corresponding voltage drop on each of them does not surpass the voltage thresholds. On the contrary, in APMs, the (FPM, RPM) = (OFF, OFF) state combination is the intermediate state during the state transitions of the circuit components; their behaviour is opposite to that of ASMs (the device initially found in the less resistive state changes first to the high resistive state).

Pulse properties of anti-serial (yellow background) and anti-parallel (light blue background) memristive switches. The voltage pulses applied to an ASM and an APM cell are shown in (a) and (c), whereas the resulting currents are shown below in (b) and (d), respectively. After the first two read pulses, as the stored information is destroyed, a write back of the initial state is performed right afterwards. The induced change to the composite resistance by the read and write pulses when applied to ASMs and APMs is shown in (e) and (f), respectively

In our case, first, a read pulse is applied to check the state of the memristive switch. In general, such a read pulse must be of appropriate amplitude and duration so as to switch the ASM (APM) to the intermediate ON/ON (OFF/OFF) state, as discussed previously. In our simulations, we assume the most convenient threshold voltage conditions for each device combination, i.e. |V RESET| > |V SET| with V RESET = −2 V and V SET = 1 V for ASMs and |V RESET| < |V SET| with V RESET = −1 V and V SET = 2 V for APMs, respectively. Therefore, based on the particular I–V characteristics of Fig. 2, we choose to apply read pulses of 3 V and 2 V to ASMs and APMs, correspondingly, so as to approximate the centre of the reading voltage windows and hence to ensure a secure reading operation. As shown in Fig. 3e, f, the resistance switching for both ASMs and APMs is completed within less than 7 ms. However, here the duration of the applied pulses is chosen to be 10 ms so as to facilitate better distinction between the reading currents in the corresponding graphs demonstrated in Fig. 3b,d. As high (low) current is detected, the ASM (APM) is initially found in the FPM/RPM = OFF/ON state. In the next step, a negative write pulse is applied which restores the initial state of the devices. We note here that the amplitude of the write pulses was selected to be ±5 and ±3 V for ASMs and APMs, respectively. Their duration was set to the minimum value which guarantees a complete transition of the composite memristance, as shown in Fig. 3e, f; in specific, it is 12 ms for ASMs and 7 ms for APMs. Then the same procedure is repeated, i.e. a read pulse is applied which results in the same current measurements, and next, a negative write pulse restores the “destroyed” state of the storage elements. As during the read process, one of the memristors changes from OFF to ON (ON to OFF) in the ASM (APM), the stored information is destroyed and needs to be rewritten. Next, a positive write pulse is applied which sets the switches to the FPM/RPM = ON/OFF state. The following read pulse results in measurable current for the APM and in almost non-detectable current in the ASM, which are indicative of reading the FPM/RPM = ON/OFF state. At this point, it is worth mentioning that all assumptions regarding both threshold and programming voltage values have been made only in the context of this study of ASMs and APMs as memory cells in crossbar arrays; thus, they do not relate to any real, manufactured or measured devices. Nevertheless, current experimental device characteristics [31] demonstrate that memristors and crossbar arrays can be integrated with existing advanced, nanometric CMOS technologies with a nominal voltage of around 1 V.

3 Memristor-Based Passive Crossbar Memories

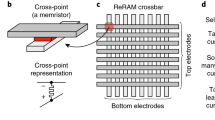

The crossbar structure possesses many attractive features as it offers the highest possible device density and the simplest interconnect configuration that still allows external access to each nano-device. In this work, we study a nano-crossbar memory system that uses compositions of anti-parallel (APM) or anti-serial (ASM) memristors as memory elements. Such system does not utilize the kind of devices (diodes or transistors) that are normally used to isolate the cell being written to and read from in conventional memories.

The simplest circuit approach for reading information from the memristor-based crossbar, whether it is based on single memristors, APMs or ASMs, is by applying a certain read voltage across a junction and transforming the current flow into a voltage. The basic setup of a nano/CMOS crossbar memory system is shown in Fig. 4. Column and row decoders drive the necessary selection switches in order to form a voltage divider circuit with the corresponding pull-up resistor and the resistance of the accessed node. Typically, the pull-up resistors are implemented in a CMOS layer or in a form of nanowire resistors. The output of the voltage divider is then driven to a CMOS sense amplifier, and the state of the device is distinguished by comparing this voltage to a reference value. The voltage swing at the output of the crossbar read circuit, between reading distinct binary stored data in form of different impedance states, should be large enough for the two states to be easily distinguishable.

Basic setup of a passive nano/CMOS crossbar memory system. Column and row decoders drive the corresponding selection devices and the voltage drop on the accessed element is then sensed and compared to a reference value by appropriate CMOS sensing circuits. In our work, the cross-point storage elements can consist of anti-serial or anti-parallel configurations of memristors

In the rest of this section, we first summarize the fundamentals of passive crossbar memories comprising single memristors as cross-point storage cells and later, extend our analysis to include the cases of ASMs and APMs. The general equivalent circuit of a read operation in a passive crossbar, regardless of the cross-point cell type, is given in Fig. 5a. In the ideal reading case, where no current sneak paths are present, the equivalent circuit for the read operation is a simple voltage divider formed by a pull-up resistor R PU and the accessed element (Fig. 5b). Considering a single memristor at each cross-point, then for a given β = R OFF/R ON ratio, the achieved voltage swing ΔV for a certain applied pull-up voltage V PU is calculated as follows:

a Read operation equivalent circuits in passive crossbar where all non-accessed cells are set to the same resistive state R sneak. b The ideal reading case with the accessed device forming a simple voltage divider with the pull-up resistor. c The more realistic case with the inevitable parasitic resistance

This normalized detection margin of the two possible states of a memory cell is maximized if the pull-up resistor R PU is optimally chosen to be the geometric mean of the two bistable resistances of the memristors. However, for large R OFF/R ON ratios, the optimal R PU is close to the less resistive state, i.e. R ON. Unfortunately in a real reading operation, with parasitic current paths in parallel to the accessed memristor, the effective R OFF/R ON ratio results substantially smaller (Fig. 5c). The impact of parasitic sneak paths definitely depends on the way the crossbar is accessed. Here, a crossbar-setup with m wordlines and n bitlines is assumed, where the resistance of the selection transistors and interconnects is neglected. Among different approaches of accessing the crossbar, one is to select one wordline, pull up one bitline and leave the other bitlines floating, whereas another way is to select one wordline and pull up all bitlines simultaneously. In this study, the first approach is used, and thus, the reading operation assumes accessing one bit at a time. The worst-case scenario for reading the crossbar is the following: when reading a memristor found in the OFF state and the parasitic resistance is as small as possible, the crossbar output voltage notably degrades. This is the case where all non-accessed memristors are set to ON, i.e. R sneak = R ON (see Fig. 5). One could similarly consider the corresponding worst-case scenario when reading a memristor found in the ON state to assume that all non-accessed nodes are set to the OFF state (i.e. R sneak = R OFF), thus resulting in smaller measured current, although the impact is less severe to the reading output in this case. The parasitic worst-case resistance for an n × m-crossbar can be computed using the equivalent circuit shown in Fig. 5c. This resistance is connected in parallel with the accessed memristor, and as a result, the maximum achievable read voltage margin gets significantly smaller with increasing crossbar size, as well as it strongly depends on the distribution of the stored information in the array [32, 33].

In the case of having ASMs as cross-point devices, the equivalent circuit of a real read operation is the same, only that now the composite resistance at each node is equal to the sum of the FPM and the RPM resistance values, i.e. R OFF + R ON, regardless of the specific stored data. Considering a high enough resistance ratio β > > 1, then the composite resistance at each node is approximately equal to R OFF. As a consequence, it is also R sneak = R OFF. Therefore, based on Fig. 5c and assuming a quadratic crossbar grid with m = n, without loss of generality and in order to simplify our calculations, the parasitic resistance connected in parallel with the accessed ASM is calculated as follows:

Parameter λ in Eq. (7) only depends on the crossbar size of the quadratic array m and its approximate value for the sizes of interest in this paper, namely, for m = n = {8, 16, 32, 64}, is, respectively, λ ≈ {0.31, 0.14, 0.07, 0.03}. The equivalent measured resistance which results by combining the resistance of the accessed node with the parasitic resistance, when the stored state of the ASM during read-out becomes FPM/RPM = ON/ON, i.e. when the composite resistance becomes 2 × R ON, is as follows:

Assuming a high enough resistance ratio β, from Eq. (8), we have R EQ,1 ≈ 2 × R ON. This means that the result of reading this state only involves the less resistive state of the memristors and is almost independent of the crossbar size and the stored data distribution within the rest of the memory array. Similarly, when the stored state of the ASM is the opposite, i.e. which remains unaffected during read-out, the corresponding equivalent resistance is as follows:

According to Eq. (9), the result of reading this stored state appears to exclusively depend on parameter λ, i.e. on the crossbar size. In particular, for large crossbar arrays where λ < < 1, it is R EQ,2 ≈ λ × R OFF. Hence, in this case, the measured resistance involves the most resistive state of the memristors. In overall, the resulting general ratio between the two equivalent resistances becomes as follows:

According to Eq. (10), since each of the binary states involves different resistive states, then a high enough ratio β between these values is necessary and will certainly play a crucial role for the effective distinction between them during read-out, compensating the effect of the larger crossbar sizes represented by the small values of parameter λ.

Relative to having APMs as cross-point devices, we use again the same equivalent circuit of Fig. 5c, only that now the composite resistance at each node is equal to the resulting resistance of the two parallel connected devices, i.e. R OFF || R ON:

regardless again of the particular stored information. As a consequence for the entire grid, it is R sneak = R ON. Therefore, considering again a high enough resistance ratio β > > 1 as well as also assuming a quadratic crossbar array with m = n, then the parasitic resistance connected in parallel with the accessed APM is calculated as follows:

This parasitic resistance, compared to that of Eq. (7) which was derived for ASM-based crossbar, it results significantly smaller involving the less resistive state of the memristors, i.e. R ON. Combined with parameter λ, which gets smaller for larger array sizes, this resistance will quickly reach very small values, and thus, it is expected to affect dramatically the overall memory function. The equivalent measured resistance which results by combining the resistance of the accessed node with the parasitic resistance, when the stored state of the APM during read-out becomes FPM/RPM = OFF/OFF, i.e. when the composite resistance becomes R OFF/2, is as follows:

Assuming a high enough resistance ratio β, from Eq. (13) we have R EQ,1 ≈ λ × R ON, i.e. the measured resistance results the same with the parasitic resistance, affected only by the crossbar size (parameter λ) but not by the stored data distribution within the rest of the memory array. Similarly, when the stored state of the APM is the opposite, hence, during read-out it remains unaffected, the corresponding equivalent resistance is as follows:

Equation (14) shows that the result of reading this stored state, likewise in the case of ASMs, depends only on parameter λ and for large crossbar arrays, where λ < < 1, it will be R EQ,2 ≈ λ × R ON. Hence, in this case, the measured resistance involves again the less resistive state of the memristors. Therefore, the resulting general ratio between the two equivalent resistances becomes as follows:

According to Eq. (15), regardless of the high resistance ratio that the memristors may exhibit, since both binary states involve only R ON, then for large crossbar arrays (i.e. when λ < < 1) the effective distinction between the different stored states during read-out becomes totally impractical.

4 Simulation Results for APM/ASM-Based Crossbar Arrays

For evaluation and comparison purposes, read-out performances of several sets of crossbar memory designs are compared in this section. For all design sets, detection margins are normalized with respect to the applied readout voltage V PU since their values will be always proportional to V PU. Simulation results for the floating memristor array, considering either of the proposed cross-point memristive solutions, are shown in Fig. 6. Model parameter values are used as given in {α, b, c, m, f o, L o} = {5 × 104, 0, 0.1, 82, 310, 5}, and the limiting values of parameter r are selected as r min = 100 and r max equal to either of the following values {170, 390, 600, 900} corresponding to R ON ≈ 2 KΩ and R OFF ≈ {20, 200, 400, 600} ΚΩ, respectively. The latter result in four different memristance ratios β = {10, 100, 200, 300}. Moreover, the threshold voltages for ASMs and APMs are set in such a way so as to result in a wider (hence clearer) reading window, as explained earlier and shown in Fig. 2. In all read-out measurements, we assume common values for the pull-up resistors, namely, we set R PU = 2 × R ON for ASMs (i.e. equal to the less resistive state of an ASM) and R PU = R ON/2 for APMs (i.e. equal to the less resistive state of an APM), respectively. Also, different array sizes and/or different β = R OFF/R ON ratios affect the measured equivalent resistance. Therefore, taking into consideration the in-series sense resistor R PU as well as the composite switching behaviour that ASM and APM devices exhibit when studied inside the crossbar array (likewise we did for the stand-alone devices and presented in Fig. 3), here we selectively adjust the amplitude and the duration of the applied reading pulse V PU in order to achieve the largest possible voltage margins. Table 1 summarizes the used V PU pulse characteristics for each simulation scenario. It can be noticed that, although the necessary pulse duration seems comparable, there is a huge difference between the voltage amplitudes; unlike ASMs, APMs require much higher operation voltages which increase for larger crossbar arrays, regardless of the β ratio. As it was previously mentioned, the absolute values of the voltages presented in Table 1 are used only in the context of this survey since it is inacceptable to use such high voltages for any concrete memory application or non-volatile embedded memories.

Read voltage margins for ASMs and APMs (a, c) and normalized read voltage margin ΔV/V PU versus the stored data distribution in the grid for four different array sizes with up to 64 × 64 elements (b, d). Normalized read voltage margin ΔV/V PU versus crossbar size (quadratic array where columns = rows) for four different β = R OFF/R ON ratios. We consider reading one cross-point element/time and assume using R PU = 2 × R ON for ASMs and R PU = R ON/2 for APMs, respectively. Graphs presented in subfigures (a) and (c) correspond to ratio β = 200

In specific, the voltage margins for different distributions of the stored information in the memory array are calculated, for different grid sizes and for different β = R OFF/R ON ratios. With the used voltage scheme, we make sure that the corresponding voltage drop approximates the middle of the reading window only at the accessed device. Voltages at all non-accessed cells are limited to values below the threshold voltages of the reading window for both serial and parallel memristive cross-point configurations; thus, these storage cells are not affected during read-out. Our calculations, without loss of generality, neglect the word and bitline resistance R LINE, which in general should be small compared to R ON in order to be able to operate large crossbar arrays (for practical arrays, optimization between the array size and the R ON/R LINE ratio has to be worked out). In pure passive memristive crossbar arrays, the noise margins almost vanish very quickly as the array size gets larger regardless of the chosen resistance ratio [33]. Moreover, the measured voltages strongly depend on the distribution of the stored information in the memory. In this context, as shown in Fig. 6a, c, ASMs and APMs could efficiently address the sneak path problem since they exhibit measured resistances which are independent of the stored data distribution within the memory array. However, although ASM-based arrays exhibit high enough noise margins, this is not true for APM-based arrays where normalized voltage margins not only are lower but also decay with increased array sizes faster than in ASM-based architectures. Furthermore, in Fig. 6b, d, we notice the minor effect that high β values have on the APM-based array performance. In fact, examining each array size separately, in ASMs seemingly there is some improvement in the voltage margin when moving from lower to higher memristance ratios, whereas in the APMs case, there is no significant change; indeed for larger arrays, there is no evident difference at all.

Thereupon, although both ASMs and APMs could seemingly address the sneak path problem, based on our mathematical analysis and the presented simulation results, the effectiveness of anti-parallel memristors fails to compensate the devastating effect that large memory arrays have on the read-out voltages. The maximum achievable read voltage margin gets significantly smaller with increasing crossbar size and seems to approximate zero very quickly, regardless of the exhibited resistance ratio β of individual memristive devices. It is therefore evident that, unless some innovative techniques are found which will enlarge significantly the measured voltage margins, thus resulting in more effective read-out memory operations, APM-based crossbars are considered inappropriate for the practical realization of large passive crossbar memory systems.

5 Application of Alternative Topologies for ASM-Based Crossbar Memories

In [28] the present, authors introduced a set of novel topologies for passive memristor-based crossbar memories. Such alternative topologies comprise a certain percentage of insulating nodes, placed between mutually perpendicular wires, which are spread out inside the array according to specific distribution patterns. The motivation is to restrain current sneak paths and thus improve the voltage margins by replacing (hence “sacrificing”) some memory cells. Such a practice is considered a viable solution given the huge device density that the crossbar geometry offers compared to other circuit architectures. All patterns were tested in 32 × 32 and 64 × 64 memory arrays for the worst-case scenario when accessing only a single cell per read operation, and their performance was compared to that of the full memristive crossbar. As far as the amount of the inserted insulators is concerned, three different cases were examined where their number approximates 10, 25 or 50 % of the total nodes of the grid under consideration. In each case, the selected distribution of the insulating junctions aims to uniformly cover the entire area of the grid, as much as this is possible, depending on the specific pattern and the actual grid size. The introduced patterns delivered up to 4× better read-out voltages for this type of reading approach. In particular, the uniformly distributed insulating junctions of the “uniformly distributed” pattern restrained better the current sneak paths, and thus, this topology had the best performance. In this pattern, the insulating nodes are placed in such a manner in order to be uniformly distributed both horizontally and vertically inside the grid. For each insulator, the closest neighbouring insulating nodes are always found at equal horizontal and vertical distances. A schematic representation of the aforementioned pattern is depicted in Fig. 7a where red dots denote insulating nodes, placed between mutually perpendicular wires, and simple wire crossings denote memristive cross-points.

Application of a novel topology to an ASM-based crossbar memory. A schematic representation of the applied pattern is shown in (a) with the insulating junctions being uniformly distributed across the array. In (b), the normalized read voltage margin for the worst-case reading scenario for both 32 × 32 and 64 × 64 grids is shown. The tested pattern introduces 10, 25, or 50 % insulators, and its performance is compared to the corresponding performance of the pure ASM-based grid with 0 % insulating nodes with the memristance ratio set to β = 200

In the present work, we applied the most efficient one of the tested topologies to ASM-based memory arrays. We then evaluated the performance of the pattern by comparing the read-out voltage margins with those of the pure ASM-based grid. In our simulations, we use the same model parameter values and the same voltage pulsing characteristics, as previously shown in Section 4, though here we examine only the case where the memristance ratio is set to β = 200. More specifically, the calculated voltage margins are normalized to those of the grid without insulators, and their relation is presented in Fig. 7b. Both 32 × 32 and 64 × 64 memory arrays were employed, and the read-out operation was performed to the leftmost cell of the upper row of the grid where no insulating node is found (see Fig. 7a). The resistances of the interconnects, the sensing elements, and the voltage source/s are not taken into consideration here in order to reduce the total complexity of the system and minimize simulation runtime, given that their effect has already been examined before [32]. As shown in Fig. 7b, the new voltage margins are improved incrementally when increasing the percentage of the inserted insulating nodes and the notable improvement reaches up to 21 % (42 %) for 32 × 32 (64 × 64) arrays when half of the existing nodes are insulators. Another interesting observation concerns the resulting ratio between the measured voltages for corresponding percentages of insulated nodes in the two considered grid sizes. Particularly, one can observe that for each one of the examined percentage rates, doubling the size of the side of the square lattice results in almost doubling the rate of improvement in the measured voltages. Therefore, it is assumed that such important improvement of the measured voltages is kept when moving to much larger quadratic memory crossbar arrays.

The induced voltage margin enhancements are uniform for the entire grid, though the actual measured voltages are expected to slightly decay as we move away from the voltage sources, taking into consideration the resistances of the word and bitlines [32]. The alternative crossbar topology should be also proven useful in large hierarchical memory organizations where the option of dividing a memory lattice into a number of smaller-sized sub-arrays exists, in order to maintain sufficient voltage margins. According to simulation results shown in Fig. 6, the smaller the memory array size, the larger the voltage margin gets. Therefore, pure memristive arrays need to get divided in much smaller sub-arrays so as to deliver voltage margins which surpass the ones offered by arrays including insulators. Given the possible voltage margin improvements offered by the novel array topology, the necessary sub-arrays composing a larger collective memory should be less in number and larger in size, thus reducing the overhead of extra peripheral circuits. The current sneak path problem is better addressed by following the presented novel approach, thus providing a viable option for the enhancement of the measured read-out voltage margins which will allow for the better distinction of the different stored memory states of ASM-based resistive crossbars.

6 Conclusions

In this work, we studied and compared the anti-serial (ASM) and anti-parallel (APM) memristors concept towards the possible solution of the current sneak path problem of crossbar memory arrays. We presented the memory operation principles for both cross-point memristive configurations and described the fundamentals of resistive memories comprising the proposed types of storage cells. Through mathematical analysis and simulations, we explored the performance and efficiency of various crossbar arrays using either ASMs or APMs and derived their pros and cons. We reported how ASMs and APMs could efficiently address the sneak path problem by exhibiting measured resistances which are independent of the stored data distribution within the rest of the memory array. Nevertheless, exclusive of their simpler configuration and operation principles, we finally proved that APMs do not allow for excessive memory scaling because the resulting read-out voltage margins substantially decay with crossbar array size. A novel architectural topology for passive resistive memory systems was also applied to an APM-based crossbar grid and delivered significantly improved read-out voltages, thus contributing even more to address the parasitic conducting problem. The presented comprehensive analysis will certainly be useful to engineers and scientists willing to study the composite operation of serial/parallel memristive configurations and explore their usefulness in a variety of emerging applications.

References

Wright, C. D., Liu, Y., Kohary, K. I., Aziz, M. M., Hicken, R. J. (2011). Arithmetic and biologically-inspired computing using phase-change materials. Advanced Materials, 23, 3408–3413.

Waser, R. (2009). Resistive non-volatile memory devices (Invited Paper). Microelectronic Engineering, 7–9, 1925–1928.

Wong, H.-S. P., Lee, H.-Y., Yu, S., Chen, Y.-S., Wu, Y., Chen, P.-S., et al. (2012). Metal-Oxide RRAM. Proceedings of the IEEE, 6, 1951–1970.

Chua, L. O. (2011). Resistance switching memories are memristors. Applied Physics, 4, 765–783.

Chua, L. O. (1971). Memristor—the missing circuit element. IEEE Trans Circuit Theory, 18, 507–519.

Strukov, D. B., Snider, G. S., Stewart, D. R., Williams, R. S. (2008). The missing memristor found. Nature, 453, 80–83.

Sacchetto, D., Doucey, M.-A., De Micheli, G., Leblebici, Y., Carrara, S. (2011). New insight on bio-sensing by nano-fabricated memristors. BioNanoScience, 1–2, 1–3.

Vourkas, I., & Sirakoulis, G. C. (2013). Recent progress and patents on computational structures and methods with memristive devices. Recent Patents on Electrical & Electronic Engineering, 2, 101–116.

Erokhin, V., Berzina, T., Camorani, P., Smerieri, A., Vavoulis, D., Feng, J., et al. (2011). Material memristive device circuits with synaptic plasticity: learning and memory. BioNanoScience, 1–2, 24–30.

Howard, G., Gale, E., Bull, L., de Lacy, C. B., Adamatzky, A. (2012). Evolution of plastic learning in spiking networks via memristive connections. IEEE Trans Evolutionary Computation, 5, 711–729.

Erokhin, V., Howard, G. D., Adamatzky, A. (2012). Organic memristor devices for logic elements with memory. International Journal of Bifurcation and Chaos, 11, 1250283.

Manem, H., Rajendran, J., Rose, G. S. (2012). Design considerations for multilevel CMOS/nano memristive memory. ACM Journal on Emerging Technologies in Computing Systems, 1–6, 1–22.

Lehtonen, E., Poikonen, J. H., Laiho, M., Kanerva, P. (2013). Large-scale memristive associative memories. IEEE Transactions on Very Large Scale Integration (VLSI) Systems. doi:10.1109/TVLSI.2013.2250319.

Eshraghian, K., Cho, K.-R., Kavehei, O., Kang, S.-K., Abbott, D., Kang, S.-M. S. (2011). Memristor MOS content addressable memory (MCAM): hybrid architecture for future high performance search engines. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 8, 1407–1416.

Gaillardon, P.-E., Sacchetto, D., Beneventi, G. B., Ben Jamaa, M. H., Perniola, L., Clermidy, F., et al. (2013). Design and architectural assessment of 3-D resistive memory technologies in FPGAs. IEEE Transactions on Nanotechnology, 1, 40–50.

Hussaina, W., & Jahinuzzaman, S. M. (2012). A read-decoupled gated-ground SRAM architecture for low-power embedded memories. Integration, the VLSI Journal (Special Issue of GLSVLSI 2011: Current Trends on VLSI and Ultra Low-Power Design), 3, 229–236.

International Technology Roadmap for Semiconductors (2013) [Online]: http://www.itrs.net/ Accessed 24 December 2013.

Heath, J. R., Kuekes, P. J., Snider, G. S., Williams, R. S. (1998). A defect-tolerant computer architecture: opportunities for nanotechnology. Science, 280, 1716–1721.

Zidan, M. A., Fahmy, H. A. H., Hussain, M. M., Salama, K. N. (2013). Memristor-based memory: the sneak paths problem and solutions. Microelectronics Journal, 2, 176–183.

Lee, M.-J., Park, Y., Kang, B.-S., Ahn, S.-E., Lee, C. B., Kim, K., et al. (2007). 2-stack 1D–1R cross-point structure with oxide diodes as switch elements for high density resistance RAM applications (pp. 771–774). Washington, DC: IEEE Int Elec Dev Meeting (IEDM 2007).

Fei, W., Yu, H., Zhang, W., Yeo, K. S. (2012). Design exploration of hybrid CMOS and memristor circuit by new modified nodal analysis. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 6, 1012–1025.

Kim, K.-H., Gaba, S., Wheeler, D., Cruz-Albrecht, J. M., Hussain, T., Srinivasa, N., et al. (2012). A functional hybrid memristor crossbar-array/CMOS system for data storage and neuromorphic applications. Nano Letters, 1, 389–395.

Kim, S., Jeong, H. Y., Kim, S. K., Choi, S.-Y., Lee, K. J. (2011). Flexible memristive memory array on plastic substrates. Nano Letters, 12, 5438–5442.

Shin, J., Kim, I., Biju, K. P., Jo, M., Park, J., Lee, J., et al. (2011). TiO2-based metal—insulator—metal selection device for bipolar resistive random access memory cross-point application. Journal of Applied Physics, 3, 033712.

Linn, E., Rosezin, R., Kugeler, C., Waser, R. (2010). Complementary resistive switches for passive nanocrossbar memories. Nature Materials, 5, 403–406.

Liu, T., Kang, Y., Verma, M., Orlowski, M. K. (2012). Switching characteristics of antiparallel resistive switches. IEEE Transactions on Electron Devices Letters, 3, 429–431.

Vourkas, I., & Sirakoulis, G. C. (2012). A novel design and modeling paradigm for memristor-based crossbar circuits. IEEE Transactions on Nanotechnology, 6, 1151–1159.

Vourkas, I., Stathis, D., Sirakoulis, G. C. (2013). Improved read voltage margins with alternative topologies for memristor-based crossbar memories (pp. 364–367). Istanbul: Proc 21st IFIP/IEEE Int Conf Very Large Scale Integr (VLSI-SoC 2013).

Tappertzhofen, S., Linn, E., Nielen, L., Rosezin, R., Lentz, F., Bruchhaus, R., et al. (2011). Capacity based nondestructive readout for complementary resistive switches. Nanotechnology, 39, 395203.

Vourkas, I., & Sirakoulis, G. C. (2013). On the analog computational characteristics of memristive networks in 2013 (pp. 309–312). Abu Dhabi: IEEE Int Conf Electronics, Circuits, and Systems (ICECS 2013).

Pershin, Y. V., & Di Ventra, M. (2011). Memory effects in complex materials and nanoscale systems. Advances in Physics, 2, 145–227.

Mustafa, J., & Waser, R. (2006). A novel reference scheme for reading passive resistive crossbar memories. IEEE Transactions on Nanotechnology, 6, 687–691.

Flocke, A., & Noll, T. G. (2007). Fundamental analysis of resistive nano-crossbars for the use in hybrid nano/CMOS-memory (pp. 328–331). Munich: 33rd European Conf Solid State Circuits (ESSCIRC 2007).

Acknowledgments

This work was supported in part by a scholarship from the Bodossaki Foundation in Greece.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Vourkas, I., Sirakoulis, G.C. Nano-Crossbar Memories Comprising Parallel/Serial Complementary Memristive Switches. BioNanoSci. 4, 166–179 (2014). https://doi.org/10.1007/s12668-014-0132-y

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12668-014-0132-y