Abstract

Multipliers act as processors and take on the notable work of many computing frameworks. The speed of the processor is profoundly affected by the speed of their multipliers. In order to improve the system speed, faster and more efficient multipliers should be used. A Vedic multiplier is one of the best solution that can be used to perform multiplications at a faster rate by eliminating the steps that are not needed in usual multiplication process. Power consumption is another critical issue in embedded systems that cannot be ignored. Reversible logic has become notable in the recent years because of its potential to reduce power utilization, which is a major concern in digital design. In this work, a high-speed 16 × 16 Vedic multiplier was designed using Urdhva Tiryagbhyam (UT) sutra, which is derived from Vedic mathematics. This is a simple structure as well as an unbeatable combination for creating any complex multiplication operations for services where speed is of prime importance. This work also proposes a new method based on Elliptic Curve Cryptography (ECC) system for encryption and decryption using Vedic multiplication. By using Vedic Multiplication in ECC the processing time is perfectly reduced. The proposed Elliptic curve cryptography method is much faster than other elliptic curve cryptographic algorithms. Compared to other cryptographic techniques, the key size required to provide equivalent security is small in ECC.

Similar content being viewed by others

Explore related subjects

Discover the latest articles, news and stories from top researchers in related subjects.Avoid common mistakes on your manuscript.

1 Introduction

Digital signal processor (DSP) circuits intended for very high-speed data handling is utilized in image processing, audio communication, information security and control applications. Most DSP applications perform arithmetic operations such as addition, subtraction, multiplication, and division. It takes more number of clock cycles to perform simple multiplication operation. To solve this problem, Urdhva Tiryagbhyam (UT) sutra is used (Saha et al. 2012; Kishore et al. 2018).

The main part of any embedded framework is low control, high speed and small area. With the use of Vedic methodology, the processor speed gets increased. Introducing reversible logic reduces power usage which is the main prerequisite of any processor design. One of the most important components of advanced digital computing design is computerized microchips, signal processing, and FIR filters and so on. Power dissipation is zero under reversible logic with Vedic mathematics. Increase in the performance of these applications can be achieved by optimizing various factors like speed, control and tolerance to non-critical failure.

Reversible logic is a promising example of a computational design that presents a method for building a computer that does not generate heat. Reversible calculations are the result of the development of quantum mechanics for general-purpose computers. Specifically, the basic principle of reversible computation is based on the relationship between entropy, quantum electromagnetic transfer of heat between electrons, and quantum molecule probability of occupying a specific state at some random time.

The elemental rule of reversible logic is that the gadget has similar number of input and output lines, where the electrodynamics of the framework permits the desire for every future state to rely upon a comparable number of known past states and the frame work arrives at each possible state, outcome of this being no power dissipation.

2 Related works

Multiplier designs based on reversible logic have received much consideration in recent years as a result of its capacity to lessen the power dissipation to make it suitable for low- power VLSI design applications. It is used in low power complementary metal-oxide semiconductors, optical computing, polymer computing, quantum computing and nanotechnology (Shukla et al. 2018). In Irreversible hardware operation, power is dissipated during running time (Krishnaveni and Umarani 2012). In upcoming low power application design methods, usage of Reversible logic will become unavoidable. The primary objective of all the computerized processors and other compact gadgets is to lessen control dispersal, which requires low power utilization and very high-speed multipliers (Kumar 2013; Rakshith and Saligram 2013; Saligram and Rakshith 2013; Parween and Murugeswari 2014).

Multiplier or Multiplication operation is significant in most of the signal processing systems. Multipliers take more operating frequencies to complete an operation and also consumes more power for processing the same. More current will be utilized to carry out this operation and the power that is dissipated as heat must be removed by using suitable cooling method. Battery life in portable electronic gadgets is restricted (Anitha et al. 2015; Pohokar et al. 2015). Low power configuration straightforwardly prompts long procedure times in these movable devices (Kant and Sharma 2015). In low power VLSI design, designing of a multiplier that consumes low power and occupying less space is a daunting task. Vedic process based multiplier design is described in Vijeyakumar et al. (2016), Sree et al. (2017), Pandey and Kumar (2016). This provides us with a hierarchical design technique.

In Arunkumar et al. (2016), Bathija et al. (2012) the Urdhva-Tiryakbhyam (UT) and Nikhilam sutras for Vedic multiplication are discussed (Gowthami and Satyanarayana 2018; Muthulakshmi et al. 2015) discussed the concept of Elliptic Curve Cryptography (ECC) with Vedic multiplier. In Shivanagi et al. (2016), using Vedic multiplier in ECC, the adder quantity is significantly reduced. Gaur et al. (2018), discussed an Indian vedic mathematics based complex multiplier design which could be employed for complex mathematical circuits performing at high speed. The Vedic multiplier is proposed using reversible logic with reduced TRLIC and reduced delay (Sonali et al. 2016; Jain and Jagtap 2014; Sakode and Morankar 2014). A 4-Bit Vedic multiplier circuit using Reversible logic with improved performance parameters is discussed by Sonali and Shekhar (2016), Shukla et al. (2020). Shaheen et al. (2018) proposed to develop encryption/decryption algorithms for digital images using DCT and DWT techniques that are suitable to transmit images over WSN. In Xia et al. (2019) provides a basic methodology for designing the adaptive control limit and recommended values of some key parameters (e.g. window size) for a better application.

3 Reversible logic gates

The reversible logic gate has a logical gadget of N input and N output that gives a coordinated mapping among input and output. In addition to the fact of N input and N output, it can also be used to recover the input from the output. Garbage output of a reversible logic refers to the number of unused outputs that are added voluntarily to produce N input and N output logic. Quantum cost indicates the cost of the circuit in terms of number of primitive gates used in the reversible gate to produce the desired output. The structural limitation for reversible logic circuits is as follows.

The reversible logic gate does not permit fan-out. Reversible logic circuits ought to have the least quantum cost. This arrangement can be stream lined to make minimum number of garbage outputs. The basic reversible logic gates are discussed below.

3.1 Feynman gate

The schematic diagram of Feynman gate is shown in Fig. 1. It is a 2 × 2 gate. Another name of Feynman gate is control NOT (CNOT) gate. The quantum cost of Feynman gate is one.

3.2 Peres gate

The logic circuit of the Peres gate has been displayed in Fig. 2. It is a 3 × 3 gate with a quantum cost of four. Different Boolean functions are implemented using this logic.

3.3 Fredkin gate

The logic circuit of the Fredkin gate is presented in Fig. 3. It isa 3 × 3 gate with a quantum cost of five. Different multiplexer designs can be implemented using this logic.

3.4 HNG Gate

The logic circuit of the HNG gate is shown in Fig. 4. It has 4 inputs 4 outputs with a quantum cost of Six. Different types of ripple carry adder circuits can be implemented using this logic. Both the sum and carry outputs of a Full adder can be generated by using HNG reversible logic gate to minimize gate count and garbage output.

3.5 Reversible logic circuit—design parameters

The below-cited factors have reflected the performance of a reversible logic circuit.

Number of gates The number of reversible logic gates required to obtain the predetermined logic.

Constant inputs The number of inputs to be maintained at a constant value to get the desired output.

Garbage outputs These outputs might be introduced voluntarily to ensure that there are N outputs corresponding to N inputs. They might remain unused but helps in maintaining the reversibility of the circuit

Quantum cost The number of original primitive gates that the reversible logic gate requires determines the quantum cost. The general quantum cost of developing all the logic gates it uses is equal to quantum cost of the reversible logic circuits.

Total reversible logic implementation cost (TRLIC) The constant input, the amount of garbage output, the quantum cost and the number of gates used refers TRLIC.

3.6 Design constraints

TRLIC and delay are the two constraints in the structure of reversible logic circuits that ought to be carefully maintained. The logical combination of reversible logic circuits, with an upgrade structure shall be completed by having

-

i.

The minimum number of logic gates ought to be utilized in structure.

-

ii.

Constant input ought to be minimal.

-

iii.

The measure of garbage outputs ought to be kept minimal.

-

iv.

Quantum costs ought to be kept as low as possible.

4 Proposed 16 × 16 bit reversible Vedic multiplier architecture

A 2 × 2 Vedic multiplier that is constructed using reversible logic gate is shown in Fig. 5. The circuit of 2 × 2 Vedic multiplier consists of six reversible logic gates which includes one Feynman gate and five Peres gates. The quantum cost is 21 fora 2 × 2 Vedic multiplier with a steady input number of 4 and garbage output of 9. A 2 × 2 multiplier is used to configure the structure of a reversible 4 × 4 Vedic multiplier. Accordingly, 4 × 4 multiplier is used to configure the structure of a 8 × 8 Vedic multiplier. 8 × 8 multiplier is used to configure the structure of 16 × 16 Vedic multiplier.

The Fig. 6 shown below is the architecture of 16 × 16 multiplier using Vedic method. In this structure is developed using four 8 × 8 multipliers. The input size of each multipliers are eight bits, which are obtained form 16 bit multipliers and 16 bit multiplicand. The output in lower 16 bits of first 16 × 16 multiplier are caught as the most minimal 16 bits of final result of multiplication. Input to 16-bit RCA is obtained by appending 16 zeros to the upper 16 bits. The 17-bit RCA input is obtained from a 16-bit RCA obtained by summing the outputs of two other 8 × 8 Vedic multipliers. The lower 8 bits yield of RCA (17bit) are caught as . The other 9 bits are given to next RCA (16 bit) in the wake of connecting 14 zeros with this 18 bits. The last 8 × 8 Vedic multiplier yields the other 16 information bits. The output of this 16-bit RCA is most significant bit of final output in 32-bit multiplication. Here PERES Gate is used to implement RCA. The quantity of bits that should be ripple carried decides the quantity of PERES gates to be utilized. Accordingly 16 bit RCA needs 16 PERES gate.

4.1 Vedic multiplication using Urdhva Tiryagbhyam algorithm

The working procedure of Vedic multiplication is based on Vedic sutras. A widely used Vedic sutra is Urdhva tiryagbhyam. In this sutra Urdhva refers to a vertical operation and Tiryagbhyam refers to a crosswise operation. The addition operation and generation of partial products is done at the same time. A generalized algorithm for n × n bit number can be structured.

Different kinds of multipliers have the number of bits added as a multiplicand or multiplier, and the delay estimate of the item is not relatively increased. Due to this reason, the calculation time is directly proportional to the clock frequency of processor. The binary multiplication function of Urdhva Tiryagbhyam is as shown in Fig. 7.

4.2 ECC using reversible Vedic mathematics

The ECC performance depends on the point multiplication. Pseudo random generators, Key negotiation, signature generation are the areas where elliptic curves shall be applied. Signature generation and verification operations involve a key role in the efficiency of the system for scalar multiplication. Scalar multiplication, floating-point arithmetic and finite field arithmetic are three levels of ECC operations. In order to reduce the ECC scalar multiplication, time point arithmetic level is an improvement where it must be implemented. Consistency is an important feature of the Vedic system. The entire system is highly correlated and unified. Normal multiplication and simple square methods can be reversed and used to generate a row square root and a row split. The following elliptic curve discrete logarithm problem is explained. Consider having two points P, Q∈E find an integer x with the end goal that Q = XP, if such x exists in the elliptic bend E defined in GF(q). Solving the elliptic bend discrete logarithm issue accomplishes ECC security. Elliptic bend discrete logarithm issue is more troublesome than solving integer deterioration issue and discrete logarithm issue.

4.2.1 Elliptic curve working procedure

Point addition Think about two distinct points’ k and K such that:

Let L = J+Kwhere

where s = slope of the line through J and K that is s = (Yj − Jk)/Xj − Xk.

Point subtraction Think about two distinct points’ k and K such that:

Then, J − K = J + (− K), Where, − K = (XK − YK)modp

Point doubling

Think about point J such that

Then

The Value of s = \(\frac{{\left( {3xj^{2} + a} \right)}}{2y}\)

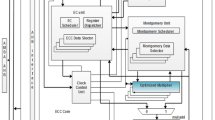

The proposed Elliptic Curve Cryptography with reversible logic based 16 × 16 Vedic multiplier’s working procedure is delineated in Fig. 8. The activity of point doubling and point expansion assumes a key job in the cryptographic calculation that determines the operational time. In this approach, two types of fields, such as binary fields and prime fields are used for the cryptosystem. Several important principles and alternative formulations used in Vedic mathematics are used here to address the full numerical multiplication. The Vedic multiplier structure has high speed compared to the conventional Montgomery multiplier.

5 Results and discussion

The Urdhva Tiryakbhayam (UT) Vedic multiplier is implemented using a reversible logic gate using Xilinx 14.3 IDE. First, the basic 2 × 2 UT Vedic multiplier is designed. This design implementation stems from traditional logic. Thereafter, a 4 × 4 vedic multiplier is obtained by block linking the 2 × 2 UT Vedic multiplier. A block of 4 × 4 UT Vedic multipliers is used to obtain an 8 × 8 multiplier. A 16 × 16 multiplier is obtained by block linking of 8 × 8 UT Vedic multipliers. The following diagram and table discusses the simulation results of the proposed reversible logic based 16 × 16 Vedic multiplier used for ECC application and the problem identification of existing ECC application is listed through Table 1.

Figure 9 shows the simulation results of a 16 × 16-bit reversible logic based Vedic multiplier using a 4 × 4 bit Vedic multiplier and an RCA.

Figure 10 shows the simulation results of a 16 × 16Vedic multiplier with reversible logic based ECC processor. This ECC processor generates three keys (OUT1, OUT2 and OUT3).

The reversible Vedic multiplier based Register Transistor Logic schematic diagram is shown in Fig. 11.

Power and time delay analysis of proposed reversible logic with Vedic multiplier based ECC processor is discussed in Table 2 and Fig. 12. The Simulation results are obtained from Xilinx 14.3 IDE. As compared with normal Vedic multiplier the proposed reversible logic based Vedic multiplier gives the perfect result against time delay and power utilization.

In numerical analysis, the speed at which a convergent sequence approaches its limit is called the rate of convergence. Fast convergence is especially important in wireless networks which are dominated by the dynamics of incoming and outgoing flows as well as the time sensitive applications. It provides the detailed comparison between the proposed algorithms and the traditional algorithm in terms of the convergence speed and the average delay through simulations

From Table No. 2 and Fig. 12 we can say that as compared with normal Vedic multiplier the proposed reversible logic based Vedic multiplier gives the perfect result against time delay and power utilization.

Table 3 and Fig. 13 discusses the time delay and performance analysis of the proposed multiplier with conventional multipliers. When compared with all multipliers, the proposed 16 × 16 multiplier gives the best results against all working conditions.

The Fig. 14 shown above discusses the performance analysis of the proposed Elliptic Curve Cryptography using Reversible logic-based Vedic multiplier. This figure clearly says that the proposed system gives the best result against all parameters, for example Hardware Area overhead Reduction is (84.01%), Power Reduction is (71.09%) and time delay reduction is (28.61%).

6 Conclusion

Multipliers are one of the most important blocks in any type of processor and computing devices. More generally, the performance of the microcontroller and Digital Signal Processor is determined depending on the quantity of multiplications finished in a unit of time. In this manner, a superior multiplier design can securely improve the capacities of the gadget. The Vedic multiplier is one such Great arrangement.

From the results, the Vedic multiplier is more efficient than the traditional multiplier. Due to the increase in the number of bits to 16 × 16 bits from 8 × 8 bits, the timing delay is significantly reduced for the Vedic multiplier compared to conventional multipliers. The time delay of a 16 × 16-bit digital gyro multiplier is 56.667 ns, while the time delay of a conventional multiplier is 70.184 ns, respectively. The memory required for the 16 × 16-bit multiplier Vatican is 264,972 kilobytes and the existing multiplier requires 300,876 kilobytes. The Vedic multiplier subsequently speaks to the upgraded speed between ordinary multipliers, while additionally diminishing the memory of the framework. The power utilization of a Vedic multiplier utilizing a reversible logic of 16 × 16 bits is 322.15 mW and without reversible logic is consume the power of 392.22 mW. Along these lines Vedic multiplier utilizing reversible logic shows decreased power utilization compared without reversible logic circuits. The proposed system gives the best result against all parameters, for example Hardware Area overhead Reduction is (84.01%), Power Reduction is (71.09%) and time delay reduction is (28.61%). In future use different multiplier to improve the security of ECC.

Change history

14 June 2022

This article has been retracted. Please see the Retraction Notice for more detail: https://doi.org/10.1007/s12652-022-04123-1

References

Anitha R, Deshmukh Neha, Agarwal P, Reglend Jacob, Sahoo Sarat Kumar, Prabhakar K (2015) A 32 BIT MAC unit design using vedic multiplier and reversible logic gate. Int Conf Circ Power Comput Technol. https://doi.org/10.1109/ICCPCT.2015.7159505

Arunkumar, Verma R, Nishanth S (2016) High speed 32-bit vedic multiplier for DSP applications. Int J Comput Appl 135(7):35–38

Bathija R, Meena R, Sarkar S, Sahu Rajesh (2012) Low power high speed 16x16 bit multiplier using vedic mathematics. Int J Comput Appl 59(6):41–44. https://doi.org/10.5120/9556-4016

Gaur HM, Singh AK, Ghanekar U (2018) In-depth comparative analysis of reversible gates for designing logic circuits. Proc Comput Sci 125:810–817

Gowthami P, Satyanarayana RVS (2018) Performance evaluation of reversible Vedic multiplier. ARPN J Eng Appl Sci 13(3):1002–1008

Jain S, Jagtap VS (2014) Vedic mathematics in computer: a survey. Int J Comput Sci Inf Technol 5(6):7458–7459

Kant A, Sharma S (2015) Applications of vedic multiplier designs—a review. Conf Reliabil Infocom Technol Optim. https://doi.org/10.1109/ICRITO.2015.7359309

Kishore K, Noorbasha F, Sandeep K, Bhupesh DNV, Imran SK, Sowmya K (2018) Linear convolution using UT Vedic multiplier. Int J Eng Technol (UAE) 7(28):409–412

Krishnaveni D, Umarani (2012) VLSI implementation of vedic multiplier with reduced delay. Int J Adv Technol Eng Res 2(4):10–14

Kumar CH (2013) Implementation and analysis of power, area and delay of array, Urdhva, Nikhilam vedic multipliers. Int J Sci Res Publ 3(1):1–5

Muthulakshmi D, Durgadevi S, Iyyappan B (2015) High speed and reduced area 16 bit vedic multiplier using carry select adder. Int J Adv Res Trends Eng Technol (IJARTET) 2(3):1–7

Pandey S, Kumar D (2016) A fast 16 x 16 vedic multiplier using carry select adder on FPGA. Int J Adv Res Comput Commun Eng 5(4):989–994

Parween AS, Murugeswari S (2014) Design of high speed, area efficient, low power vedic multiplier using reversible logic gate. Int J Emerg Technol Adv Eng 4(2):336–340

Pohokar SP, Sisal RS, Gaikwad KM, Patil MM, Borse R (2015) Design and implementation of 16 × 16 multiplier using Vedic mathematics. In: 2015 International Conference on industrial instrumentation and control, pp 1174–1177, https://doi.org/10.1109/iic.2015.7150925

Rakshith TR, Saligram R (2013) Design of high speed low power multiplier using reversible logic: a vedic mathematical approach. In: Proceedings of IEEE International Conference on circuit, power and computing technologies, pp 775–781, https://doi.org/10.1109/ICCPCT.2013.6528848

Saha P, Banerjee A, Dandapat A, Bhattacharyya P (2012) Design of high speed vedic multiplier for decimal number system. In: Rahaman H, Chattopadhyay S, Chattopadhyay S (eds) Progress in VLSI Design and test. Lecture notes in computer science, vol 7373. Springer, Berlin

Sakode, Morankar AD (2014) Reversible multiplier with peres gate and full adder. IOSR J Electro Commun Eng 9:43–50

Saligram R, Rakshith TR (2013) Optimized reversible vedic multipliers for high speed low power operations. In: 2013 IEEE conference on information and communication technologies, pp 809–814, https://doi.org/10.1109/cict.2013.6558205

Shaheen AM, Sheltami TR, Al-Kharoubi TM, Shaksukhi E (2018) Digital image encryption techniques for wireless sensor networks using image transformation methods: dCT and DWT. J Ambient Intell Human Comput 10:4733–4750

Shivanagi S, Kalpana AB, Kumaraswamy KV (2016) Do-254 implementation of high speed vedic multiplier. Int J Adv Res Electr Electron Instrum Eng 5(5):3537–3542

Shukla Vandana, Singh OP, Mishra GR, Tiwari RK (2018) Reversible realization of N-bit arithmetic circuit for low power loss ALU applications. Proc Comput Sci 125:847–854

Shukla V, Singh O, Mishra G, Tiwari R (2020) A novel approach for reversible realization of 4 × 4 bit vedic multiplier circuit. In: Advances in VLSI, communication, and signal processing. lecture notes in electrical engineering, vol. 587, pp. 733-746, https://doi.org/10.1007/978-981-32-9775-3_67

Sonali SK, Shekhar HB (2016) High speed, low power vedic multiplier using reversible logic gate. Int J Sci Res (IJSR) 5(9):570–573

Sonali SK, Kharat GU, Bodakeonali SH (2016) A review on vedic multiplier using reversible logic gate. Int J Innov Res Sci Eng Technol 5(4):5838–5844

Sree K, Mrudula ST, Geetha K, Ramachandra R (2017) Speed efficient 64 Bit MAC design using VEDIC multiplier and reversible logic gates. Int J Adv Res Innov Ideas Educ 3(6):370–376

Vijeyakumar KN, Kalaiselvi S, Saranya K (2016) VLSI implementation of high speed area efficient arithmetic unit using vedic mathematics. ICTACT J Microelectron 2(1):198–202

Xia B, Jian Z, Tao N (2019) An effective combined multivariate control chart based on support vector data description. J Ambient Intell Human Comput 10:4819–4835. https://doi.org/10.1007/s12652-018-1168-6

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

This article has been retracted. Please see the retraction notice for more detail: https://doi.org/10.1007/s12652-022-04123-1"

About this article

Cite this article

Karthikeyan, S., Jagadeeswari, M. RETRACTED ARTICLE: Performance improvement of elliptic curve cryptography system using low power, high speed 16 × 16 Vedic multiplier based on reversible logic. J Ambient Intell Human Comput 12, 4161–4170 (2021). https://doi.org/10.1007/s12652-020-01795-5

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12652-020-01795-5