Abstract

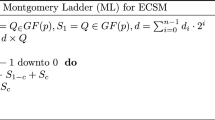

This paper presents a hardware implementation of Elliptic Curve Cryptography (ECC) with optimized scalar multiplication. In elliptic curve cryptography, scalar multiplication is an important and most time-consuming operation that dominates the ECC performance. In this paper, the scalar multiplication is carried out using the Vedic multiplier for finite field multiplication operation to improvise the performance. The proposed architecture is implemented and evaluated for the performance evaluation parameters—area, delay, and power consumption. To evaluate the efficiency of the proposed design, the results are compared with Karatsuba based ECC design. The comparative results show that ECC using Vedic multiplier outperform then Karatsuba based ECC for the area, delay and power consumption. The elliptic curve cryptosystem is implemented over GF(2m) binary field for B-233 field size, which is more secured according to NIST Digital Signature Standards. The cryptosystem is designed in Verilog HDL, synthesized and simulated using Xilinx 13.2 IDE on Virtex6 FPGA device.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Miller, V.S.: Use of elliptic curves in cryptography. In: Exploratory Computer Science, pp. 6–10. IBM Research, Yorktown Heights, New York (2013)

Koblitz, N.: Elliptic curve cryptosystems. Math. Comput. 48(177), 203–209 (1987)

Perumal, V., Gao, X.: Comparative analysis of elliptic curve cryptosystem and its survey. J. Chem. Pharm. Sci. 10(1), 414–419 (2017)

Christi, C., Kancheti, S.: Comparative study of elliptic curve cryptography and RSA in constrained environment (2010)

Setiadi, I., Kistijantoro, A.I., Miyaji, A.: Elliptic curve cryptography: algorithms and implementation analysis over coordinate systems. In: International Conference on Advanced Informatics: Concepts, Theory and Applications, November (2015)

Thakur, N.V., Kakde, O.G.: Compression mechanism for multimedia system in consideration of information security. In: Proceeding of International Workshop on Machine Intelligence Research MIR Day GHRCE-Nagpur, pp. 87–96, India (2009)

Deshmukh, K.H., Thakur, N.V.: An overview and approach for joint image encryption and compression. Int. J. Sci. Eng. Res. 7(2), 403–408 (2016)

Koschuch, M., et al.: Hardware/Software Co-Design of Elliptic Curve Cryptography on an 8051 Microcontroller, pp. 430–444. International Association for Cryptologic Research (2006)

Nawari, M., Ahmed, H., Hamid, A., Elkhidir, M.: FPGA based implementation of elliptic curve cryptography (2015)

Bartolini, S., Branovic, I., Giorgi, R., Member, S., Martinelli, E.: Effects of instruction-set extensions on an embedded processor : a case study on elliptic-curve cryptography over GF(2^m). 57(5), 672–685 (2008)

National Institute of Standards and Technology Gaithersburg, Publication, “Archived publication,” Federal Information Processing Standards Publication, Digital Signature Standard (DSS), vol. 3, no. August 2009 (2010)

“Elliptic Curve Cryptography: Algorithms and Implementation Analysis over Coordinate Systems Elliptic Curve Cryptography: Algorithms and Implementation Analysis over Coordinate Systems,” no. November (2014)

Lauter, K.: The advantages of elliptic curve cryptography for wireless security. IEEE Wirel. Commun. 11(1), 62–67 (2004)

Bhatta, J.: Techniques for elliptic curve cryptosystems on resource-constrained devices. In: 2015 9th International Conference on Software, Knowledge, Information Management and Applications (SKIMA), no. 978–1–4673–6744–8/15 (2015)

Harris, S., Mills, G., Brown, T.: Variability and drivers of extreme fire weather in fire-prone areas of south-eastern Australia. Int. J. Wildland Fire 26(3), 177–190 (2017)

Roy, S.S., Rebeiro, C., Mukhopadhyay, D.: Theoretical modeling of elliptic curve scalar multiplier on LUT-based FPGAs for area and speed. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 21(5), 901–909 (2013)

Azarderakhsh, R., Reyhani-Masoleh, A.: Parallel and high-speed computations of elliptic curve cryptography using hybrid-double multipliers. 26(6), 1668–1677 (2015)

Masoumi, M., Mahdizadeh, H.: Efficient hardware implementation of an elliptic curve cryptographic processor over GF(2^163). Int. J. Comput., Electr., Autom., Control. Inf. Eng. 2012 Int. 6(5), 725–732 (2012)

Rebeiro, C., Mukhopadhyay, D.: High performance elliptic curve crypto-processor for FPGA platforms. In: Proceedings of the 21st International Conference on VLSI Design, Hyderabad, IEEE Computer Society, pp. 706–711

Rebeiro, C., Mukhopadhyay, D.: Hybrid masked Karatsuba multiplier for GF (2^233). In: Proceedings of the 11th IEEE VLSI Design and Test Symposium, no. 1, pp. 379–387, Kolkata, VLSI Society of India

Vaidya, S., Dandekar, D.: Delay-power performance comparison of multipliers in VLSI. Int. J. Comput. Netw. Commun. (IJCNC) 2(4), 47–56 (2010)

Rajasekar, D., Anbalagan, E.: Design of high speed optimized vedic multiplication techniques. Int. J. Chem. Sci. 14(4), 3025–3036 (2016)

August, D.S.: Virtex-6 family overview summary of Virtex-6 FPGA features. 150, 1–11 (2015)

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2020 Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Kadu, R.K., Adane, D.S. (2020). Hardware Implementation of Elliptic Curve Cryptosystem Using Optimized Scalar Multiplication. In: Zhang, YD., Mandal, J., So-In, C., Thakur, N. (eds) Smart Trends in Computing and Communications. Smart Innovation, Systems and Technologies, vol 165. Springer, Singapore. https://doi.org/10.1007/978-981-15-0077-0_32

Download citation

DOI: https://doi.org/10.1007/978-981-15-0077-0_32

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-15-0076-3

Online ISBN: 978-981-15-0077-0

eBook Packages: Intelligent Technologies and RoboticsIntelligent Technologies and Robotics (R0)