Abstract

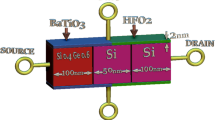

This paper presents a method-based investigation on the application of low dimensional materials like graphene, carbon nanotube (CNT), transition metal dichalcogenides (TMDCs) in tunnel field effect transistors (TFETs) for high on-current requirements. Three multi-criteria decision making methods (MCDM) are employed to arrive at a consensus on the appropriate material. The Ashby technique, the Technique for Order Preference by Similarity to Ideal Solution (TOPSIS) and VlseKriterijumska Optimazicija I Kompromisno Resenjein in Serbian (VIKOR) are utilized using constraints which decide a TFET’s performance. In order to select the material, dominant parameters have been included in the formulation which includes intrinsic material properties like the band gap, dielectric constant and electron effective mass along with an extrinsic parameter, namely, the on-state current to the off-state current ratio. The analysis demonstrates a remarkable agreement between the results of Ashby, TOPSIS and VIKOR methods, and concludes that carbon nanotube (CNT) has the most potential amongst all the candidates to be employed in the next generation TFETs.

Article PDF

Similar content being viewed by others

Explore related subjects

Discover the latest articles, news and stories from top researchers in related subjects.Avoid common mistakes on your manuscript.

References

Yong-Bin K (2010) Challenges for Nanoscale MOSFETs and emerging Nanoelectronics. Trans Electr Electron Mater 11:93. https://doi.org/10.4313/TEEM.2009.10.2.021

Chopra S, Subramaniam S (2015) A review on challenges for MOSFET scaling. Int J Innov Sci Eng Technol 2:1055–1057

Taur Y, Ning TH (2009) Fundamentals of modern VLSI Devices

Yau LD (1974) A simple theory to predict the threshold voltage of short-channel IGFET’s. Solid State Electron 17:1059–1063

Model TV, Devices LC (2005) Threshold voltage model. in: mosfet modeling & BSIM3 user’s guide. pp 65–103

Tamak P, Mehra R (2017) Review on tunnel field effect transistors ( TFET ). Int Res J Eng Technol 4:1195–1200

Esseni D, Pala M, Palestri P et al (2017). A review of selected topics in physics based modeling for tunnel field-effect transistors Semicond Sci Technol:32. https://doi.org/10.1088/1361-6641/aa6fca

Lu H, Seabaugh A (2014) Tunnel field-effect transistors: state-of-the-art. IEEE J Electron Devices Soc 2:44–49. https://doi.org/10.1109/JEDS.2014.2326622

Madan J, Chaujar R (2016) Gate drain-overlapped-asymmetric gate dielectric-GAA-TFET: a solution for suppressed ambipolarity and enhanced ON state behavior. Appl Phys A Mater Sci Process 122:1–9. https://doi.org/10.1007/s00339-016-0510-0

Boucart K, Ionescu AM (2007) Double-gate tunnel FET with high-$\kappa$ gate dielectric. IEEE Trans Electron Devices 54:1725–1733. https://doi.org/10.1109/TED.2007.899389

Madan J, Gupta RS, Chaujar R (2017) Performance investigation of heterogeneous gate dielectric-gate metal engineered–gate all around-tunnel FET for RF applications. Microsyst Technol 23:4081–4090. https://doi.org/10.1007/s00542-016-3143-5

Verhulst AS, Vandenberghe WG, Maex K, Groeseneken G (2007) Tunnel field-effect transistor without gate-drain overlap. Appl Phys Lett 91:1–4. https://doi.org/10.1063/1.2757593

Mallik A, Chattopadhyay A, Guin S, Karmakar A (2013) Impact of a spacer-drain overlap on the characteristics of a silicon tunnel field-effect transistor based on vertical tunneling. IEEE Trans Electron Devices 60:935–943. https://doi.org/10.1109/TED.2013.2237776

Naderi A, Keshavarzi P (2012) The effects of source/drain and gate overlap on the performance of carbon nanotube field effect transistors. Superlattice Microst 52:962–976. https://doi.org/10.1016/j.spmi.2012.07.016

Lee HK, Choi WY (2013) Linearity of hetero-gate-dielectric tunneling field-effect transistors. J Semicond Technol Sci 13:551–555. https://doi.org/10.5573/JSTS.2013.13.6.551

Kumar D, Dasgupta S, Ts JDS, et al (2017) With high on current and reduced turn on voltage

Gandhi R, Chen Z, Singh N et al (2011) Vertical Si-nanowire n-type tunneling FETs with low subthreshold swing (≤50 mV/decade) at room temperature. IEEE Electron Device Lett 32:437–439. https://doi.org/10.1109/LED.2011.2106757

Vishnoi R, Kumar MJ (2014) Compact analytical drain current model of gate-all-around nanowire tunneling FET. IEEE Trans Electron Devices 61:2599–2603. https://doi.org/10.1109/TED.2014.2322762

Arun Samuel TS, Arumugam N, Chandra ST (2017) Analytical approach and simulation of GaN single gate TFET and gate all around TFET. Trans Electr Eng Electron Commun 15:1–7

Beneventi GB, Gnani E, Gnudi A et al (2014) Dual-metal-gate InAs tunnel FET with enhanced turn-on steepness and high on-current. IEEE Trans Electron Devices 61:776–784. https://doi.org/10.1109/TED.2014.2298212

Kao KH, Verhulst AS, Vandenberghe WG et al (2012) Optimization of gate-on-source-only tunnel FETs with counter-doped pockets. IEEE Trans Electron Devices 59:2070–2077. https://doi.org/10.1109/TED.2012.2200489

Mitra SK, Bhowmick B (2019) An analytical drain current Model of gate-on-source/channel SOI-TFET. Silicon. https://doi.org/10.1007/s12633-019-0090-7

Yang Z (2016) Tunnel field-effect transistor with an L-shaped gate. IEEE Electron Device Lett 37:839–842. https://doi.org/10.1109/LED.2016.2574821

Convertino C, Zota CB, Schmid H et al (2018) III-V heterostructure tunnel field-effect transistor. J Phys Condens Matter 30. https://doi.org/10.1088/1361-648X/aac5b4

Kim G, Lee J, Kim JH, Kim S (2019) High on-current Ge-channel heterojunction tunnel field-effect transistor using direct band-to-band tunneling. Micromachines 10. https://doi.org/10.3390/mi10020077

Singh A, Khosla M, Raj B (2017) Design and analysis of electrostatic doped Schottky barrier CNTFET based low power SRAM. AEU - Int J Electron Commun 80:67–72. https://doi.org/10.1016/j.aeue.2017.06.030

Lam KT, Cao X, Guo J (2013) Device performance of heterojunction tunneling field-effect transistors based on transition metal dichalcogenide monolayer. IEEE Electron Device Lett 34:1331–1333. https://doi.org/10.1109/LED.2013.2277918

Balaji Y, Smets Q, Lockhart De La Rosa CJ et al (2018) Tunneling transistors based on MoS2/MoTe2Van der Waals Heterostructures. IEEE J Electron Devices Soc 6:1018–1055. https://doi.org/10.1109/JEDS.2018.2815781

Jena D (2013) Tunneling transistors based on Graphene and 2-D crystals. Proc IEEE 101:1585–1602. https://doi.org/10.1109/JPROC.2010.2070470

Gupta N, Haldiya V (2018) High-k gate dielectric selection for germanium based CMOS devices. Int J Nanoelectron Mater 11:119–126

Kandpal K, Gupta N (2016) Investigations on high-κ dielectrics for low threshold voltage and low leakage zinc oxide thin-film transistor, using material selection methodologies. J Mater Sci Mater Electron 27:5972–5981. https://doi.org/10.1007/s10854-016-4519-0

Deshmukh D, Angira M (2019) Investigation on switching structure material selection for RF-MEMS shunt capacitive switches using Ashby, TOPSIS and VIKOR. Trans Electr Electron Mater 20:181–188. https://doi.org/10.1007/s42341-018-00094-3

Ashby MF (2000) Multi-objective optimization in material design and selection. Acta Mater 48:359–369. https://doi.org/10.1016/S1359-6454(99)00304-3

Ashby M (2010) Materials selection in mechanical design: fourth edition

Hwang CL, Masud ASM (1979) Multiple objective decision making - methods and applications. Lect Notes Econ Math Syst 1:358. https://doi.org/10.1007/978-3-642-45511-7

Opricovic S, Tzeng GH (2004) Compromise solution by MCDM methods: a comparative analysis of VIKOR and TOPSIS. Eur J Oper Res 156:445–455. https://doi.org/10.1016/S0377-2217(03)00020-1

Lv Y, Qin W, Wang C et al (2019) Recent advances in low-dimensional Heterojunction-based tunnel field effect transistors. Adv Electron Mater 5:1–15. https://doi.org/10.1002/aelm.201800569

Roy T, Tosun M, Kang JS et al (2014) Field-effect transistors built from all two-dimensional material components. ACS Nano 8:6259–6264. https://doi.org/10.1021/nn501723y

Ilatikhameneh H, Tan Y, Novakovic B et al (2015) Tunnel field-effect transistors in 2-D transition metal Dichalcogenide materials. IEEE J Explor Solid-State Comput Devices Circuits 1:12–18. https://doi.org/10.1109/JXCDC.2015.2423096

Strojnik M, Kovic A, Mrzel A, et al (2014) MoS 2 nanotube field effect transistors. AIP Adv 4:0–5. https://doi.org/10.1063/1.4894440

Appenzeller J, Lin YM, Knoch J et al (2005) Comparing carbon nanotube transistors - the ideal choice: a novel tunneling device design. IEEE Trans Electron Devices 52:2568–2576. https://doi.org/10.1109/TED.2005.859654

Jiang XW, Li SS (2014) Performance limits of tunnel transistors based on mono-layer transition-metal dichalcogenides. Appl Phys Lett 104:1–5. https://doi.org/10.1063/1.4878515

Jahan A, Ismail MY, Sapuan SM, Mustapha F (2010) Material screening and choosing methods - a review. Mater Des 31:696–705. https://doi.org/10.1016/j.matdes.2009.08.013

Liao TW (2015) Two interval type 2 fuzzy TOPSIS material selection methods. Mater Des 88:1088–1099. https://doi.org/10.1016/j.matdes.2015.09.113

Mousavi-Nasab SH, Sotoudeh-Anvari A (2017) A comprehensive MCDM-based approach using TOPSIS, COPRAS and DEA as an auxiliary tool for material selection problems. Mater Des 121:237–253. https://doi.org/10.1016/j.matdes.2017.02.041

Opricovic S (1998) Multicriteria optimization of civil engineering systems

Léonard F, Tersoff J (2003) Dielectric response of semiconducting carbon nanotubes. Appl Phys Lett 81:4835–4837. https://doi.org/10.1063/1.1530373

Trivedi AR, Amir MF, Mukhopadhyay S (2014) Ultra-low power electronics with Si/Ge tunnel FET. 1–6. https://doi.org/10.7873/date.2014.244

Samuel TSA, Balamurugan NB (2014) Analytical modeling and simulation of germanium single gate silicon on insulator TFET. J Semicond 35. https://doi.org/10.1088/1674-4926/35/3/034002

Bessler R, Duerig U, Koren E (2019) The dielectric constant of a bilayer graphene interface. Nanoscale Adv 1:1702–1706. https://doi.org/10.1039/c8na00350e

Zhang Y, Tang TT, Girit C et al (2009) Direct observation of a widely tunable bandgap in bilayer graphene. Nature 459:820–823. https://doi.org/10.1038/nature08105

Fiori G, Iannaccone G (2009). On the possibility of tunable-gap bilayer graphene FET 30:261–264

Haddara YM, Ashburn P, Bagnall DM (2017) Silicon-germanium: properties, growth and applications. In: Kasap S, Capper P (eds) Springer handbook of electronic and photonic materials. Springer International Publishing, Cham, p 1

Huang C-TT (2015) Electrical and material properties of strained silicon/relaxed silicon germanium Heterostructures for single-Electron quantum dot applications. 1–127

Barber HD (1967) Effective mass and intrinsic concentration in silicon. Solid State Electron 10:1039–1051. https://doi.org/10.1016/0038-1101(67)90122-0

Sze SM, Ng KK (2006) Appendix F properties of important semiconductors. In: physics of semiconductor Devices. John Wiley & Sons, Ltd, p 789

Zhou HL, Jiang J, Zhang MX, Fang L (2010) Opitimization of tunneling carbon nanotube-FETs based on stair-case doping strategy. Sci China Inf Sci 53:2696–2704. https://doi.org/10.1007/s11432-010-4102-x

Javey A, Tu R, Farmer DB et al (2005) High performance n-type carbon nanotube field-effect transistors with chemically doped contacts. Nano Lett 5:345–348. https://doi.org/10.1021/nl047931j

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Manocha, P., Kandpal, K. & Goswami, R. Selection of Low Dimensional Material Alternatives to Silicon for Next Generation Tunnel Field Effect Transistors. Silicon 13, 707–717 (2021). https://doi.org/10.1007/s12633-020-00452-y

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-020-00452-y