Abstract

This paper presents the investigations on high-κ dielectrics for low operating voltage and low leakage zinc oxide thin film transistor (ZnO TFT) using three material selection methodologies namely Ashby, technique for order preference by similarity to ideal solution (TOPSIS) and VlseKriterijumska Optimizacija I Kompromisno Resenjein in Serbian (VIKOR). Various material properties such as dielectric constant, conduction band offset to ZnO, band-gap and temperature coefficient mismatch of high κ to ZnO are investigated to find out the most promising gate dielectric material. The analysis concludes that lanthanum oxide (La2O3) is the most promising gate dielectric material for ZnO TFT transistor. The result shows a good agreement between Ashby’s, TOPSIS and VIKOR approaches.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

From the last two decades, thin film transistors (TFTs) are mostly using polycrystalline silicon (poly-Si) or amorphous silicon (a-Si) as an active channel layer [1, 2]. However, these TFTs (especially the a-Si ones) suffer from various limitations such as low field effect mobility (μ FE ), light sensitivity, light degradation and threshold voltage shift. Fortunato et al. [3] suggested that utilization of efficient and reliable oxide based TFTs may overcome these problems. Transparent oxide semiconductor based transistors have recently been proposed using an active channel layer of zinc oxide, a II–VI compound semiconductor. ZnO possesses wide band-gap (3.4 eV), and has a stable wurtzite structure with lattice spacing a = 0.325 nm and c = 0.521 nm. It is a multifunctional material that can be applied to gas sensors, transparent electrodes, blue and UV light emitters, piezoelectric devices, photovoltaic devices, and bulk acoustic wave devices [4, 5]. Intrinsically it is an n-type semiconductor primarily due to presence of oxygen vacancies. As compared to a-Si, ZnO provides many advantages. It can be grown as a crystalline material at relatively low deposition temperature [6]. Further, it can be deposited on various substrates made of silicon or amorphous glasses [6], which make it possible to have a total transparent ZnO-TFT by depositing ZnO on the indium tin oxide (ITO) glasses. Because of its wide band-gap, the characteristics of ZnO-TFTs do not degrade in the exposure of visible light. Also, ZnO thin film used as an active channel layer can achieve a relatively high mobility.

The performance of a TFT depends fundamentally on the type of gate insulator and the quality of dielectric-channel interface because of the current flows in the ZnO channel next to the interface. In recent years, researchers have focused on high-κ dielectric materials as an alternative to SiO2 in highly-scaled electronic devices [7–10]. However, despite the intensive work on high-κ dielectrics, the performance of the devices with high-κ dielectrics is still rather poorly analyzed compared to those with SiO2 gate oxides. The use of high-κ gate dielectrics in TFTs is becoming increasingly necessary, as scaled transistors lead to unacceptable levels of gate leakage current. ZnO TFTs suffer from high operation voltage and threshold voltage compared to Si–H TFT, e.g. ZnO TFT with SiO2 or Si3N4 gate dielectric exhibits a very high threshold voltage (VT) value (10–20 V) [11]. An increase in coupling of gate field to the channel layer reduces the operating voltage of the transistor. This can be done either by reducing the gate dielectric thickness or by using a gate dielectric material with higher dielectric permittivity (high-κ gate dielectric). Both solutions increase the gate capacitance; however, high-κ material presents a more promising solution since a thicker high-κ layer may be used to produce an equivalent capacitance. But, the gate dielectric material selection is not straightforward. Many dielectric materials are currently under consideration as potential gate dielectric of ZnO thin film transistor. It includes HfO2, Gd2O3, La2O3, ZrO2, Ga2O3, Al2O3, BaTiO3 etc. [20–26].

The key performance parameters for selection of a potential gate dielectric require permittivity, band-gap and band alignment to ZnO. However, together with these parameters; film morphology, stability, interface quality, reliability and process compatibility [12] are also important to further enhance the device performance. As there are various high-κ dielectric that have been reported in fabrication of ZnO-TFT, where each dielectric is having its own advantages and limitations, so in order to find out the best possible alternative, one can use multi-criteria decision making (MCDM) approach [14] when there are more than one attribute. The MCDM approach is further subdivided into multi-objective decision making (MODM) and multi-attribute decision making (MADM). These approaches are well studied by many researchers in engineering regime [14–19]. The most popular material selection methodologies are Ashby approach [15, 16], TOPSIS and VIKOR [17, 18].

This paper is organized as follows: Sect. 2 deals with ZnO thin film transistor and high-κ dielectrics. Section 3 deals with material selection methodologies used in this work. Section 4 consists of determination of material indices used in the analysis. Section 5 consists of results and discussion, and Sect. 6 presents the conclusion drawn from the study.

2 ZnO TFT and high-κ dielectric

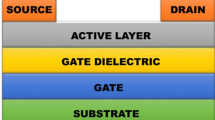

Figure 1 shows a schematic view of bottom gate ZnO-TFT in which ZnO acts as a channel between drain and source of TFT. In bottom gate structure, ZnO thin film is deposited over gate dielectric. An interface between ZnO and gate dielectric is formed which is very crucial for the device performance. For enhanced performance, the interface needs to be clean and free from various defects. Therefore, the ZnO channel and underlying gate dielectric should not be subjected to excessive stress as it can give rise to interface defects or can raise reliability concerns. Moreover, the dielectric material and the channel should not react in elevated temperature. Thus, the interface should be chemically and thermodynamically stable.

According to the boundary condition, the transverse electric field density (D) should be continuous at the oxide-ZnO interface,

In terms of electric field Eq. (1) can be written as,

From the above equation it is clear that the higher the dielectric constant of gate oxide, the higher would be the electric field in the ZnO, which will result in same amount of charge in the ZnO with less applied gate bias, resulting in a lower threshold voltage VT.

In terms of the voltage the Eq. (2) can be written as

Hence a reduction in oxide thickness can also results in high field with reduced gate bias.

Another term which is used to define the scaling capability of high-κ dielectric compared to SiO2 is EOT (Effective oxide Thickness). The EOT of a high κ is the thickness required by SiO2 to achieve same voltage modulation effect or same equivalent capacitance density [12]. EOT is defined as

A lower value of EOT is helpful in reducing leakage.

There are advantages associated with high-κ gate dielectric in ZnO-TFTs. Using a thicker dielectric layer, will lead to reduction in gate field at the ZnO-Oxide interface and consequently reduce the effect of gate bias stressing on the threshold voltage VT. The use of thicker high-κ dielectric layers also reduces gate leakage current without affecting the induced interface charge density. Moreover, since one needs high driving capacity of TFT to drive the OLED pixel, one needs higher oxide capacitance and this can be achieved effectively by high-κ dielectric. However, a very large value of dielectric constant κ can lead to unfavorable large fringing field at source and drain region [13].

3 Material selection methodologies

Ashby approach is one of the most commonly used MODM approach as it optimizes alternatives based on the prioritized objectives. VIKOR and TOPSIS are MADM techniques and the alternatives are ranked on the basis of weighted attributes. Ashby approach is very easy when performance indices are less in number however, it does not generate ranking score. VIKOR and TOPSIS are widely used for a wide range of material selection problem which gives ranking solution. VIKOR and TOPSIS approaches differ in the fact that; VIKOR uses linear normalization method whereas TOPSIS uses vector normalization to convert different scales of various criteria into standard units [18, 19]. TOPSIS method gives the solution by finding the shortest distance from the ideal solution and longest distance from worst case solution whereas the VIKOR gives the compromise solution by determining least individual regret of the opponent and highest group utility of majority [18, 19].

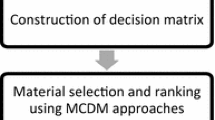

Flow chart shown in Fig. 2 illustrates the various steps that are used to find out the best gate dielectric for ZnO TFT. First step is to find out the possible dielectric candidates those form stable interface with ZnO. Lei H. Wen et al. [20] has studied ZnO–Al2O3 heterojunction, which is formed by Laser Molecular Beam epitaxy (LMBE). Moon et al. [21] studied ZnO TFT using La2O3 gate dielectric, where La2O3 was deposited using electron cyclotron resonance-atomic layer deposition (ECR-ALD). Moreover, the ZnO and BaTiO3 interface was studied and band offsets was measured by Jia et al. [22]. Similarly all the other dielectric materials used in this study has been successfully demonstrated by various researchers on ZnO [23–27]. Next step is to find out the material indices like Eg, κ and CBO and difference in temperature coefficient. This will lead to construction of fundamental decision matrix. This is followed by particular material selection methodology, to find out the best suitable material candidate out of all the possible alternatives.

3.1 Ashby approach

The Ashby approach involves mainly four steps, i.e.

-

1.

Translation of design requirements, based on objective, design constraints and free variables.

-

2.

Screening using various constraints

-

3.

Finding out suitable set of solution using the objectives

-

4.

Seeking additional information and validation with experimental results if available.

The objective is to minimize leakage and maximize dielectric constant so that ZnO TFT can be operated at low voltages. The constraints for Ashby analysis for this device are:

-

1.

Band-gap should be high (>5 eV) [39]

-

2.

Dielectric constant (κ) >15 [39]

-

3.

Conduction band offset (ΔEc) >1 eV [40]

Here the variables are the choice of materials (from set of material reported for ZnO TFT in literature) and material indices (M) are band-gap (Eg), Dielectric constant (κ) and CBO (ΔEc). The functional parameter (F) is leakage current and the geometrical parameter is scaling limit (tox or EOT). Now, one can define Ashby function A, which will determine the performance of TFT as: A = f {F, G, M}.

In any field effect transistor, the leakage current density for the case when tunneling is dominated by ECB tunneling mechanism, can be modeled by a semi empirical equation [30] given by

where h is Planck’s constant, q is electron charge, m eff is electron tunneling mass, and ϕ b is barrier height.

where \(= \left( {m_{eff } \emptyset_{b} } \right)^{{\frac{1}{2}}} k\), a and b are the constant.

From Eq. (6) it is deduced that higher the value of f, lower will be the leakage current density. For a given value of supply voltage and maximum current density JGmax the scaling limit is reciprocally related to figure of merit as:

3.2 TOPSIS approach

This approach was introduced by K. Yoon and H. C. Lai in 1981 [17]. This is used to find out the best alternative by finding out the shortest Euclidean distance (S*) from ideal solution (A*) and largest distance (S−) from worst case solution (A−) (or negative ideal solution). The steps followed in TOPSIS approach are:

Step 1

Preparation of normalized decision matrix N.

Normalized decision matrix N, consists of nij, elements with ith number of alternatives under jth number of criterion. This matrix is normalized with RMS value given by:

where i represents the set of alternative = 1, 2, 3,…, u, and j represents set of criteria = 1, 2,…,v

Step 2

Preparation of weighted normalized matrix.

In this step we assign weight to all criteria where the value of weights is chosen such that \(\mathop \sum \nolimits_{J = 1}^{v} w_{j}\) = 1, now weighted normalized matrix Mij = n ij x w j .

Step 3

Computation of ideal and negative ideal solution.

-

The ideal solution \({\text{A}}^{*} = \{ \hbox{max} {\text{M}}_{{i{\text{j}}}} |{\text{ j}} \in {\text{J}}_{1} \} \,{\text{or}}\,(\hbox{min} \,{\text{M}}_{\text{ij}} |{\text{ j}} \in {\text{J}}_{2} ) = \left\{ {{\text{M}}_{1}^{*} ,{\text{M}}_{2}^{*} ,{\text{ M}}_{3}^{*} , \ldots ,{\text{M}}_{\text{v}}^{*} } \right\} .\)

-

The worst case solution A− = {min Mij | j ∈ J1} or (max Mij | j ∈ J2) = {M1 −, M2 −, M3 −,…, M −v }.

where J1 is associated with the benefit criteria and J2 is associated with cost criteria.

Step 4

Calculation of separation measure from ideal and non ideal solution.

Now Euclidean distance can be measured as:

For both i = 1, 2, 3… u.

Step 5

Measurement of relative closeness (Ci) from ideal solution.

The relative closeness from ideal solution can be measured as:

The ranking of alternatives now depends upon the value of C i , larger the value of C i , better will be the performance of the alternative.

3.3 VIKOR approach

This approach was first proposed by Opricovic in 1998 [31] and widely accepted for selecting the material for engineering design. However, Chang [32] developed a modification in VIKOR method to simplify numerical calculation in solving problems. This method focuses on ranking and selecting from various alternatives. It is a fuzzy logic based methodology which provides a compromising solution based on the following steps.

Step 1

Determination of \(x_{j}^{*}\) and x − j values.

If x ij element belongs ith row (belongs to alternative) and jth column (belongs to criterion) of fundamental decision matrix, then first we determine \(x_{j}^{*}\), where j = 1,2,…, v, as max{x ij } or min {x ij } for i = 1,2,3,…, u,if it represents benefit criteria or cost criteria respectively. Similarly x − j is min {x ij }or max{x ij } for i = 1,2,…, u, if it represents benefit criteria or cost criteria respectively.

Step 2

To construct the maximum group utility G i and minimum regret of the opponent R i.

The values for G i and R i where i = 1,2,3,…, u is given by the following equations.

where w j is the weight of jth criteria and \(\mathop \sum \limits_{j = 1}^{v} w_{j} = 1\).

Step 3

Calculation of Q i for ith alternative where i = 1,2,3,…, u.

This is done using

where G − is max{G i } and G* is min{G i }, R − is max{R i } and R* is min{R i } and \(\sigma\) weight of strategy G i and (1-\(\sigma\)) is weight of strategy R i , usually the value of \(\sigma\) is chosen 0.5.

Step 4

Sorting the value of R, G and Q.

Finding out the value of R, G and Q in increasing order compute the ranking order (A 1 , A 2 , A 3,…,A u).

Step 5

Now the best alternative can be find out depending upon the flow chart illustrated in Fig. 3, where DQ = 1/(U − 1); where U is number of alternative.

4 Material indices of the gate-dielectrics

The value of band-gap (Eg) and dielectric constant for the high-κ material can be found easily in literature [27]. In literature the band offset value for various dielectrics are mentioned with respect to silicon. However, in present work it is required to calculate the band alignment of dielectrics on ZnO.

Figure 4 shows the dielectric-ZnO interface which is used to calculate the band offset of high-κ material on ZnO. From this figure it seems that conduction band offset (∆Ec) is the difference between electron affinity of high-κ and ZnO. However, band offset also depends upon charge transfer across interface which creates interface dipole. J. Robertson and B. Falabertti [27, 28] have used charge neutrality level (CNL) method to find out the conduction band offset (ΔEc) of high κ gate oxide on III–V semiconductor. One can use the same model to find out the band offset value on ZnO semiconductor. According to this interface between oxide and semiconductor can be considered as an interface between two semiconductor, i.e. semiconductor a and semiconductor b. The conduction band (CB) offset is given by [27]

where χ is electron affinity of semiconductor and CNL is the charge neutrality level of respective semiconductor measured from vacuum level. S is a Schottky barrier pinning factor, 0 < S < 1. The value of S is 1 in the absence of dipoles i.e. wide band-gap material and the value of S is 0 for the strongly pinned interface. So we can simplify the Eq. (15) for ZnO-high κ interface as:

The electron affinity and CNL of ZnO are 4.6 eV and 3.27 eV [27] respectively. The values of electron affinity of various dielectrics are found on J. Robertson [28] work. The value of S can be found by the empirical relation given by Monch [29].

where \(\varepsilon_{\infty }\) is electronic part of dielectric constant. The CNL values given in Table 1 are measured from the top of valence band. Like La2O3, Sc2O3 and Y2O3 show same bad offset performance of 3.1 eV as calculated from Eq. (16). Table 1 shows electron affinity, charge neutrality level, S and conduction band offset to ZnO of all possible high-κ gate dielectric and Table 2 provides the values for band-gap, dielectric constant and conduction band offset.

Most of the oxide e.g. La2O3, Al2O3, Gd2O3, ZrO2 etc. show excellent CBO because ZnO possesses large value of electron affinity. Once the CBO values are known, the valence band offset (VBO) values can be easily computed. Figure 5 shows the CBO and VBO of various high κ oxides on ZnO. A positive value of VBO indicates that the holes need particular amount of energy to cross energy barrier i.e. ZnO valence band to high-κ valence band. Table 2 gives material indices of various dielectrics.

Together with the material indices listed in Table 2; thermal expansion coefficient mismatch (|ΔTEC|) also plays an important role in deciding the performance of TFT because deposition of thin film on a substrate or channel includes high temperature process. Also a significant amount of temperature coefficient mismatch may lead to considerable amount of stress which will eventually leads to defects in interface, or excessive stress which can cause the device failure. Table 3 shows the values of thermal coefficient mismatch in PPM/0K of various gate dielectrics with ZnO.

ZnO has a thermal expansion coefficient close to 4.6 × 10−6/ °C [33]. |Δ TEC| in PPM/ °C is computed by taking the difference between TEC of ZnO and dielectric irrespective of the nature of stress i.e. compressive or tensile. So |Δ TEC| is a cost criterion for TOPSIS and VIKOR approach.

5 Results and discussion

5.1 Ashby analysis

In Ashby approach first step is to plot the graphs in between various material indices. Then one needs to apply the constraints to find out possible sets of dielectrics.

Figure 6 shows the plot between conduction band offset and band-gap for all the possible high-κ dielectric. As one requires Eg more than 5 eV and CBO more than 1 eV it is clear that Ga2O3, SrTiO3, Ta2O5, BaTiO3 do not fulfill the required conditions. The materials that satisfy the requirements are shown under the shaded rectangle.

Figure 7 shows the plot between band-gap and dielectric constant of all possible materials. As one needs E g more than 5 eV and κ more than 15, SiO2, Al2O3, HfSiO4, Si3N4, Ta2O5, Ga2O3, Sc2O3, Gd2O3 violate the constraints and are removed from the selection of gate dielectric. Shaded rectangle shown in Fig. 7 covers all those materials that satisfy the conditions.

Figure 8 shows plot between CBO and dielectric constant. As stated one needs CBO greater than 1 eV and κ greater than 15, SiO2, Al2O3, Sc2O3, HfSiO4, Si3N4 don’t fit in constraint. Hence the material left that satisfies all the constraints are HfO2, ZrO2, La2O3, LaAlO3. Ga2O3 and Ta2O5 narrowly violate these constraints. However, by investigating the figure of merit (f) of these possible dielectrics it is clear that best alternative as a gate dielectric of ZnO TFT is La2O3. This is followed by LaAlO3, ZrO2 and HfO2 (Fig. 9).

5.2 TOPSIS analysis

For the TOPSIS and VIKOR one needs a weight matrix with proper justification. The dielectric constant κ can be given highest weight because of reason stated in Sect. 2. It is followed by CBO and then by band-gap and the least weight is given to temperature coefficient mismatch because various process techniques are available which either can deposit oxides in low thermal budget or some additional deposition of stress relieving material which can overcome the induced intrinsic stress. So keeping \(\mathop \sum \limits_{J = 1}^{v} w_{j}\) = 1 in view, the weight matrix is W = [0.4, 0.3, 0.2, 0.1]. Table 4 shows the weighted normalized matrix as mentioned in Sect. 3.2.

The parameters in brackets in Table 4 are the normalized value of parameter with respect to root mean square value. From the Table 4 one can find out the ideal (A*) and negative ideal (A−) solution as:

Table 5 gives the values of Euclidean distance from ideal and non ideal solution, relative closeness from ideal solution (C) and the TOPSIS rank.

From the Table 5 it is observed that La2O3 is best ranked material followed by, HfO2, ZrO2 and LaAlO3.

5.3 VIKOR analysis

From the calculation of maximum group utility Gi and minimum regret of the opponent Ri one can find out the following.

Table 6 shows the value R, G and Q for all the dielectrics and ranking based on the values of corresponding R, G and Q.

Since Q(A 2) − Q(A 1) > 0.08334 and A1 is the same for R and G too hence La2O3 is best choice material followed by HfO2. While comparing the result of all the three approaches all gives La2O3 a lead over other dielectrics. Other suitable dielectric materials that can be used are HfO2, ZrO2 and LaAlO3.

In order to validate findings of this work, the results of proposed analysis are compared with the experimental data. Table 7 shows the comparative analysis of ZnO based TFT employing different dielectrics namely La2O3, HfO2 and ZrO2, which are deposited using RF sputtering. It clearly indicates that ZnO based TFT using La2O3 as a gate dielectric shows superior performance than HfO2 and ZrO2 in terms of threshold voltage (VT) and leakage current (Ioff). The close match between outcome of this work and experimental results shows the validity of the proposed analysis for the low voltage and low leakage TFT. In order to improve other performance indices like mobility and SS, the ZnO deposition techniques can be optimized so that it results in less number of grain boundary and large grain size.

6 Conclusion

This paper highlighted the importance of high-κ dielectric for low voltage and low leakage ZnO TFT. The values of band offset of various dielectrics on ZnO TFT are calculated analytically. Three different material selection methodologies like Ashby, TOPSIS and VIKOR are used to find out the best gate dielectric material. Dielectric constant, band-gap, conduction band offset and thermal coefficient mismatch are used as material indices in these methodologies. These analyses converge that La2O3 is the most promising gate dielectric material for low threshold voltage and low leakage TFT. The result shows good agreement among Ashby, TOPSIS and VIKOR approaches.

References

R.A. Street, Technology and Applications of Amorphous Silicon (Springer, Berlin, 2000)

B.C. Easton, J.A. Chapman, O.F. Hill, M.J. Powell, The plasma-enhanced deposition of hydrogenated amorphous silicon. Vacuum 34, 371 (1984)

E.M.C. Fortunato, P.M.C. Barquinha, A.C.M.B.G. Pimentel, A.M.F. Gonçalves, A.J.S. Marques, R.F.P. Martins, L.M.N. Pereira, Wide-bandgap high-mobility ZnO thin-film transistors produced at room temperature. Appl. Phys. Lett. 85, 2541 (2004)

C.Y. Tsay, M.C. Wang, S.C. Chiang, Characterization of Zn1−xMgxO films prepared by sol–gel process and their application for thin-film transistors. J. Electron. Mater. 38, 1962–1968 (2009)

J. Hue, R.G. Gordon, Textured aluminum-doped zinc oxide thin films from atmospheric pressure chemical-vapor deposition. J. Appl. Phys. 71, 880 (1992)

S. Hayamizu, H. Tabata, H. Tanaka, T. Kawai, Preparation of crystallized zinc oxide films on amorphous glass substrates by pulsed laser deposition. J. Appl. Phys. 80, 787 (1996)

L. Chang, Y.K. Choi, H. Daewon, P. Ranade, X. Shiying, J. Bokor, H. Chenming, T.J. King, Extremely scaled silicon nano-CMOS devices. Proc. IEEE 91, 1860–1873 (2003)

M. Koh, W. Mizubayashi, K. Lwamoto, H. Murakami, T. Ono, M. Tsuno, T. Mihara, K. Shibahara, S. Miyazaki, M. Hirose, Limit of gate oxide thickness scaling in MOSFETs due to apparent threshold voltage fluctuation induced by tunnel leakage current. IEEE Trans. Electron. Dev. 48, 259–264 (2001)

R.M. Wallace, G.D. Wilk, Exploring the limits of gate dielectric scaling. Semicond. Int. 24, 153–154 (2001)

B.N. Aditya, N. Gupta, Material selection methodology for gate dielectric material in metal-oxide-semiconductor. Mater. Des. 35, 696–700 (2012)

B.J. Norris, J. Anderson, J.F. Wager, D.A. Keszler, Spin-coated zinc oxide transparent transistors. J. Phys. D Appl. Phys. 36, L105–L107 (2003)

G.D. Wilk, R.M. Wallace, J.M. Anthony, High-κ gate dielectrics: current status and materials properties considerations. J. Appl. Phys. 89(10), 5243–5273 (2001)

Plummer, J. D., Griffin, Material and process limits in silicon VLSI technology. Proc. IEEE 89, 240–258 (2001)

L. Anojkumar, M. Ilangkumaran, V. Sasirekha, Comparative analysis of MCDM methods for pipe material selection in sugar industry. Expert Syst. Appl. 41, 2964–2980 (2014)

M.F. Ashby’s, Multi objective optimization in material design and selection. Acta Mater. 48, 1792–1795 (2000)

M.F. Ashby’s, Material Selection in Mechanical Design, 2nd edn. (Butterworth-Heinemann, Oxford, 1999)

C. Hwang, K. Yoon, in Multiple Attribute Decision Making Methods and Application Survey, 1st edn., vol. 181 (Springer, Berlin, 2005), pp. 58–191

S. Opricovic, G.H. Tzeng, Compromise solution by MCMD methods: a comparative analysis of VIKOR and TOPSIS. Eur. J. Oper. Res. 156, 445–455 (2004)

P. Sharma, N. Gupta, Investigation on material selection for gate dielectric in nanocrystalline silicon (nc-Si) top-gated thin film transistor (TFT) using Ashby’s, VIKOR and TOPSIS. J. Mater. Sci. Mater. Electron. 26(12), 9607–9613 (2015). doi:10.1007/s10854-015-3624-9

L.E.I. Hong Wen, Z. Kong, W.X. Min, Z. Yan, Y.D. Wei, J.Z. Qian, Y. Gang, Z.T. Xian, W.W. Dong, Measurement of ZnO/Al2O3 heterojunction band offsets by in situ X-ray photoelectron spectroscopy. Chin. Phys. Lett. 30, 11 (2013)

Y.K. Moon, S. Lee, J.W. Park, Characteristic of ZnO based TFT using La2O3 high-κ dielectrics. J. Korean Phys. Soc. 55(5), 1906–1909 (2009)

C.H. Jia, Y.H. Chen, X.L. Zhou, A.L. Yang, G.L. Zheng, X.L. Liu, S.Y. Yang, Z.G. Wang, Valence band offset of ZnO/BaTiO3 heterojunction measured by X-ray photoelectron spectroscopy. Appl. Phys. A 99, 511–514 (2010)

J.H. Kim, B.D. Ahn, C.H. Lee, K.A. Jeon, H.S. Kang, S.Y. Lee, Characteristics of transparent ZnO based thin film transistors with amorphous HfO2 gate insulators and Ga doped ZnO electrodes. Thin Solid Films 516(7), 1529–1532 (2008)

Y.J. Cho, J.H. Shin, S.M. Bobade, Y.B. Kim, D.K. Choi, Evaluation of Y2O3 gate insulators for a-IGZO thin film transistors. Thin Solid Films 517, 4115–4118 (2009)

Y. Gao, X. Li, L. Chen, J. Shi, X.W. Sun, J. Zhang, High mobility solution-processed hafnium indium zinc oxide TFT with an Al-doped ZrO2 gate dielectric. IEEE Electron. Dev. Lett. 35, 5 (2014)

J. Yang, J.K. Park, S. Kim, W. Choi, S. Lee, H. Kim, Atomic-layer-deposited ZnO thin-film transistors with various gate dielectrics. Phys. Status Solidi A 209(10), 2087–2090 (2012)

J. Robertson, B. Falabretti, Band offsets of high K gate oxides on III–V semiconductor. J. Appl. Phys. 100, 014111 (2006)

J. Robertson, High dielectric constant oxides. Eur. Phys. J. Appl. Phys. 28, 265–291 (2004)

W. Monch, Role of virtual gap states and defects in metal–semiconductor contacts. Phys. Rev. Lett. 58, 1260 (1987)

Y. Yeo, T.J. King, C. Hu, MOSFET gate leakage modeling and selection guide for alternate gate dielectrics based on leakage considerations. IEEE Trans. Electron. Dev. 50, 1027–1035 (2003)

S. Opricovic, Multi-criteria optimization of civil engineering systems (Faculty of Civil Engineering, Belgrade, 1998)

C.-L. Chang, A modified VIKOR method for multiple criteria analysis. Environ. Monit. Assess. 168, 339–344 (2010)

N. Yamamoto, H. Makino, T. Yamamoto, Young’s modulus and coefficient of linear thermal expansion of ZnO conductive and transparent ultra-thin films. Adv. Mater. Sci. Eng. (2011). doi:10.1155/2011/136127

J. Sanghera, W. Kim, G. Villalobos, B. Shaw, C. Baker, J. Frantz, B. Sadowski, I. Aggarwal, Ceramic laser materials. Materials 5, 258–277 (2012)

S.R. Skaggs, Zero and low coefficient of Thermal expansion polycrystalline oxides (Scientific laboratory of the University of California, Los Alamos, 1977)

V.B. Braginsky, A.A. Samoilenko, Measurements of the optical mirror coating properties. Phys. Lett. A 315, 175–177 (2003)

R.V. Krishnan, G. Panneerselvam, P. Mankinandan, M.P. Antony, K. Nagarajan, Heat capacity and thermal expansion of uranium–gadolinium mixed oxides. J. Nucl. Radiochem. Sci. 10, 19–26 (2009)

L. Fu, J. Wong-Leung, P.N.K. Deenapanray, H.H. Tan, C. Jagadish, B. Gong, R.N. Lamb, R.M. Cohen, W. Reichert, L.V. Dao, M. Gal, Suppression of interdiffusion in GaAs/AlGaAs quantum-well structure capped with dielectric films by deposition of gallium oxide. J. Appl. Phys. 92, 7 (2002)

International Technology Roadmap for Semiconductors (ITRSs). Semiconductor Industry Association, 181 Metro Drive, Suite 450, San Jose, CA 95110 (2006)

A.P. Huang, Z.C. Yang, P.K. Chu, in Hafnium-based high-κ gate dielectrics, ed. by P.K. Chu. Advances in Solid State Circuits Technologies, vol. 446 (INTECH, Rijeka, 2010)

L.X. Qian, P.T. Lai, W.M. Tang, Effects of Ta incorporation in La2O3 gate dielectric of InGaZnO thin-film transistor. Appl. Phys. Lett. 104, 123505 (2014). doi:10.1063/1.4869761

L.-W. Ji, C.-Z. Wu, T.-H. Fang, Y.J. Hsiao, T.-H. Meen, W. Water, Z.-W. Chiu, K.-T. Lam, Characteristics of flexible thin-film transistors with ZnO channels. IEEE Sens. J. 13, 12 (2013)

J.S. Lee, S. Chang, S.-M. Koo, S.Y. Lee, High-performance a-IGZO TFT with ZrO2 gate dielectric fabricated at room temperature. IEEE Electron. Dev. Lett. 31(3), 225–227 (2010)

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflict of interest.

Rights and permissions

About this article

Cite this article

Kandpal, K., Gupta, N. Investigations on high-κ dielectrics for low threshold voltage and low leakage zinc oxide thin-film transistor, using material selection methodologies. J Mater Sci: Mater Electron 27, 5972–5981 (2016). https://doi.org/10.1007/s10854-016-4519-0

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10854-016-4519-0